Пристрій для контролю бінарного коду на парність

Номер патенту: 82300

Опубліковано: 25.07.2013

Автори: Козелкова Катерина Сергіївна, Одноралов Ігор Васильович, Гавриленко Валерій Володимирович, Шульга Олександр Васильович

Формула / Реферат

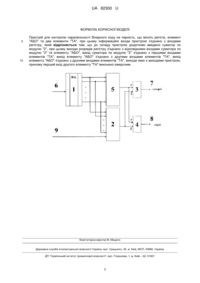

Пристрій для контролю паралельності бінарного коду на парність, що місить регістр, елемент "АБО" та два елементи "ТА", при цьому інформаційні входи пристрою з'єднано з входами регістру, який відрізняється тим, що до складу пристрою додатково введено суматор по модулю "2", при цьому виходи розрядів регістру з'єднано з відповідними входами суматора по модулю "2" та елементу "АБО", вихід суматора по модулю "2" з'єднано з першими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", виходи яких є виходами пристрою, причому перший вхід другого елементу "ТА" виконано інверсним.

Текст

Реферат: Пристрій для контролю паралельності бінарного коду на парність місить регістр, елемент "АБО" та два елементи "ТА", при цьому інформаційні входи пристрою з'єднано з входами регістру. До складу пристрою додатково введено суматор по модулю "2". Виходи розрядів регістру з'єднано з відповідними входами суматора по модулю "2" та елементу "АБО". Вихід суматора по модулю "2" з'єднано з першими входами елементів "ТА". Вихід елементу "АБО" з'єднано з другими входами елементів "ТА". Вихід елементу "АБО" з'єднано з другими входами елементів "ТА", виходи яких є виходами пристрою. Перший вхід другого елементу "ТА" виконано інверсним. UA 82300 U (12) UA 82300 U UA 82300 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі обчислювальної техніки та автоматики, зокрема до приладів та пристроїв обчислювальної техніки, а саме, до пристроїв для контролю паралельного бінарного коду на парність та може бути використана у пристроях для перевірки на парність інформації, що застосовується у паралельному коді. Відомий пристрій для контролю бінарного коду на парність, що містить елементи "ТА", перші входи яких з'єднані з виходами відповідних розрядів, що контролюються, елементи "АБО", виходи яких підключені до виходів елементів "ТА", розподілювач імпульсів та фіксуючий тригер [1]. Недоліками відомого аналогу є його складність та низька швидкодія, обумовлена необхідність опитування усіх розрядів, у тому числі тих, які знаходяться у нульовому стані, а також необхідність спеціального обнуління відповідних розрядів після закінчення процесу контролю коду на парність, внаслідок чого сповільнюється готовність до контролю наступної кодової комбінації. Відомий пристрій для контролю паралельного бінарного коду на парність, що містить вхідний реєстр, дешифратор, шифратор, формувач імпульсу та елемент "АБО", при цьому вхід вхідного реєстру є інформаційним входом пристрою, а вихід вхідного реєстру з'єднано з інформаційним входом дешифратора [2]. Недоліками відомого технічного рішення є низька швидкодія та необхідність використання тактових імпульсів, що, крім іншого, обмежує межи його застосування (за рахунок виключення з меж застосування асинхронних систем). Відомий пристрій для контролю паралельного бінарного коду на парність, що містить регістр, групу елементів "ТА", елемент "АБО", тригер, елемент "ТА" та елемент "ТА-НІ", при цьому інформаційні входи пристрою з'єднано з одиничними входами регістру, одиничний вихід кожного розряду регістру з'єднано з першим входом відповідного елементу "ТА" групи, вихід кожного елементу "ТА" групи з'єднано з нульовим входом відповідного розряду регістру та з відповідним входом елементу "АБО", вихід якого з'єднано з ліченим входом тригера, виходи якого є виходами пристрою, тактовий вхід пристрою з'єднано з першим входом елемента "ТА", вихід якого з'єднано з другими входами елементів "ТА" групи, нульовий вихід к-того розряду регістру з'єднано з відповідним входом елементу "ТА-НІ" та з (k+2)-ми входами елементів "ТА" групи від (k+1)-го до n-го, вихід елементу "ТА-НІ" з'єднано з другим входом елементу "ТА" [3]. Недоліками відомого технічного рішення є низька швидкодія та необхідність використання тактових імпульсів, що, крім іншого, обмежує межи його застосування (за рахунок виключення з меж застосування асинхронних систем). До недоліків відноситься також складність системи, при цьому конструктивне виконання пристрою не дозволяє використовувати його у асинхронних системах, де необхідно отримувати результат контролю паралельного бінарного коду на парність відразу після його відправлення до приймального регістру. Найбільш близьким технічним рішенням, як за суттю, так і за задачею, що вирішується, яке вибрано за найближчий аналог (прототип) є пристрій для контролю паралельного коду на парність, що містить регістр, елемент "АБО" та два елементи "ТА", при цьому інформаційні входи пристрою з'єднано з входами регістру [4]. Недоліками пристрою для контролю паралельності коду на парність, який вибрано за найближчий аналог (прототип), є його низька швидкодія та обмежена область застосування, оскільки тактування роботи пристрою не дозволяє використовувати його у асинхронних системах, де необхідно отримувати результат контролю паралельного бінарного коду на парність відразу після його відправлення до приймального регістру. В основу корисної моделі покладена задача шляхом введення до складу пристрою для контролю паралельності бінарного коду на парність суматора по модулю "2" забезпечити більш високу швидкодію при упрощенні схеми перетворення коду з розширенням при цьому межі застосування пристрою. Суть технічного рішення у пристрої для контролю паралельності бінарного коду на парність, що містить регістр, елемент "АБО" та два елементи "ТА", при цьому інформаційні входи пристрою з'єднано з входами регістру, полягає у тому, що до складу пристрою додатково введено суматор по модулю "2", при цьому виходи розрядів регістру з'єднано з відповідними входами суматора по модулю "2" та елементу "АБО", вихід суматора по модулю "2" з'єднано з першими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", виходи яких є виходами пристрою, причому перший вхід другого елементу "ТА" виконано інверсним. Рішення поставленої задачі в пристрої, який заявляється, дійсно можливе тому, що до складу пристрою додатково введено суматор по модулю "2", що, в свою чергу, дозволить забезпечити більш високу швидкодію та розширити межі застосування пристрою. 1 UA 82300 U 5 10 15 20 25 30 35 40 45 50 55 60 Отримання позитивного ефекту при реалізації корисної моделі досягається тим, що введення суматора по модулю "2" дозволяє проводити контроль паралельного бінарного коду на парність асинхронно, без застосування тактових імпульсів. Таке схемно-технічне рішення спрощує процес контролю, спрощує конструктивне виконання пристрою, що заявляється, та розширює межи його застосування за рахунок використання зазначеного пристрою у асинхронних системах. Таким чином, пристрій для контролю паралельності бінарного коду на парність, що заявляється, відповідає критерію корисної моделі "новизна". Суть корисної моделі пояснюється за допомогою креслення, де на кресленні показано (як варіант конструктивного виконання) функціональну схему пристрою для контролю паралельності бінарного коду на парність, що заявляється. Пристрій для контролю паралельності бінарного коду на парність, що заявляється, містить (як варіант конструктивного виконання див. блок-схему на кресленні) регістр 1 (додатково позначений "RG" - див. блок-схему на кресленні), елемент (2) "АБО", перший та другий елементи "ТА" (відповідно, позиції 3 та 4), суматор 5 по модулю "2", перший (6) інформаційний вхід пристрою, виходи (позиції 7 та 8) пристрою та другий (9) інформаційний вхід пристрою. При цьому конструктивно перший вхід другого (4) елементу "ТА" виконано інверсним. Конструктивно і технологічно конструктивні елементи пристрою для контролю паралельності бінарного коду на парність, що заявляється, з'єднано між собою таким чином: - перший (6) інформаційний вхід пристрою з'єднано з входом регістра 1 (додатково позначений "RG" - див. блок-схему на кресленні); - другий (9) інформаційний вхід пристрою з'єднано з входом елемента (2) "АБО"; - виходи регістра 1 з'єднано з відповідними входами суматора 5 по модулю "2" та входами елемента (2) "АБО"; - вихід суматора 5 по модулю "2" з'єднано з першими входами першого та другого елементів "ТА" (відповідно, позиції 3 та 4); - вихід елементу 2 "АБО" з'єднано з другими входами першого та другого елементів "ТА" (відповідно, позиції 3 та 4), виходи яких є виходами 7 та 8 пристрою. Пристрій для контролю паралельності бінарного коду на парність, що заявляється, працює таким чином. Паралельний бінарний код, що перевіряється на парність, заноситься до регістру 1. Ознакою того, що бінарний код, відмінний від нульового, у регістр 1 записано сигнал на виході елемента (2) "АБО". Якщо код "000…0" у цифровій системі не є кодом-роз'єднувачем, а є інформаційним кодом [5], то сигнал на виході елементу (2) "АБО" може бути сформований сигналом "ДОЗВІЛ КОНТРОЛЮ" з виходу попереднього блоку, що надходить на вхід (9) пристрою, а саме, на вхід елемента (2) "АБО". Сигнал з виходу елементу (2) "АБО" дозволяє проходження результату контролю через перший та другий елементи "ТА" (відповідно, позиції 3 та 4), на виходи (7) та (8) пристрою. Сигнал на виході (7) пристрою свідчить про непарність одиниць у числі, а сигнал на виході (8) пристрою свідчить про парність одиниць у числі. Таким чином, введення суматора по модулю "2" до складу пристрою для контролю паралельності бінарного коду на парність, що заявляється, дозволяє проводити контроль на парність у асинхронних системах, що виключає застосування тактових імпульсів. Пристрій, що заявляється, є більш простим у виконанні (по відношенню до аналогів) та більш швидкодіючим у порівнянні з прототипом. Підвищення ефективності застосування пристрою для контролю паралельності бінарного коду на парність, що заявляється, по відношенню до прототипу, досягається тим, що шляхом введення до складу зазначеного пристрою суматора по модулю "2", здійснюється можливість проведення контролю на парність у асинхронних системах, що виключає застосування тактових імпульсів, а це, у свою чергу, дозволить розширити межи його застосування за рахунок використання зазначеного пристрою у асинхронних системах. Джерела інформації: 1. Авторське свідоцтво СРСР № 428385, G 06 F 11/10, 1975 г. - аналог. 2. Авторське свідоцтво СРСР № 1084800, G 06 F 11/10, бюл. № 13, 1984 - аналог. 3. Авторське свідоцтво СРСР № 883910, G 06 F 11/10, бюл. № 43, 1981 - аналог. 4. Патент Російської Федерації № 2159988, опубл. 27.11.2000, бюл. № 33, МПК (2006.1) Н 03 М 5/12 прототип. 5. Патент Російської Федерації № 2297096 (13) С1, опубл. 10.04.2007, МПК (2006.1) Н 03 М 5/12 2 UA 82300 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 Пристрій для контролю паралельності бінарного коду на парність, що місить регістр, елемент "АБО" та два елементи "ТА", при цьому інформаційні входи пристрою з'єднано з входами регістру, який відрізняється тим, що до складу пристрою додатково введено суматор по модулю "2", при цьому виходи розрядів регістру з'єднано з відповідними входами суматора по модулю "2" та елементу "АБО", вихід суматора по модулю "2" з'єднано з першими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", вихід елементу "АБО" з'єднано з другими входами елементів "ТА", виходи яких є виходами пристрою, причому перший вхід другого елементу "ТА" виконано інверсним. Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for control of parallel binary code pairing

Автори англійськоюOdnoralov Ihor Vasyliovych, Kozelkova Kateryna Serhiivna, Havrylenko Valerii Volodymyrovych, Shulha Oleksandr Vasyliovych

Назва патенту російськоюУстройство для контроля бинарного кода на парность

Автори російськоюОдноралов Игорь Васильевич, Козелкова Екатерина Сергеевна, Гавриленко Валерий Владимирович, Шульга Александр Васильевич

МПК / Мітки

МПК: G06F 11/10

Мітки: парність, контролю, коду, пристрій, бінарного

Код посилання

<a href="https://ua.patents.su/5-82300-pristrijj-dlya-kontrolyu-binarnogo-kodu-na-parnist.html" target="_blank" rel="follow" title="База патентів України">Пристрій для контролю бінарного коду на парність</a>

Попередній патент: Спосіб визначення жирнокислотного складу ліпідів кульбаби та цикорію

Наступний патент: Пристрій для перетворення адреси

Випадковий патент: Спосіб отримання нанокомпозитів на основі поліетеру та вуглецевих нанотрубок