Пристрій для обчислення усіченого перетворення фур`є в залишкових класах

Номер патенту: 14431

Опубліковано: 15.05.2006

Автори: Колмиков Максим Миколайович, Дуденко Сергій Васильович, Алексєєв Сергій Вікторович, Рубан Ігор Вікторович, Калачова Вероніка Валеріївна

Формула / Реферат

Пристрій для обчислення усіченого перетворення Фур'є в залишкових класах, який містить блок оперативної пам'яті, перший, другий, третій та четвертий блоки постійної пам'яті, перший та другий мультиплексори, блок складання по модулю два, перший, другий, третій, четвертий та п'ятий регістри, блок керування, до складу якого входять генератор тактових імпульсів, перший, другий та третій тригери, перший, другий, третій та четвертий лічильники, дешифратор, перший, другий, третій, четвертий та п'ятий елементи І, формувач фронтів, перший та другий елементи АБО, постійний запам'ятовуючий пристрій, який відрізняється тим, що додатково введені перший та другий мультиплексори, п'ятий регістр, до блока керування додатково введені другий, третій та четвертий лічильники, п'ятий елемент І, формувач фронтів, перший та другий елементи АБО, другий та третій тригери, блок постійної пам'яті, вхід запуску пристрою з'єднаний з входом блока керування, адресні входи блока оперативної пам'яті з'єднані з першим виходом блока керування, вхід дозволу читання блока оперативної пам'яті з'єднаний з другим виходом блока керування, вихід блока оперативної пам'яті з'єднаний з адресними входами першого, другого, третього та четвертого блоків постійної пам'яті, входи дозволу читання першого, другого, третього та четвертого блоків постійної пам'яті з'єднані з другим виходом блока керування, вихід першого блока постійної пам'яті з'єднаний з першим входом першого мультиплексора, вихід другого блока постійної пам'яті з'єднаний з другим входом першого мультиплексора, вихід третього блока постійної пам'яті з'єднаний з третім входом першого мультиплексора, вихід четвертого блока постійної пам'яті з'єднаний з четвертим входом першого мультиплексора, адресні входи першого мультиплексора з'єднані з третім виходом блока керування, вихід першого мультиплексора з'єднаний з другим входом блока, що реалізує операцію складання по модулю два, вихід блока, що реалізує операцію складання по модулю два, з'єднаний з входами даних першого, другого, третього та четвертого регістрів, входи дозволу запису першого, другого, третього та четвертого регістрів з'єднані з четвертим виходом блока керування, вихід першого регістра з'єднаний з першим входом другого мультиплексора, вихід другого регістра з'єднаний з другим входом другого мультиплексора, вихід третього регістра з'єднаний з третім входом другого мультиплексора, вихід четвертого регістра з'єднаний з четвертим входом другого мультиплексора, адресні входи другого мультиплексора з'єднані з п'ятим виходом блока керування, вихід другого мультиплексора з'єднаний з входом даних п'ятого регістра, вхід дозволу запису п'ятого регістра з'єднаний з п'ятим виходом блока керування, вихід п'ятого регістра є виходом пристрою та з'єднаний з першим входом блока, що реалізує операцію складання по модулю два, вхід блока керування з'єднаний з входом переводу першого тригера в одиницю, вихід першого тригера з'єднаний з входом генератора тактових імпульсів, вихід якого з'єднаний з рахунковим входом другого лічильника та другими входами другого, третього, четвертого та п'ятого елементів І, вхід скидання першого тригера з'єднаний з виходом переповнення (переносу) першого лічильника, перший вихід другого лічильника (молодший розряд) з'єднаний з першим входом дешифратора (молодший розряд) і першим входом першого елемента І, другий вихід другого лічильника з'єднаний з другим входом дешифратора, третій вихід другого лічильника з'єднаний з третім входом дешифратора, четвертий вихід другого лічильника (старший розряд) з'єднаний з четвертим входом дешифратора (старший розряд) і другим входом першого елемента І, вихід першого елемента І з'єднаний з входом формувача фронтів, вихід формувача фронтів з'єднаний з входом першого лічильника, входом обнуління другого лічильника, входами обнуління другого та третього тригерів, перший вихід дешифратора з'єднаний з входом переводу другого тригера в одиницю, другий вихід дешифратора з'єднаний входом переводення третього тригера в одиницю, третій вихід дешифратора з'єднаний з першим входом першого елемента АБО, четвертий вихід дешифратора з'єднаний з другим входом другого елемента АБО і першим входом другого елемента І, п'ятий вихід дешифратора з'єднаний з другим входом першого елемента АБО, шостий вихід дешифратора з'єднаний з третім входом другого елемента АБО і першим входом третього елемента І, сьомий вихід дешифратора з'єднаний з третім входом першого елемента АБО, восьмий вихід дешифратора з'єднаний з першим входом другого елемента АБО і першим входом четвертого елемента І, дев'ятий вихід дешифратора з'єднаний з четвертим входом першого елемента АБО, десятий вихід дешифратора з'єднаний з четвертим входом другого елемента АБО і першим входом п'ятого елемента І, вихід першого елемента АБО з'єднаний з тактовим входом третього лічильника, вихід другого елемента АБО з'єднаний з тактовим входом четвертого лічильника, виходи четвертого лічильника з'єднані з входами постійного запам'ятовуючого пристрою, вихід першого лічильника (молодший розряд) по першому виходу блока керування з'єднаний з адресним входом (молодший розряд) блока оперативної пам'яті, вихід першого лічильника (старший розряд) по першому виходу блока керування з'єднаний з адресним входом (старший розряд) блока оперативної пам'яті, вихід другого тригера по другому виходу блока керування з'єднаний з входом дозволу читання блока оперативної пам'яті, вихід третього тригера по другому виходу блока керування з'єднаний з входами дозволу читання першого, другого, третього та четвертого блоків постійної пам'яті, виходи постійного запам'ятовуючого пристрою по третьому виходу блока керування з'єднані з адресними входами першого мультиплексора, вихід другого елемента І по четвертому виходу блока керування з'єднаний з входом дозволу запису першого регістра, вихід третього елемента І по четвертому виходу блока керування з'єднаний з входом дозволу запису другого регістра, вихід четвертого елемента І по четвертому виходу блока керування з'єднаний з входом дозволу запису третього регістра, вихід п'ятого елемента І по четвертому виходу блока керування з'єднаний з входом дозволу запису четвертого регістра, вихід першого елемента АБО по п'ятому виходу блока керування з'єднаний з входом дозволу запису п'ятого регістра, виходи третього лічильника по п'ятому виходу блока керування з'єднані з адресними входами другого мультиплексора.

Текст

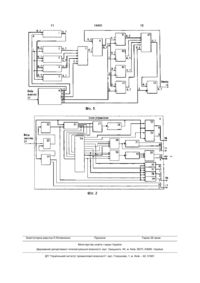

Пристрій для обчислення усіченого перетворення Фур'є в залишкових класах, який містить блок оперативної пам'яті, перший, другий, третій та четвертий блоки постійної пам'яті, перший та другий мультиплексори, блок складання по модулю два, перший, другий, третій, четвертий та п'ятий регістри, блок керування, до складу якого входять генератор тактових імпульсів, перший, другий та третій тригери, перший, другий, третій та четвертий лічильники, дешифратор, перший, другий, третій, четвертий та п'ятий елементи І, формувач фронтів, перший та другий елементи АБО, постійний запам'ятовуючий пристрій, який відрізняється тим, що додатково введені перший та другий мультиплексори, п'ятий регістр, до блока керування додатково введені другий, третій та четвертий лічильники, п'ятий елемент І, формувач фронтів, перший та другий елементи АБО, другий та третій тригери, блок постійної пам'яті, вхід запуску пристрою з'єднаний з входом блока керування, адресні входи блока оперативної пам'яті з'єднані з першим виходом блока керування, вхід дозволу читання блока оперативної пам'яті з'єднаний з другим виходом блока керування, вихід блока оперативної пам'яті з'єднаний з адресними входами першого, другого, третього та четвертого блоків постійної пам'яті, входи дозволу читання першого, другого, третього та четвертого блоків постійної пам'яті з'єднані з другим виходом блока керування, вихід першого блока постійної пам'яті з'єднаний з першим входом першого мультиплексора, вихід другого блока постійної пам'яті з'єднаний з другим входом першого мультиплексора, вихід третього блока постійної пам'яті з'єднаний з третім входом першого мультиплексора, вихід четвертого блока постійної пам'яті з'єднаний з четвертим входом першого мультиплексора, адресні входи першого мультиплексора з'єднані з третім 2 (19) 1 3 14431 4 тього тригера в одиницю, третій вихід дешифратонаний з адресним входом (старший розряд) блока ра з'єднаний з першим входом першого елемента оперативної пам'яті, вихід другого тригера по друАБО, четвертий вихід дешифратора з'єднаний з гому виходу блока керування з'єднаний з входом другим входом другого елемента АБО і першим дозволу читання блока оперативної пам'яті, вихід входом другого елемента І, п'ятий вихід дешифратретього тригера по другому виходу блока керутора з'єднаний з другим входом першого елемента вання з'єднаний з входами дозволу читання перАБО, шостий вихід дешифратора з'єднаний з трешого, другого, третього та четвертого блоків постім входом другого елемента АБО і першим вхотійної пам'яті, виходи постійного запам'ятовуючого дом третього елемента І, сьомий вихід дешифрапристрою по третьому виходу блока керування тора з'єднаний з третім входом першого елемента з'єднані з адресними входами першого мультиплеАБО, восьмий вихід дешифратора з'єднаний з пексора, вихід другого елемента І по четвертому ршим входом другого елемента АБО і першим виходу блока керування з'єднаний з входом довходом четвертого елемента І, дев'ятий вихід дезволу запису першого регістра, вихід третього шифратора з'єднаний з четвертим входом першоелемента І по четвертому виходу блока керування го елемента АБО, десятий вихід дешифратора з'єднаний з входом дозволу запису другого регістз'єднаний з четвертим входом другого елемента ра, вихід четвертого елемента І по четвертому АБО і першим входом п'ятого елемента І, вихід виходу блока керування з'єднаний з входом допершого елемента АБО з'єднаний з тактовим вхозволу запису третього регістра, вихід п'ятого еледом третього лічильника, вихід другого елемента мента І по четвертому виходу блока керування АБО з'єднаний з тактовим входом четвертого ліз'єднаний з входом дозволу запису четвертого чильника, виходи четвертого лічильника з'єднані з регістра, вихід першого елемента АБО по п'ятому входами постійного запам'ятовуючого пристрою, виходу блока керування з'єднаний з входом довихід першого лічильника (молодший розряд) по зволу запису п'ятого регістра, виходи третього першому виходу блока керування з'єднаний з адлічильника по п'ятому виходу блока керування ресним входом (молодший розряд) блока операз'єднані з адресними входами другого мультиплетивної пам'яті, вихід першого лічильника (старший ксора. розряд) по першому виходу блока керування з'єд Запропонована корисна модель відноситься до галузі автоматики й обчислювальної техніки і може бути використана в системах кодування даних. Відомий "Пристрій для реалізації швидкого перетворення Хартлі" [1], який містить блок оперативної пам'яті, блок постійної пам'яті, блок керування, суматор, перемножувач, накопичуваючий суматор. Блок керування містить: генератор тактових імпульсів, тригер, два лічильника, дешифратор, одновібратор, чотири елемента І. Недоліком пристрою є те, що він обчислює дискретне перетворення Хартлі, яке має аналітичні вирази, що відрізняються від виразів для усіченого перетворення Фур'є в остаточних класах. Відомий також "Пристрій для швидкого дійсного перетворення Хартлі-Фур'є" [2], який містить блок синхронізації, два лічильника адреси, блок постійної пам'яті, вхідний регістр, регістр, вихідний регістр, блок пам'яті, два перемножувача, два комутатора, суматор-вичитач, вихідний регістр, комутатор, інформаційний вхід, інформаційний вихід. Недоліком пристрою є те, що він не виконує обчислень векторів. Найбільш близьким до запропонованого технічним рішенням, обраним як прототип, є "Пристрій для обчислення усіченого перетворення Фур'є в остаточних класах" [3], який містить блок оперативної пам'яті, перший, другий, третій та четвертий блоки постійної пам'яті, перший, другий та третій блоки, які реалізують операцію складання по модулю два, перший, другий, третій та четвертий допоміжні блоки постійної пам'яті, перший, другий, третій та четвертий регістри, блок керування, до складу якого входять генератор тактових імпульсів, тригер, лічильник, дешифратор, перший, другий, третій та четвертий елементи І. Недоліком пристрою-прототипу є те, що він обчислює усічене перетворення Фур'є в остаточних класах табличним способом. В основу корисної моделі поставлена задача створити "Пристрій для обчислення усіченого перетворення Фур'є в остаточних класах", який реалізує знаходження вихідного вектора при реалізації чотирьохточечного усіченого перетворення Фур'є в полі GF(28) математичним способом згідно (1). Поставлена задача вирішується за рахунок того, що у пристрої-прототипі усунуті другий та третій блоки, які реалізують операцію складання по модулю два, перший, другий, третій та четвертий допоміжні блоки постійної пам'яті, та додатково введені перший та другий мультиплексори, п'ятий регістр. До блока керування додатково введені другий, третій та четвертий лічильники, п'ятий елемент І, формувач фронтів, перший та другий елементи АБО, другий та третій тригери, блок постійної пам'яті. Також додатково введені нові зв'язки у всьому пристрої. Технічний результат, який може бути отриманий при використанні корисної моделі, полягає в одержанні технічного засобу для знаходження вихідного вектора при реалізації чотирьохточечного усіченого перетворення Фур'є в полі GF(28) математичним способом. На Фіг.1 приведена блок-схема запропонованого пристрою. На Фіг.2 приведена блок-схема блока керу 5 14431 6 вання запропонованого пристрою. дешифратора 26. Четвертий вихід лічильника 25 Запропонований пристрій для обчислення усі(старший розряд) з'єднаний з четвертим входом ченого перетворення Фур'є в остаточних класах дешифратора 26 (старший розряд) і другим вхомістить блок оперативної пам'яті 1, перший, друдом елемента І 27. Вихід елемента І 27 з'єднаний з гий, третій та четвертий блоки постійної пам'яті 2входом формувача фронтів 28. Вихід формувача 5, блок керування 6, перший мультиплексор 7, фронтів 28 з'єднаний з входом лічильника 24, вхоблок складання по модулю два 8, перший, другий, дом обнуління лічильника 25, входами обнуління третій та четвертий регістри 9-12, другий мультиптригерів 33 і 34. Перший вихід дешифратора 26 лексор 13, п'ятий регістр 14, вхід запуску 15, вихід з'єднаний з входом переводу тригера 33 в одини16, причому вхід запуску 15 пристрою з'єднаний з цю, другий вихід дешифратора 26 з'єднаний вховходом блока керування. Адресні входи блока дом переводу тригера 34 в одиницю, третій вихід оперативної пам'яті 1 з'єднані з виходом 17 блока дешифратора 26 з'єднаний з першим входом елекерування. Вхід дозволу читання блока оперативмента АБО 29, четвертий вихід дешифратора 26 ної пам'яті 1 з'єднаний з виходом 18 блока керуз'єднаний з другим входом елемента АБО 30 і певання. Вихід блока оперативної пам'яті 1 з'єднаний ршим входом елемента І 36, п'ятий вихід дешифз адресними входами блоків постійної пам'яті 2-5. ратора 26 з'єднаний з другим входом елемента Входи дозволу читання блоків постійної пам'яті 2-5 АБО 29, шостий вихід дешифратора 26 з'єднаний з з'єднані з виходом 18 блока керування. Вихід блотретім входом елемента АБО 30 і першим входом ка постійної пам'яті 2 з'єднаний з першим входом елемента І 37, сьомий вихід дешифратора 26 з'єдмультиплексора 7. Вихід блока постійної пам'яті 3 наний з третім входом елемента АБО 29, восьмий з'єднаний з другим входом мультиплексора 7. Вивихід дешифратора 26 з'єднаний з першим входом хід блока постійної пам'яті 4 з'єднаний з третім елемента АБО 30 і першим входом елемента І 38, входом мультиплексора 7. Вихід блока постійної дев'ятий вихід дешифратора 26 з'єднаний з четвепам'яті 5 з'єднаний з четвертим входом мультипртим входом елемента АБО 29, десятий вихід делексора 7. Адресні входи мультиплексора 7 з'єдшифратора 26 з'єднаний з четвертим входом еленані з виходом 19 блока керування. Вихід мультимента АБО 30 і першим входом елемента І 39. плексора 7 з'єднаний з другим входом блока 8, що Вихід елемента АБО 29 з'єднаний з тактовим вхореалізує операцію складання по модулю два. Видом лічильника 31. Вихід елемента АБО 30 з'єднахід блока 8, що реалізує операцію складання по ний з тактовим входом лічильника 32. Виходи лімодулю два, з'єднаний з входами даних регістрів чильника 32 з'єднані з входами постійного 9-12. Входи дозволу запису регістрів 9-12 з'єднані запам'ятовуючого пристрою 35. Вихід лічильника з виходом 20 блока керування. Вихід регістра 9 24 (молодший розряд) по виходу 17 блока керуз'єднаний з першим входом мультиплексора 13. вання 6 з'єднаний з адресним входом (молодший Вихід регістра 10 з'єднаний з другим входом мульрозряд) блока оперативної пам'яті 1. Вихід лічильтиплексора 13. Вихід регістра 11 з'єднаний з треника 24 (старший розряд) по виходу 17 блока кетім входом мультиплексора 13. Вихід регістра 12 рування 6 з'єднаний з адресним входом (старший з'єднаний з четвертим входом мультиплексора 13. розряд) блока оперативної пам'яті 1. Вихід тригера Адресні входи мультиплексора 13 з'єднані з вихо33 по виходу 18 блока керування 6 з'єднаний з дом 21 блока керування. Вихід мультиплексора 13 входом дозволу читання блока оперативної пам'яті з'єднаний з входом даних регістра 14. Вхід дозво1. Вихід тригера 34 по виходу 18 блока керування лу запису регістра 14 з'єднаний з виходом 21 бло6 з'єднаний з входами дозволу читання блоків поска керування. Вихід регістра 14 є виходом 16 притійної пам'яті 2-5. Виходи постійного запам'ятовустрою та з'єднаний з першим входом блока 8, що ючого пристрою 35 по виходу 19 блока керування реалізує операцію складання по модулю два. 6 з'єднані з адресними входами мультиплексора 7. Блок керування 6 пристрою для обчислення Вихід елемента І 36 по виходу 20 блока керування усіченого перетворення Фур'є в остаточних класах 6 з'єднаний з входом дозволу запису регістра 9. містить: генератор тактових імпульсів 22, перший Вихід елемента І 37 по виходу 20 блока керування тригер 23, перший та другий лічильники 24 і 25, 6 з'єднаний з входом дозволу запису регістра 10. дешифратор 26, перший елемент І 27, формувач Вихід елемента І 38 по виходу 20 блока керування фронтів 28, перший та другий елементи АБО 29 і 6 з'єднаний з входом дозволу запису регістра 11. 30, третій та четвертий лічильники 31 і 32, другий Вихід елемента І 39 по виходу 20 блока керування та третій тригери 33 і 34, постійний запам'ятовуюб з'єднаний з входом дозволу запису регістра 12. чий пристрій 35, другий, третій, четвертий та п'яВихід елемента АБО 29 по виходу 21 блока керутий елементи І 36-39, причому вхід 15 блока керування 6 з'єднаний з входом дозволу запису регіствання з'єднаний з входом переводу тригера 23 в ра 14. Виходи лічильника 31 по виходу 21 блока одиницю, вихід тригера 23 з'єднаний з входом гекерування 6 з'єднані з адресними входами мульнератора тактових імпульсів 22, вихід якого з'єдтиплексора 13. наний з рахунковим входом лічильника 25 та друРобота запропонованого пристрою здійснюгими входами елементів І 36-39. Вхід скидання ється за 4 цикли по 10 тактів у кожному та полягає тригера 23 з'єднаний з виходом переповнення (пев наступному. Перед початком роботи в блок опереносу) лічильника 24. Перший вихід лічильника ративної пам'яті 1 записаний вхідний вектор v={v1, 25 (молодший розряд) з'єднаний з першим входом v2, v3, v4} в двійковому коді, причому vi GF(28). дешифратора 26 (молодший розряд) і першим В блок постійної пам'яті 2 за адресою vі=0 255 входом елемента І 27. Другий вихід лічильника 25 записані результати множення в GF(28) у виді з'єднаний з другим входом дешифратора 26. Тре{P(v1 52)}, тій вихід лічильника 25 з'єднаний з третім входом де Р(Х) - перехід від десяткового представ 7 14431 8 лення елемента поля GF(28) до двійкового предвиходу елемента АБО 29 лічильник 31 збільшує ставлення. своє значення на одиницю. Двійковий код з виходу лічильника 31 через вихід 21 блока керування 6 В блок постійної пам'яті 3 за адресою vi=0 255 поступає на адресні входи мультиплексора 13 та записані результати комутує на вхід даних регістра 14 вихід регістра {P(vi 103)}. 10. В блок постійної пам'яті 4 за адресою vi=0 255 На четвертому такті формується рівень "1" на записані результати четвертому виході дешифратора 26, що з виходу {P(v1 154)}. елемента І 36 через вихід 20 блока керування 6 В блок постійної пам'яті 5 за адресою vi=0 255 записує до регістра 9 результат складання по мозаписані результати дулю 2 результату множення v1 у полі GF (28) зі {P(vi 205)}. значенням, що міститься на виході регістра 14. Регістри 9-12, регістр 14, тригер 23, лічильники Рівень "1" з четвертого виходу дешифратора 26 24, 25, 31, 32, тригери 33 і 34 у нульовому стані. поступає на елемент АБО 30. По передньому На виході дешифратора 26 під час роботи фронту імпульсу з виходу елемента АБО 30 лічипристрою формується унітарний код такту, причольник 32 збільшує своє значення на одиницю. При му рівень "1" буде тільки на одному з його виходів. цьому з виходу постійного запам'ятовуючого приПостійний запам'ятовуючий пристрій 35 місстрою 35 через вихід 19 блока керування 6 на адтить для кожного з тактів 4, 6, 8, 10 циклів 1-4 адресних входах мультиплексора 7 встановлюється реси, що використовуються для адресації мультиновий адрес і двійкове представлення результату плексора 7 з метою здіснення математичного множення з виходу відповідного блока постійної способу знаходження вихідного вектора при реаліпам'яті 2-5 через мультиплексор 7 поступає на зації чотирьохточечного усіченого перетворення другий вхід блока 8. З виходу блока 8 результат Фур'є в полі GF(28). складання по модулю 2 результату множення з По сигналу "Запуск обробки", що надходить по значенням, що міститься на виході регістра 14, входу 15 пристрою, тригер 23 встановлюється в поступає на входи даних регістрів 9-12. одиничний стан, сигнал " 1" з виходу тригера 23 На п'ятому такті формується рівень "1" на п'янадходить на вхід генератора тактових імпульсів тому виході дешифратора 26, що з виходу елеме22, що починає формувати послідовність тактових нта АБО 29 через вихід 21 блока керування 6 по імпульсів, що надходять на рахунковий вхід лічипередньому фронту імпульсу в регістр 14 через льника 25 та другі входи елементів І 36-І 39. мультиплексор 13 записує значення, що міститься Цикл 1. у регістрі 10. По задньому фронту імпульсу з вихоНа першому такті формується рівень "1" на ду елемента АБО 29 лічильник 31 збільшує своє першому виході дешифратора 26, що встановлює значення на одиницю. Двійковий код з виходу літригер 33 в одиницю. Рівень "1" з виходу тригера чильника 31 через вихід 21 блока керування 6 пос33 через вихід 18 блока керування 6 поступає на тупає на адресні входи мультиплексора 13 та ковхід дозволу читання блока оперативної пам'яті 1, мутує на вхід даних регістра 14 вихід регістра 11. на виході якого формується двійкове представНа шостому такті формується рівень "1" на лення числа v1. шостому виході дешифратора 26, що з виходу На другому такті формується рівень "1" на елемента І 37 через вихід 20 блока керування 6 другому виході дешифратора 26, що встановлює записує до регістра 10 результат складання по тригер 34 в одиницю. Рівень "1" з виходу тригера модулю 2 результату множення v1 у полі GF (28) зі 34 через вихід 18 блока керування 6 поступає на значенням, що міститься на виході регістра 14. входи дозволу читання блоків постійної пам'яті 2Рівень "1" з шостого виходу дешифратора 26 пос5. При цьому на виході блока постійної пам'яті 2 тупає на елемент АБО 30. По передньому фронту формується двійкове представлення результату імпульсу з виходу елемента АБО 30 лічильник 32 8 множення v1 52 у полі GF (2 ), на виході блока посзбільшує своє значення на одиницю. При цьому з тійної пам'яті 3 - двійкове представлення резульвиходу постійного запам'ятовуючого пристрою 35 8 тату множення v1 103 у полі GF (2 ), на виході блочерез вихід 19 блока керування 6 на адресних ка постійної пам'яті 4 - двійкове представлення входах мультиплексора 7 встановлюється новий 8 результату множення v1 154 у полі GF (2 ), на виадрес і двійкове представлення результату мноході блока постійної пам'яті 5 - двійкове представження з виходу відповідного блока постійної пам'я8 лення результату множення v1 205 у полі GF (2 ). ті 2-5 через мультиплексор 7 поступає на другий Двійкове представлення результату множення з вхід блока 8. З виходу блока 8 результат складанвиходу відповідного блока постійної пам'яті (2-5) ня по модулю 2 результату множення зі значенчерез мультиплексор 7 поступає на другий вхід ням, що міститься на виході регістра 14, поступає блока 8. З виходу блока 8 результат складання по на входи даних регістрів 9-12. модулю 2 результату множення зі значенням, що На сьомому такті формується рівень "1" на міститься на виході регістра 14, поступає на входи сьомому виході дешифратора 26, що з виходу даних регістрів 9-12. елемента АБО 29 через вихід 21 блока керування На третьому такті формується рівень "1" на 6 по передньому фронту імпульсу в регістр 14 четретьому виході дешифратора 26, що з виходу рез мультиплексор 13 записує значення, що міселемента АБО 29 через вихід 21 блока керування титься у регістрі 11. По задньому фронту імпульсу 6 по передньому фронту імпульсу в регістр 14 чез виходу елемента АБО 29 лічильник 31 збільшує рез мультиплексор 13 записує значення, що міссвоє значення на одиницю. Двійковий код з виходу титься у регістрі 9. По задньому фронту імпульсу з лічильника 31 через вихід 21 блока керування 6 9 14431 10 поступає на адресні входи мультиплексора 13 та представлення числа v2. комутує на вхід даних регістра 14 вихід регістра Цикл 2 здійснюється аналогічно циклу 1 за ви12. нятком того, що всі операції здійснюються з викоНа восьмому такті формується рівень "1" на ристанням двійкового представлення числа v2. восьмому виході дешифратора 26, що з виходу Цикл 3 здійснюється аналогічно циклу 1 за виелемента І 38 через вихід 20 блока керування 6 нятком того, що всі операції здійснюються з викозаписує до регістра 11 результат складання по ристанням двійкового представлення числа v3. модулю 2 результату множення v1 у полі GF (28) зі Цикл 4 здійснюється аналогічно циклу 1 за визначенням, що міститься на виході регістра 14. нятком того, що всі операції здійснюються з викоРівень "1" з восьмого виходу дешифратора 26 пористанням двійкового представлення числа v4. ступає на елемент АБО 30. По передньому фронту Після завершення останнього такту четвертого імпульсу з виходу елемента АБО 30 лічильник 32 циклу на виході переповнення лічильника 24 форзбільшує своє значення на одиницю. При цьому з мується рівень "І", що скидає тригер 23 у нульовий виходу постійного запам'ятовуючого пристрою 35 стан, а пристрій повертається у початковий стан, через вихід 19 блока керування 6 на адресних при цьому з виходу 16 пристрою повинний бути входах мультиплексора 7 встановлюється новий зчитаний остаточний результат. адрес і двійкове представлення результату мноУсічене перетворення Фур'є в остаточних клаження з виходу відповідного блока постійної пам'ясах визначено [4]: ті 2-5 через мультиплексор 7 поступає на другий n 1 вхід блока 8. З виходу блока 8 результат складанVj w ij i , (1) ня по модулю 2 результату множення зі значенi 1 ням, що міститься на виході регістра 14, поступає n 1 1 на входи даних регістрів 9-12. ( w ij L ) Vj , (2) i n modp На дев'ятому такті формується рівень " 1" на j 1 дев'ятому виході дешифратора 26, що з виходу де w - елемент порядку n у полі GF (qm); елемента АБО 29 через вихід 21 блока керування - операція складання у полі; 6 по передньому фронту імпульсу в регістр 14 чеL=-1. рез мультиплексор 13 записує значення, що місІснує два способу знаходження вихідного вектиться у регістрі 12. По задньому фронту імпульсу тора: з виходу елемента АБО 29 лічильник 31 встанов1. Математичний спосіб, який полягає у виколюється в 0. Двійковий код з виходу лічильника 31 нанні усіх математичних операцій згідно (1). через вихід 21 блока керування 6 поступає на ад2. Табличний спосіб, який полягає в тому, що ресні входи мультиплексора 13 та комутує на вхід строяться (n-1) таблиць, які складаються з 2m еледаних регістра 14 вихід регістра 9. ментів, розміру m (n-1) біт, а вихідний вектор На десятому такті формується рівень "1" на отримується шляхом складання елементів табдесятому виході дешифратора 26, що з виходу лиць, які відповідають точкам вхідного вектору. елемента І 39 через вихід 20 блока керування 6 Джерела інформації: записує до регістра 12 результат складання по 8 1. Деклараційний патент №58743А України, модулю 2 результату множення v1 у полі GF (2 ) зі 7МПК G06F7/04. Пристрій для реалізації швидкого значенням, що міститься на виході регістра 14. перетворення Хартлі /Дуденко С.В., Рубан І.В., Рівень "1" з десятого виходу дешифратора 26 посГолубнічий Д.Ю., Корольова Н.А. -№20021107777; тупає на елемент АБО 30. По передньому фронту Заяв. 1.10.2002, Опубл. 15.08.2003, Бюл. №8. -4с. імпульсу з виходу елемента АБО 30 лічильник 32 ил. збільшує своє значення на одиницю. При цьому з 2. А.с. 1569847 СССР, МКИ G06F15/332. Уствиходу постійного запам'ятовуючого пристрою 35 ройство для быстрого действительного преобрачерез вихід 19 блока керування 6 на адресних зования Хартли-Фур'є /С.Н. Демиденко, Э.Б. Куновходах мультиплексора 7 встановлюється новий вский, О.В. Малашонок, Е.М. Левин. -№4473106; адрес і двійкове представлення результату мноЗаяв. 10.08.88, Опубл. 7.06.90, Бюл. №21. ження з виходу відповідного блока постійної пам'я3. Деклараційний патент №4264U України, ті 2-5 через мультиплексор 7 поступає на другий 7МПК G06F7/04. Пристрій для обчислення усіченовхід блока 8. З виходу блока 8 результат складанго перетворення Фур'є в остаточних класах ня по модулю 2 результату множення зі значен/Дуденко С.В., Рубан І.В., Третяк В.Ф., Сумцов Д.В. ням, що міститься на виході регістра 14, поступає -№2004032321; Заяв. 30.03.2004, Опубл. на входи даних регістрів 9-12. По задньому фронту 17.01.2005, Бюл. №1. -4с. ил. імпульсу з виходу елемента І 27 через формувач 4. Рубан И.В., Дуденко С.В. Оптимизация теофронтів 28 здійснюється збільшення на одиницю ретико-числовых преобразований //Інформаційнолічильника 24, обнуління лічильника 25 та встанокеруючі системи на залізничному транспорті. влення в "0" тригерів 33 і 34. Двійковий код з вихо2002. -№6. -С.47-49. ду лічильника 24 через вихід 17 блока керування 6 встановлює на адресних входах блока оперативної пам'яті 1 адресу для зчитування двійкового 11 Комп’ютерна верстка Л.Литвиненко 14431 Підписне 12 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for calculating truncated fourier transform by residue arithmetic

Автори англійськоюDudenko Serhii Vasyliovych, Ruban Ihor Viktorovych, Alekseiev Sergii viktorovych, Alekseiev Serhii Viktorovych

Назва патенту російськоюУстройство для вычисления усеченного преобразования фурье с помощью арифметики в остаточных классах

Автори російськоюДуденко Сергей Васильевич, Рубан Игорь Викторович, Алексеев Сергей Викторович

МПК / Мітки

МПК: G06F 17/14, G06F 5/00

Мітки: класах, фур'є, залишкових, перетворення, пристрій, обчислення, усіченого

Код посилання

<a href="https://ua.patents.su/6-14431-pristrijj-dlya-obchislennya-usichenogo-peretvorennya-fureh-v-zalishkovikh-klasakh.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обчислення усіченого перетворення фур`є в залишкових класах</a>

Попередній патент: Спосіб ортодонтичного лікування спадкових форм патології прикусу іі класу за енглем у змінному прикусі

Наступний патент: Комбінована система автоматичного відключення електромережі при сильному вітрі

Випадковий патент: Спосіб нормалізації функціонування органів та систем організму людини цигановой к-м.м.