Пристрій для з’єднання процесорів через спільну пам’ять у багатопроцесорній системі

Номер патенту: 1619

Опубліковано: 25.10.1994

Автори: Єрзаков Євген Михайлович, Деніщенко Ігор Якович, Кравченко Тетяна Іванівна, Головін Віктор Іванович

Формула / Реферат

1. Устройство для сопряжения процессоров через общую память в многопроцессорной системо по авт. св. 1231508, отличающееся тем, что, с целью расширения функциональных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных, в него дополнительно введен блок управления режимом, причем выходы первого мультиплексора соединены с группой информационных входов блока управления режимом, вход разрешения изменения приоритетов которого соединен с выходом режима блока управления памятью, первый выход блока управления режимом соединен со входом запуска первого узла приоритета блока формирования заявок, второй выход блока управления режимом соединен с третьими входами первого и второго элементов И группы узлов запоминания заявок, выходы ненулевого состояния счетчиков заявок формирователя заявок соединены с соответствующими входами сброса группы триггеров первого узла приоритета, а выходы переполнения указанных счетчиков заявок — с установочными входами указанных групп триггеров первого узла приоритета, дополнительные выходы квитирования считывания блока ввода-вывода соединены с соответствующими входами разрешения считывания формирователя заявок, которые соединены с дополнительными входами синхронизации счетчиков заявок формирователя заявок, каждый дополнительный управляющий вход триггера соединен с соответствующим управляющим выходом формирователя заявок, а выходы «Сброс» первого узла приоритета соединены только с соответствующими выходами ненулевого состояния счетчиков заявок формирователя заявок.

2. Устройство по п.1, отличающееся тем, что блок управления режимом содержит триггер блокировки, триггер запуска, триггер запрета, дешифратор и два элемента И, причем вход типа сообщения группы информационных входов блока управления режимом соединен с синхронизирующими входами триггера запрета и триггера запуска, инверсный выход триггера запуска соединен с первым выходом блока управления режимом, прямой выход триггера запрета соединен с первыми входами первого и второго элементов И, вторые входы которых соединены со входом разрешения изменения приоритетов блока управления режимом, третьи входы первого и второго элементов И соединены с выходами признаков соответственно начала и конца массива дешифратора, выходы признаков пуска и останова дешифратора соединены с входами соответственно сброса и установки триггера запуска, выходы признаков разрешения и запрещения работы с массивами дешифратора соединены с входами соответственно установки и сброса триггера запрета, входы дешифратора соединены с входами кода операции группы информационных входов блока управления режимом, выходы первого и второго элементов И соединены с входами соответственно установки и сброса триггера блокировки, инверсный выход которого соединен с вторым выходом блока управления режимом.

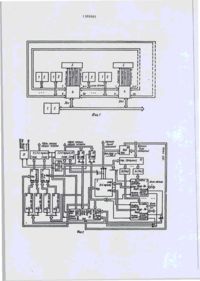

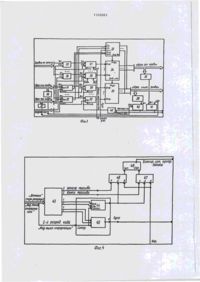

Текст

Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных : системах управления в качестве модуля обработки информации,, Целью изоб ретения является расширение функциональных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных. Для этого в микропроцессорную систему, содержащую микропроцессоры, оперативные запоминающие устройства, общие оперативные запоминающие устройства, устройства для сопряжения процессоров через общую память, дополнительно введен блок управления режимом, состоящий из дешифратора, триггера запрета, триггера запуска, первого и второго элементов И и триггера блокировки* I з.п. ф-лы, 5 ил. і (Л С СО 00 00 00 00 РПФ-К 1 1388881 Изобретение относится к вычислительной технике, может быть использовано в автоматизированных системах управления в качестве модуля обработки информации и является дополнительным к авт о св, № 1231508и Целью изобретения является расширение функциональных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных. На фиг о J изображена блок-схема многопроцессорной системы с использованием устройства для сопряжения процессоров; на фиг о 2 - структурная схема устройства для сопряжения процессоров через общую память; на фиг„3 - функциональная схема блока формирования заявок; на фиг. 4 -функциональная схема блока управления режимом; на фиг„5 - функциональная схема узла запоминания заявок. Предлагаемое устройство содержит микропроцессоры 1, один из которых центральный, местные оперативные запоминающие устройства, (ОЗУ) 2, общие оперативные запоминающие устройства 3, устройство 4 для сопряжения процессоров через общую память, содержащее первый блок 5 ввода-вывода, (2К+і)-й блок 6 ввода-вывода, первый 7, второй 8 и третий 9 мультиплексоры, демультиплексор 10, четвертый 11 и памяти 12 мультиплексоры, первый регистр 13, (2К+1)-й регистр 14, первый счетчик 15 адреса считывания, (2К+ї)~й счет•іомер получателя сообщений (№ процессора, ЭВМ) - 8 бит t o 15 20 25 ЗО 35 чик 16 адреса считывания, первый счетчик 17 адреса записи, (2К+1)-й счетчик 18 адреса записи, первый 19 и второй 20 дешифраторы, блок 21 управления памятью, блок 22 формирования заявок, первый 230 Ї и второй 23,2 элементы задержки, блок 24 управления режимомо Блок формирования заявок содержит первый триггер 25 первой группы, {2К+1)-й триггер 26 первой группы, первый узел 27 запоминания заявок, (2К+1)-й узел 28 запоминания заявок, первый триггер 29 второй группы, (2К+1)-й триггер 30 второй группы, первый счетчик 31 заявок, (2К+1)~й счетчик 32 заявок, первый 33, второй 34 и третий 35 узлы приоритета, первый 36, второй 37, третий 38, четвертый 39 и пятый 40 элементы ИЛИ, триггеры 41 и 42„ Блок управления режимом содержит дешифратор 43, триггер 44 запрета, триггер 45 запуска, первый 46 и второй 47 элементы И, триггер 48 блокировки. Узел запоминания заявок содержит первый 49 и второй 50 элементы И, триггер 51 „ Устройство функционирует следующим образомо Функционирование блока управления режимом происходит под действием сигналов, сформированных в управляющей части форматов сообщений, передаваемых по выходу "Выход сообщений" устройства в общую память 0 Формат этих сообщений следующий: Номер отправителя сообщения (№ процессора, ЭВМ) - 5 бит Самостоятельно блок управления режимом не может обеспечить непрерывное считывание сообщений из общей памяти, так как это осуществляется 50 автоматически под управлением блока формирования заявоко Задача блока управления режимом состоит в том, чтобы принять адресуемое ему сообщение (признаки "код типа информации" 55 и "данные") и проанализировать коды, содержащиеся в них.> Факт необходимости анализа признака "данные" определяется приемом кодов 010, 011,ПО, Код типа информа Данные {8 бит) ции (3 бита) 111 в признаке "код типа информации". Команда управления "Начало масива" в виде кода UIXKXXX содержится в трех первых разрядах признака "Данные11, команда управления "Конец массива" в виде кода 000ХХХХХ, команда управления "Пуск" - в виде кода П0ХХХ, а команда управления "Стоп" - в виде кода 101ХХХХ с запоминанием в триггере запуска. Устройство начинает работать после того, как на блок управления режимом поступает команда "Пуск"„ Триг 38888 li t z гк 1 2 0UZ.1 Адрес ячейка ОВЩЄО п ОП9ЇЇіи ядрес ceruttu оіїшеї) nammu Фагг 138888 гер запуска устанавливается в состояние "О" по каналу управления разрешается 1-го узла приоритета,, При поступлении команды управления с "Разрешение работы с массивами" происходит установка триггера запрета. Теперь при поступлении на вход дешифратора 43 первого элемента массива на его выходе формируется признак 10 начала массива и при наличии разрешающего сигнала работы триггер 48 блокировки устанавливается в " 1 " о На втором выходе блока управления режимом формируется сигнал 0" и происхо- 15 дит блокировка изменения приоритетов заявок путем поступления сигнала "і" на входы элементов и 49 и 50 узлов запоминания заявок блока формирования заявок20 По окончании массива дешифратор 43 вырабатывает признак окончания массива, который сбрасывает триггер 48 блокировки, и разрешается работа узлов запоминания заявок0 В резуль- 25 тате блокировка изменения приоритета на запись сообщений в общую память снимается и начинает действовать установленная ранее система приоритетов * 30 Ф о р м у л а и з о б р е т е н и я )„Устройство для сопряжения процессоров через общую память в мно- 35 гопроцессорной системе по авт. св. № 1231508, о т л и ч а ю щ е е с я тем, что, с цепью расширения функциональных возможностей за счет динамического переопределения до приоритетов процессоров при обработке одномерных и многомерных структур данных, в него дополнительно введен блок управления режимом, причем выходы первого мультиплексора соедине- 45 ны с группой информационных входов блока управления режимом, вход разрешения изменения приоритетов которого соединен с выходом режима блока управления памятью, первый выход бло- ^п ка управления режимом соединен с входом запуска первого узла приоритета блока формирования заявок, второй выход блока управления режимом соединен с третьими входами первого и _, второго элементов И группы узлов запоминания заявок, выходы ненулевого состояния счетчиков заявок формирователя заявок соединены с соответствую щими входами гбросл группы тритеров первого узла приоритета, а выходы переполнения указанных счетчиков заявок - с установочними входами указанных групп триггеров первого узла приоритета, дополнительные выходы квитирования считывания блока вводавывода соединены с соответствующими входами разрешения считывания формирователя заявок, которые соединены с дополнительными входами синхронизации счетчиков заявок формирователя заявок, каждый дополнительный управляющий вход триггера соединен с соответствующим управляющим выходом формирователя заявок, а выходы "Сброс" первого узла приоритета соединены только с соогветствующими выходами ненулевого состояния счетчиков заявок формирователя заявок„ 2 0 Устройство по п о 1 , о т л и ч а ю щ е е с я тем, что блок управления режимом содержит триггер блокировки , триггер запуска, триггер запрета, дешифратор и два элемента И, причем вход типа сообщения группы информационных входов блока управления режимом соединен с синхронизирующими входами триггера запрета и триггера запуска, инверсный выход триггера запуска соединен с первым выходом блока управления режимом, прямой выход триггера запрета соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с входом разрешения изменения приоритетов блока управления режимом, третьи входы первого- и второго элементов И соединены с выходами признаков соответственно начала и конца массива дешифратора, выходы признаков пуска и останова дешифратора соединены с входами соответственно сброса и установки триггера запуска, выходы признаков разрешения и запрещения работы с массивами дешифратора соединены с -входаї-іи соответственно установки и сброса триггера запрета, входы дешифратора соединены с входами кода операции группы информационных входов блока управления режимом, выходы первого и второго элементов И соединены с входами соответственно установки и сброса триггера блокировки, инверсный выход которого соединен с вторым выходом блока управления режимом,, I J8888 Щ *-sP £«£&* Заядги на запись УСТ 25 Sat 27 адрес 28 Cs* 26 39 сан*. Ш Сброс сш заві адрес 35 U»? w Cjpoc зап. 3

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice to connect processors through common memory in multiprocessor system

Автори англійськоюYerzakov Yevhen Mykhailovych, Holovin Viktor Ivanovych, Denischenko Ihor Yakovych, Kravchenko Tetiana Ivanivna

Назва патенту російськоюУстойство для сопряжения процессоров через общую пам'ять в многопроцессорной системе

Автори російськоюЕрзаков евгений Михайлович, Головин Виктор Иванович, Денищенко Игорь Яковлевич, Кравченко Татьяна Ивановна

МПК / Мітки

МПК: G06F 15/16, G06F 15/167

Мітки: спільну, багатопроцесорній, процесорів, пристрій, системі, з'єднання, пам'ять

Код посилання

<a href="https://ua.patents.su/6-1619-pristrijj-dlya-zehdnannya-procesoriv-cherez-spilnu-pamyat-u-bagatoprocesornijj-sistemi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для з’єднання процесорів через спільну пам’ять у багатопроцесорній системі</a>

Попередній патент: Пристрій для управління зчепленням та передачею транспортного засобу

Наступний патент: Спосіб зведення випереджаючого кріплення

Випадковий патент: Різально-метальний робочий орган