Пристрій для виправлення однократних та виявлення багатократних помилок

Номер патенту: 23944

Опубліковано: 31.08.1998

Автори: Боцюра Ірина Петрівна, Мусаєв Ікрам Мохтарамович, Фадеева Олена Григорівна

Формула / Реферат

Устройство для исправления однократных и обнаружения многократных ошибок, содержащее входной регистр, дешифратор, сумматор, блок индикации, сумматор по модулю два, выходной регистр, блок деления, отличающееся тем, что в устройство введены блок сумматоров, блок сравнения, первый и второй блоки элементов И, причем входы входного регистра и вход блока деления соединены с входной шиной, а информационные выходы входного регистра соединены с первыми входами сумматора по модулю два и со входами блока сумматоров, при этом со входами блока сумматоров соединены и проверочные выходы входного регистра, кроме того, выходы блока сумматоров соединены со входами дешифратора, выходы которого соединены с первыми входами второго блока элементов И, а выходы блока деления соединены с входами сумматора, выходы которого одновременно соединены со входами блока сравнения и со вторыми входами первого блока элементов И, причем выходы блока сравнения одновременно соединены со вторыми входами второго блока элементов И, с первыми входами первого блока элементов И и со входом разрешения приема/выдачи выходного регистра, кроме этого, выходы первого блока элементов И соединены со входами блока индикации, а выходы второго блока элементов И соединены со вторыми входами сумматора по модулю два, выходы которого соединены с первыми восемью входами выходного регистра.

Текст

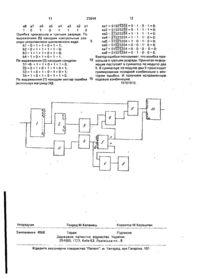

Устройство для исправления однократных и обнаружения многократных ошибок, содержащее входной регистр, дешифратор, сумматор, блок индикации, сумматор по модулю два, выходной регистр, блок деления, о т л и ч а ю щ е е с я тем, что в устройство введены блок сумматоров, блок сравнения, первый и второй блоки элементов И, причем входы входного регистра и вход блока деления соединены с входной шиной, а информационные выходы входного регистра соединены с первыми входами сумматора по модулю два и со входами блока суммато ров, при этом со входами блока сумматоров соединены и проверочные выходы входного регистра, кроме того, выходы блока сумматоров соединены со входами дешифратора, выходы которого соединены с первыми входами второго блока элементов И, а выходы блока деления соединены с входами сумматора, выходы которого одновременно соединены со входами блока сравнения и со вторыми входами первого блока элементов И, причем выходы блока сравнения одновременно соединены со вторыми входами второго блока элементов И, с первыми входами первого блока элементов И и со входом разрешения приема/выдачи выходного регистра, кроме этого, выходы первого блока элементов И соединены со входами блока индикации, а выходы второго блока элементов И соединены со вторыми входами сумматора по модулю два, выходы которого соединены с первыми восемью входами выходного регистра. Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах и системах передачи цифровой информации Известно устройство для исправления однократных и обнаружений многократных ошибок [Авт.св СССР Г 323778, кп. G 06 F Ф 11 /08,1969], содержащее регистры сдвига и сумматоры по модулю два и функционирующее на основе циклических кодов Недостаток устройства состоит в том, что оно может работать либо в режиме исправления однократных ошибок, либо в режиме обнаружения многократных ошибок. Наиболее близким по технической сущности к заявляемому является устройство для исправления одиночных и обнаружения многократных ошибок [Авт ев СССР № 1115055, кл. G 06 F 11 /10,1984], содержащее входной регистр и блок деления, информа 23944 ционные входы которых объединены и образуют информационный вход устройства, сумматор по модулю два, выход которого соединен с информационным входом выходного регистра, выходы которого являются 5 информационными выходами устройства, выход входного регистра соединен с первым входом сумматора по модулю два, распределитель импульсов, выход которого соединен с управляющими входами входного регист- 10 ра, блока деления, выходного регистра и первым входом триггера, блок обнаружения ошибок. Недостатком известного устройства является неуниверсальность, трудность проек- 15 тировзния дешифраторов для обнаружения и исправления ошибок. В основу изобретения поставлена задача создать такое устройство для исправления однократных и обнаружения 20 многократных ошибок, которое, за счет введений блока сумматоров, блока сравнения и блоков элементов И, позволило бы значительно снизить аппаратурные затраты при проектировании блоков для обнаружения 25 многократных ошибок. Поставленная задача достигается тем, что устройство для исправления однократных и обнаружения многократных ошибок содержит входной регистр, блок суммато- 30 ров, дешифратор, сумматор, блок сравнения, блоки элементов И, блок индикации, сумматор по модулю два, выходной регистр, блок деления, причем входы входного регистра и блока деления соединены с входной' 8В шиной, а информационные выходы входного регистра соединены с первыми входами сумматора по модулю два и входами блока сумматоров, при этом, со входами блока сумматоров соединены также проверочные 40 выходы входного регистра, кроме того, выходы блока сумматоров соединены со входами дешифратора, выходы которого соединены с первыми входами второго блока элементов И, а выходы блока деления 45 соединены со входами сумматора, выходы которого одновременно соединены со вторыми входами первого блока элементов И и со входами блока сравнения, выходы которого одновременно соединены со вторыми 50 входами второго блока элементов И, с первыми входами первого блока элементов И и со входом разрешения приема/выдачи выходного регистра, кроме того, выходы первого блока элементов И соединены со 55 входами блока индикации, з выходы второго блока элементов И соединены со вторыми входами сумматора по модулю два, выходы которого соединены с первыми восемью входами выходного регистра. В прототипе имеется блок обнаруженияошибок, который содержит дешифратор исправляемых ошибок, группу дешифраторов неисправляемых ошибок, элемент ИЛИ, элемент И и является громоздким, что затрудняет проектирование устройства. В заявляемом устройстве вместо этого блока введены блок сумматоров, блок сравнения и блоки элементов И, которые, в совокупности с остальными блоками, позволяют решать ту же задачу со значительно меньшими аппаратурными затратами. Кроме того, устройство предназначено для исправления однократных и обнаружения многократных ошибок с помощью укороченного циклического кода для различных образующих полиномов, что делает предлагаемое устройство универсальным. На чертеже представлена функциональная схема устройства. Устройство содержит входной регистр 1, блок сумматоров 2 (суммирование осуществляется по модулю два), дешифратор 3, сумматор 4, блок сравнения 5, блоки элементов И 6-7, блок индикации 8, сумматор по модулю два 9, выходной регистр 10, блок деления 11. Входы регистра 1 и входы блока деления 11 соединены с входной шиной. Выход Q0 входного регистра 1 соединен с первым входом сумматора по модулю два 9. Выход Q1 входного регистра 1 соединен с третьим входом сумматора по модулю два 9. Выход Q2 входного регистра 1 соединен с пятым вхоЙом сумматора по модулю два 9. Выход Q3 входного регистра 1 соединен с седьмым входом сумматора по модулю два 9. Выход Q4 входного регистра 1 соединен с девятым входом сумматора по модулю два 9. Выход Q5 входного регистра 1 соединен с одиннадцатым входом сумматора по модулю два 9. Выход Q6 входного регистра 1 соединен с тринадцатым входом сумматора по модулю два 9. Выход Q7 входного регистра 1 соединен с пятнадцатым входом сумматора по модулю два 9. Кроме того, выход Q0 входного регистра 1 соединен с первым входом первого сумматора первой группы сумматоров блока сумматоров 2 и с первым входом первого сумматора второй группы сумматоров блока сумматоров 2. Выход Q1 входного регистра 1 соединен со вторым входом первого сумматора первой группы сумматоров блока сумматоров 2, со вторым входом первого суммэтсра второй группы сумматоров блока сумматоров 2 и с первым входом первого сумматора третьей группы сумматоров блока сумматоров 2. Выход Q2 входного регистра 1 соединен со вторым входом 23944 ьторого сумматора второй группы сумматоров блока сумматоров 2 и со вторым входом первого сумматора третьей группы сумматоров блока сумматоров 2 Выход Q3 входного регистра 1 соединен со вторым входом 5 третьего сумматора второй группы сумматоров блока сумматороа 2, со вторым входом второго сумматора третьей группы сумматороа блока сумма горой 2 и с первым входом первого сумматора четвертой груп- 10 пы сумматоров блока сумматоров 2 Выход Q4 входного регистра 1 соединен со вторым входом третьего сумматора третьей , группы сумматоров блока сумматоров 2 и со вторым входом первого сумматора чет- 15 вертой группы сумматоров блока сумматоров 2. Выход Q5 входного регистра 1 соединен со вторым входом второго сумматора первой группы сумматоров блока сумматоров 2, со вторым входом четверто- 20 го сумматора третьей группы сумматоров блока сумматороа 2 и со вторым входом второго сумматора четвертой группы сумматоров блока сумматоров 2. Выход Q6 входного регистра 1 соединен со вторым входом третьего сумматора пер- 25 вой группы сумматоров блока сумматоров 2 и со вторым входом третьего сумматора четвертой группы сумматоров блока сумчатооов 2. Выход Q7 входного регистра 1 соединен со вторым вводом четвертого сумматора первой 30 группы сумматоров блока сумма? орсзв 2, со вторым входом четвертою сумматора второе І руппы сумматоров блока сумматоров 2 и со вторым входом четвертого сумматора четвертой группы сумматоров блока сумматоров 2. Выход G8 35 входного регистра 1 соединен со вторым входом пятого сумматора первой группы сумматоров блока сумматоров 2. Выход Q9 входного регистра 1 соединен со вторым входом пятого сумматора второй группы сумматоров блока 40 сумматорои 2 Выход Q10 входного регистра 1 соединен со вторым входом пятого суммітора третьей группы сумматоров блока сумматороа 2. Выход G11 входного регистра 1 соединен со вторым входом пятого сумматора четвертой 45 группы сумматоров блока суммзторов 2. При этом, выход первого сумматора первой группы сумматоров блока сумматоров 2 соединен с первым входом второго сумматора первой группы сумматоров блока сумматоров 2, выход 50 которого создинеи с первым входом третьего сумматора первой группы сумматороа блока сумматоров 2. сыход которого соединен с первым входом четвертого сумматора пераой группы сумматоров блок?сумматоров 2, выход 55 которого соединен е первым входом пятого сумматора персойгоуппы сумматоров блока с у м м а т о р о в 2. Выход первого с у м м а тора второй группы сумматоров блока сумматоров 2 соединен с первым входом второго сумматора второй группы сумматоров блока сумматоров 2, выход которого соединен с пераым входом третьего сумматора второй группы сумматоров блока сумматоров 2 пыход которого соединен с первым входом четвертого сумматора второй группы сумматоров блока сумматоров 2, выход которого соединен с первым входом пятого сумматора второй группы сумматоров блока сумматоров 2. Выход первого сумматора третьей группы сумматоров блогт сумматоров 2 соединен с первым входом второго сумматора третьей группы сумм а т о р о в блока сумматоров 2, выход которого соединен с первым входом третьего сумматора третьей группы сумматоров блока сумматоров 2, выход которого соединен с первым входом четвертого сумматора третьей группы сумматоров блока сумматоров 2, выход которого соединен с первым входом пятого сумматора третьей группы сумматоров блока сумматоров 2 Выход первого сумматора четвертой группы сумматоров блока сумматоров 2 соединен с первым входом второго сумматора четвертой группы сумматоров блока сумматоров 2, выход которого соединен с первым входом третьего сумматора четвертой группы сумматоров блока сумматоров 2, выкод которого соединен с ПРОВЫМ входом четвертого сумматора четвертое группы сумматоров блока сумматоров 2, выход которого соединен с первым входом пятого сумматира четвертое группы сумматоров блока сумматоров 2. Прямые и инверсные выходы блока сумматоров 2 соединены с входами дешифратора 3 согласно выражений (1): eai = SiS2S3S4, о з 5 - S1S2SCS4, SiS2S3S4; еаб-S1S2S3S4; ea?~ S1S2S3S4; = S1S?S3S4 еав - S1S2S3S4. Первый выход дешифратора 3 соединен с первым ехоцом блої'а элементов \Л 7. Второй выход дешифратора 3 соединен с третьим входом блока элементов И 7. Третий выход дешифратооа 3 соединен с пятым входом блока элементов И 7 Четвертый выход дешифратора 3 срединой с седьмым входом блока элементов И 7. Пятый выход дешифратора 3 соединен с девятым входом блока элементов И 7 Шестой выход дешифратора 3 соединен с одиннадцатым аходом блока элементов сі 7 Седьмой вы/од дешифратора 3 соединен с тринадцатым входом блока элементов И 7 Восьмой выход дешифратора 3 соединен с пятнадцаї ым входом блока элементов И 7. Первый выход блока деления 11 23944 соединен с первым входом сумматора 4. Второй выход блока деления 11 соединен со вторым входом сумматора 4 Третий выход блока деления 11 соединен с третьим входом сумматора 4. Четвертый выход блока деления 11 соединен с четвертым входом сумматора 4. Первый выход сумматора 4 соединен с четвертым входом блока сравнения 5 и со вторым входом блока элементов И 6. Второй выход сумматора 4 соединен с шеетым входом блока сравнения 5 и с четвертым входом блока элементов И 6 Третий выход сумматора 4 соединен с восьмым входом блока сравнения 5 и с шестым входом блока элементов И 6. Первый выход блока сравнения 5 соединен со вторым, четвертым, шестым, восьмым, десятым, двенадцатым, четырнадцатым, шестнадцатым входами блока элементов И 7 и со входом RS разрешения приема/выдачи в ы х о д н о г о р е г и с т р а 10. Второй выход блока сравнения 5 соединен с первым, третьим и пятым входами блока элементов И 6. Первый выход блока элементов И 6 соединен с первым входом блока индикации 8. Второй выход блока элементов И 6 соединен со вторым входом блока индикации 8. Третий выход блока элементов И 6 соединен с третьим входом біокз индикации 8. Первый выход блока элементов И 7 соединен со вторым входом сумматора по модулю два 9. Второй выход блока элементов И 7 соединен с четвертым входом сумматора по модулю два 9. Третий выход блока элементов И 7 соединен с шестым входом сумматора по модулю два 9. Четвертый выход блока элементов И 7 соединен с восьмым входом сумматора по модулю два 9. Пятый выход блока элементов И 7 соединен с десятым входом сумматора по модулю два 9. Шестой выход блока элементов И 7 соедийен с двенадцатым входом сумматора по модулю двз 9. Седьмой выход блока элементов И 7 соединен с четырнадцатым входом сумматора по модулю два 9. Восьмой выход блока элементов И 7 соединен с шестнадцатым входом сумматора по модулю два 9, Первый выход сумматора по модулю дпа 9 соединен с первым входом выходного регистра 10. Второй выход сумматора по модулю два 9 соединен со вторым входам выходного ре~ гистра 10. Третий выход сумматора по модулю два 9 соединен с третьим входом выходного регистра 10. Четвертый выход сумматора по модулю два 9 соединен с четвертым входом выходного регистра 10. Пятый выход сумматора по модул ю два Э соединен с пятым входом выходного регистра 10. Шестой выход сумматора по модулю два 9 соединен с шестым входом выходного регистра 1D. Седьмой выход сумматора по модулю гЛва 9 соединен с 5 10 15 20 25 30 35 40 8 седьмым входом выходного регистра 10. Восьмой выход сумматора по модулю два 9 соединен с восьмым входом выходного регистра 10. Устройство работает следующим образом, На входы входного регистра 1 последовательно поступает двенадцатиразрядная кодовая комбинация с входной шины. С выходов входного регистра 1 восемь информационных символов (а1, . ,э8) поступают на первые входы сумматора по модулю два 9. На вход первого сумматора блока сумматоров 2, который вычисляет первый разряд синдрома S1, поступают следующие символы: а1, а2, аб, а7, а8 и Ы . На вход второго сумматора блока сумматоров 2, который вычисляет второй разряд синдрома S2. поступают следующие символы: а1, з2, аЗ, а4, а8 и Ь2 На вход третьего сумматора блока сумматоров 2, который вычисляет третий разряд синдрома S3, поступают такие символы: а2, эЗ, а4, а5, аб и ЬЗ, На вход четвертого сумматора блока сумматоров 2, который вычисляет четвертый разряд синхрома S4, поступают символы: а4, а5, аб, а7, а8 и Ь4. На выходах блока сумматоров 2 будем иметь синдром ошибки S1S2S3S4, который поступает на входы дешифратора 3. Дешифратор 3 определяет вектор ошибки по выражениям (1). Полученный вектор ошибки Єз1еа2еа3еа4еа5еа6ез7еа8 поступает на первые входы блока элементов И 7. Входной код с входной шины поступает также на входы блока деления 11, в котором происходит деление кодовой комбинации на полином (2): (2) В результате этого деления получаем остаток, количество единиц в котором свидетельствует о кратности возникшей ошибки. На основании имеющегося остатка, пол45 ученного с выходов блока деления 11, сумматор А определяет вес о с т а т к а в информации при передаче. Результат суммирования в сумматоре 4 поступает одновременно на первые входы блока сравнения 50 5 (отметим что иа вторые входы блока сравнения 5 подзется кодовая комбинация, соответствующая единице) и на вторые входы блока элементов И 6. В блоке сравнения 5 определяется: количество единиц з остатке 55 больше или меньше 1. С выхода "меньше равно" блока сравнения 5 сигнал, свидетельствующий о том, что ошибок нет или произошла одна ошибка, поступает на вторые входы блока элементов И 7 и на вход RS разрешения приема/выдачи выходного ре 10 23944 гмгл^м 10. С выходов блока элементов И 7 вектор ошибки поступает на вторые входы сумматора по модулю два 9. В сумматоре по модулю два 9 происходит исправление одной возникшей ошибки. 5 Результат суммирования в сумматоре по модулю два 9 поступает на входы выходного регистра 10. С выходов выходного регистра 10 снимается исправленная комбинация. С выхода "больше" блока сравнения 5 сигнал, 10 свидетельствующий о том, что произошло больше одной ошибки, поступает на первые входы блока элементов И 6. С выходов блока элементов И 6 кодовая комбинация поступает в блок индикации 8, в котором отобража- 15 ется количество возникших ошибок. При возникновении многократных ошибок выходной регистр 10 не принимает и не выдает никакой информации, так как на выходе "меньше - равно" блока сумматоров 2 уро- 20 вень сигнэяэ соответствует нулю. Рассмотрим примеры работы устройства: 1. Случай приема информации без ошибок. 25 Во входном регистре 1 происходит запись двенадцатисимвольной последовательности по сигналу, поступающему на управляющий вход входного регистра 1. После записи двенадцатого символа происхо- 30 дит считывание из входного регистра 1 восьми информационных символов, которые проходят череасумматор по модулю два 9 без изменений, так как сигнал исправляемой ошибки не вырабатывается дешифрато- 35 ром 3 (т.е. на всех выходах дешифратора 3 уровень сигнала соответствует нулю). При этом, в выходной регистр 10 записываются по управляющему сигналу информационные символы принятой кодовой комбинаций. С 40 выхода выходного регистра 10 имеем достоверно принятую информацию. 2. Случай возникновения одиночной ошибки. В случае, если произошла одиночная 45 ошибка, выходная кодопая комбинация из входного регистра 1 поступает в блок сумма торов 2, в котором вычисляется синдром, реализующий уравнение (3) S1 =а1 + а2 + а6 + а7 + а8 + Ы; S2-a1 +a2-+ a3 + a4-t-a8 4 b2; 53 * а2 4 аЗ + аА + а5 + аб + ЬЗ; 54 *- э4 л а5 + аб 4 а7 + а8 4 Ь4. Входной код с входной шины поступает з блок деления 11, где происходит деление кода на полином (2). На основании полученного из блока деления 11 остатка & сумматоре 4 определяется ,вес остатка, соответствующий количеству ошибок, котооые произошли при передаче информации. Если ошибка одна или меньше, то с выхода "меньше - равно" блока сравнения 5 высокий уровень сигнала, который разрешает запись вектора ошибки с выходов дешифратора 3 (вектор ошибки вычисляется по уравнениям [Y)) поступает на вторые входы сумматора подмодулю два 9 через блок элементов И 7. В сумматоре по модулю два 9 происходит исправление одмокраіньїх ошибок. С выходов сумматора по модулю два 9 исправленная кодовая комбинация поступает в выходной регистр 10. . 3. Случай возникновения многократной ошибки. В случае возникновения многократной ошибки на выходе сумматора 4 получим код, который соответствует числу 2 (или больше). Выходная информация из сумматора 4 одновремен»») поступает в блок сравнения 5 и в блок элементов И о Высокий сигнал с выхода "больше" блока сравнения 5, свидетельствующий о том, что ошибок больше одной, разрешает прохождение информации из сумматора 4 а блок индикации 8, где отображается количество ошибок в передаваемой информации. Следовательно, с выхода "меньше - равно" блока сравнения 5 низкий уровень сигнала запрещает запись кодовой комбинации в выходной регистр 10. Рассмотрим на примере, как формируется укороченный циклический коди как осуществляется исправление однократных ошибок, і (4): Проверочная матрица кода имеет вид а1 Н= 12,8 а2 аЗ a4 a5 аб а7 з8 1 1 0 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 1 0 1 1 1 0 0 1 г 1 О С 1 1 Кодирующее устройство реализует еле дующие уравнения для вычисления проверочных символов (5). Ы =а1 4- э2< а6 + а7 * а8; (5) а4 + з8; (3) Ы 1 0 О Ь2 О 1 О ЬЗ О О 1 Ь4: О О О :51 : S2 (4) : S3 : 0 0 0 1 : S4 ЬЗ - а2 + аЗ * а4 4 &5 + аб; - а Ь4 = э4 а5 І аб 4- о7 + э8 } Например, если имеется исходная кодо вая комбинация: 11 23944 a8 a7 аб a5 a4 аЗ а2 a1 1 0 1 0 1 1 1 0 Ошибка произошла в третьем разряде. По выражениям (5) находим контрольные разряды укороченного циклического кода: Ы =0 + 1 + 1 + 0 + 1 - 1 ; Ь2 = 0 + 1 + 1 + 1 + 1 = 0 ; ЬЗ - 1 + 1 + 1 + 0 + 1 = 0; Ь 4 - 1 + 0 + 1 + 0 + 1 = 1. По выражениям (3) находим синдром: 51 -0- + 1 + 1 + 0 + 1 + 1 = 0 ; 52 = 0 + 1 + 0 + 1 + 1 + 0 = 1; 53 = 1 + 0 + 1 + 0 + 1 + 0 = 1; 54 = 1 + 0 + 1 + 0 + 1 + 1 = 0 . По выражениям (1) находим вектор ошибки (используя матрицу (4J): Упорядник Замовлення 4566 12 ea1=S1S2S3S4 = 0 • 1 - 0 1 = 0 ; 1—0; 1-0; еа4 = S±S2S3S4 = 1 0-0; еа5 = S1S2S3S4 = 1 • 0 = 0; еаб = S1S2S3S4 « 0 0 = 0; 0 = 0; 0 = 0. = S1S2S3S4 = Вектор ошибки показывает, что ошибка произошла в третьем разряде. Принятая информация поступает в сумматор по модулю два 9. В сумматоре по модулю два 9 происходит суммирование исходной комбинации с вектором ошибки. И получаем исправленную кодовую комбинацию 10101010. Техред М.Келемеш Коректор М.Керецман Тираж Підписне Державне патентне відомство України, 254655, ГСП. Київ-53, Львівська пл.. 8 Відкрите акціонерне товариство "Патент", м. Ужгород, вул.Гагаріна, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for correcting single errors and detecting repeated errors

Автори англійськоюMusaiev Ikram Mokhtaramovych, Botsiura Iryna Petrivna, Fadieeva Olena Hryhorivna

Назва патенту російськоюУстройство для исправления однократных ошибок и обнаружения многократных ошибок

Автори російськоюМусаев Икрам Мохтарамович, Боцюра Ирина Петровна, Фадеева Елена Григорьевна

МПК / Мітки

МПК: G06F 11/08, G06F 7/498

Мітки: виправлення, помилок, пристрій, однократних, виявлення, багатократних

Код посилання

<a href="https://ua.patents.su/6-23944-pristrijj-dlya-vipravlennya-odnokratnikh-ta-viyavlennya-bagatokratnikh-pomilok.html" target="_blank" rel="follow" title="База патентів України">Пристрій для виправлення однократних та виявлення багатократних помилок</a>

Попередній патент: Індукційний пристрій

Наступний патент: Насос

Випадковий патент: Механізм товароприйому круглов'язальної машини