Блок сортувальної мережі

Текст

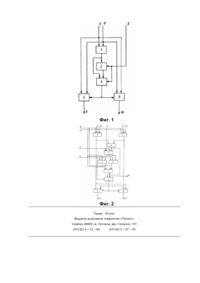

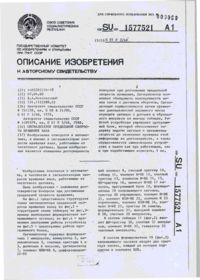

Изобретение относится к вычислительной технике и предназначено для построения на его основе сетей сортировки и коммутации данных. Выполним анализ известных те хнических решений на предмет выявления аналогов, содержащи х признаки, отличающие заявленное решение от прототипа. Известны блоки сортировочной сети [Кнут Д. Искусство программирования для ЭВМ, т. 3. Сортировка и поиск. – М.: Мир, 1978, с. 295–294], содержащие два вхо да, два выхода и компараторный модуль. Эти признаки являются общи ми с заявляемым блоком. Причинами, мешающими достижению поставленной задачи, являются следующие: отсутствие элементов и вхо дов для приема, хранения и выдачи дополнительных управляющи х сигналов программируемого характера. Эти же причины не позволяют уменьшить число элементов при построении сети сортировки, что, в свою очередь, затрудняет техническую реализацию сети сортировки при больши х n (где n – число сортируемых чисел). Известна ячейка комбинационной матрицы [Вышенчук И.М., Черкасский Н.В. Алгоритмические операционные устройства и супер ЭВМ. – К.: Те хника, 1990, с. 128–130, рис. 3, 43 (г)], со держащая схе му сравнения двух многоразрядных чисел, два эле мента И–ИЛИ, коммутируемые сигналом несравнения, два вхо да и два выхо да. Общими признаками являются: наличие схе мы сравнения двух многоразрядных чисел, два элемента И–ИЛИ, два входа и два выхо да. Такая ячейка может быть использована для построения сети сорти ровки [с. 129, рис. 3.43(в)], реализующей четно-нечетную сортировку по методу "кирпичной кладки". Причина невозможности решить поставленную задачу кроется в том, что ячейка не имеет элементов памяти и соответствующей системы связей этих эле ментов; поэтому значительно ограничена длина n сортируемых массивов чи сел и затруднена реализация устройства на одном кристалле БИС, особенно при больши х n. Известно устройство для сортировки чисел [А.с. 1659998 СССР, МКИ 5 G 06 F 7/08. Опубл. 30.06.91, Бюл. №24], содержащее m ячеек сравнения (m – количество сортируемых чисел), каждая из которых содержит регистр, два коммутато ра, элемент сравнения, что является общим признаком со схемой заявляемого блока сортировочной сети. Причиной невозможности решить поставленную задачу является иная организация системы связей внутри ячеек сравнения, так как этот аналог ограничен решением только задачи повышения быстродействия. Тогда как такая часть задачи заявляемого устройства как запоминание путей доступа к числовым кодам объектов с использованием ячейки аналога и схе мы, в состав которой она входит, решена быть не может. В то же время заявляемый блок сортировочной сети может быть использован и для реше ния задачи, решаемой схемой рассматриваемого аналога. Известно устpойство для сортировки [А.с. 1397900 СССР, МКИ 4 G 06 F 7/08. Опубл. 23.05.88, Бюл. №19], содержащее m ячеек анализа, где m – количество чисел в выходном массиве. Каждая ячейка (элемент) содержит приемный регистр, блок сравнения, регистр результата и коммутатор. Повыше ние быстродействия при сортировке нескольких массивов чисел дости гается введением в каждую ячейку (блок) дополнительно первого и второго триггеров. Большие по величине числа перемещаются через ячейки без задержки, в отличие от меньших, вынужденных пройти больший путь, перезаписываясь дополнительно из приемных регистров в регистры результата. Что касается повыше ния быстродействия при сортировке нескольких массивов чи сел (задача авторов), то это достигается совмещением начала сортировки одного массива с началом загрузки в регистры нового массива (как в буфер), при этом возможность перемешивания чисел из разных массивов блокируется сигналами с введенных ячейку триггеров. Недостаток устройства – большое количество регистров, затрудняющее микроэлектронное исполнение. Общи ми признаками являются: элемент сравнения, коммутатор, триггеры управления, информационный вход и выход окончания сорти ровки массива. Причина, мешающая решить поставленную задачу, заключена в ограничениях в организации системы связей для сорти ровки нескольких массивов (один после другого), улучшающей конвейерное выполнение, однако исключающей решение иной задачи, а именно: решаемой заявляемым блоком сорти ровочной сети. Известно также устройство для сортировки чисел [А. с. 1223222 СССР, МКИ 4 G 06 F 7/08. Оп убл. 07.04.86, Бюл. №13], содержащее блоки сортировки, каждый из которых со держит группу регистров, счетчик, сдвиговый регистр, эле мент 2И–ИЛИ, элемент И, триггер, мультиплексор. Для повышения быстродействия в каждый блок сортировки дополнительно введена группа изрегистров, элементов 2И–ИЛИ, триггер, два счетчика, два элемента И, элемент ИЛИ, сдвиговый регистр и муль типлексор. При помощи та ких блоков устройство вы полняет сортировку чисел мето дом слияния, кото рый заключается в получении упорядочения списка из двух упо рядоченных списков меньшей длины. Для нашего анализа в данном случае важно, что в каждый блок рассматриваемого устройства вхо дили элемент 2И–ИЛИ, И, триггеp, мультиплексор, и для достижения своей цели авторы, помимо прочего, вве ли груп пу из элементов 2И–ИЛИ, триггер, два элемента И, эле мент ИЛИ и мультиплексор. Общими признаками являются: эле менты 2И–ИЛИ, триггер. Причина невозможности решить поставленную задачу заключена в том, что, хотя описанное устройство ориентировано на большое число БИС, но при значительных аппаратур ных затратах его авторы не предусмотрели возможности свертки громоздкой схемы и, следовательно, ее компактного размеще ния на БИС для последующего микроэлектронного исполнения. Наиболее близким по технической сущности к заявляемому блоку является элемент сортировочной сети [А.с. 1603367 СССР, МКИ 5 G 06 F 7/06. А.А. Мельник и В.С. Илькив, Опубл. 30.10.90, Бюл. №40], содержащий блок сравнения и два коммутатора, причем первый информационный вход эле мента соединен с первым входом блока сравнения и первыми информационными входами первого и второго коммута торов, вто рой информационный вход элемента соединен с вторым входом блока сравнения и вторыми информационными входами первого и второго коммутаторов, уп равляющие вхо ды первого и второго коммутаторов объединены, а выхо ды являются первыми и вторыми выхо дами элемента, отличающий ся тем, что, с целью расши рения функциональных возможностей за счет возможности коммутации входных сигналов, в него введены триггер и третий коммутатор, причем информационный вход первого триггера соединен с выходом блока сравнения и первым информационным входом третьего коммутатора, а его синхровход – с входом задания режима элемента и управляющим входом третьего коммута тора, выход первого триггера соединен с вторым информационным входом третьего коммутатора, выход которого соединен с управляющими входами первого и второго коммута торов. На чертеже элемента – прототипа (фиг.1) использована следующая цифровая нумерация его структурных компонент: элемент (блок) 1 сравнения, первый триггер 2, первый, второй и третий коммутаторы 3, 4 и 5, первый и второй информационные входы 6,7, второй вход 8 задания режима, первый и второй информационные выхо ды 9 и 10. Общи ми признаками являются: элемент сравнения, первый вход которого объединен с первым информационным входом второго коммутато ра и вторым информационным входом третьего коммутатора, вто рой вход элемента сравнения объединен с первым инфор мационным входом третьего коммутатора и со вторым информационным входом второго коммутатора, выход которого является первым выхо дом блока, выход эле мента сравнения соединен с первым информационным входом первого коммута тора, управляющий вход которого объединен с первым управляющим вхо дом первого триггера и соединен со вторым вхо дом задания режима блока, уп равляющий вход третьего коммута тора объединен с управляющим входом второго коммутатора, а выход является вторым выхо дом блока. Схема прототи па (фиг.1) имеет ту особенность, что в процессе ее работы первый триггер 2 (в режиме коммутации) устанавливается в единичное состояние только один раз. Следовательно, использование этого же элемента при смене направления процесса сортировки в сети, исключено. Поэтому причина невозможности решить поставленную задачу свя зана с тем, что у эле мента – прото типа ограничено количество элементов памяти и логических элементов, не позволяющие выполнять сортировку чисел в двух направлениях, а также уменьшить за счет это го длину сорти ровочной сети. В основу изобретения поставлена задача создать такой блок сортировочной сети, в котором введение новых эле ментов и свя зей позволило бы выполнять сортировку и коммутацию с изменяемым направлением поступ ления чисел исходного массива на сорти ровочную сеть, и за счет этого расширить функциональные возможности блока сорти ровочной сети. Поставленная задача решается тем, что блок сортировочной сети, содержащий элемент сравнения, первый вход которого объединен с первым информационным входом второго коммута тора и вторым информационным входом третьего коммутатора, второй вход элемента сравнения объединен с первым информационным входом третьего коммутатора со вто рым информационным входом второго коммутатора, выход которого является первым выхо дом блока, выход элемента сравнения соединен с первым информационным входом первого коммута тора, управляющий вход которого объединен с первым управляющим вхо дом перво го тригге ра и соединен со вторым входом задания режима блока, управляющий вход третьего коммутатора объединен с уп равляющим входом второго коммута тора, а выход является вторым выходом блока, введены четыре элемента 2И–ИЛИ, при этом первый управляющий вход у третьего из них является инверсным, и второй триггер, причем, первый и второй информационные входы первого элемента 2И–ИЛИ являются соответственно первым и вторым входами блока, а выход соединен с первым информационным вхо дом второго коммутатора, вто рым информационным входом третьего коммутатора и первым вхо дом элемента сравнения, выход которого соединен со вторым информационным входом третьего элемента 2И–ИЛИ, первый инфор мационный вход третьего элемента 2И–ИЛИ является третьим входом блока, а первый управляющий (инверсный) вход объединен со вторым управляющим вхо дом и соединен с первым входом задания режима блока, первый и второй информационные входы второго элемента 2И– ИЛИ являются соответственно четвертым и пятым вхо дами блока, а выход соединен со вторым входом элемента сорти ровки, первым информационным входом третьего коммутатора и вто рым информационным вхо дом второго коммута тора, информационный вход второго триггера объединен с информационным входом перво го триггера и соединен с выходом третьего элемента 2И–ИЛИ, а первый управляющий вход соединен со вторым вхо дом задания режима блока, первый и второй информационные входы четвертого элемента 2И–ИЛИ соединены соответственно с выхо дом первого триггера и с выходом второго триггера, а выход соединен со вторым информационным входом первого коммутатора и является третьим выхо дом блока, первый уп равляющий вход первого элемента 2И–ИЛИ объединен с первым управляющим входом второго эле мента 2И–ИЛИ, вторым управляющим входом перво го триггера, вто рым управляющим вхо дом четвертого элемента 2И–ИЛИ и соединен с входом выбора прямого направления блока, а его вто рой управляющий вход объединен со вторым управляющим входом второго элемента 2И–ИЛИ, вторым управляющим вхо дом второго тригге ра, первым управляющим входом четвертого элемента 2И–ИЛИ и соединен с вхо дом выбора обратного направления блока. Общие признаки с прототи пом: элемент сравнения, первый вход которого объединен с первым информационным входом второго коммутато ра и вторым информационным входом третьего коммутатора, вто рой вход элемента сравнения объединен с первым инфор мационным входом третьего коммутатора и со вторым информационным входом второго коммутатора, выход которого является первым выхо дом блока, выход эле мента сравнения соединен с первым информационным входом первого коммута тора, управляющий вход которого объединен с первым управляющим вхо дом первого триггера и соединен со вторым вхо дом задания режима блока, уп равляющий вход третьего коммута тора объединен с управляющим входом второго коммутатора, а выход является вторым выхо дом блока. Отличительные признаки от прототи па: в него вве дены четыре элемента 2И–ИЛИ, при этом первый уп равляющий вход у третьего из них является инверсным, и второй триггер, причем, первый и второй информационные входы первого эле мента 2И–ИЛИ являются соответственно первым и вторым входами блока, а выход соединен с первым инфор мационным входом второго коммутатора, вторым информационным вхо дом третьего коммутатора и первым входом элемента сравнения, выход которого соединен со вторым инфор мационным входом третьего элемента 2И–ИЛИ, первый инфор мационный вход третьего элемента 2И–ИЛИ является третьим входом блока, а первый уп равляющий (инверсный) вход объединен со вторым уп равляющим вхо дом и соединен с первым вхо дом задания режима блока, первый и вто рой информационные входы вто рого элемента 2И–ИЛИ являются соответственно четвертым и пятым вхо дами блока, а выход соединен со вторым вхо дом элемента сортировки, первым информационным входом третьего коммутатора и вто рым информационным входом второго коммутато ра, информационный вход второго триггера объединен с информационным входом первого триггера и соединен с выхо дом третьего элемента 2И– ИЛИ, а первый управляющий вход соединен со вторым вхо дом задания режима блока, первый и вто рой информационные входы четверто го элемента 2И–ИЛИ соединены соответственно с выхо дом первого триггера и с выхо дом второго триггера, а выход соединен со вторым инфор мационным входом первого коммутатора и является третьим выхо дом блока, первый управляющий вход первого элемента 2И–ИЛИ объединен с первым управляющим вхо дом второго элемента 2И–ИЛИ, вторым управляющим вхо дом первого триггера, вторым управляющим вхо дом четвертого элемента 2И–ИЛИ и соединен с входом выбора прямого направления блока, а его второй управляющий вход объединен со вторым управляющим вхо дом второго элемента 2И–ИЛИ, вторым управляющим вхо дом второго триггера, первым управляющим входом четвертого элемента 2И–ИЛИ и соединен с вхо дом выбора обратного направления блока. Благодаря введению в блок сорти ровочной сети таких существенных отличительных признаков, является возможность решения поставленной технической задачи. Поскольку на элемент поступают две разные пары чисел, то комбинационные логические элементы "И–ИЛИ" управляют их перемеще нием внутри элемента. При этом элемент сортировки используется для сравнения каждой пары чисел, то есть используется дважды, а каждый триггер фиксирует (при наличии соответствующе го управляюще го сигнала) результат сравнения одной конкретной пары. Исключение влияния эффекта гонок обеспечивается работой триггеров (первого и второго) в противофа зе (это проявляется в том случае, если необхо димо переписать информацию из одного из этих триггеров в другой, или со сдвигом на пол-такта сорти ровать два разных массива чисел (один в прямом, другой – в обратном направлении), используя при этом одни и те же элементы сравнения и коммутаторы. Данное изобретение обеспечивает также и другие виды технического результата, а именно: 1) Устройство содержит средства, реализующие меха низм свертки сетей сортировки. Это новое свойство особенно значимо при интегральном микроэлектронном исполнении сетей сорти ровки. 2) Открывается возможность программируемости сети сортировки, то есть аппаратно – программной реализации сетей сортировки. Это свойство также является новым. 3) Запоминать пути доступа к числовым кодам объектов. Та кое новое свойство особенно актуально при хранении в памяти динамических сложных объектов, имеющих числовую кодировку. 4) Можно сортировать два массива: один – в прямом направлении, другой – в обратном. Все структурные компоненты блока сортировочной сети строятся на стандартных функциональных элемента х. В качестве возможной реализации триггеров могут быть использованы RS-триггеры. На фиг. 1 изображена схема прототипа, на фиг. 2 – схе ма заявляемого блока сортировочной сети. Заявляемый блок сортировочной сети (фиг.2) содержит первый элемент 2И–ИЛИ 1, второй элемент 2И–ИЛИ 2, элемент 3 сравнения, третий элемент 2И–ИЛИ 4, первый управляющий вход кото рого является инверсным, первый триггер 5, вто рой триггер 6, четвертый элемент 2И–ИЛИ 7, первый коммута тор 8, второй коммутатор 9, третий коммутатор 10, причем первый и второй информационные входы первого элемента 2И–ИЛИ 1 являются соответственно первым и вторым выхо дами 11, 12 блока, а его выход соединен с первым входом элемента 3 сравнения, вторым информационным входом третьего коммута тора 10 и первым информационным входом второго коммутатора 9, выход которого является первым выхо дом 21 блока, первый и вто рой информационные входы вто рого элемента 2И–ИЛИ 2 является соответственно четвертым и пятым вхо дами 14, 15 блока, а выход соединен со вторым вхо дом элемента 3 сравнения, вторым инфор мационным входом второго коммутатора 9, первым инфор мационным входом третьего коммутатора 10, выход которого является вторым выхо дом 22 блока, выход элемента 3 сравнения соединен со вторым инфор мационным входом третьего элемента 2И–ИЛИ 4 и с первым инфор мационным вхо дом первого коммутато ра 8, выход которого соединен с управляющи ми входами второго и третьего коммутаторов 9, 10, первый инфор мационный вход третьего элемента 2И–ИЛИ 4 является третьим входом 13 блока, а его первый уп равляющий инверсный вход и вто рой управляющий вход объединены и соединены с первым вхо дом 18 задания режима блока, информационный вход первого триггера 5 объединен с информационным входом второго триггера 6 и соединен с выхо дом третьего элемента 2И–ИЛИ 4, а вы ход соединен с первым инфор мационным входом четвертого коммута тора 7, выход кото рого соединен со вторым информационным входом первого коммутатора 8 и является третьим выхо дом 20 блока, первый управляющий вход второго триггера 6 объединен с первым управляющим входом первого триггера 5, управляющим вхо дом первого коммутатора 8 и соединен со вторым входом 19 задания режима блока, а выход соединен со вторым инфор мационным входом четвертого элемента 2И–ИЛИ 7, второй управляющий вход которого объединен со вторым управляющим вхо дом первого триггера 5, первым управляющим входом первого элемента 2И– ИЛИ 1, первым управляющим вхо дом второго элемента 2И–ИЛИ 2 и соединен с вхо дом 16 выбора прямого направления блока, первый управляющий вход четвертого элемента 2И–ИЛИ объединен со вторым управ ляющим вхо дом второго триггера 6, вто рым управляющим входом первого элемента 2И–ИЛИ, вто рым управляющим вхо дом второго элемента 2И–ИЛИ 2 и соединен с входом 17 выбора обратного направления блока. Третий инфор мационный вход 13 и третий инфор мационный выход 20 блока сорти ровочной сети – одноразрядные, первый, вто рой, четвертый, пятый информационные входы 11, 12, 14, 15 и первый и второй инфор мационные выхо ды 21, 22 – много разрядные; их разрядность соответствует разрядности сортируемых чи сел. Первый вход третьего элемента 2И–ИЛИ 4 является инверсным. Выходы третьего и четвертого элементов 2И–ИЛИ 4, 7 – одноразрядные, выхо ды первого и вто рого элементов 2И–ИЛИ 1, 2 – многоразрядные; их разрядность соответствуе т разрядности сортируе мых чисел. Блок сорти ровочной сети предназначен для построения на его основе различных сетей сортировки. Поэтому он может работать в тре х режимах: сортировки, коммутации и с переменным направлением сортировки. В режиме сортировки блок сортировочной сети используется в качестве комбинационной схемы, сравнивающей два числа, и, в зависимости от результата этого сравнения, большее число подается на первый информационный выход 21, а меньшее – на вто рой информационный выход 22. В режиме коммутации блок сортировочной сети в зави симости от значений первых двух сравниваемых чисел настраивается на коммутацию прямо (если на первый или четвертый информационные входы 11, 14 подаются большие числа), или коммутацию накрест, если большие числа подаются на вторые или пятые информационные входы 12, 15. После этого коммутация фиксируется и, в дальнейшем, вне зависимости от значений чисел, поступающи х на входы блока сорти ровочной сети, производится их транзитная пересылка в соответствии с фиксированным направлением коммутации. В режиме с переменным направлением сортировки блок сортировочной сети может работать в двух вариантах. В первом он осуществляет сортировку в двух направлениях – в прямом или обратном. При этом производится фиксация коммутации только в том случае, когда при сравнении пары чисел произведена коммута ция накрест, то есть если их поменяли местами, то этот момент фиксируется, и в этом направлении сортировки блок сортировочной сети дальше продолжает работать как коммутатор; аналогично – и при сорти ровке в обратном направлении. Во втором варианте блок сортировочной сети работает в составе сети сорти ровки с переменным направлением, в котором производится сортировка, то есть направление может изменяться многократно. Поэтому блок сортировочной сети, помимо сорти ровки в прямом или обратном направлении, может восстанавливать свое первоначальное состояние или возвращаться в установившееся ранее в соответствии с теми процессами, которые происхо дят в сети сортировки в целом. Для этого блок сорти ровочной сети имеет третий информационный вход 13 для фиксации требуемой извне блока коммута ции; или наоборот, ее отмены, при сорти ровке в каком-либо направлении. При этом предыдущие состояния считаются из блока сортировочной сети для фиксирова ния вне его; для этого блок сортировочной сети имеет третий информационный выход 20. Блок сортировочной сети работает следующим образом. Установка режима сорти ровки производится подачей потенциального единичного сигнала на первый вход 18 задания режима блока и потенциального нулевого сигнала на вто рой вход 19 задания режима блока. Прямое направление сортировки устанавливается подачей потенциального единичного сигнала на вход 16 выбора прямого направления и потенциального нулевого сигнала на вход 17 выбора обратного направления. При сортировке в прямом направлении сортируе мые числа поступают так: одно на первый информационный вход 11, другое – на четвертый информационный вход 14. С выхо дов элементов 2И–ИЛИ 1, 2 они поступают в элемент 3 сравнения и на второй и третий коммутаторы 9, 10. С элемента 3 сравнения через первый коммутатор 3 на управляющие вхо ды второго и третьего коммутаторов передается управляющий сигнал, зависящий от результата сравнения. В результате сортировки с выхода вто рого коммутатора 9 на первый информационный выход 21 будет вы дано большее число, а с выхода третьего коммутато ра 10 на вто рой информационный выход 22 будет выдано меньшее число. Обратное направление сортировки устанавливается подачей потенциального единичного сигнала на вход 17 выбора обратного направления блока и потенциального нулевого сигнала на вход 16 выбора прямого направления блока. При сортировке в обратном направлении первое число подается на второй информационный вход 12, а вто рое число – на пятый инфор мационный вход 15. В остальном, сорти ровка в обратном направлении выполняется также, как и в прямом, то есть понятие направления сортировки относится в данном случае к сети сортировки в целом, а блок сортировочной сети участвует в ней как составная часть сети. Установка режима коммутации производится подачей потенциальных единичных сигналов на первый вход 18 задания режима и на второй вход 19 задания режима. Прямое направление коммутации устанавливается подачей потенциального единичного сигнала на вход 16 выбора прямого направления, и подачей потенциального нулевого сигнала на вход 17 выбора обратного направления. При режиме коммутации в прямом направлении первое число подается на первый информационный вход 11, а на вто рое – на четвертый информационный вход 14. С выхо дов элемента 2И–ИЛИ 1, 2 сравниваемые числа поступают в элемент 3 сравнения и на второй и третий коммутаторы 9, 10. Сигнал с выхо да элемента 3 сравнения поступает на четвертый вход третьего элемента 2И–ИЛИ 4 и на второй вход первого коммутато ра 8. Если большее число находилось на первом элементе 2И–ИЛИ 1, то коммута ция – прямо, если на втором элементе 2И–ИЛИ 2, то коммутация – накрест. В зави симости от результата сравнения производится коммутация прямо или накрест, после чего на выходе второго коммута тора 9 нахо дится большее число, а на выхо де третьего коммутатора 10 – меньшее. То есть сравнение первой пары чисел позволяет настроить блок сортировочной сети на конкретный способ коммутации – соединение прямо или накрест. С прихо дом потенциальных единичных сигналов по первому и вто рому входам 18, 19 задания режимов, сигнал с выхода элемента 3 сравнения проходит через третий элемент 2И–ИЛИ 4 и фиксируется в первом триггере 5. После этого зафиксированный таким образом вид коммута ции сохраняется в блоке сортировочной сети и используется при прямом направлении коммутации в сети. Обратное направление коммутации в сети сортировки устанавливается подачей потенциального единичного сигнала на вход 17 вы бора обратного направления блока и потенциального нулевого сигнала на вход 16 вы бора прямого направления блока. При коммутации в обратном направлении первое число подается на второй информационный вход 12, а вто рое – на пятый информационный вход 15. С выхо дов первого и вто рого элементов 2И–ИЛИ 1, 2 числа поступают на входы элемента 3 сравнения и на входы вто рого и третьего коммута торов 9, 10. Сигнал результата сравнения с выхо да элемента 3 сравнения поступает на четвертый вход третьего элемента 2И–ИЛИ 4 и второй вход третьего коммутатора 8. Если большее число находилось на первом элементе 2И–ИЛИ 1, то коммута ция выполняется прямо – это число через второй коммутатор 9 подается на первый инфор мационный выход 21, если же на нем нахо дилось меньшее число, то коммутация выполняется накрест – это число через третий коммутатор 10 подается на второй информационный выход 22. Аналогично – со вторым числом, то есть если оно больше, чем первое, то поступит на первый информационный вход 21, если меньше – то на второй информационный вход 22. С прихо дом потенциальных единичных сигналов по первому и вто рому входам 18, 19 задания режимов, сигнал с выхода элемента 3 сравнения фиксируется во вто ром триггере 6. В дальнейшем установленный вид коммутации, зафиксированный триггером 6, сохраняется в блоке сортировочной сети и используется при обратном направлении коммутации в сети. До установки режима с переменным направлением сорти ровки (производится подачей потенциального нулевого сигнала на первый вход 18 задания режима и потенциального единичного сигнала на второй вход 19 задания режима) уста навливается режим коммутации. Прямое направление коммутации устанавливается подачей потенциального единичного сигнала на вход 16 выбора прямого направления блока и подачей потенциального нулевого сигнала на вход 17 вы бора обратного направления блока. При режиме с переменным направлением сортировки в прямом направлении первое число подается на первый инфор мационный вход 11, второе – на четвертый информационный вход 14. С выходов первого и второго элементов 2И–ИЛИ 1, 2 числа поступают для сравнения в элемент 3 сравнения, а также во второй и третий коммутаторы 9, 10. Сигнал с вы хода элемента 3 сравнения поступает на четвертый вход третьего элемента 2И–ИЛИ 4 на второй вход третьего коммутатора. Большее число коммутируется на выход вто рого коммутатора 9, а меньшее число коммутируется на выход третьего коммутатора 10. Установленная коммутация запоминается (фиксируется) в первом триггере 5. После этого блок сортировочной сети переводится в режим с переменным направлением сортировки подачей по перво му входу 18 задания режима блока потенциального нулевого сигнала. Те перь инфор мация с первого триггера 5 считывается через третий инфор мационный выход 20 и запоминается вне блока сорти ровочной сети. При этом на вход триггера поступает либо ранее запомненная управляющая информация, считанная с него до это го, либо новая, уп равляющая фиксацией. То есть состояние триггера либо изменяется на нулевое, либо он возвращается в единичное состояние, в зависимости от требований к условиям работы бло ка сортировочной сети на данном этапе сортировки или коммутации. Если в первый триггер 5 записывается через третий информационный вход 13 н улевое значение, то блоком сортировочной сети вы полняются перечисленные выше действия по сравнению очередных двух чи сел и перехо ду в состояние коммутации, которое, в свою очередь, опять можно изменить на начальное состояние блока сортировочной сети, пропустив через второй вход третьего элемента 2И–ИЛИ 4 установочное значение с третьего информационного вхо да 13. Переход в обратное направление сортировки выполняется соответствующей сменой сигналов на вхо дах 16, 17 выбора прямого и обратного направлений. При этом перечисленные выше действия выполняются так: числа прохо дят путь своей обработки через вторые информационные входы 12 и пятые информационные входы 15, элемент 3 сравнения, первый, вто рой, третий коммутаторы 8, 9, 10 и второй триггер 6, кото рый подключается к третьему информационному входу 13 посредством третьего элемента 2И–ИЛИ 14, а к третьему инфор мационному выхо ду 20 он подключается посредством четвертого элемента 2И–ИЛИ 7. Многократное изменение состояния первого или второго триггеров 5, 6 может осуществляться как во время смены направлений сорти ровки в сети сортировки, так и при сохранении направления. В результате работы блока сортировочной сети в режиме с переменным направлением сортировки могут выполняться и первые два режима, причем первый режим – сортировки выполняется при постоянном обнулении первого (или, соответственно, второго) триггеров 5, 6. В этом случае на выходах второго коммута тора 9 нахо дится большее число, а на выходах третьего коммутатора 10 – меньшее. При этом режим с переменным направлением сортировки прерывается и устанавливается либо режим сортировки, либо режим коммутации. То есть третий режим выступает по отношению к первым двум режимам блока как подготови тельный, то есть уста навливающий необхо димое по процессу ра боты сети состояние фиксаторов в ее элементах. Предлагаемый блок сортировочной сети, как видно из описания, может быть реализован в производственных условиях, поскольку в устройстве используется функциональная элементная база широкого назначения. Фиг. 1 Фиг. 2 Тираж 50 екз. Відкрите акціонерне товариство «Патент» Україна, 88000, м. Ужгород, вул. Гагаріна, 101 (03122) 3 – 72 – 89 (03122) 2 – 57 – 03

ДивитисяДодаткова інформація

Назва патенту англійськоюBlock of sorting network

Автори англійськоюFesenko Mykola Borysovych

Назва патенту російськоюБлок сортировочной сети

Автори російськоюФесенко Николай Борисович

МПК / Мітки

МПК: G06F 7/06

Мітки: блок, мережі, сортувальної

Код посилання

<a href="https://ua.patents.su/6-29498-blok-sortuvalno-merezhi.html" target="_blank" rel="follow" title="База патентів України">Блок сортувальної мережі</a>

Попередній патент: Спосіб реєстрації теплового випромінювання

Наступний патент: Спосіб визначення об’єму правого шлуночка

Випадковий патент: Пристрій для виготовлення ребристих труб з плоских