Перетворювач двійково-к-значного коду в двійковий код

Номер патенту: 44423

Опубліковано: 15.02.2002

Автори: Лопухін Ярослав Юрійович, Макаренко Ганна Миколаєвна, Лопухін Юрій Володимирович, Какурін Микола Якович, Штець Леонід Констянтинович

Формула / Реферат

Перетворювач двійково-К-значного коду в двійковий код, який складається з групи n розрядних регістрів зсуву, де n-розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, генератора імпульсів, групи n тригерів стану, накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи яких є виходами перетворювача і з'єднані з відповідними другими входами комбінаційних двійкових суматорів, виходи яких з'єднані з входами регістрів результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами відповідних тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, формувача еквівалентів, який складається з шифратора, комбінаційного зсувача та підсумовуючого лічильника імпульсів, підсумовувальний вхід якого з'єднаний з прямим виходом генератора імпульсів, а виходи з'єднані з керуючими входами комбінаційного зсувача, інформаційні входи якого з'єднані з відповідними виходами шифратора, входи якого з'єднані з відповідними виходами першого і другого тригерів стану, який відрізняється тим, що в нього введені перший, другий і третій комбінаційні суматори першого і другого ступеня, а формувач еквівалентів виконано багатоканальним, при цьому входи шифраторів кожного каналу з'єднані з відповідними виходами розрядних тригерів стану, входи першого і другого доданку комбінаційних суматорів першого ступеня з'єднані з відповідними виходами комбінаційних зсувачів в формувачах еквівалентів, виходи з відповідними входами першого і другого доданку комбінаційного суматора другого ступеня, виходи якого з'єднані з відповідними першими входами комбінаційного суматора підсумовувальний вхід лічильників усіх каналів з'єднано з прямим виходом генератора імпульсів.

Текст

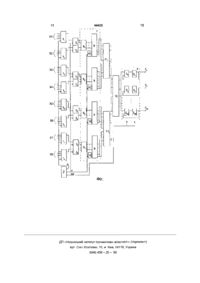

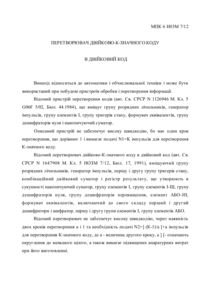

Перетворювач двійково-К-значного коду в двійковий код, який складається з групи п розрядних регістрів зсуву, де n-розрядність перетворюваного коду, паралельні інформаційні входи яких є входами перетворювача, генератора імпульсів, групи п тригерів стану, накопичувального суматора, виконаного з комбінаційного двійкового суматора та регістра результату, виходи яких є виходами перетворювача і з'єднані з ВІДПОВІДНИМИ другими входами комбінаційних двійкових суматорів, виходи яких з'єднані з входами регістрів результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, інверсний вихід якого з'єднаний з входами зсуву усіх розрядних регістрів зсуву, виходи першого біта розрядних регістрів зсуву з'єднані з інформаційними входами ВІДПОВІДНИХ тригерів стану, входи синхронізації яких з єднані з прямим виходом генератора імпульсів, формувача еквівалентів, який складається з шифратора, комбінаційного зсувача та підсумовуючого лічильника імпульсів, підсумовувальний вхід якого з'єднаний з прямим виходом генератора імпульсів, а виходи з'єднані з керуючими входами комбінаційного зсувача, інформаційні входи якого з'єднані з ВІДПОВІДНИМИ виходами шифратора, входи якого з'єднані з ВІДПОВІДНИМИ виходами першого і другого тригерів стану, який відрізняється тим, що в нього введені перший, другий і третій комбінаційні суматори першого і другого ступеня, а формувач еквівалентів виконано багатоканальним, при цьому входи шифраторів кожного каналу з'єднані з ВІДПОВІДНИМИ виходами розрядних тригерів стану, входи першого і другого доданку комбінаційних суматорів першого ступеня з'єднані з ВІДПОВІДНИМИ виходами комбінаційних зсувачів в формувачах еквівалентів, виходи з ВІДПОВІДНИМИ входами першого і другого доданку комбінаційного суматора другого ступеня, виходи якого з'єднані з ВІДПОВІДНИМИ першими входами комбінаційного суматора підсумовувальний вхід ЛІЧИЛЬНИКІВ усіх каналів з'єднано з прямим виходом генератора імпульсів CO Винахід відноситься до автоматики і обчислювальної техніки і може бути використаний при побудові пристроїв обробки і перетворення інформації Відомий перетворювач двійково-К-значного коду в двійковий код (авт Св СРСР № 1783618 М Кл 5Н03М7/12, Бюл № 47, 1992), вміщуючий групу з п розрядних ЛІЧИЛЬНИКІВ, де п - розрядність перетворюваного коду, генератор імпульсів, першу, другу та третю групи тригерів стану, комбінаційний двійковий суматор і регістр результату, що утворюють в сукупності накопичуючий суматор, першу і другу групи елементів І, першу і другу групу елементів 1І ї, групу кодових шифраторів, (п-1)-— у групу елементів АБО, групу дешифраторів нуля, першу і другу групу дешифраторів перевищення, перший і другій елементи АБО-НІ, формувач екві валентів, включаючий до свого складу перший, другий і третій дешифратори та шифратор, першу другу і третю групи елементів І, групу елементів АБО Такий перетворювач не забезпечує достатньо високої швидкодії, через наявність трьох кроків (1, а, Ь) перетворення та необхідності подачі N3=] (К1)/Ь [+] (Ь-1)/а [+а імпульсів для перетворення Кзначного коду, а також має значні апаратні витрати при його виготовленні внаслідок ускладнення як операційної частини перетворювача, що зумовлено введенням окрім другого, ще й третього кроку перетворювання , так і особливо ускладненням формувача еквівалентів, що повинен генерувати М3=т(2п-І)+І=3*(2п-І)+І=1 5*2(2П-І)+І=1 5*2п+1-2 еквівалентів, тобто в 1 5 рази більше, ніж в двокроковому перетворювачі кодів, m - КІЛЬКІСТЬ кроків пе 44423 формувач еквівалентів виконано багатоканальретворення ним, при цьому входи шифраторів кожного каналу В наведених вище формулах b, a, I - третій, з'єднані з ВІДПОВІДНИМИ виходами розрядних тридругий та перший кроки перетворення ВІДПОВІДНО герів стану, входи першого і другого доданку комНайбільш значною причиною різкого збільбінаційних суматорів першого ступеня з'єднані з шення апаратних витрат описаного перетворюваВІДПОВІДНИМИ виходами комбінаційних зсувачів в ча кодів і особливо формувача еквівалентів є зроформувачах еквівалентів, виходи з ВІДПОВІДНИМИ стання КІЛЬКОСТІ еквівалентів у ступені від п (2П), входами першого і другого доданку комбінаційного що при великому значенні п та організації формусуматора другого ступеня, виходи якого з'єднані з вача еквівалентів у вигляді одного каналу призвоВІДПОВІДНИМИ першими входами комбінаційного дить до вказаного вище недоліку суматора, підсумовуючий вхід ЛІЧИЛЬНИКІВ усіх каНайбільш близьким по сукупності ознак щодо налів з'єднано з прямим виходом генератора імпузаявляемого є перетворювач двійково-К-значного льсів коду в двійковий код (патент України на винахід № 17979А, МПК 6 Н03М7/12), вміщуючий групу з пВведення в відомий перетворювач двійково-Крозрядних регістрів зсуву, де n-розрядність перезначного коду в двійковий код додаткових комбітворюваного коду, генератор імпульсів, групу з (пнаційних суматорів, додаткових Р-1 каналів в фоІ)-го тригера стану, комбінаційний двійковий сумармувач еквівалентів, нових зв'язків, а також вилутор і регистр результату, що створюють в сукупночення з формувача еквівалентів першої групи сті накопичуючий суматор, формувач еквівалентів, елементів АБО, групи елементів І, дозволило підвключаючий в свій склад групу елементів І, групу вищити швидкодію з п'ятьох тактів перетворення елементів АБО, шифратор, підсумовуючий лічильдо чотирьох та істотно зменшити апаратні витрати ник імпульсів, комбінаційний зсувач в2 п /Р*2 п/р разів Описаний перетворювач при наявності чотиНа фігурі зображена структурна схема перерьох кроків (І, а, Ь, с) перетворення, де с - четвертворювача двійково-К-значного коду в двійковий тий крок перетворення (с=8, Ь=4, а=2), не забезпекод при К=12, п=8, Р=4 чує достатньо високої швидкодії через Перетворювач містить п розрядних регістрів необхідність подачі N4=5 імпульсів при перетвозсуву 1, де n-розрядність перетворювача коду ренні К-значних чисел (3< К ! С , (S 10 3 , j = 2 , s4 = (4 I 0 ( C 7 + 4 Ю ' С Д J - 3;(8) (8.10 S C , -E- 8 - Ю ' C s t , / = 4 , Перетворення двійкових кодів (Сі,С2),(Сз,С4),(С5,Сб),(С7,С8), що можуть приймати в кожній парі чотири значення 00, 01, 10, 11 та ВІДПОВІДНИХ значенням перших біт розрядних регістрів 1-1-18, виконується в ВІДПОВІДНОСТІ з законом функціонування формувачів еквівалентів 7-і-74 для першого такту (таблиця) В другому такті ДВІЙКОВІ значення еквівалентів за допомогою комбінаційних зсувачив 10-І-104 будуть збільшені в 2 рази (зсувом ліворуч на один розряд), в третьому такті вони будуть збільшені в 4 рази (зсувом ліворуч усіх кодів в таблиці на 2 розряди) та в четвертому такті вони будуть в порівнянні з таблицею для першого такту збільшені в 8 разів (зсунені ліворуч на З двійкових розряди) Підсумовуючи лічильники Ю-і-104 перед початком перетворення повинні бути встановлені в по 44423 8 = чатковий стан 112 С 7 =11, С 6 і С 5 01, С 4 , 03=01,02, Сі=11) Запис інформації в регістри триггерів стану 3-іВ результаті цього коди перших біт числа Ао 3s виконується перепадом 0-1 прямого імпульса П надійдуть по два розряди (С2, С-і), (С4, Сз), (Сє, генератора імпульсів 2, зсув інформації в розрядС5),(Cs, C7) ВІДПОВІДНО на входи шифраторів 7-і-74 і них регістрах 1-1-18 виконується перепадом 0-1 перетворяться на складові еквівалентів S-i(C2, інверсного імпульса І (тобто по задньому фронту Сі)=101І2=11іо, S2(C4, Сз)=0110 01002=100ю, імпульса П) та запис інформації в регістр резульS3(C6, C5)=001011000100002=1 ООООю, S4(C8, тату 6 накопичуючого суматора 4 виконується пеС7)=10100111 11011000110000002=110ОООООю репадом 1-0 імпульсу з прямого затриманного виКомбінаційний двійковий суматор 111 в реходу ПЗ генератора 2 3 приходом переднього зультаті додавання складових еквівалентів фронту першого імпульсу на прямому виході П Si(C2,Ci)= 11(ю) і S 2 = 100(ю) видасть на виходах генератора 2 значення сигналу зміниться з 0 на 1, двійковий код числа 111(ю), що надійде на входи що дозволить занесення коду числа (усіх перших першого доданку третього комбінаційного суматобіт) Сз-С-і в тригери регістрів стану Зз-З-і (Се, ра 12 Таблиця Значення Значення Значення Значення Десятковий ДВІЙКОВИЙ КОД еквіваленту третіх яругах перших код Значення вихідних розрядів біт біт біт еквіваленту У24-У1 С8С7 С6С5 С4СЗ С2С1 S10 00 00 00 00 0 000000000000000000000000 00 00 00 01 1 00000000000000000000000І 00 00 00 10 10 000000000000000000001010 00 00 00 11 п 000000000000000000001011 00 00 00 00 0 000000000000000000000000 00 00 01 00 100 000000000000000001100100 00 00 1 0 00 1000 000000000000001111101000 00 0 0 1 1 0 0 1100 000000000000010001001100 00 00 00 0 0 0 оооооооооооооооооооооооо 00 01 00 00 10000 000000000010011100010000 00 10 00 00 100000 000000011000011010100000 00 11 00 00 110000 000000111010110110110000 00 00 00 00 0 оооооооооооооооооооооооо 01 00 00 00 1000000 000011110100001001000000 10 00 00 00 10000000 100110001001011010000000 11 00 00 00 11000000 10100ШИОП00011000000 Четверти X Біт Комбінаційний двійковий суматор першого ступеня 112 в результаті додавання складових еквіваленту S31 S4 видасть на виході двійковий код числа 11 ОЮООО(Ю), що надходить на виходи другого доданку третього 12-і комбінаційного суматора В результаті додавання чисел 111-ю і 11 010 000-ю третім комбінаційним двійковим суматором 12, на його виходах утвориться двійковий код еквіваленту 11 010 111 ю, що надходить далі на перші входи комбінаційного двійкового сумітора 5 в на 24...... 1 копичуючому суматорі 4 Задній фронт прямого затриманого імпульсу ПЗ з виходу генератора 2 виробить запис результату складання з виходів комбінаційного двійкового суматора 5 в регістр результату 6 Двійковий код числа 11 010 111-ю з'явиться також і на виходах перетворювача З приходом переднього фронту другого прямого імпульсу на прямому виході П генератора 2 значення сигналу на цьому виході зміниться з 0 на 44423 1, що дозволить занесення коду числа Ао (усіх перших біт) із-за зсуву на один біт праворуч першим інверсним імпульсом І) в тригери Сз-С-і регістрів стану С 8 С 7 = 0 1 , С 6 С 5 =00, С 4 С 3 = 0 1 , С 2 Сі=00 В результаті цього ДВІЙКОВІ КОДИ других біт числа Ао по два розряди((С2,Сі),(С 4 ,С 3 ),(Сб,С 5 ),(С 8 ,С 7 )) надійдуть ВІДПОВІДНО на входи шифраторів і перетворяться на складові еквівалентів Si(C2,Ci)=Oio, S 2 (C 4 ,C 3 ) = 100io, S3(C6,C7)=OOOio, S 4 (C 8 ,C 7 )=1 000 ОООю Ці складові за допомогою комбінаційних зсувачив ІО1-Ю4 в кожному каналі будуть збільшені в другому такті вдвічи внаслідок стану всіх ЛІЧИЛЬНИКІВ 9 І - 9 4 = 0 1 (2) Таким чином в другому такті на виходах каналів 7і-74 формувача еквівалентів матиме ВІДПОВІДНО ДВІЙКОВІ коди складових еквівалентів >\Ь> ті Ъ rWSw Ъ i-l 0 i-i.UUU,UUUfn. В результаті по парного додавання S-і, S2, S3 і S4, а потім і їх результатів, на виходах комбінаційного двійкового суматора 12 одержимо в другому такті еквівалент 2 000 200-ю, що буде складений за допомогою накопичуючого суматора 4 з накопленою сумою еквівалентів 11 010 111ю, що залишилася в регістрі результату 6 з першого такту Результат цього додавання 13 010 311-ю з приходом заднього фронту другого прямого затриманого імпульсу ПЗ з виходу генератора 2 буде занесено в регістр результату 6 Задній фронт другого інверсного імпульсу з виходу І генератора 2, ще до занесення результату в регістр 6, виконає зсув праворуч на один розряд числа А 0 =0100 0011 0100 0100 0010 0011 0010 0100, в результаті цього в розрядних регистрах 1 8 1і буде знаходиться число А 0 "=0010 0001 0010 0010 0001 0001 0001 0010, тобто на МІСЦІ перших біт будуть знаходиться треті біти з вагою 4 З приходом переднего фронту третього прямого імпульсу з виходу П генератора 2 в тригери Cs-Ci регістрів стану 3 8 -3і буде записане число С 8 С 7 = 0 1 , С 6 С 5 =00, С 4 Сз=11, С 2 Сі=10 В результаті цього за допомогою шифраторів 81-84 на їх виходах будуть сформовані ДВІЙКОВІ коди чисел Si=10io, S 2 =1100io, S 3 =0i 0 , S4=1 000 ОООю Внаслідок того, що третій прямий імпульс з виходу П генератора 2 змінив стан усіх ЛІЧИЛЬНИКІВ Ю-і-104 с 012 на Юг, то всі складові еквівалентів S 2 i-S 2 4 за допомогою комбінаційних зсувачив 9-і-94 в кожному блоці будуть в третьому такті збільшені в чотири рази В результаті на виходах формувачів еквівалентів 7-і-74 матимемо такі коди S і=40ю, S 3 2 =4400io, S 3 3 = 0 i 0 , S 3 4 =4 000 ОООю Після підсумовування комбінаційні суматори 11і 112, і 12-І одержимо загальний еквівалент S 3 =4 004 440-ю Значення цього еквіваленту пода 10 ється на перші входи накопичуючого суматора 4 і буде складено з накопиченою сумою еквівалентів 13 0 1 0 311 іо, що залишиться в регістрі результату 6 накопичуючого суматора 4 Задній фронт третього прямого затриманого імпульсу з виходу ПЗ генератора 2 виконає запис результату складання числа 4 004 440-ю та числа 13 0 1 0 311 іо в регістр 6 результату, тобто числа 17 014 751ю Задній фронт третього інверсного імпульсу з виходу І генератора 2, ще до занесення результату в регістр 6, виконає зсув праворуч на один розряд числа Ао'-ООЮ 0001 0010 0010 0001 0001 0001 0010, в результаті цього в розрядних регістрах 18-1-1 буде знаходитись число А"'о=0001 0000 0001 0001 0000 0000 0000 0001 З приходом переднього фронту четвертого прямого імпульсу з виходу П генератора 2 в тригери Сз-С-і регистрів стану 3 8 -3і буде записане число С 8 С 7 =10СбС 5 =11, С 4 С 3 =00,С 2 Сі=01 В результаті цього коди четвертих біт числа Ао по два розряди (С2,Сі),(С 4 ,С 3 ),(Сб,С 5 ),(С8,С 7 ) надійдуть ВІДПОВІДНО на входи шифраторів 81-84 и перетворяться на складові еквівалентів S1i—110, S 1 2 =0io, S 1 3 =110000io, S 1 4 =10000000io Внаслідок того, що четвертий прямий імпульс П збільшив стан всіх ЛІЧИЛЬНИКІВ Ю1-Ю4 з 10г на 112, складові еквівалентів s Y s V в четвертому такті за допомогою комбінаційних зсувачив 9-і-94 будуть збільшені в ВІСІМ разів Таким чином на виходах формувачів еквівалентів 7-і-74 ВІДПОВІДНО матимемо Si=8-io, S 2 =0io, S 3 =880 ОООю, S 4 =80 000 ОООю За допомогою комбінаційних двійкових суматорів 11-І, 1121 12-І одержимо загальнийсеквівалент 80 880 008ю Цей загальний еквівалент 80 880 008(ю) буде додано до накопленої суми еквівалентів, що залишився в регістрі результату 6 з третього такту 17 014 751ю Результат цього додавання число 97894759-ю з приходом заднього фронту четвертого прямого затриманого імпульса з виходу ПЗ регістра 2 буде занесено в регістр результату 6 накопичуючого суматора 4 Двійковий код числа 97894759-ю з'явиться також і на виходах перетворювача На цьому процес перетворення закінчується Четвертий інверсний імпульс І призведе до повного обнуления розрядних регістрів 18-1-1 Перед кожним наступним перетворенням необхідно обнулити регістр результату 6 і виконати запис перетворюваного К-значного числа в розрядні регістри 1 8-1-1 Швидкодія пристрою, що пропонується, не залежить від розрядності перетворюваного коду і для 8

ДивитисяДодаткова інформація

Автори англійськоюKakurin Mykola Yakovych, Lopukhin Yurii Volodymyrovych, Lopukhin Yaroslav Yuriiovych, Makarenko Hanna Mykolaivna, Shtets Leonid Kostiantynovych

Автори російськоюКакурин Николай Яковлевич, Лопухин Юрий Владимирович, Лопухин Ярослав Юрьевич, Макаренко Анна Николавна, Штец Леонид Константинович

МПК / Мітки

МПК: H03M 7/02

Мітки: двійковий, коду, код, двійково-к-значного, перетворювач

Код посилання

<a href="https://ua.patents.su/6-44423-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду в двійковий код</a>

Попередній патент: Пристрій для перетворення підйомної гідростатичної сили рідини в механічну енергію

Наступний патент: Санітарний чохол

Випадковий патент: Розкидач органічних добрив