Перетворювач двійково-к-значного коду в двійковий код

Номер патенту: 30396

Опубліковано: 15.11.2000

Автори: Лопухін Юрій Володимирович, Макаренко Ганна Миколаєвна, Лопухін Ярослав Юрійович, Какурін Микола Якович, Штець Леонід Констянтинович

Формула / Реферат

Перетворювач двійково-К-значного коду в двійковий код, що вміщує групу з n розрядних регістрів зсуву, де n – розрядність вхідного коду, паралельні інформаційні входи яких є входами перетворювача, генератор імпульсів, накопичуючий суматор, виконаний з комбінаційного двійкового суматора та регістра результату, виходи якого є виходами перетворювача кодів, формувач еквівалентів, що складається з першого і другого шифраторів, першого комбінаційного двійкового суматора, підсумовуючого лічильника імпульсів, групи елементів І, групи елементів АБО, при цьому виходи регістра результату накопичуючого суматора є виходами перетворювача і з'єднані з відповідними другими входами комбінаційного двійкового суматора, молодші перші входи якого є молодшими інформаційними входами накопичуючого суматора і з'єднані з відповідними виходами групи елементів АБО, старші інформаційні входи накопичуючого суматора з'єднані з відповідними старшими інформаційними виходами формувача еквівалентів, виходи комбінаційного двійкового суматора з'єднані з відповідними входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, прямий вихід якого з'єднаний з синхровходом підсумовуючого лічильника імпульсів, старший вихід якого з'єднаний з усіма другими входами групи елементів І, входи першого і другого шифраторів є відповідно другою і третьою інформаційною групою входів формувача еквівалентів, бітові виходи молодшого розрядного регістру зсуву з'єднані через відповідні біти першої групи входів формувача еквівалентів з відповідними першими входами групи елементів І, виходи яких з'єднані з відповідними першими входами групи елементів АБО, виходи першого шифратора з'єднані з відповідними входами першого доданку першого комбінаційного двійкового суматора, входи другого доданку якого з'єднані з відповідними виходами другого шифратора, входи зсуву (і+1)-го розрядного регістра зсуву (і=1,..., (n-1)) з'єднані з інверсним виходом генератора імпульсів, який відрізняється тим, що в формувач еквівалентів введені третій і четвертий шифратори, другий і третій комбінаційні двійкові суматори, молодші виходи третього комбінаційного двійкового суматора з'єднані з відповідними другими входами групи елементів АБО, старші виходи якого є старшими інформаційними виходами формувача еквівалентів, входи першого і другого доданку в третьому комбінаційному двійковому суматорі з'єднані з відповідними виходами першого і другого комбінаційних двійкових суматорів, входи першого і другого доданків другого комбінаційного двійкового суматора з'єднані з відповідними виходами третього і четвертого шифраторів, входи яких є відповідно входами четвертої і п'ятої інформаційних груп входів формувача еквівалентів і з'єднані з відповідними виходами другого і четвертого біт (і+1)-го розрядного регістра зсуву (і=1,..., (n-1)), входи другої і третьої інформаційних груп входів формувача еквівалентів з'єднані з відповідними виходами перших і третіх біт (і+1)-го розрядного регістра зсуву (і=1,..., (n-1)), входи скидання яких з'єднані зі старшим виходом підсумовуючого лічильника імпульсів в формувачі еквівалентів.

Текст

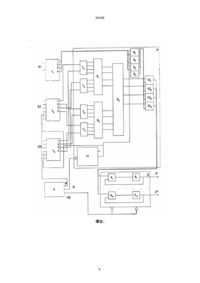

Перетворювач двійково-К-значного коду в двійковий код, що вміщує гр упу з n розрядних регістрів зсуву, де n – розрядність вхідного коду, паралельні інформаційні входи яких є входами перетворювача, генератор імпульсів, накопичуючий суматор, виконаний з комбінаційного двійкового суматора та регістра результату, ви ходи якого є виходами перетворювача кодів, формувач еквівалентів, що складається з першого і другого шифраторів, першого комбінаційного двійкового суматора, підсумовуючого лічильника імпульсів, групи елементів І, гр упи елементів АБО, при цьому виходи регістра результату накопичуючого суматора є ви ходами перетворювача і з'єднані з відповідними другими входами комбінаційного двійкового суматора, молодші перші входи якого є молодшими інформаційними входами накопичуючого суматора і з'єднані з відповідними виходами групи елементів АБО, старші інформаційні входи накопичуючого суматора з'єднані з відповідними старшими інформаційними виходами формувача еквівалентів, виходи комбінаційного двійкового суматора з'єднані з відповідними входами регістра результату, син хровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, прямий вихід якого з'єднаний з синхровходом підсумовуючого лічильника імпульсів, старший вихід якого з'єднаний з усіма другими входами групи елементів І, входи першого і другого ши фраторів є відпо A (54) ПЕРЕТВОРЮВАЧ ДВІЙКОВО-К-З НАЧНОГО КОДУ В ДВІЙКОВИЙ КОД 30396 дорівнює 1 і вимагає подачі N1=K імпульсів для перетворення К-значного коду. Відомий перетворювач двійково-К-значного коду в двійковий код (а.с. СРСР № 1647908 М. Кл. 5 Н03М7/12, Бюл. 17, 1991), вміщуючий гр упу розрядних лічильників, генератор імпульсів, першу і другу гр упу тригерів стану, комбінаційний двійковий суматор і регістр результату, що утворюють в сукупності накопичуючий суматор, групу елементів І, гр уп у елементів І-НІ, груп у деши фраторів нуля, груп у деши фраторів перевищення, елемент АБО-НІ, формувач еквівалентів, включаючий до свого складу перший і другий дешифратори і шифратор, першу і др угу гр упи елементів І, гр упу елементів АБО. Відомий перетворювач не забезпечує високу швидкодію, через наявність двох кроків перетворення а і 1 та необхідність подачі N2=] (К-1)/а [+а імпульсів для перетворення К-значного коду, де а величина другого кроку, а ] [ - означають округлення до меншого цілого, а також вимагає підвищених апаратурних ви трат при його виготовленні. Відомий також перетворювач двійково-Кзначного коду в двійковий код (а.с. СРСР № 1783618 М. Кл. 5 Н03М7/12, Бюл. 47, 1992), вміщуючий груп у з n розрядних лічильників, де n розрядність перетворюємого коду, генератор імпульсів, першу, другу та третю гр упи тригерів стану, комбінаційний двійковий суматор і регістр результату, що утворюють в сук упності накопичуючий суматор, першу і другу гр упи елементів І, першу і др угу гр упу елементів І-НІ, гр упу кодових шифраторів, (n-1)-у гр упу елементів АБО, груп у дешифраторів нуля, першу і другу гр упу деши фраторів перевищення, перший і другий елементи АБОНЕ, формувач еквівалентів, включаючий до свого складу перший, другий і третій деши фратори та шифратор, першу др угу і третю групи елементів І, груп у елементів АБО. Відомий перетворювач не забезпечує достатньо високої швидкодії, через наявність трьох кроків (1, а, b) перетворення та необхідності подачі N3=] (к-1)/b [+] (b-1)/а [+а імпульсів для перетворення К-значного коду. Відомий також перетворювач двійково-Кзначного коду в двійковий код (патент України на винахід № 17979А, МПК 6 Н03М7/12), вміщуючий груп у з n-розрядних регістрів зсуву, де n - розрядність перетворюємого коду, генератор імпульсів, груп у з (n-1)-го тригера стану, комбінаційний двійковий суматор і регістр результату, що створюють в сукупності накопичуючий суматор, формувач еквівалентів, включаючий до свого складу гр упу елементів І, групу елементів АБО, ши фратор, підсумовуючий лічильник імпульсів, комбінаційний зсувач. Описаний перетворювач при наявності чотирьох кроків (1, а, b, с) перетворення, де с - четвертий крок перетворення (с=8), не забезпечує достатньо високої швидкодії через необхідність подачі N4=5 імпульсів при перетворенні К-значних чисел. (3£К£15). Найбільш близьким за сукупністю ознак щодо пропонованого є перетворювач двійково-Кзначного коду в двійковий код (заявка на патент України № 97063339 від 27.06.1997 МПК 6 Н03М7/12), вміщуючий гр упу з n розрядних регіст рів зсуву, де n - розрядність перетворюємого коду, генератор імпульсів, першу і другу групи з (n-1)-го тригера стану, комбінаційний двійковий суматор і регістр результату, що утворюють в сукупності накопичуючий суматор, формувач еквівалентів, включаючий до свого складу груп у елементів І, груп у елементів АБО, перший і другій шифратори, перший комбінаційний двійковий суматор формувача еквівалентів, підсумовуючий лічильник імпульсів, комбінаційний зсувач. Описаний перетворювач при наявності чотирьох кроків (1, а, b, с), де с - четвертий крок перетворення (с=8), не забезпечує гранично високу швидкодію через необхідність подачі N5=3 імпульсів при перетворенні К-значних чисел (3£К£15). В основу винаходу поставлено задачу створення такого перетворювача двійково-К-значного коду в двійковий код, в якому нове схемне рішення дозволило б при невеликому збільшенні апаратурних витрат істотно підвищити його швидкодію. Такого технічного результату може бути досягнуто, якщо до перетворювача двійково-К-значного коду в двійковий код, вміщуючого груп у з n розрядних регістрів зсуву, де n - розрядність вхідного коду, паралельні інформаційні входи яких є входами перетворювача, генератор імпульсів, накопичуючий суматор, виконаний з комбінаційного двійкового суматора та регістра результату, ви ходи якого є виходами перетворювача кодів, формувач еквівалентів, що складається з першого і другого ши фраторів, першого комбінаційного двійкого суматора, підсумовуючого лічильника імпульсів, групи елементів І, групи елементів АБО, при цьому виходи регістра результату накопичуючого суматора є виходами перетворювача та з'єднані з відповідними другими входами комбінаційного двійкового суматора, молодші перші входи якого є молодшими інформаційними входами накопичуючого суматора та з'єднані з відповідними виходами групи елементів АБО, старші інформаційні входи накопичуючого суматора з'єднані з відповідними старшими інформаційними виходами формувача еквівалентів, ви ходи комбінаційного двійкового суматора з'єднані з відповідними входами регістра результату, синхровхід якого з'єднаний з прямим затриманим виходом генератора імпульсів, прямий вихід якого з'єднаний з синхровходом підсумовуючого лічильника імпульсів, старший вихід якого з'єднаний з усіма другими входами групи елементів І, входи першого і другого шифраторів є відповідно другою і третьою інформаційними групами входів формувача еквівалентів, бітові виходи молодшого розрядного регістру зсуву з'єднані через відповідні біти першої групи входів формувача еквівалентів з відповідними першими входами групи елементів І, виходи яких з'єднані з відповідними першими входами групи елементів АБО, ви ходи першого шифратора з'єднані з відповідними входами першого доданку першого комбінаційного двійкового суматора, входи другого доданку якого з'єднані з відповідними виходами другого шифратора, входи зсуву (і+1)-го розрядного регістра зсуву (і=1,..., (n-1)) з'єднані з інверсним виходом генератора імпульсів, відповідно до винаходу, в формувач еквівалентів введені третій і четвертий шифратори, другий і третій комбінаційні двійкові суматори, молодші виходи третього комбінаційного 2 30396 двійкового суматора з'єднані з відповідними другими входами групи елементів АБО, а старші виходи третього комбінаційного двійкового суматора є старшими інформаційними виходами формувача еквівалентів, входи першого і другого доданку в третьому комбінаційному двійковому суматорові з'єднані з відповідними виходами першого і другого комбінаційних двійкових суматорів, входи першого і другого доданків другого комбінаційного двійкового суматора з'єднані з відповідними виходами третього і четвертого шифраторів, входи яких є відповідно входами четвертої і п'ятої інформаційних гр уп входів формувача еквівалентів і з'єднані з відповідними виходами другого і четвертого біт (і+1)-го розрядного регістру зсуву (і=1,..., (n-1)), входи др угої і третьої інформаційних груп входів формувача еквівалентів з'єднані з відповідними виходами перших і третіх біт (і+1)-го розрядного регістра зсуву (і=1,..., (n-1)), входи скидання яких з'єднані зі старшим інформаційним виходом підсумовуючого лічильника імпульсів в формувачі еквівалентів. Введення в відомий перетворювач двійково-Кзначного коду в двійковий код третього і четвертого шифраторів, другого і третього комбінаційних двійкових суматорів, а також нових зв'язків, дозволило, при невеликому збільшенні апаратурних витрат, значно підвищити швидкодію, скоротивши максимальне число тактів перетворення з трьох до двох. На фігурі зображена структурна схема перетворювача двійково-К-значного коду в двійковий код при К=12, n=3. Перетворювач містить групу з n розрядних регістрів 1 зсуву, де n - розрядність перетворюємого коду, паралельні інформаційні входи яких є входами перетворювача, генератор 2 імпульсів, вміщуючий прямий П, інверсний І затриманий, прямий затриманий ПЗ виходи, накопичуючий суматор 3, виконаний з комбінаційного двійкового суматора 4 і регістра 5 результату, формувач 6 еквівалентів, що складається з першого 71, другого 72 , третього 73 і четвертого 74 шифраторів, першого 81, другого 82 і третього 83 комбінаційних двійкових суматорів, гр упи елементів І 9, гр упи елементів АБО 10, підсумовуючого лічильника 11 імпульсів. Виходи 11 регістра 5 результату є виходами перетворювача і з'єднані з відповідними другими входами комбінаційного двійкового суматора 4, молодші перші входи якого є молодшими інформаційними входами суматора 3 і з'єднані з відповідними виходами групи елементів АБО 10 формувача 6 еквівалентів, старші інформаційні входи накопичуючого суматора 3 з'єднані з відповідними старшими інформаційними виходами формувача 6 еквівалентів, виходи комбінаційного двійкового суматора 4 з'єднані з відповідними входами регістра 5 результату, ви ходи якого є інформаційними виходами перетворювача кодів, а синхровхід якого з'єднаний з прямим затриманим виходом ПЗ генератора 2 імпульсів, прямий вихід П якого з'єднаний з синхровходом підсумовуючого лічильника 11 імпульсів формувача 6 еквівалентів, входи зсуву (і+1)-го розрядного регістра зсуву 1 (і=1,..., (n-1)) з'єднані з інверсним затриманим виходом І генератора імпульсів 2. Перші входи групи елементів І 9 є першою інформаційною групою входів формувача еквівалентів 6 і з'єднані з відповідними бітами молодшого розрядного 11 регістра зсуву. Входи першого 7 1 другого 72, третього 73 і четвертого 74 шифраторів формувача 6 еквівалентів є відповідно другою, третьою, четвертою і п'ятою інформаційними групами входів формувача 6 еквівалентів. Входи другої і третьої інформаційних груп входів формувача 6 еквівалентів з'єднані відповідно з виходами першого і третього біт (і+1)-го розрядного регістра 1 зсуву (і=1,..., (n-1)), входи четвертої і п'ятої інформаційних груп входів формувача 6 еквівалентів, з'єднані відповідно з виходами другого і четвертого біт (і+1)-го розрядного регістра 1 зсуву (і=1,..., (n-1)), виходи першого 71 і другого 72 шифраторів з'єднані відповідними входами першого і другого доданку першого комбінаційного двійкового 81 суматора формувача 6 еквівалентів, виходи третього 73 і четвертого 74 ши фраторів з'єднані з відповідними входами першого і другого доданків другого комбінаційного двійкового 82 суматора формувача 6 еквівалентів. Виходи першого 81 і другого 82 комбінаційних двійкових суматорів з'єднані з відповідними входами першого і другого доданків в третьому комбінаційному двійковому суматорі 83, старші виходи якого є старшими виходами формувача 6 еквівалентів і з'єднані зі старшими інформаційними входами накопичуючого 3 суматора, молодші інформаційні виходи третього комбінаційного двійкового 83 суматора з'єднані з відповідними другими входами групи елементів АБО 10, виходи яких є молодшими інформаційними виходами формувача 6 еквівалентів і з'єднані з молодшими інформаційними входами накопичуючого суматора 3. Перші входи елементів групи АБО 10 з'єднані з відповідними виходами групи елементів І 9, всі другі входи яких з'єднані зі старшим виходом підсумовуючого лічильника 11 імпульсів формувача 6 еквівалентів та зі входами скидання R (і+1)-го розрядного регістра 1 зсуву (і=1,..., (n-1)). Ланцюги ініціювання та скидання на кресленні не наведені. Пристрій працює таким чином. Якщо в конкретному випадку n=3, К=12, то діапазон зміни вхідного коду від 0 до (123-1)= =0-1727(10). В перетворювачі, що пропонується, двійковоК-значного коду в двійковий код формувач 6 еквівалентів, виконаний у вигляді паралельнопослідовного сполучення першого 71 другого 72, третього 73, четвертого 74 шифраторів, першого 81, другого 82 і третього 83 комбінаційних двійкових суматорів, а також підсумовуючого лічильника 11 імпульсів з передустановлюванням, реалізує функцію ì KCl + K 2C2 + bKE1+ bK2 E2 + ï ï S = í+ aKD1+ aK 2D2 + cKF1 + cK2F 2 При j = 1 , ïX1 При j = 2; ï î де Сі, Di, Ei, Fi - значення відповідно першого, другого, третього і четвертого бітови х виходів старших (і+1)-х розрядних регістрів 1 зсуву (і=1,.., (n-1)); а - другий крок перетворення (вага другого біта); b - третій крок перетворення (вага третього [( 3 [( ) ( ) ( )] )] 30396 біта); с - четвертий крок перетворення; X1 - молодша тетрада перетворюємого числа, j - номер такту зсуву. Перший крок перетворення (вага першого біта) дорівнює 1. Формувач 6 еквівалентів перетворитьспочатку в першому такті за допомогою шифраторів 71, 72, 73, 74 двійкові коди С2 С1, D2 D1, Е2 E1, F2 F1, відповідаючих значенням відповідно перших, других, треті х і четвертих біт старши х розрядних регістрів зсуву 13 і 12, забезпечуючи їхнє попарне складання за допомогою комбінаційних двійкових суматорів 81, 82 , 83 , а в др угому такті транслює (передає без зміни) на вихід формувача 6 еквівалентів молодшу тетраду X1, що відповідає першому виразу в квадратних дужках. Складова еквівалента, відповідна сумі [(КСl+К2С2)+(bКЕ1+bК2Е2)], формується в першому такті першим 81 комбінаційним суматором; складова еквівалента, відповідна другому виразу в квадратних дужках [(dKD1+dK2b2)+(cKF1+cK2F2)] формується в цьому ж (першому) такті другим 82 комбінаційним суматором. Додавання обох складових виконується третім комбінаційним суматором 83. Розглянемо роботу пристрою на наступному прикладі. Нехай необхідно перетворити трирозрядний вхідний 12 - значний код числа А0=1011 0110 1001(2-12)=В69(12)=1665(10); Формувач 6 еквівалентів при використанні коду прямого заміщення 8421 реалізує функцію ì[(12Cl + 144C 2 ) + (48E1 + 576E2 )] + ï S = í+ [(24C1 + 288C2 ) + (96F1 + 1152F2 )] При j = 1 , ï X1 При j = 2; î значення D2 D1=11 перетвориться третім шифратором на число 312 на його виходах, код значення третіх біт Е2 Е1=01 перетвориться другим шифратором 72 на число 48 на його виходах, та, нарешті, двійковий код F2 F1=10 перетвориться четвертим 74 шифратором на число 115210 на його виходах. Двійковий комбінаційний суматор 81 в результаті додавання складових еквівалента 144 і 48 має видати на виході двійковий код числа 192=144+48, що надходить на входи першого доданку третього комбінаційного суматора 83; двійковий комбінаційний суматор 82 в результаті додавання складових 1152 і 312 видасть на виході двійковий код числа 1464=1152+312, що надходить на входи другого доданку третього комбінаційного суматора 83. В результаті додавання чисел 192 і 1464 третім комбінаційним суматором 83 на його виходах утвориться двійковий код еквівалента 1656=1464+192, що надходить на ви ходи формувача 6 еквівалентів і далі на входи накопичуючого суматора 3. Надходячи з виходу ПЗ генератора 2, передній фронт першого позитивного затриманого імпульсу ПЗ дозволить складання чисел 0 і 1656 в накопичуючому суматорові 3, а задній фронт цього ж імпульсу виробить запис інформації з виходів комбінаційного двійкового суматора 4 в регістр 5 результату, встановивши на др уги х складаючих входах суматора 4 двійкове значення числа 165610. З приходом заднього фронту першого інверсного затриманого імпульсу з інверсного виходу І генератора 2, тобто за перепадом 0-1 на вході синхронізації С старших розрядних регістрів 1 відбудеться зсув інформації в цих регістрах на один розряд, тобто в регістрах 1 встановиться число А1=0101 0011 1001. З приходом переднього фронту др угого позитивного імпульсу з прямого виходу генератора 2 стан підсумовуючого 11 лічильника імпульсів зміниться з 012 на 102, що призведе до відкриття групи елементів І 9 і до надходження одиничного сигналу на входи скидання R всіх старших розрядних регістрів зсуву 12 , 13. В результаті в регістрах 1 встановиться число А2=0000 0000 1001, а на виходах формувача 6 еквівалентів з'явиться код молодшої тетради Х1=10012=910. Передній фронт другого прямого затриманого імпульсу з виходу ПЗ генератора 2 дозволить складання чисел 1656 і 9, а задній фронт цього ж імпульсу виробить перезапис результату складання з виходів комбінаційного двійкового суматора 4 в регістр 5 результату, встановивши на других складаючих входах суматора 4 двійкове значення числа 166510. Двійковий код цього числа 1665 з'явиться також і на виходах перетворювача. На цьому процес перетворення закінчується. Перед кожним наступним перетворенням необхідно обнулити регістр 5 результату і виконати запис перетворюємого двійково-12-значного числа в регістри зсуву 1. Швидкодія пристрою, що пропонується, не залежить від розрядності перетворюємого коду, і для 12-значної системи обчислення не перевищує двох тактів. Перетворення двійкових кодів С2 С1, двійкових кодів D2 D1, двійкових кодів Е2 Е1, двійкових кодів F2 F1, відповідних значенням перших, других, треті х і четвертих біт старши х розрядних регістрів 1 зсуву, виконується у відповідності до закону функціонування формувача 6 еквівалентів (таблиця). В початковому стані регістр 5 результату обнулено, на прямому П і прямому затриманому ПЗ виходах генератора 2 - низький рівень; на інверсному І ви ході генератора 2 - високий рівень. Початкове занесення паралельного двійково12-значного коду перетворюємого числа в розрядні регістри 1, та передустановлення складаючого лічильника 11 за mod 2 формувача 6 еквівалентів в стан 00(2)=0(10) виконується подачею нульового сигналу на входи V розрядних регістрів 1 зсуву і на вхід паралельного занесення V лічильника 11. Запис інформації в регістр 5 результату виконується перепадом 1-0 імпульсу з прямого затриманого виходу ПЗ генератора 2. З приходом переднього фронту першого позитивного імпульсу з прямого виходу П генератора 2 стан підсумовуючого лічильника 11 по mod 2 зміниться з 00(2) на 01(2), що не дозволить виконати трансляцію молодшої тетради Х1=10012 на виходи формувача 6 еквівалентів. Водночас коди С2 С1=10, надходячи через другу інформаційну гр упу входів формувача 6 еквівалентів, перетворяться першим 71 шифратором на складову еквівалента 144 на його виходах, код 4 30396 Таблиця Закон функціонування формувача еквівалентів Такт J 1 2 Значення четвертих біт F2F1 00 00 00 00 00 00 00 00 00 00 00 00 00 01 10 11 00 Значення третіх біт Е2Е1 00 00 00 00 00 00 00 00 00 01 10 11 00 00 00 00 00 Значення други х біт D2D1 00 00 00 00 00 01 10 11 00 00 00 00 00 00 00 00 00 Значення перших біт С2С1 00 01 10 11 00 00 00 00 00 00 00 00 00 00 00 00 00 5 Десятковий код еквівалента S10 0 12 144 156 0 24 288 312 0 48 576 624 0 96 1152 1248 XI Значення вихідних розрядів Y 11 10 9 8 7 6 5 4 3 2 1 00000000000 00000001100 00010010000 00010011100 00000000000 00000011000 01001000000 01001110000 00000000000 00000011000 00101000000 01001110000 00000000000 00001100000 10010000000 10011100000 Трансляція тетради XI 30396 Фіг. 6 30396 __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2002 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 35 прим. Зам._______ __________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 __________________________________________________________ 7

ДивитисяДодаткова інформація

Назва патенту англійськоюTwo-k- digit-to-bianary converter

Автори англійськоюKakurin Mykola Yakovych, Lopukhin Yurii Volodymyrovych, Lopukhin Yaroslav Yuriiovych, Makarenko Hanna Mykolaivna, Shtets Leonid Kostiantynovych

Назва патенту російськоюПреобразователь двоично-к-значного кода в двоичный код

Автори російськоюКакурин Николай Яковлевич, Лопухин Юрий Владимирович, Лопухин Ярослав Юрьевич, Макаренко Анна Николавна, Штец Леонид Константинович

МПК / Мітки

МПК: H03M 7/02

Мітки: двійковий, двійково-к-значного, код, коду, перетворювач

Код посилання

<a href="https://ua.patents.su/7-30396-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду в двійковий код</a>

Попередній патент: Контактна лінза для офтальмоскопії

Наступний патент: Спосіб вихрового диспергування і активації матеріалів і пристрій для його здійснення

Випадковий патент: Композиція інгредієнтів для горілки "метрополь"