Перетворювач двійково-к-значного коду у двійковий код

Номер патенту: 24674

Опубліковано: 04.08.1998

Автори: Какурін Микола Яковлевич, Макаренко Ганна Миколаївна, Лопухін Юрій Володимирович, Штець Леонід Констянтинович, Лопухін Ярослав Юр'євич

Формула / Реферат

Преобразователь двоично-K-значного кода в двоичный код, содержащий группу из n разрядных регистров сдвига, где n - разрядность входного кода, параллельные информационные входы которых являются входами преобразователя, генератор импульсов, первую группу из (n - 1) триггера состояния, накапливающий сумматор, выполненный из комбинационного двоичного сумматора и регистра результата, формирователь эквиватентов, состоящий из первого шифратора, суммирующего счетчика импульсов, комбинационного сдвигателя, группы элементов И, группы элементов ИЛИ, при этом выходы регистра результата накапливающего сумматора являются преобразователя и соединены с соответствующими вторыми входами комбинационного двоичного сумматора, младшие входы которого являются младшими информационными входами накапливающего сумматора и соединены с соответствующими выходами группы элементов ИЛИ, старшие информационные входы накапливающего сумматора соединены с соответствующими старшими информационными выходами формирователя эквивалентов, выходы комбинационного двоичного сумматора соединены с соответствующими входами регистра результата, синхровход которого соединен с прямым задержанным выходом генератора импульсов, прямой выход которого соединен с синхровходом первой группы триггеров состояния, прямые выходы которых соединены через входы второй информационной группы входов формирователя эквивалентов с соответствующими входами первого шифратора, информационные входы i - го триггера состояния (i = 1, ..., (n - 1)) первой группы соединены с выходами первого бита (i + 1) - го разрядного регистра сдвига, входы сдвига которых соединены с инверсным выходом генератора импульсов, битовые выходы младшего разрядного регистра сдвига соединены через соответствующие биты первой группы входов формирователя эквивалентов с соответствующими первыми входами группы элементов И, выходы которых соединены с соответствующими первыми входами группы элементов ИЛИ, вторые входы которых соединены с соответствующими младшими выходами комбинационного сдвигателя, старшие выходы которого являются соответствующими старшими выходами формирователя эквивалентов, а управляющие входы соединены с соответствующими младшими выходами суммирующего счетчика импульсов, старший выход которого соединен со всеми вторыми входами группы элементов И, а синхровход счетчика соединен с прямым выходом генератора импульсов, отличающийся тем, что в него введена вторая группа из (n - 1) - го триггера состояния, синхровходы которых соединены с прямым выходом генератора импульсов, информационные входы i - го триггера состояния (i = 1, 2, ..., (n - 1)) второй группы соединены с выходами третьего бита (i + 1) - го разрядного регистра сдвига, прямые выходы триггеров состояния второй группы соединены с соответствующими входами третьей информационной группы входов формирователя эквивалентов, в который введены комбинационный двоичный сумматор и второй шифратор, входы которого являются входами третьей информационной группы входов формирователя эквивалентов, а выходы второго шифратора соединены с соответствующими входами второго слагаемого в комбинационном двоичном сумматоре формирователя эквивалентов, входы первого слагаемого комбинационного двоичного сумматора формирователя эквивалентов соединены с соответствующими выходами первого шифратора, выходы комбинационного двоичного сумматора формирователя эквивалентов соединены с соответствующими входами комбинационного сдвигателя, входы сброса триггеров состояния первой группы соединены со старшим информационным выходом суммирующего счетчика импульсов в формирователе эквивалентов.

Текст

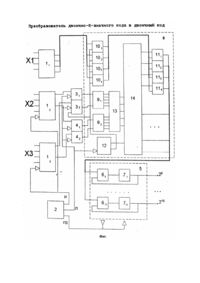

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств обработки и преобразования информации. Известно устройство преобразования кодов (А.св. СССР №1126946, кл. G06F5/02, опубл. 1984, Бюл. №44), содержащее группу разрядных счетчиков, генератор импульсов, группу элементов И, группу триггеров состояния, формирователь эквивалентов, группу дешифраторов нуля и накапливающий сумматор. Описанное устройство не обеспечивает высокое быстродействие, так как имеет один шаг преобразования равный и требует подачи импульсов для преобразования ичного кода. Известен преобразователь двоично ичного кода в двоичный код (А.с. СССР №164908, кл. H03M7/12, опубл. 1991, Бюл.17), содержащий группу разрядных счетчиков, генератор импульсов, первую и вторую группы триггеров состояния, комбинационный двоичный сумматор и регистр результата, образующих в совокупности накапливающий сумматор, труппу элементов И, группу элементов И-НЕ, группу дешифраторов нуля, группу дешифраторов превышения, группу шифраторов, элемент ИЛИ-НЕ, формирователь эквивалентов, включающий в свой состав первый и второй дешифраторы и шифратор, первую и вторую группы элементов И, группу элементов ИЛИ. Известный преобразователь не обеспечивает высокое быстродействие, из-за наличия двух шагов преобразования и и необходимости подачи импульсов для преобразования K-ичного кода, где - величина второго шага, означают округление до меньшего целого, а также требует повышенных аппаратурных затрат при его изготовлении. Известен также преобразователь двоично ичного кода в двоичный код (А.с. СССР №1783618, кл. H03M7/12, опубл. 1992, Бюл. 47), содержащий группу из n разрядных счетчиков, где n - разрядность преобразуемого кода, генератор импульсов, первую, вторую и третью группы триггеров состояния, комбинационный двоичный сумматор и регистр результата, образующих в совокупности накапливающий сумматор, первую и вторую группы элементов И, первую и вторую группу элементов И-НЕ, группу кодовых шифраторов, группу элементов ИЛИ, группу дешифраторов нуля, первую и вторую группу дешифраторов превышения, первый и второй элементы ИЛИ-НЕ, формирователь эквивалентов, включающий в свой состав первый, второй и третий дешифраторы и шифратор, первую вторую и третью группы элементов И, группу элементов ИЛИ. Известный преобразователь не обеспечивает достаточно высокого быстродействия, из-за наличия трех шагов преобразования, и необходимости подачи импульсов для преобразования K-ичного кода. Наиболее близким по совокупности признаков к заявляемому является преобразователь двоично ичного кода в двоичный код (Заявка Украины №96010262, кл. H03M7/12 от 23.01.96, решение о выдаче патента Украины от 05.03.97), содержащий группу из n разрядных регистров сдвига, где n разрядность входного кода, генератор импульсов, группу из го триггера состояния, комбинационный двоичный сумматор и регистр результата, образующих в совокупности накапливающий сумматор, формирователь эквивалентов, включающий в свой состав группу элементов И, группу элементов ИЛИ, шифратор, суммирующий счетчик импульсов, комбинационный сдвигатель. Описанный преобразователь при наличии четырех шагов преобразования достаточно высокого необходимости подачи где - четвертый шаг не обеспечивает быстродействия из-за импульсов при преобразовании ичных чисел В основу изобретения поставлена задача создания такого преобразователя двоично значного кода в двоичный код, в котором новое схемное решение позволило бы при небольшом увеличении аппаратурных затрат существенно повысить его быстродействие. Такой технический результат может быть достигнут, если в преобразователь двоично ичного кода в двоичный код, содержащий группу из n разрядных регистров сдвига, где n - разрядность входного кода, параллельные информационные входы которых являются входами преобразователя, генератор импульсов, первую группу из триггера состояния, накапливающий сумматор, выполненный из комбинационного двоичного сумматора и регистра результата, формирователь эквивалентов, состоящий из первого шифратора, суммирующего счетчика импульсов, комбинационного сдвигателя, группы элементов И, группы элементов ИЛИ, при этом выходы регистра результата накапливающего сумматора являются выходами преобразователя и соединены с соответствующими вторыми входами комбинационного двоичного сумматора, младшие первые входы которого являются младшими информационными входами накапливающего сумматора и соединены с соответствующими выходами группы элементов ИЛИ, старшие информационные входы накапливающего сумматора соединены с соответствующими старшими информационными выходами формирователя эквивалентов, выходы комбинационного двоичного сумматора соединены с соответствующими входами регистра результата, синхровход которого соединен с прямым задержанным выходом генератора импульсов, прямой выход которого соединен с синхровходом первой группы триггеров состояния, прямые выходы которых соединены через входы второй информационной группы входов формирователя эквивалентов с соответствующими входами первого шифратора, информационные входы триггера состояния первой группы соединены с выходами первого бита разрядного регистра сдвига, входы сдвига которых соединены с инверсным выходом генератора импульсов, битовые выходы младшего разрядного регистра сдвига соединены через соответствующие биты первой группы входов формирователя эквивалентов с соответствующими первыми входами группы элементов И, выходы которых соединены с соответствующими первыми входами группы элементов ИЛИ, вторые входы которых соединены с соответствующими младшими выходами комбинационного сдвигателя, старшие выходы которого являются соответствующими старшими выходами формирователя эквивалентов, а управляющие входы соединены с соответствующими младшими выходами суммирующего счетчика импульсов, старший выход которого соединен со всеми вторыми входами группы элементов И, а синхровход счетчика соединен с прямым выходом генератора импульсов, согласно изобретению введена вторая группа из триггера состояния, синхровходы которых соединены с прямым выходом генератора импульсов, информационные входы триггера состояния второй группы соединены с выходами третьего бита разрядного регистра сдвига, прямые выходы триггеров состояния второй группы соединены с соответствующими входами третьей информационной группы входов формирователя эквивалентов, в который комбинационный двоичный сумматор и второй шифратор, входы которого являются входами третьей информационной группы входов формирователя эквивалентов, а выходы второго шифратора соединены с соответствующими входами второго слагаемого в комбинационном двоичном сумматоре формирователя эквивалентов, входы первого слагаемого комбинационного двоичного сумматора формирователя эквивалентов соединены с соответствующими выходами первого шифратора, выходы комбинационного двоичного сумматора формирователя эквивалентов соединены с соответствующими входами комбинационного сдвигателя, входы сброса триггеров состояния первой группы соединены со старшим информационным выходом суммирующего счетчика импульсов в формирователе эквивалентов. Введение в известный преобразователь двоично ичного кода в двоичный код второй группы из триггера состояния, а в формирователь эквивалентов преобразователя второго шифратора и комбинационного сумматора, а также новых связей, позволило, при небольшом увеличении аппаратурных затрат, значительно повысить быстродействие, сократив максимальное число тактов преобразования с пяти до трех. На чертеже (фиг.) приведена структурная схема преобразователя двоично ичного кода в двоичный код при Преобразователь содержит группу из n разрядных регистров сдвига, где n - разрядность входного кода, параллельные информационные входы которых являются входами преобразователя, генератор 2 импульсов, содержащий прямой П, инверсный И, прямой задержанный ПЗ выходы, первую группу из триггера 3 состояния, вторую группу из триггера 4 состояния, накаливающий сумматор 5, выполненный из комбинационного двоичного сумматора 6 и регистра 7 результата, формирователь 8 эквивалентов, состоящий из первого и второго шифраторов, группы элементов И 10, группы элементов ИЛИ 11, суммирующего счетчика 12 импульсов, комбинационного сумматора 13 и сдвигателя 14. Выходы регистра 7 результата являются выходами преобразователя и соединены с соответствующими вторыми входами комбинационного двоичного сумматора 6, младшие первые входы которого являются младшими информационными входами сумматора 5 и соединены с соответствующими выходами группы элементов ИЛИ 11 формирователя 8 эквивалентов, старшие информационные входы накапливающего сумматора 5 соединены с соответствующими старшими информационными выходами формирователя 8 эквивалентов, выходы комбинационного двоичного 6 сумматора соединены со входами регистра 7 результата, синхровход которого соединен с прямым задержанным выходом ПЗ генератора 2 импульсов, прямой выход П которого соединен с синхровходами триггеров состояния первой группы, с синхровходом суммирующего счетчика 12 импульсов, с синхровходами триггеров состояния второй группы, прямые входы которых соединены через входы третьей информационной группы входов формирователя 8 эквивалентов с соответствующими входами второго шифратора выходы которого соединены с соответствующими входами второго слагаемого в комбинационном двоичном сумматоре 13, выходы которого соединены с соответствующими входами комбинационного сдвигателя 14, информационные входы триггера состояния второй группы соединены с выходами третьего бита разрядного регистра сдвига, информационные входы триггера состояния первой группы соединены с выходами первого бита разрядного регистра сдвига, входы сдвига которых соединены с инверсным выходом И генератора 2 импульсов, входы сброса всех триггеров состояния второй группы соединены со старшим информационным выходом суммирующего счетчика 12 импульсов, выходы триггеров состояния первой группы через входы второй информационной группы соединены с соответствующими входами первого шифратора выходы которого соединены с соответствующими входами первого слагаемого a комбинационном двоичном сумматоре 13, выходы которого соединены с соответствующими входами комбинационного сдвигателя 14. Битовые входы младшего разрядного регистра сдвига соединены через соответствующие биты первой группы входов формирователя 8 эквивалентов с соответствующими первыми входами группы элементов И 10, выходы которых соединены с соответствующими первыми входами группы элементов ИЛИ 11, вторые входы которых соединены с соответствующими младшими выходами комбинационного сдвигателя 14, старшие выходы которого являются соответствующими старшими выходами формирователя 8 эквивалентов, управляющие входы сдвигателя 14 соединены с соответствующими младшими выходами суммирующего счетчика 12 импульсов, старший выход которого соединен со всеми вторыми входами элементов И 10 группы. Цепи инициирования и сброса на чертеже не приведены. Устройство работает следующим образом. Так как в конкретном случае то диапазон изменения входного кода от до Группа триггеров 3 состояния фиксирует значение первых битов (выходов) соответствующих старших разрядных регистров 1. Группа триггеров 4 состояния фиксирует значение третьих битов (выходов) соответствующих старших разрядных регистров 1. Код состояний триггеров как первой группы 3, так и второй группы 4 может иметь четыре значения от 00 до 11. В предлагаемом преобразователе двоично-Kзначного кода в двоичный код формирователь эквивалентов 8, выполненный в виде последовательного соединения комбинационного сдвигателя 14, комбинационного сумматора 13, первого и второго шифраторов и а также суммирующего счетчика 12 импульсов с предустановкой, реализует функцию где - второй шаг преобразования (вес второго бита); - третий шаг преобразования (вес третьего бита); - четвертый шаг преобразования (вес четвертого бита); - младшая тетрада преобразуемого целого числа; - номер такта сдвига. Первый шаг преобразования (вес первого бита) равен 1. Формирователь эквивалентов 8 преобразует вначале в первом такте двоичный код триггеров 3 состояния, соответствующих значениям бита 1, соответствующих значениям бита 1 соответствующих старших разрядных регистров 1 и двоичный код триггеров 4 состояния, соответствующих значениям бита 3 соответствующих старших разрядных регистров 1; во втором такте преобразует со сдвигом влево на один разряд (в сторону старших двоичных разрядов) код триггеров 3 состояния, соответствующих значениям бита 2 старших разрядных регистров 1 и двоичный код триггеров 4 состояния, соответствующих значениям бита 4 соответствующих старших разрядных регистров 1, и в третьем такте транслирует (передает без изменения) на выход формирователя 8 эквивалентов младшую тетраду X1 преобразуемого целого числа. При использовании двоично-десятичного кода прямого замещения a = 2, значение эквивалента на выходе формирователя эквивалентов описывается функцией комбинационного сдвигателя 14. Составляющая эквивалента, соответствующая выражению формируется в каждом такте первым шифратором составляющая эквивалента, соответствующая второму выражению формируется в каждом такте вторым шифратором Сложение обоих составляющих выполняется комбинационным двоичным сумматором 13. Рассмотрим работу устройства на следующем примере. Пусть требуется преобразовать трехразрядный входной 12-ричный код числа Формирователь эквивалентов при использовании кода прямого замещения реализует функцию Преобразование двоичных кодов триггеров 3 состояния и двоичных кодов триггеров 4 состояния соответствует закону функционирования формирователя эквивалентов (таблица). В исходном состоянии регистр 7 результата обнулен, на прямом П и прямом задержанном ПЗ выходах генератора 2 - низкий уровень; на инверсном И выходе генератора 2 - высокий уровень. Запись информации в триггеры 3 состояния с первых выходов соответствующих старших разрядных регистров 1 сдвига и запись информации в триггеры 4 состояния с третьих выходов соответствующих старших разрядных регистров 1 сдвига производится перепадом 0 - 1, т.е. по переднему фронту импульсов с прямого выхода П генератора 2; сдвиг вправо (в сторону младших бит) в старших разрядных регистрах 1 также производится перепадом 0 - 1, т.е. по заднему фронту импульсов с инверсного выхода И генератора 2. Первоначальное занесение параллельного двоично-12-ричного кода преобразуемого числа в разрядные регистры 1 и предустановка суммирующего счетчика 12 по mod 3 формирователя эквивалентов 8 в состояние выполняется подачей нулевого сигнала на входы разрядных регистров 1 сдвига и на вход параллельного занесения счетчика 12. Запись информации в регистр результата производится перепадом импульса с прямого задержанного выхода ПЗ генератора 2. С приходом переднего фронта первого положительного импульса с прямого выхода П генератора 2 состояние суммирующего счетчика 12 по mod 3 изменится с на нулевой код триггеров 3 состояния изменится с на Этот код поступит на вторые информационные входы формирователя 8 эквивалентов и преобразуется в где 2 перед квадратной скобкой означает сдвиг влево на один двоичный разряд с помощью двоичный код числа на выходе. Одновременно нулевой код триггеров 4 состояния изменится с Этот код информационные изменится на на входы поступает на третьи формирователя 8 эквивалентов и с помощью второго шифратора преобразуется в двоичный код числа на его выходе. Двоичный комбинационный сумматор 13 в результате сложения составляющих эквивалента и выдаст на выходе двоичный код эквивалента который без изменения (из-за отсутствия сдвига в комбинационном сдвигателе 14) поступит на выходы формирователя эквивалентов 8. Поступая с выхода ПЗ генератора 2 передний фронт первого положительного задержанного импульса ПЗ разрешит сложение чисел и в накапливающем сумматоре 5, а задний фронт этого же импульса произведет запись информации с выходов комбинационного сумматора 6 в регистр 7 результата, установив на вторых суммирующих входах сумматора 6 двоичное значение числа С приходом заднего фронта первого отрицательного импульса с инверсного выхода И генератора 2, т.е. по перепаду на входах синхронизации старших разрядных регистров 1 произойдет сдвиг информации в этих регистрах на один разряд, т.е. в регистрах 1 установится число С приходом переднего фронта второго положительного импульса с прямого выхода генератора 2 состояние суммирующего счетчика 12 изменится с на что приведет к сдвигу влево на один разряд выходного двоичного кода комбинационного сумматора 13 с помощью сдвигателя 14 и к записи в триггеры 3 состояния кода а в триггеры 4 кода В результате на выходах первого и второго шифраторов будут соответственно сформированы двоичные коды чисел и на выходах двоичного комбинационного сумматора появится их сумма Из-за сдвига двоичного кода числа комбинационным сдвигателем 14 на один двоичный разряд (что соответствует умножению числа на 2) на выходах формирователя эквивалентов 8 появится двоичный код числа Передний фронт второго положительного задержанного импульса с выхода ПЗ генератора 2 разрешит сложение чисел и а задний фронт этого же импульса произведет перезапись результата суммирования с выходов двоичного сумматора 6 в регистр 7 результата, установив на вторых суммирующих входах сумматора 6 двоичное значение числа Задний фронт второго отрицательного импульса установит в разрядных регистрах 1 сдвига число С приходом переднего фронта третьего положительного импульса с прямого выхода П генератора 2 в счетчике 12 установится состояние 10, а код триггеров 3 состояния с состояния код триггеров 4 с изменится на Затем после установления в счетчике 12 состояния 10 (единица на старшем выходе), единичный сигнал с этого выхода счетчика 12 поступит на входы сброса регистра 3 состояния и на управляющие входы группы вентилей И10, что приведет к установлению нулевых кодов и и к отпиранию группы элементов И10. В этом случае формирователь эквивалентов 8 транслирует двоичный код младшего разряда преобразуемого числа с разрядного регистра 11 на соответствующие четыре младших входа комбинационного сумматора 6. Передний фронт третьего прямого задержанного ПЗ импульса разрешит сложение чисел и 9, а задний фронт этого же импульса установит двоичный код числа на выходах устройства, установит двоичный код числа на выходах устройства. На этом процесс преобразования заканчивается. Перед каждым следующим преобразованием необходимо обнулить регистр 7 результата и выполнить запись преобразуемого двоично ричного числа в регистры 1 сдвига. Быстродействие предлагаемого устройства не зависит от разрядности преобразуемого кода и для ричной системы счисления не превышает трех тактов.

ДивитисяДодаткова інформація

Автори англійськоюKachurin Mykola Yakovych, Makarenko Hanna Mykolaivna, Lopukhin Yurii Volodymyrovych, Lopukhin Yaroslav Yuriiovych, Shtets Leonid Kostiantynovych

Автори російськоюКачурин Николай Яковлевич, Макаренко Анна Николаевна, Лопухин Юрий Владимирович, Лопухин Ярослав Юрьевич, Штец Леонид Константинович

МПК / Мітки

МПК: H03M 7/02

Мітки: двійково-к-значного, код, перетворювач, коду, двійковий

Код посилання

<a href="https://ua.patents.su/5-24674-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-u-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду у двійковий код</a>