Пристрій для моделювання нейрона

Номер патенту: 46470

Опубліковано: 25.12.2009

Автори: Ботвин Роман Ігорович, Куперштейн Леонід Михайлович, Хаїмзон Ігор Ізєвич, Мартинюк Тетяна Борисівна

Формула / Реферат

Пристрій для моделювання нейрона, який містить формувачі вхідних сигналів, входи яких є входами пристрою, блоки задання вагових коефіцієнтів, два тригери, генератор імпульсів, два елементи І, два елементи АБО, елемент затримки, два формувачі спайок, причому вхід лічби першого тригера з'єднаний з першим входом першого елемента І, його вхід встановлення нуля з'єднаний з виходом першого елемента І, а вихід тригера підключений до першого входу другого елемента І, другий вхід якого з'єднаний з виходом генератора, а вихід підключений до перших входів першого і другого елементів АБО і до входу елемента затримки, вихід якого з'єднаний з другим входом першого елемента АБО і входом першого формувача спайок, вихід якого є аксонним виходом пристрою, а вихід другого елемента АБО з'єднаний з входом другого формувача спайок, вихід якого є соматичним виходом пристрою, вихід першого елемента АБО з'єднаний з входом лічби другого тригера, вихід якого з'єднаний з другим входом першого елемента І, який відрізняється тим, що в нього введено перетворювачі частоти в код, перетворювач коду в частоту і адаптивний суматор, входи якого з'єднані відповідно з виходами блоків задання вагових коефіцієнтів, а вихід з'єднаний з входом перетворювача коду в частоту, вхід задання порогу, адресний вхід та вхід керування адаптивного суматора з'єднані з відповідними входами пристрою, виходи формувачів вхідних сигналів з'єднані відповідно з входами перетворювачів частоти в код, виходи яких з'єднані відповідно з входами блоків задання вагових коефіцієнтів, вихід перетворювача коду в частоту з'єднаний з входом лічби першого тригера і другим входом другого елемента АБО.

Текст

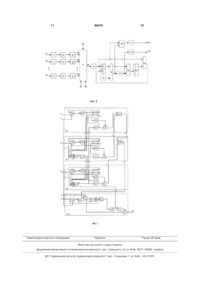

Пристрій для моделювання нейрона, який містить формувачі вхідних сигналів, входи яких є входами пристрою, блоки задання вагових коефіцієнтів, два тригери, генератор імпульсів, два елементи І, два елементи АБО, елемент затримки, два формувачі спайок, причому вхід лічби першого тригера з'єднаний з першим входом першого елемента І, його вхід встановлення нуля з'єднаний з виходом першого елемента І, а вихід тригера підключений до першого входу другого елемента І, другий вхід якого з'єднаний з виходом генератора, а вихід підключений до перших входів першого і другого елементів АБО і до входу елемента затримки, вихід якого з'єднаний з другим входом U 2 (19) 1 3 вих коефіцієнтів, виходи яких з'єднані з входами суматора, функціональний перетворювач з трапецеїдальною амплітудною характеристикою і перетворювач напруги в частоту, вихід якого є виходом пристрою, а вхід з'єднаний з виходом функціонального перетворювача, вхід якого з'єднаний з виходом суматора, два тригера, генератор імпульсів, два елементи І, два елементи АБО, елемент затримки, два формувачі спайків, причому вхід лічби першого тригера з'єднаний з виходом перетворювача напруги в частоту і першим входом першого елемента І, його вхід встановлення нуля з'єднаний з виходом елемента І, а вихід тригера підключений до першого входу другого елемента І, другий вхід якого з'єднаний з виходом генератора, а вихід підключений до перших входів першого і другого елементів АБО і до входу елемента затримки, вихід якого з'єднаний з другим входом першого елемента АБО і входом першого формувача спайків, вихід якого є аксонним виходом пристрою, другий вхід другого елемента АБО з'єднаний з виходом перетворювача напруги в частоту, а вихід другого елемента АБО з'єднаний з входом другого формувача спайків, вихід якого є соматичним виходом пристрою, вихід першого елемента АБО з'єднаний з входом лічби другого тригера, вихід якого з'єднаний з другим входом першого елемента І. Недоліком даного пристою є складність його реалізації. В основу корисної моделі поставлено задачу створення пристрою для моделювання нейрона, в якому за рахунок введення нового блока з розширеними функціональними можливостями та нових зв'язків досягається спрощення структури пристрою. Поставлена задача вирішується тим, що у пристрій для моделювання нейрона, який містить формувачі вхідних сигналів, входи яких є входами пристрою, блоки завдання вагових коефіцієнтів, два тригера, генератор імпульсів, два елементи І, два елементи АБО, елемент затримки, два формувачі спайків, причому вхід лічби першого тригера з'єднаний з першим входом першого елемента І, його вхід встановлення нуля з'єднаний з виходом першого елемента І, а вихід тригера підключений до першого входу другого елемента І, другий вхід якого з'єднаний з виходом генератора, а вихід підключений до перших входів першого і другого елементів АБО і до входу елемента затримки, вихід якого з'єднаний з другим входом першого елемента АБО і входом першого формувача спайків, вихід якого є аксонним виходом пристрою, а вихід другого елемента АБО з'єднаний з входом другого формувача спайків, вихід якого є соматичним виходом пристрою, вихід першого елемента АБО з'єднаний з входом лічби другого тригера, вихід якого з'єднаний з другим входом першого елемента І, введено перетворювачі частоти в код, перетворювач коду в частоту і адаптивний суматор, входи якого з'єднані відповідно з виходами блоків завдання вагових коефіцієнтів, а вихід з'єднаний з входом перетворювача коду в частоту, вхід завдання порогу, адресний вхід та вхід керування адаптивного суматора з'єднані з відповідними входами пристрою, виходи форму 46470 4 вачів вхідних сигналів з'єднані відповідно з входами перетворювачів частоти в код, виходи яких з'єднані відповідно з входами блоків завдання вагових коефіцієнтів, вихід перетворювача коду в частоту з'єднаний з входом лічби першого тригера і другим входом другого елемента АБО. На фіг. 1 представлено структурну схему пристрою для моделювання нейрона, на фіг. 2 наведено функціональну схему адаптивного суматора. Пристрій для моделювання нейрона (фіг. 1) містить формувачі 1і,...,1n вхідних сигналів, перетворювачі 21,..,2n частоти в код, блоки 31,...,3n завдання вагових коефіцієнтів, де n - кількість вхідних сигналів пристрою, адаптивний суматор 4, інформаційні входи 51, ...,5n пристрою, перетворювач 6 коду в частоту, перший тригер 7, другий елемент І 8, генератор 9 імпульсів, другий елемент АБО 10, другий формувач 11 спайків, соматичний вихід 12 пристрою, елемент 13 затримки, аксонний вихід 14 пристрою, перший формувач 15 спайків, перший елемент АБО 16, другий тригер 17 і перший елемент І 18. Адаптивний суматор 4 має входи 191,...,19n, вхід 20 завдання порогу, адресний вхід 21, вхід 22 керування і вихід 23. Формувачі 11,...,1n вхідних сигналів, входи яких є інформаційними входами 51,...5n пристрою відповідно, послідовно з'єднані з перетворювачами 21,...,2n частоти в код і блоками 31,...,3n завдання вагових коефіцієнтів, виходи яких з'єднані відповідно з входами 191,...19n адаптивного суматора 4, вихід 23 якого з'єднаний з входом перетворювача 6 коду в частоту. Вхід лічби першого тригера 7 з'єднаний з виходом перетворювача 6 коду в частоту і першим входом першого елемента І 18, його вхід встановлення нуля з'єднаний з виходом першого елемента І 18, а вихід тригера 7 підключений до першого входу другого елемента І 8. Другий вхід другого елемента І 8 з'єднаний з виходом генератора 9 імпульсів, а вихід підключений до перших входів першого 16 і другого 10 елементів АБО і до входу елемента 13 затримки. Вихід елемента 13 затримки з'єднаний з другим входом першого елемента АБО 16 і входом першого формувача 15 спайків, вихід якого є аксонним виходом 14 пристрою. Другий вхід другого елемента АБО 10 з'єднаний з виходом перетворювача 6 коду в частоту, а вихід другого елемента АБО 10 з'єднаний з входом другого формувача 11 спайків, вихід якого є соматичним виходом 12 пристрою. Вихід першого елемента АБО 16 з'єднаний з входом лічби другого тригера 17, вихід якого з'єднаний з другим входом першого елемента 118. Адаптивний суматор 4 (фіг. 2) містить (n+1) комірок 24, причому і - та комірка 24 містить мультиплексор 25, регістр 26, суматор - віднімач 27, суматор 28, D - тригер 29, мініматор 30, два регістри 31, 32, комутатор 33. Перший інформаційний вхід мультиплексора 25 з'єднаний з входом 19i і-ої комірки 24, керуючий вхід з'єднаний з адресним входом 21 пристрою, а його вихід підключено до входу 34 регістра 26, в якого вихід з'єднаний з прямим входом 35 суматора - віднімача 27 та інформаційним входом 36 мініматора 30. Вихід регістра 32 і-ої комірки 24 з'єднаний з інформаційним входом комутатора 33 та інверсним входом 37 5 суматора - віднімача 27, вихід 38 якого з'єднаний з другим інформаційним входом мультиплексора 25, а вихід 39 знака суматора - віднімача 27 з'єднаний зі знаковим входом 40 мініматора 30 і D - входом D - тригера 29, інверсний вихід якого з'єднаний з керуючим входом комутатора 33. Вихід комутатора 33 підключено до виходу 41 і-ої комірки 24, крім того, інформаційний вхід 42 мініматора 30 і-ої комірки 24 з'єднаний з виходом 43 (і-1) - ої комірки 24, вхід 44 суматора 28 і-ї комірки 24 з'єднаний з виходом 45 (і-1) - ої комірки 24, а вхід 46 підключено до виходу 41 (і+1) – ої комірки 24. В і-й комірці 24 вхід регістра 32 підключено до входу 47 цієї комірки 24, вихід 48 мініматора 30 з'єднаний з входом регістра 31 цієї комірки, інформаційний вихід якого є виходом 43 і-ої комірки 24, а його вихід знака є виходом 49 і-ої комірки 24, який з'єднаний зі знаковим входом 50 мініматора 30 (і+1) - ої комірки 24, а вихід 48 мініматора 30 nої комірки 24 підключений до входів 47 всіх (n-1) молодших комірок 24. У першій комірці 24 вихід регістра 26 є виходом 43 першої комірки 24, вихід 39 знака суматора - віднімача 27 є її виходом 49, а вхід 44 суматора 28 з'єднаний з виходом комутатора 33 цієї ж комірки 24. Вихід 48 мініматора 30 nої комірки 24 з'єднаний з входом регістра 32 цієї комірки, а його вихід ознаки нуля є виходом 51 n-ої комірки 24. Старша (n+1) - а комірка 24 містить мультиплексор 25, регістр 26, суматор - віднімач 27, D тригер 29, комутатор 33, елементи АБО 52 і І 53, комутатор 54. Перший інформаційний вхід мультиплексора 25 (n+1) - ї комірки 24 з'єднаний з входом 20 завдання порогу пристрою, керуючий вхід з'єднаний з адресним входом 21 пристрою, а його вихід підключено до входу 34 регістра 26, вихід якого з'єднаний з прямим входом 35 суматора віднімача 27 цієї комірки 24, вихід 38 якого з'єднаний з другим інформаційним входом мультиплексора 25 цієї комірки 24. Вихід 45 (n-1) - ї комірки 24 з'єднаний з інформаційним входом комутатора 33 (n+1) - ї комірки 24, його керуючий вхід з'єднаний з керуючим входом 22 пристрою, а його вихід з'єднаний з інверсним входом 37 суматора - віднімача 27 цієї комірки 24, вихід 39 знака якого з'єднаний з першим входом елемента АБО 52, а вихід 55 ознаки нуля з'єднаний з другим входом елемента АБО 52. Вихід елемента АБО 52 з'єднаний 3D входом D - тригера 29 (n+1) - ої комірки 24, прямий вихід якого з'єднаний з першим входом елемента І 53 цієї комірки 24, другий вхід якого з'єднаний з виходом 51 n-ої комірки 24, а його вихід підключений до керуючого входу комутатора 54. Інформаційний вхід комутатора 54 (n+1) - ої комірки 24 з'єднаний з виходом регістра 26 цієї комірки 24, а його вихід є виходом 23 адаптивного суматора 4. Пристрій для моделювання нейрона (фіг. 1) працює таким чином. На збуджуючі входи формувачів 11,...,1n вхідних сигналів поступають відповідно вхідні імпульсні послідовності спайків з інформаційних входів 51,...,5n пристрою. У формувачах 11,...,1n вхідних сигналів відбувається їх стандартизація за амплітудою і тривалістю, далі відбувається відповідно перетворення їх в код, величина якого пропорційна частоті, в перетворювачах 46470 6 21,...,2n частоти в код, і масштабування в блоках 31,...,3n завдання вагових коефіцієнтів відповідно до ваги синапсу. Перетворені таким чином сигнали подаються на відповідні входи 191,...,19n, підсумовуються і обробляються за порогом зі входу 20 в адаптивному суматорі 4. При цьому задіяно адресний вхід 21 і вхід 22 керування адаптивного суматора 4. Результуючий сигнал з виходу 23 адаптивного суматора 4 поступає на вхід перетворювача 6 коду в частоту, при цьому на його виході з'являються прямокутні імпульси, частота яких пропорційна величині коду на виході 23 адаптивного суматора 4. Імпульс, сформований на виході перетворювача 6 коду в частоту, подається на вхід лічби першого тригера 7 і встановлює його в одиничний стан. В результаті одиничний сигнал з виходу першого тригера 7 подається на перший вхід другого елемента І 8 і є дозволяючим для напруги з виходу генератора 9 імпульсів, яка у вигляді послідовності прямокутних імпульсів проходить на вихід другого елемента І 8. Ця послідовність, надходячи через перший вхід другого елемента АБО 10 і доповнюючись в ньому з імпульсами з виходу перетворювача 6 коду в частоту, подається на вхід другого формувача 11 спайків, де перетворюється в імпульси, близькі за формою до спайків, і поступає на соматичний вихід 12 пристрою. Сигнали з виходу другого елемента І 8 також, затримуючись в елементі 13 затримки на час , поступають на аксонний вихід 14 пристрою через перший формувач 15 спайків, і є аксонними розрядами пристрою. Крім того, ця аксонна послідовність розрядів з виходу елемента 13 затримки поступає на другий вхід першого елемента АБО 16, на перший вхід якого поступають імпульси з виходу другого елемента І 8. Під час подачі імпульсу з виходу другого елемента І 8 через перший вхід першого елемента АБО 16 на вхід лічби другого тригера 17 відбувається встановлення його в одиничний стан переднім фронтом імпульсу. Через час затримки т елемента 13 затримки цей імпульс з'являється на його виході і також поступає на вхід лічби другого тригера 17, встановлюючи його переднім фронтом в нульовий стан. Далі, з виходу другого елемента І 8 подається наступний імпульс через час Т щодо першого, визначеного частотою генерації генератора 9 імпульсів, і процеси повторюються. При цьому другий тригер 17 перемикається по черзі імпульсами з виходу другого елемента І 8 і виходу елемента 13 затримки. Під час подачі на вхід лічби першого тригера 7 наступного імпульсу з виходу перетворювача 6 коду в частоту, викликаного синаптичним збудженням через час Т1, яке є обернено пропорційним величині коду з виходу 23 адаптивного суматора 4, можливі два випадки. До подачі імпульсу після чергового затриманого імпульсу на виході елемента 13 затримки і до моменту надходження наступного імпульсу з виходу другого елемента І 8, імпульс з виходу перетворювача 6 коду в частоту поступає на перший вхід першого елемента І 18, на другому вході якого напруга з виходу першого тригера 17 у цей момент дорівнює нулю, в наслідок чого сигнал на виході 7 46470 першого елемента I 18 також рівний нулю і скидання першого тригера 7 в нульовий стан не відбувається. У зв'язку з цим описані процеси продовжують повторюватися, оскільки імпульс, що прийшов з виходу перетворювача 6 коду у частоту, не впливає на них. При цьому на соматичному виході 12 пристрою формується імпульсна послідовність з частотою імпульсів з генератора 9 імпульсів, з накладеною на неї послідовністю імпульсів з виходу перетворювача 6 коду в частоту, а на аксонному виході 14 пристрою - послідовність з виходу другого елемента І 8, але зміщена на T 2. Таким чином, між двох тригерних зон виникає автогенерація спайків, імпульс синаптичного походження (з виходу перетворювача 6 коду в частоту) є таким, що лише запускає процес. В даному випадку новий імпульс з виходу перетворювача 6 коду в частоту приходить в момент, коли черговий аксонний імпульс вже виник в аксонній зоні і рухається йому назустріч у бік соми. Оскільки зворотне розповсюдження аксонного імпульсу електротонічне, тобто зі значним згасанням, то блокування соматичного імпульсу з виходу перетворювача 6 коду в частоту не відбувається, а результуючий імпульс від взаємодії цих двох імпульсів зберігає напрям руху імпульсу з виходу перетворювача 6 коду в частоту, тобто убік аксонної тригерної зони, і знов запускає її, внаслідок чого процеси генерації між двома зонами не зриваються. Суть роботи адаптивного суматора 4 (фіг. 2) полягає в тому, що порогове оброблення n чисел зводиться до обчислення і підсумовування N часткових сум S , де N - кількість різноманітних вхідних величин аi, порівняння цих сум з порогом Θ і формування вихідних даних вигляду: n Y S , якщо S N ai i 1 N Sj j 1 q jd j , j 1 (1) де Y - результат оброблення пристрою; qj - загальна значуща частина доданків (мінімальний елемент) j-гo етапу; dj - кратність загальної частини q на j-му етапі; Θ - значення порогу оброблення, j - етап оброблення. Процес порогового оброблення в адаптивному суматорі 4 має такий вигляд. Спочатку визначається загальна значуща частина qj всіх доданків на j-му етапі оброблення, тобто: 0 у протилежно му випадку , qj min ai, j n 1 i 1, j 1N , , (2) де аi, 0 - і-й доданок на вході суматора 4, і перевіряється умова: qj=0. (3) Якщо умова (3) виконується, то процес оброблення припиняється. У протилежному випадку виділяється різницевий зріз Аj, тобто сукупність величин різниці всіх доданків j-гo етапу з їхньою загальною частиною qj: Aj ai, j n i 1 ai, j 1 qj n i 1. (4) 8 В подальшому отриманий різницевий зріз Aj є вхідною множиною доданків для наступного (j+1)гo етапу оброблення. Далі формується часткова сума Sj як кратне загальної частини qj де кратність dj визначається кількістю додатних доданків j-гo етапу: Sj=qjdj (5) Після сформування часткової суми S1, за формулою (5) на першому етапі формується різниця між заданим порогом Θ та частковою сумою S1, отриманою на цьому етапі, тобто: (6) 1=Θ-S1, перевіряється умова (7) 1 0 і в разі її виконання перевіряється виконання умови (3). Якщо обидві умови виконуються, то формується відповідний результат Y пристрою (1) і порогове оброблення припиняється. Якщо умова (3) не виконується, то процес порогового оброблення продовжується і в подальшому поточна різниця j-1, є поточним значенням порогу на наступному j - му етапі оброблення, тобто (8) j= j-1-Sj На j-му етапі перевіряється умова (9) j 0. Процес порогового оброблення повторюється до визначення нульової величини qj (3). Виконання умови (3) свідчить про закінчення процесу і про формування остаточного результату Y порогового оброблення (1). Отже, адаптивний суматор 4 (фіг. 2) працює таким чином. На вхід 19; і-ої комірки 24 надходить і-й операнд аі,0 з групи операндів, кількість яких n. Запис операндів в комірки 24 виконується паралельно за наявністю одиничного сигналу на адресному вході 21 адаптивного суматора 4. Через мультиплексор 25 і-й операнд аi,0 надходить на вхід 34 регістра 26 і-ої комірки 24. Одночасно на вхід 20 порогу подають зовнішний поріг 0, який через мультиплексор 25 (n+1) - ої комірки 24 надходить по входу 34 в регістр 26 цієї комірки 24. Після цього виконується послідовне виділення загальної (мінімальної значущої) частини двох операндів - (і - 1) - го та і - го мініматором 30 і запис результату в регістр 31 і - ої комірки 24 з виходу 48 мініматора 30, i 2,n . Згідно з виразом (2) ця операція виконується послідовно, починаючи з другої комірки 24. Кінцевий результат q1 виділення загальної частини всіх n операндів на першому етапі формується в n-ій комірці 24 і з виходу 48 мініматора 30 цієї комірки 24 записується в регістри 32 всіх n комірок 24 паралельно по входу 47. Після цього в і-й комірці 24 відбувається порівняння в суматорі - віднімачі 27 і-го операнда аi,0, що надходить з регістра 26 на його прямий вхід 35, та загальної частини q1 всіх операндів, що надходить з регістра 32 на його інверсний вхід 37. Порівняння відбувається в процесі віднімання від величини операнда загальної частини всіх величин операндів згідно з виразом (4) і ця різниця записується з виходу 38 суматора - віднімача 27 через мультиплексор 25 в регістр 26 по його входу 34 за наявністю нульового сигналу на адресному вході 9 46470 21 адаптивного суматора 4. При цьому на виході 39 знака суматора - віднімача 27 формується знак різниці. Перед початком роботи регістри 26, 31, 32 і тригер 29 всіх комірок 24 занулені. При відсутності одиничного сигналу знака від'ємного результату одиничний сигнал з інверсного виходу D - тригера 29 подається на керуючий вхід комутатора 33 і дозволяє проходження в і - й комірці через комутатор 33 загальної частини q1 операндів з регістра 32 на вхід 46 суматора 28 (і-1) - ої комірки 24, де відбувається накопичування загальної частини операндів. У випадку, якщо на виході 39 знака суматора - віднімача 27 і-ої комірки 24 з'явиться одиничний сигнал знака від'ємного результату, то наявність нульового сигналу на інверсному виході D - тригера 29, а отже, на керуючому вході комутатора 33 заборонить надходження загальної частини q1 операндів на даному етапі оброблення через комутатор 33 на вхід 46 суматора 28 (і-1) - ої комірки 24. В суматорі 28 кожної комірки 24, крім n-ої і (n+1) - ої комірок 24, відбувається послідовне підсумовування загальних частин q1 групи з n операндів, в результаті чого на виході суматора 28 (n-1) - ої комірки 24, тобто на виході 45 цієї комірки 24 формується часткова сума S1 операндів згідно з виразом (5). Після цього відбувається порівняння в суматорі-віднімачі 27 (n+1) - ї комірки 24 зовнішнього порогу Θ, що надходить по його прямому входу 35 з регістра 26, та часткової суми S1, що надходить по його інверсному входу 37 з виходу комутатора 33. Порівняння відбувається в процесі віднімання у першому циклі від зовнішнього порогу Θ часткової суми S1 згідно з виразом (6) за наявністю одиничного сигналу на вході 22 керування. 10 Різниця 1 записується з виходу 38 суматора - віднімача 27 (n+1) - ої комірки 24 через мультиплексор 25 у регістр 26 по його входу 34 за наявністю нульового сигналу на адресному вході 21 адаптивного суматора 4. Сигнали з виходу 39 знака і виходу 55 ознаки нуля суматора-віднімача 27 (n+1) - ої комірки 24 подаються через елемент АБО 52 на D - вхід D тригера 29 (n+1) - ої комірки 24. При цьому при наявності одиничного сигналу на одному з виходів: виході 39 знака або виході 55 ознаки нуля суматора - віднімача 27 одиничний сигнал з прямого виходу D - тригера 29 подається на один з входів елемента І 53. В подальшому процес порогового оброблення виконується аналогічно першому етапу оброблення згідно з формулами (2) - (5) та (8), (9) і припиняється тоді, коли загальна значуща частина qj всіх поточних доданків на j - му етапі дорівнює нулю за виразом (3), а саме, коли присутній одиничний сигнал на виході 51 n - ої комірки 24, тобто на виході ознаки нуля мініматора 30 цієї комірки 24. При виконанні умови (3) після виконання N етапів оброблення у регістрі 26 (n+1) - ої комірки 24 формується результат Y оброблення вигляду (1), який з'являється на виході 23 адаптивного суматора 4, оскільки на обидва входи елемента І 53 (n+1) - ої комірки 24 надходять одиничні сигнали, які формують одиничний сигнал на керуючому вході комутатора 54 цієї комірки 24. У табл. 1 наведено приклад порогового оброблення чисел масиву {13, 8, 3, 11}, а саме часткових сум Sj, поточного порогу j, результату Y. Таблиця 1. Різницеві зрізи Aj Елементи ai,j зрізів a1,j a2,j а3,j a4,j Етапи оброблення Найменше число qj Часткова сума Sj Поточний поріг j Результат Y А0 А1 А2 А3 А4 А5 13 8 3 11 0 0 0 30 0 10 5 0 8 1 3 3x4=12 30-12=18 0 5 0 3 2 5 5x3=15 18-15=3 0 2 0 3 3 3x2=6 3-6=-3 0 0 4 2 2x1=2 -3-2=-5 0 0 5 0 0 -5 5 Пропонований пристрій для моделювання нейрона має спрощену структуру, оскільки введення адаптивного суматора з розширеними функціональними можливостями, який крім підсумовування виконує також порівняння результату підсумовування з порогом, знімає потребу у наявності суматора і функціонального перетворювача з трапецеїдальною амплітудною характеристикою, який має складну структуру та значні апаратні затрати. 11 Комп’ютерна верстка І.Скворцова 46470 Підписне 12 Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for neurone modeling

Автори англійськоюMartyniuk Tetiana Borysivna, Khaimzon Ihor Izevych, Kupershtein Leonid Mykhailovych, Botvyn Roman Ihorovych

Назва патенту російськоюУстройство для моделирования нейрона

Автори російськоюМартынюк Татьяна Борисовна, Хаимзон Игорь Изевич, Куперштейн Леонид Михайлович, Ботвин Роман Игоревич

МПК / Мітки

МПК: G06G 7/60

Мітки: нейрона, моделювання, пристрій

Код посилання

<a href="https://ua.patents.su/6-46470-pristrijj-dlya-modelyuvannya-nejjrona.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання нейрона</a>

Попередній патент: Спосіб прогнозування індивідуальної стійкості щурів до гострого емоційного стресу

Наступний патент: Модульний гідророзподільник

Випадковий патент: Багатокаскадний iir-фільтр і розпаралелена фільтрація даних таким