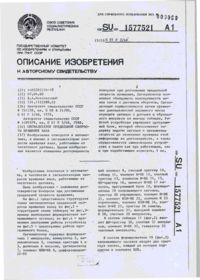

Аналого-цифровий перетворювач

Номер патенту: 9083

Опубліковано: 30.09.1996

Автори: Лаврентьєв Василь Миколайович, Клочан Петро Степанович

Формула / Реферат

1. Аналого-цифровой преобразователь, содержащий первый блок формирования уровней квантования, выход которого соединен с первым входом первого квантователя, второй вход которого является шиной преобразуемого сигнала, а выход соединен с информационным входом первого регистра и первым входом блока управления, первый выход которого соединен со стробирующим входом первого регистра, второй регистр, выходы . которого являются выходной шиной, генератор парафазных сигналов, первый преобразователь напряжение - код, отличающийся тем, что, с целью повышения точности, в него введены два секционированных блока задержки, два коммутатора, второй блок формирования уровней квантования, второй квантователь, второй преобразователь напряжение - код, два блока элементов И, элемент ИЛИ и третий регистр, причем первый выход генератора парафазных сигналов соединен с первым информационным входом первого коммутатора и входом первого блока задержки, выходы которого соединены с соответствующими вторыми информационными входами первого коммутатора, второй выход генератора парафазных сигналов соединен с первым информационным входом второго коммутатора и входом второго блока задержки, выходы которого соединены с соответствующими вторыми информационными входами второго коммутатора, выход которого через второй блок формирования уровней квантования соединен с первым входом второго квантователя и непосредственно с информационным входом первого преобразователя напряжение - код, выход первого коммутатора соединен с входом первого формирователя уровней квантования и информационным входом второго преобразователя напряжение - код, стробирующий вход которого соединен с первым выходом блока управления, а выходы соединены соответственно с первыми входами первого блока элемента И, второй вход блока управления объединен с информационным входом третьего регистра и соединен с выходом второго квантователя, второй вход которого объединен с вторым входом первого квантователя, второй выход блока управления соединен со стробируемыми входами первого преобразователя напряжение - код и третьего регистра, выход которого и выходы первого преобразователя напряжение - код соединены соответственно с первыми и вторыми входами второго блока элементов И, выходы первого регистра соединены с соответствующими вторыми входами- первого блока элементов И, третьи входы первого и второго блоков элементов И соединены соответственно с третьим и четвертым выходами блока управления, пятый и шестой выходы которого соединены соответственно с управляющими входами первого и второго коммутаторов, выходы первого и второго блоков элементов И соединены через элемент ИЛИ с информационным входом второго регистра, строби-рующий вход которого соединен с седьмым выходом блока управления. 2. Преобразователь по п. 1, отличающийся тем, что блок управления выполнен на элементе ИЛИ, двух формирователях коротких импульсов, двух. RS-триггерах, двух элементах И, двух цифровых компараторах идвух инверторах, первый вход первого инвертора объединен с первым входом первого цифрового компаратора и является первым входом блока, а выход инвертора соединен с вторым входом цифрового компаратора, выход которого соединен с первым входом первого элемента И и является первым выходом блока, второй вход первого элемента И соединен с инверсным выходом первого RS-триггера, а выход соединен с S-входом второго RS-триггера, R-вход которого объединен с-R-входом первого RS-триггера и соединен с выходом элемента ИЛИ, который является седьмым выходом блока, инверсный выход второго RS-триггера соединен с первым входом второго элемента И, прямой выход является третьим выходом блока и соединен с входом первого формирователя коротких импульсов, выход которого является пятым выходом блока и соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго формирователя коротких импульсов, который является шестым выходом блока, вход второго формирователя коротких импульсов соединен с прямым выходом первого RS-триггера, который является четвертым выходом блока, S-вход первого RS-триггера соединен с выходом второго элемента И, второй вход которого соединен с выходом второго цифрового компаратора, который является вторым выходом блока, первый вход цифрового компаратора объединен с входом второго инвертора и является вторым входом блока, а второй вход соединен с выходом второго инвертора.

Текст

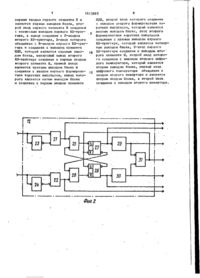

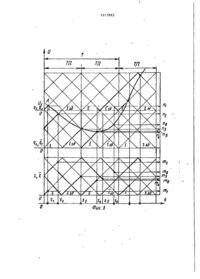

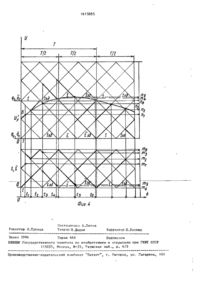

СОЮЗ СОБЕТСНИХ СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИН ( 5 1 ) 5 Н 03 М 1/3$ ГОСУДАРСТВЕННЫЙ НОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР f (21) 4 4 2 7 * ^ 1 / 2 4 - 2 4 (22) 16.05,88 (46) (71) им. (72) 23,12.90, Бюл, № 47 Институт кибернетики , В.М.Глугакова ІЬС.Клочан и В.Н.Лаврентьев (53) 681,325 (088,8) (56) Авторское свидетельство СССР № 762170, к л . Н 03 М 1/52, 1976. Авторское свидетельство СССР № 89270ч, к л . Н 03 М 1/52, 1977. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобр-етение относится к вычисли тельной технике и может быть использовано в системах преобразования формы информации. Изобретение п о з воляет повысить точность. Это д о с т и гается тем, что в устройство, с о д е р жащее блок 6 формирования уровней квантования, квантователь 8, регистр 13, преобразователь 10 напряжениекод, регистр 18, блок 12 управления, генератор 1 парафазиых сигнален в в е дены коммутаторы 4, 5, блоки 2, 3 задержки,, блок 7 формирования уровней квантования, квантователь 9, п р е образователь 11 напряжение - код, регистр 14, блок элементов И 15, 16 элемент ИЛИ 17. 1 з . п о ф-лы, 4 и л . ' ч Фае. 1 •к 1615885 Изобретение относится к вычислительной технике и может быть использовакс s системах преобразования формь информации» Дел» изобретения - повышение точности „ На фиг0 1 приведена функциональная схема преобразователя; на фигu 2 - функциональная схема блока управления; на фиг, 3 и 4 - временные диаграммы работы преобразователя„ Преобразователь (фиг.1) содержит генератор 1 ларафазных сигналов, блоки 2 и 3 задержки, коммутаторы 4 и 5, блоки 6 и 7 формирования уровней квантования, квантователи 8 и 9, преобразователи 10 и 11 напряжение код, блок 12 управления, регистры 13 и 14, блоки 15 и 16 элементов И, элемент И И 17, регистр 18, шину 19 Л преобразуемого сигнала, выходную шину 20. Б момент равенства преобразуемого сигнала с одним из модулированных уровней происходит переключение со5 ответствующего компаратора квантователя 8 или квантователя 9. На выходе соответствутощего квантователя, например на выходе квантователя 8, и з меняется сигнал. Этот сигнал воздейст10 вует на первый вход блока 12. Под воздействием этого сигнала на первом выходе блока 12 появляется импульс, стробирующий преобразователь 10 и регистр 13, в результате чего цифроJ5 вое значение квантованной величины преобразуемого сигнала считывается из квантователя 8 и записывается в регистр 13, где осуществляется также дешифрация унитарного кода в парал20 лельный двоичный код. Одновременно с этим преобразователем 10 определяется цифровое значение вспомогательного сигнала, соответствующее его Блок управления (фиг,2) содержит величине в момент срабатывания компацифровые компараторы 21 и 22, инвер- 25 ратора квантователя 8. Под воздейстторы 23 и 24, элементы И 25 и 26, вием импульса с третьего выхода блоRS-триггеры 27 и 28, формирователи ка 12 на третий вход блока 15 цифро29 и 30 коротких импульсов, элемент вые значения с выхода преобразоваИ И 31 . Л теля 10 и регистра 13 поступают через На диаграммах (фиг- 3 и 4) обозна- Q блок 15 и элемент И И 17 на регистр Л чено: q* и q# ~ уровни квантования 18. Запись результата аналого-цифроквантователя 8', 7\{i Чл ~ Уровни кванвого преобразования в регистр 18 тования квантователя 9J 1, 1 - паосуществляется при появлении импульрафазные сигналы генератора 1 ^ 1,д, са на седьмом выходе блока 12. log - эти же задержанные сигналы, Перед появлением импульса на седь35 Аналого-цифровой преобразователь мом выходе блока 12 импульсом на пятом работает следующим образом, выходе этого блока коммутатор 4 В исходном состоянии на выходах переключается на второй канал. Нагенератора 1 сигналы отсутствуют, чинается НОБЫЙ цикл аналого-цифровона выходах блоков б и 7 установлены го преобразования, в котором аналого40 уровни квантования, которые воздей цифровой преобразователь работает ствуют на первые входы соответственаналогично рассмотренному. но квантователей 8 и 9. На вторые В случае, если в первом цикле входы квантователей 8 и 9 воздейстаналого-цифрового преобразования вует преобразуемый сигнал. перекпючение соответствующего компаПреобразование начинается с появ- 4 5 ратора квантователя 9 происходит лением сигналов на выходах генератораньше, чем переключение соответстра 1 . Сигнал с первого выхода геневующего компаратора квантователя 8, ратора 1 поступает через первый като отличием от рассмотренного в ранал коммутатора 4 на вход блока 6 боте аналого-цифрового преобразоваи вход преобразователя 10. Этим 50 теля будет лишь т о , что управляющие сигналом модулируются уровни квантосигналы будут появляться соответствания квантователя 8, Одновременно венно на втором входе, втором, четс этим с второго выхода генератора 1 вертом и шестом выходах блока 12 и через первый канал коммутатора 5 на воздействовать на соответствующие вход блока 7 и вход преобразователя 55 входы соответственно преобразовате11 поступает сигнал, парафазный сигля 11, регистра 14, блока 16 и комналу на первом выходе генератора 1. мутатора 5« Этим сигналом модулируются уровни После окончания второго цикла квантователя 9. начинается третий цикл аналого-циф э 16 і 5885 * рового преобразователя и т . д . В кон-~ с соответствующими вторыми инЗормаце каждого цикла осуществляется ционными входе mi второго кеммутаторз, переключение каналов коммутатора 4 выход которого черрз второй блок последовательно с первого канала формирования уровней квантования с о на второй, с второго на третий и единен с первым входом второго квант . д е и, наконец, в последнем цикле тователя и непосредственно с инфорп-го канала на первый канал после мационным входом первого преобразокаждого срабатывания компараторов вателя напряжение - код, выход пер™ квантователя 8 и аналогичное .Q вого коммутатора соединен с входом переключение каналов коммутатора 5 первого формирователя уровней к в а н после каждого срабатывания компаратования и информационным входом в т о торов квантователя 9. За период рого преобразователя напряжение — изменения вспомогательных сигналов код, стробирутещий вход которого генератора 1 на выходе аналого-циф**; соединен с первым выходом блока упрового преобразователя будет получеравления> а выходы соединены соответно п цифровых отсчетов, гце п - ч и с ственно с первыми входами первого ло сдвинутых по фазе вспомогательблока элемента И, второй вход блока ных сигналов или, что то же самое, управлнния объединен с информационколичество каналов коммутатора А но ным в>.одом т р е т ь е г о регистра и соедиили 5 . нен с выходом второго квантователя» второй вход которого объединен с вторым входом первого квантователя, Ф о р м у л а и з о б р е т е н и я второй выход блока управления соеди*I н 25 е н со стробируемымн входами перво1» Аналого-цифровой преобразоваго преобразователя напряжение - код т е л ь , содержащий первый блок формирои третьего р е г и с т р а , выход которого вания уровней квантования, выход к о и выходы первого преобразователя торого соединен с первым входом напряжение - код соединены с о о т в е т с т гсервого квантователя, второй вход -jQ венчо с первыми и вторыми входами которого является шиной преобразуевторого блока элементов И, выходы мого сигнала, а выход соединен с пергого регистра соединены с соответинформационным входом первого р е г и с т ствующими вторыми входами первого ра и первым входом блока управления, блока элементов И 5 третьи входы п е р первый выход которого соединен со вого и второго Гщоков элементов И стробирующим входом первого р е г и с т р а , 35 соединены соответственно с третьим второй р е г и с т р , выходы которого я в к четвертым выходаг-ш: блока управлеляются выходной шиной, генератор ния, пятый и шестой выходы которого парафазных сигналов, первый преобрасоединены соответственно с управляюзователь напряжение - код, о т щими входами первого и второго комл и ч а ю щ и й с я тем, ч т о , с ц е мутаторов, выходы первого и второго лью повышения точности, в него в в е блоков элементов И соединены через дены два секционированных блока з а элемент ИЛИ с информационным входом держки, два коммутатора, второй второго р е г и с т р а , стробирующий вход блок формирования уровней к в а н т о в а которого соединен с седьмым выходом ния, второй квантователь, второй преблока управления, образователь напряжение - код, два блока элементов И, элемент ИЛИ и 2» Преобразователь по п . 1 , о т третий регистр, причем первый выход л и ч а ю щ и й с я тем, что блок генератора парафазных сигналов соедиуправления выполнен на элементе ИЛИ, нен с первык информационным входом 50 двух формирователях коротких импервого коммутатора и входом первого пульсов, двух RS-триггерах, двух блока задержки, выходы которого с о элементах И, двух цифровых компараединены с соответствующими вторыми торах; и двух инверторах, первый информационными входами первого комвход первого инвертора объединен мутатора, второй выход генератора t-£ с первым входом первого цифрового парафазных сигналов соединен с п е р компаратора и я в л я е т с я первым вховым информационным входом второго дом блока, а выход инвертора соедикоммутатора и входом второго блока нен с вторым входом цифрового компа.задержки, выходы которого соединены ратора, выход которого соединен г 1615885 8 ИЛИ, второй вход которого соединен первым входом первого элемента И и с выходом второго формирователя коявляется первым ЕЫХОДОМ блока, второтких импульсов, который является рой вход первого элемента И соединен шестым выходом блока, вход второго с инверсным выходом первого RS-тригформирователя коротких импульсов гера, а выход соединен с S-входом соединен с прямым выходом первого второго RS-триггера, R-вход которого RS-триггера, который является четверобъединен с R-входом первого RS-тригтым выходом блока, S-вход первого гера и соединен с выходом элемента RS-триггера соединен с выходом вто-* ИЛИ, который является седьмым выхо10 рого элемента И, второй вход котородом блока, инверсный выход второго го соединен с выходом второго цифроRS-триггера соединен с первым входом вого компаратора, который является второго элемента И, прямой выход вторым выходом блока, первый вход является третьим выходом блока и цифрового компаратора объединен с соединен с входом первого формирователя коротких импульсов, выход кото- 15 входом второго инвертора и является вторым входом блока, а второй вход рого является пятым выходом блока соединен с выходом второго инвертора, и соединен с первш входом элемента 1615885 1615885 Фив.4 Редактор Н.Тупица Составитель Л.Титов Техред М.Длдык Корректор JT.Бескид Заказ 3996 Тираж 666 Подписное В И П Государственного комитета по изобретениям и открытиям при ГКНТ СССР НИЙ 113035, Москва, Ж-35, Раушская наб„, д . А/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog-to-digital converter

Автори англійськоюKlochan Petro Stepanovych, Lavrentiev Vasyl Mykolaiovych

Назва патенту російськоюАналого-цифровой преобразователь

Автори російськоюКлочан Петр Степанович, Лаврентьев Василий Николаевич

МПК / Мітки

МПК: H03M 1/36

Мітки: аналого-цифровий, перетворювач

Код посилання

<a href="https://ua.patents.su/6-9083-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач</a>

Попередній патент: Змінна передача

Наступний патент: Імітатор ехо-сигналів від морської поверхні

Випадковий патент: Стаціонарна стратосферна станція для метеоастрономічних досліджень конструкції є.б.левіна