Аналого-цифровий перетворювач інтегральних характеристик електричних величин

Номер патенту: 10794

Опубліковано: 25.12.1996

Автори: Портнов Михайло Львович, Дороніна Ольга Михайлівна, Лавров Генадій Миколайович

Формула / Реферат

1. Аналого-цифровой преобразователь интегральных характеристик электрических величин, содержащий согласующее устройство, первый и второй аналоговые коммутаторы, источник опорного напряжения, постоянное запоминающее устройство масштабного коэффициента и устройство управления, содержащее нуль-орган, первый и второй счетчики, первый и второй регистры, постоянное запоминающее устройство и элемент ИЛИ, причем вход нуль-органа является первым входом устройства управления, выходы разрядов первого счетчика соединены со входами первого регистра, выходы разрядов второго счетчика соединены со входами второго регистра, выходы которого подключены к третьим выходам устройства управления, входы согласующего устройства соединены с шинами входных сигналов, а выходы - со входами первого аналогового коммутатора, выход источника опорного напряжения подключен ко второму входу второго аналогового коммутатора, третьи входы которого соединены с выходами первого аналогового коммутатора, первые и вторые выходы устройства управления подключены ко входам управления соответственно первого и второго аналоговых коммутаторов, а третьи и четвертые выходы соответственно - к первым и вторым адресным входам постоянного запоминающего '· устройства масштабного коэффициента, отличающийся тем, что в него введены аналого-цифровой преобразователь, цифровой вычитатель, третий и четвертый регистры, первый и второй мультиплексоры, оперативное запоминающее устройство, арифметическологическое устройство, цифровой умножитель, постоянные запоминающие устройства коэффициента коррекции, корня квадратного и частоты, буферное оперативное запоминающее устройство и первый и второй шинные формирователи, причем первый вход аналого-цифрового преобразователя соединен с выходом второго аналогового коммутатора, а выходы -со входами третьего регистра и первыми входами цифрового вычитателя, вторые входы которого подключены к выходам третьего регистра, а выходы - к первым входам первого мультиплексора, вторые входы которого соединены с шиной "нуль-вольт" и первым входом второго аналогового коммутатора, а выходы - с адресными входами постоянных запоминающих устройств коэффициента коррекции и корня квадратного, выводами входа/выхода оперативного запоминающего устройства, выводами первых входов/выходов арифметическо-логического устройства, выходами цифрового умножится я и постоянного запоминающего устройства частоты, входами первого и второго шинных формирователей и четвертого регистра, выходы которого подключены ко вторым входам арифметическо-логического устройства, выходы постоянных запоминающих устройств коэффициента коррекции, масштабного коэффициента и квадратного корня соединены с первыми и вторыми входами цифрового умножителя, выходами первого шинного формирователя, адресными входами постоянного запоминающего устройства частоты и пятыми выходами устройства управления, выводы входа/выхода буферного оперативного запоминающего устройства подключены к выходам второго шинного формирователя и шинам выходной информации, а адресные входы - к выходам второго мультиплексора, первые входы которого соединены с адресными входами постоянного запоминающего устройства масштабного коэффициента, а вторые входы -с шинами кода параметра, первый вход устройства управления подключен к одному из выходов согласующего устройства, второй вход - к выходу готовности информации аналого-цифрового преобразователя, третий вход - к шине запроса выходной информации, шестые выходы - ко входам управления и выборки первого мультиплексора, входам режима работы, адреса и выборки оперативного запоминающего устройства, входу записи четвертого регистра, входам записи, режима работы и выборки арифметическо-логического устройства, входами выборки первого шинного формирователя, постоянных запоминающих устройств коэффициента коррекции, масштабного коэффициента, корня квадратного и частоты, входам записи и выборки цифрового умножителя, седьмой выход - ко входу записи третьего регистра, восьмой выход - ко входу запуска аналого-цифрового преобразователя, девятый выход- ко входу управления второго мультиплексора, входу выборки второго шинного формирователя и шине готовности выходной информации, десятый выход - ко входу режима работы буферного оперативного запоминающего устройства.

2. Преобразователь по п.1, отличающийся тем, что устройство управления содержит генератор опорной частоты, третий, четвертый и пятый счетчики, синхронизатор первый и второй триггеры и первый и второй элементы И, причем второй вход устройства управления соединен со входом пятого счетчика и первым входом элемента ИЛИ, остальные входы которого подключены к выходам разрядов четвертого счетчика, входам первого элемента И и вторым адресным входам постоянного запоминающего устройства управления, третий вход устройства управления соединен с D-входом второго триггера, С-вход которого подключен к выходу четвертого счетчика и второму входу синхронизатора, прямой выход- к девятому выходу устройства управления, а инверсный выход - к первому входу второго элемента И, выход которого соединен с десятым выходом устройства управления, выход нуль-органа подключен к первому входу синхронизатора и D-входу первого триггера, С-вход которого соединен с выходом старшего разряда третьего счетчика, R-вход - с выходом старшего разряда первого счетчика, а прямой и инверсный выходы - соответственно со входом записи третьего регистра и входом установки в "нуль" первого счетчика, первый выход синхронизатора подключен ко входу записи второго регистра, а второй выход - к первому адресному входу постоянного запоминающего устройства управления и входу второго счетчика, выходы которого соединены с первыми выходами устройства управления, выход генератора опорной частоты подключен ко входу третьего счетчика, выход которого соединен со входами первого и четвертого счетчиков и восьмым выходом устройства управления, а выходы разрядов -с третьими адресными входами постоянного запоминающего устройства управления, выходы которого подключены соответственно к четвертым и шестым выходам устройства управления, входу выборки первого регистра и второму входу второго элемента И, выход элемента ИЛИ соединен с седьмым выходом устройства управления, выходы первого регистра - с пятыми выходами устройства управления, а выход первого элемента И - со входом установки в "нуль" пятого счетчика, выходы разрядов которого соединены со вторыми выходами устройства управления.

Текст

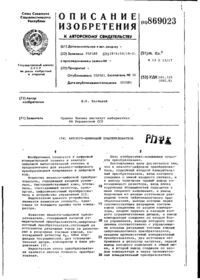

Изобретение относится к области энергетики и может быть использовано в измерительноинформационных системах, автоматизированных системах управления, где предусматривается контроль и ввод данных об интегральных параметрах электрической сети в электронные вычислительные машины для последующей обработки. Наиболее близким по технической сущности к предлагаемому является аналого-цифровой преобразователь интегральных характеристик электрических сигналов [2], содержащий согласующее устройство, первый и второй аналоговые коммутаторы, источник опорного напряжения, постоянное запоминающее устройство масштабного коэффициента и устройство управления, содержащее нуль-орган, первый и второй счетчики, первый и второй регистры, постоянное запоминающее устройство управления и элемент ИЛИ. В нем обеспечивается возможность получения кодового отображения по каждому контролируемому каналу (трехфазной электрической сети) трехфазных токов и напряжений, активной и реактивной мощности. В этом устройстве аналого-цифровое преобразование каждого из указанных восьми параметров (характеристик) электрической сети производится за два смежных периода частоты сети, так как используемые методы аналого-цифрового преобразования не позволяют получить значения интегралов квадратов и произведений входных сигналов, используемых при вычислении интегральных параметров, за один период частоты электрической сети. В результате время, затрачиваемое на получение кодовых отображений восьми параметров трехфазной сети, равно шестнадцати периодам частоты сети. На современном уровне развития энергетики к информационно-измерительной аппаратуре, используемой в АСУ энергообъектов, народу с высокой точностью, многофункциональностью (преобразование основных электрических величин: фазных токов, фазных или линейных напряжений, активной и реактивной мощностей, частоты, одним устройством при унификации методов преобразования), многоканаль-ностью (контроль за всеми подключениями энергообъекта, число которых может достигать 64) предъявляются требования высокого быстродействия. Последнее необходимо для работы релейной защиты, включающейся при достижении действующими значениями входных токов высоких уровней, например, при коротких замыканиях. Для оперативной работы релейной защиты промышленных энергообъектов временные интервалы между точками контроля входных токов не должны превышать 1-2 секунд. В устройстве-прототипе период контроля параметров для указанного выше числа контролируемых каналов (64) оказывается равным 2.0,02 · 8 · 64>20 сек, что не обеспечивает требуемого быстродействия. Задачей изобретения является повышение быстродействия для удовлетворения требований релейной защиты. Поставленная задача достигается тем, что в аналого-цифровой преобразователь интегральных характеристик электрических величин, содержащий согласующее устройство, первый и второй аналоговые коммутаторы, источник опорного напряжения, постоянное - запоминающее устройство масштабного коэффициента и устройство управления, входы согласующего устройства соединены с шинами входных сигналов, а выходы - со входами первого аналогового коммутатора, выход источника опорного напряжения подключен ко второму входу второго аналогового коммутатора, третьи входы которого соединены с выходами первого аналогового коммутатора, первые и вторые выходы устройства управления подключены ко входам управления соответственно первого и второго аналоговых коммутаторов, а третьи и четвертые выходы соответственно к первым (старшим) и вторым (младшим) адресным входам постоянного запоминающего устройства масштабного коэффициента, согласно изобретению, введены аналого-цифровой преобразователь, цифровой вычитатель, третий и четвертый регистра, первый и второй мультиплексоры, оперативное запоминающее устройство, арифметическо-логическое устройство, цифровой умножитель, постоянные запоминающие устройства коэффициента коррекции, корня квадратного и частоты, буферное оперативное запоминающее устройство и первый и второй шинные формирователи, причем вход аналогоциф-рового преобразователя соединен с выходом второго аналогового коммутатора, а выходы - со входами третьего регистра и первыми входами цифрового вычитателя, вторые входы которого подключены к выходам третьего регистра, а выходы - к первым входам первого мультиплексора, вторые входы первого мультиплексора соединены с шиной "нуль вольт" и первым входом второго аналогового коммутатора, а выходы - с адресными входами постоянных запоминающих устройств коэффициента коррекции и корня квадратного, выводами входа/выхода оперативного запоминающего устройства, выводами первых входов/выходов арифметическо-логического устройства, выходами цифрового умножителя и постоянного запоминающего устройства частоты, входами первого и второго шинных формирователей и четвертого регистра, выходы которого подключены ко вторым арифметическо-логического устройства, выходы постоянных запоминающих устройств коэффициента коррекции, масштабного коэффициента и квадратного корня соединены с первыми и вторыми входами цифрового умножителя, выходами первого шинного формирователя, адресными входами постоянного запоминающего устройства частоты и пятыми выходами устройства управления, выводы входа /выхода буферного оперативного запоминающего устройства подключены к выходам второго шинного формирователя и шинам выходной информации, а адресные входы к выходам второго мультиплексора, первые входы которого соединены с адресными входами постоянного запоминающего устройства масштабного коэффициента, а вторые входы - с шинами кода параметра, первый вход устройства управления подключен к одному из выходов согласующего устройства, второй вход - к выходу готовности информации аналого-цифрового преобразователя, третий вход - к шине запроса выходной информации, шестые выходы - ко входам управления и выборки первого мультиплексора, входам режима работы, адреса и выборки оперативного запоминающего устройства, входу записи четвертого регистра, входам записи, режима работы и выборки арифметическо-логического устройства, входам выборки первого шинного формирователя, постоянных запоминающих устройств коэффициента коррекции, масштабно/о коэффициента, квадратного корня и частоты, входам записи и выборки цифрового умножителя, седьмой вход - ко входу записи третьего регистра, восьмой выход - ко входу запуска аналого-цифрового преобразователя, девятый выход - ко входу управления второго мультиплексора, входу выборки второго шинного формирователя и шине готовности выходной информации, десятый выход - ко входу режима работы буферного оперативного запоминающего устройства. Кроме того, в устройство управления, содержащее нуль-орган, первый и второй счетчики, первый и второй регистры, постоянное запоминающее устройство управления и элемент ИЛИ, причем вход нульоргана является первым входом устройства управления, выходы разрядов первого счетчика соединены со входами первого регистра, выходы разрядов второго счетчика соединены со входами второго регистра, выходы которого подключены к третьим выходам устройства управления, дополнительно введены генератор опорной частоты, третий, четвертый и пятый счетчики, синхронизатор, первый и второй триггеры и первый и второй элементы И, причем второй вход устройства управления соединен со входом пятого счетчика и первым входом элемента ИЛИ, остальные входы которого подключены к выходам разрядов четвертого счетчика, входам первого элемента И и вторым адресным входам постоянного запоминающего устройства управления, третий вход устройства управления соединен с D-входом второго триггера, С-вход которого подключен к выходу четвертого счетчика и второму входу синхронизатора, прямой выход- к девятому выходу устройства управления, а инверсный выход - к первому входу второго элемента И. выход которого соединен с десятым выходом устройства управления, выход нуль-органа подключен к первому входу синхронизатора и D-входу первого триггера, С-вход которого соединен с выходом старшего разряда третьего счетчика, С-вход с выходом старшего разряда первого счетчика, а прямой и инверсный выходы - соответственно со входом записи первого регистра и входом установки в "нуль" первого счетчика, первый выход синхронизатора подключен ко входу записи второго регистра, а второй выход - к первому адресному входу постоянного запоминающего устройства управления и входу второго счетчика, выходы которого соединены с первыми выходами устройства управления, выход генератора опорной частоты подключен ко входу третьего счетчика, выход которого соединен со входами первого и четвертого счетчиков и восьмым выходом устройства управления, а выходы разрядов - с третьими адресными входами постоянного запоминающего устройства управления, выходы которого подключены соответственно к четвертым и шестым выходам устройства управления, входу выборки первого регистра и второму входу второгоэлемента И, выход элемента ИЛИ соединен с седьмым выходом устройства управления, выходы первого регистра - с пятыми выходами устройства управления, а выход первого элемента И - со входом установки в "нуль" пятого счетчика, выходы разрядов которого соединены со вторыми выходами устройства управления. В частном случае реализации в качестве аналого-цифрового преобразователя использована микросхема К1108ПВ2 (6КО.348.863 ТУ). Цифровой вычитатель построен на основе микросхем КР1533ИПЗ (6КО 348.806-03 ТУ), включенных в режим вычитания; регистры -на основе микросхем КР1533ИР37 (6КО.348.806-22 ТУ), работающих в режиме выборки, первый и второй мультиплексоры -на основе микросхем КР1533КП11 (6КО.348.806-28 ТУ), оперативное и буферное оперативное запоминающие устройства -на основе микросхем КР537РУ10 (6КО.348.532-10 ТУ), арифметическо-логическое устройство - на основе микросхем КР1802ВС1 (6КО.348.62902 ТУ), цифровой умножитель - на основе микросхемы КМ 1802 ВР4 (6КО.348.766-08ТУ), постоянные запоминающие устройства коэффициента коррекции, корня квадратного и частоты - на основе микросхем КР556РТ7А (6КО.348.322-07 ТУ), шинные формирователи на основе микросхем КР1533АП4 (6КО.348.806-32 ТУ). Генератор опорной частоты построен на основе кварцевого резонатора РГ-05-14БП-8192кГц-МЗУ (ОДО.338.065 ТУ), шунтированного индуктивно-емкостной цепочкой и элементом КР1533ЛН1 (6КО.348-806-01 ТУ); счетчики - на основе микросхем КР1533ИЕ18 (6КО.348.806-27 ТУ). Синхронизатор построен на основе двух D-триггеров (КР1533ТМ2. 6КО.348.806-02 ТУ), элементов И-НЕ (КР1533ЛАЗ 6КО.348.806-01 ТУ) и НЕ (КР1533ЛН1, 6КО.348.806-01 ТУ), причем первый (Д) вход первого триггера соединен с первым входом синхронизатора, второй (С) вход- со вторым входом синхронизатора и Свходом второго триггера, прямой выход - с D-входом второго триггера и первым входом элемента И-НЕ, второй вход которого подключен к инверсному выходу второго триггера, а выход - ко входу элемента НЕ и первому выходу синхронизатора, второй выход последнего соединен с выходом элемента НЕ. Первый и второй триггеры построены на основе микросхемы КР1533ТМ2 (6КО.348.806-02 ТУ), первый элемент И - на основе микросхемы КР1533ЛИ6 (6КО.348.806-02 ТУ), а второй элемент И - на основе микросхемы КР1533ЛИ1 (6КО.348.806-01 ТУ). В результате введения новых функциональных узлов и связей между ними все вычисления, необходимые для получения интегральных значений фазных токов и напряжений, активной и реактивной мощности по одному трехфазному каналу, завершаются в пределах одного периода частоты электрической сети без потери точности вычислений по сравнению с известным устройством. Таким образом, реализация предполагаемого изобретения позволяет обеспечить получение кодовых отображений всех параметров трехфазной сети по 64 контролируемым каналам за время Т-0,02 * 64-1,28 сек, что удовлетворяет требованиям по быстродействию для систем релейной защиты. На фиг. 1 представлена схема предлагаемого аналого-цифрового преобразователя, на фиг.2,3 временные диаграммы, поясняющие его работу. Аналого-цифровой преобразователь интегральных характеристик электрических величин содержит согласующее устройство 1, аналоговые коммутаторы 2 и 3, источник опорного напряжения 4, аналогоцифровой преобразователь 5, цифровой вычитатель 6, регистры 7 и 8, мультиплексоры 9 и 10, оперативное запоминающее устройство 11, арифметическо-логическое устройство 12, постоянные запоминающие устройства коэффициента коррекции 13 масштабного коэффициента 14, корня квадратного 15 и частоты 16, цифровой умножитель 17, буферное оперативное запоминающее устройство 18, шинные формирователя 19 и 20. и устройство управления 21. Входы согласующего устройства 1 соединены с шинами входных сигналов, а выходы соответственно со входами первого аналогового коммутатора 2 и первым входом устройства управления 21. Входы второго аналогового коммутатора 3 соединены соответственно с шиной "нуль вольт" (OV). выходом источника опорного напряжения 4 и выходами первого аналогового коммутатора 2, а выход- со входом аналогоцифрового преобразователя 5, выходы которого подключены к первым входам цифрового вычитателя 6 и входом третьего регистра 7. Вторые входы цифрового вычитателя 6 соединены с выходами регистра 7, а выходы - с первыми входами первого мультиплексора 9, вторые входы которого подключены к шине "нуль вольт", а выходы - к адресным входам постоянных запоминающих устройств корректирующего коэффициента и корня квадратного 13 и 15, выводам входа/выхода оперативного запоминающего устройства 11, выводам первых входов/выходов арифметическо-логического устройства 12, выходам цифрового умножителя 17 И постоянного запоминающего устройства частоты 16 и входам первогои второго шинных формирователей 19 и 20 и четвертого регистра 8. Выходы регистра 8 соединены со вторыми входами арифметическо-логического устройства 12. Выходы постоянных запоминающих устройств 13, 14 и 15 подключены к первым и вторым входам цифрового умножителя, выходам первого шинного формирователя 19, адресным входам постоянного запоминающего устройства 16 и пятым выходам устройства управления 21. Выводы входа/выхода буферного оперативного запоминающего устройства 18 соединены с выходами шинного формирователя 20 и шинами выходной информации, а адресные входы - с выходами второго мультиплексора 10, первые входы которого подключены к первым и вторым адресным входам постоянного запоминающего устройства масштабных коэффициентов 14, соединенным соответственно с третьими и четвертыми выходами устройства управления 21. Вторые входы второго мультиплексора 10 подключены к шинам кода параметра. Второй вход устройства управления 21 соединен с выходом готовности информации аналого-цифрового преобразователя 5, третий вход - с шиной запроса выходной информации, первые и вторые выходы - со входами управления, соответственно, аналоговых коммутаторов 2 и 3, шестые выходы - со входами управления и выборки первого мультиплексора 9, входами режима работы, адреса и выборки оперативного запоминающего устройства 11, входом записи регистра 8, входами записи, режима работы и выборки арифметическо-логического устройства 12, входами выборки постоянных запоминающих устройств 13, 14, 15 и 16 и шинного формирователя 19 входами записи и выборки умножителя 17, седьмой выход - со входом записи регистра 7, восьмой выход - со входом запуска аналого-цифрового преобразователя 5, девятый выход - со входами управления второго мультиплексора 10, входом выборки шинного формирователя 20, а также шиной готовности выходной информации, десятый выход - со входом режима работы буферного оперативного запоминающего устройства 18. Устройство управления 21 содержит нуль-орган 22, синхронизатор 23, генератор опорной частоты 24, счетчики 25, 26, 27, 28 и 29, регистры 30 и 31, триггеры 32 и 33, элемент ИЛИ 34, элементы И 35 и 36 и постоянное запоминающее устройство управления 37. Первый вход устройства управления 21 соединен со входом нуль-органа 22, выход которого подключен к первому входу синхронизатора 23 и D-входу первого триггера 32. Второй вход устройства управления соединен со входом пятого счетчика 29 и первым входом элемента ИЛИ 34, остальные входы которого подключены к выходам разрядов четвертого счетчика 26, входам первого элемента И 35 и вторым адресным входам постоянного запоминающего устройства 37. Третий вход устройства управления 21 соединен с первым (D)-входом второго триггера 33, второй (С)-вход которого подключен к выходу четвертого счетчика 26 и второму входу синхронизатора 23, прямой выход - к девятому выходу устройства управления 21, а инверсный выход -к первому входу второго элемента И 36. Выход последнего соединен с десятым выходом устройства управления 21. Второй (С)-вход триггера 32 соединен с выходом старшего разряда третьего счетчика 25, R-вход - с выходом старшего разряда первого счетчика 28, а прямой и инверсный выходы -соответственно со входом записи первого регистра 30 и входом установки в "нуль" первого счетчика 28, выходы разрядов которого подключены ко входам первого регистра 30. Первый выход синхронизатора 23 соединен со входом записи второго регистра 31, а второй выход - с первым адресным входом постоянного запоминающего устройства 37 и входом второго счетчика 27, выходы разрядов которого подключены ко входам второго регистра 31 и первым выходом устройства управления 21. Выход генератора опорной частоты 24 подключен ко входу третьего счетчика 25, выход которого соединен со входами счетчиков 26 и 28 и восьмым выходом устройства управления 21, а выходы разрядов - с третьими адресными входами постоянного запоминающего устройства 37. Выходы последнего подключены соответственно к четвертым и шестым выходам устройства управления 21, второму входу элемента И 36 и входу выборки первого регистра 30, выходы которого соединены с пятыми выходами устройства управления 21. Выход элемента ИЛИ 34 подключен к седьмому выходу устройства управления 21. Выход элемента И 35 соединен со входом установки в "нуль" пятого счетчика 29, выходы разрядов которого подключены ко вторым выходам устройства управления 21, а выходы второго регистра 31 соединены с третьими выходами этого устройства. В частном случае реализации согласующее устройство 1 содержит S входных устройств, рассмотренных в описании к авт.свид. СССР № 978060. кл. G 01 R 21/06, G 01 R 25/00 от 30.11.80, причем S - число контролируемых каналов энергообъекта. Аналоговый коммутатор 2 содержит Ρ микросхем КР590КН6 (6КО.348.209-05 ТУ) с объединенными входами управления, где Ρ - число контролируемых входных сигналов по одному каналу (3 фазных тока и 3 фазных напряжения). Коммутатор 3 построен на основе микросхемы КР590КН6. Источник 4 опорного напряжения построен по схеме, описанной в книге Н.В.Воробьев, В.Д.Вер-нер "Элементная база и схемотехника средств сопряжения", М., "Высшая школа", 1984. с.58, рис.2.46, 2.47. Постоянные запоминающие устройства 14 и 37 построены на основе микросхем КР556РТ7А (6КО.348.322-07 ТУ), причем устройство 36 включено постоянно в режим выборки информации. В качестве нуль-органа 22 использован триггер Шмитта. Элемент ИЛИ 34 построен на основе микросхемы КР1533ЛЛ1 {6КО.348.806-01 ТУ). Работа аналого-цифрового преобразователя интегральных характеристик электрических величин заключается в следующем. Входные напряжения и токи от контролируемого энергообъекта преобразуются в согласующем устройстве 1 в нормированные напряжения, им прямо пропорциональные. Одно из нормированных напряжений (фиг.2а) поступает на вход нуль-органа 22, формирующего прямоугольный сигнал с периодом-следования, равным периоду Τ колебаний сигналов контролируемого энергообьекта(фиг.2б). Сигнал с выхода нуль-органа 22 поступает на вход синхронизатора 23, синхронизирующего его с сигналом такта с выхода счетчика 26 (фиг.3б,в,г,д). Сигнал такта формируется путем деления частоты f 0 опорной импульсной последовательности с выхода генератора 24 счетчиками 25 и 26 на f o Tmin/n. где n -необходимое для обеспечения нужной точности преобразования число выборок мгновенных значений контролируемых входных токов и напряжений за период (в конкретном случае реализации n - не менее 300 при Τ·=45-55 Гц). Сигналы с выходов разрядов счетчиков 25 и 26 вместе с синхронизированным сигналом периода (фиг.3Д) являются управляющими для постоянного запоминающего устройства (ПЗУ) управления 37. Для определения длительности очередного периода Τ колебаний сигналов исследуемого энергообъекта в течение этого периода счетчиком 28 периода подсчитывается число Ντ импульсов опорной частотой следования f o/m, где m - коэффициент пересчета счетчика 25: С появлением положительного периода сигнала на выходе нуль-органа 22 (фиг.2,36), обозначающего конец очередного периода, триггер 32 сигналом с выхода старшего разряда счетчика 25 устанавливается в "единичное" состояние, управляя тем самым записью содержания счетчика 28 периода в регистр 30 периода и подготавливая счетчик 28 к установке в "нуль", осуществляемой под действием ближайшего положительного перепада сигнала с выхода счетчика 25 (фиг.3е.ж.з). Устанавливаясь в "нуль", старший разряд счетчика 28 устанавливает в "нуль" и триггер 32 и поддерживает его в этом состоянии большую часть следующего периода. Сигнал синхронизированного периода со второго выхода синхронизатора 23 (фиг.3д) поступает на вход счетчика 27 цикла, отсчитывающего количество периодов, равное числу подлежащих контролю каналов энергообъектов. Выходной код счетчика 27, определяющий номер контролируемого канала, управляет коммутатором 2, подключающим каналы ко входам коммутатора 3, и с задержкой на 1 такт (фиг.3г) переносится в регистр 31. Сигнал с выхода счетчика 26 делит очередной период Τ на n тактов t (фиг.3в), в каждом из которых на выходе счетчика 25 формируются импульсы запуска АЦП (фиг.3ж), а на выходе элемента И 35 - импульсы установки в "нуль" счетчика 29 (фиг.3и), работающего от сигнала готовности аналого-цифрового преобразователя (АЦП) 5 и управляющего коммутатором 3, подключающим ко входу АЦП аналоговые сигналы: нуль вольт (OV), опорное напряжение Uo с выхода источника и фазные токи ід, їв, 1с и напряжения UA, UB. UC очередного контролируемого канала с выходом коммутатора 2 (фиг.3к.,л,м,н). АЦП 5 преобразует мгновенные значения поступающих на его вход сигналов в цифровой код N. Причем код Nov (нуль вольт), представляющий собой аддитивную погрешность преобразования/записывается в регистр 7 сигналом с выхода элемента "ИЛИ" 34 (фиг.Зо) в начале каждого текущего такта, а все остальные коды после вычитания из них кода аддитивной погрешности (посредством вычитателя 6) подключаются мультиплексором 9 ко входам оперативного запоминающего устройства (ОЗУ) 11. и записываются в него по адресам, определяемым ПЗУ 37. В течение текущего такта ϊ) работы преобразователя интегральных характеристик электрических величин осуществляется формирование текущих значений сумм квадратов и произведений мгновенных значений входных сигналов для вычисления действующих значений токов и напряжений, мощностей и запись их в ОЗУ 11. Работа узлов преобразователя осуществляется под управлением сигналов (потенциалов или фронтов в зависимости от каждого конкретного случая) с выходов ПЗУ 37, куда предварительно записывается программа работы. Изменение выходных сигналов ПЗУ 37 осуществляется с изменением кода на выходах счетчиков 25, 26 и синхронизатора 23 с шагом, равным периоду следования импульсов на выходе генератора 24. Здесь следует отметить, что выходы некоторых узлов, например, узлов 9, 11, 12 и 17, объединены в общие шины. Поэтому при необходимости выдачи информации с выходов одного из этих узлов, например, узла 9, выходы узлов 11,12 и 17 соответствующими потенциалами с соответствующих выходов ПЗУ 37 отключаются от общей шины. Узлы 13,14,15 и 30 работают аналогично. Работа преобразователя пошагово заключается в следующем: - чтение из ОЗУ 11 по адресу, определяемому соответствующими разрядами ПЗУ 37, кода NUAJ мгновенного значения UAj напряжения фазы А очередного канала где I и DI - расчетное значение коэффициента пропорциональности и его отклонение от этого значения, и запись NUAJ через шинный формирователь 19 во входные регистры умножителя 17, где он перемножается сам на себя. Шинный формирователь 19 необходим здесь для разделения входов и выходов умножителя 17, т.к. и те и другие должны быть соединены с шиной, объединяющей узлы 11,8 и 12; - чтение из ОЗУ 11 суммы предыдущие такты и запись ее в регистр 8; квадратов кодов мгновенных значений напряжения UA за соответственно с выходов умножителя 17 и регистра 8 во входные регистры арифметическо-логического устройства (АЛУ) 12, где производится их сложение; - запись результата сложения из АЛУ 12 в ОЗУ 11. Формирование текущих значений сумм квадратов напряжений фаз В и С и токов всех фаз осуществляется аналогично. Вычисление текущих значений сумм активной и реактивной мощностей трехфазной сети отличается тем, что здесь осуществляется перемножение кодов мгновенных значений тока и напряжения, где чего в первый и второй входные регистры цифрового умножителя 17 из ОЗУ 11 через формирователь 19 эти коды переносятся по очереди (изменяется адрес считывания ОЗУ 11) в течение двух шагов. Кроме того, перемножение производится дважды: кода )-го мгновенного значения напряжения фазы на коды (j-ro)-ro и j-го мгновенного значения тока этой фазы, после чего полученные произведения прибавляются к текущей сумме для вычисления активной мощности. Для реактивной мощности второе произведение вычитается. К концу текущего периода в ОЗУ 11 находятся коды следующих сумм: R - сопротивление калиброванных резисторов согласующего устройства 1, посредством которых входные токи преобразуются в пропорциональные им напряжения. В течение первого такта следующего периода (на выходе g синхронизатора - единичный потенциал) осуществляется обработка результатов вычислений за предыдущий период. При этом работа преобразователя пошагово заключается в следующем: - код Nug' из ОЗУ 11 записывается через шинный формирователь 19 в первый входной регистра умножителя 17; - код Νυο' из ОЗУ 11 подается на адресные входы ПЗУ 13, откуда извлекается соответствующее ему значение коэффициента коррекции. записываемое во второй регистр умножителя 17, после чего Nug' и 1к перемножаются; - результат перемножения подается на адресные входы ПЗУ 15, откуда считывается соответствующее ему значение корня квадратного и записывается в первый входной регистр умножителя 17; -из ПЗУ 14 считывается код масштабного коэффициента 1ми. необходимый для приведения результата преобразования соответствующего параметра к реальному значению; при этом адрес ячейки ПЗУ 14 определяется кодом номера канала, контролируемого в предыдущем периоде, с выходов регистра 31 и кодом параметра с соответствующих выходов ПЗУ 37; код 1ми заносится во второй входной регистр умножителя 17, после чего перемножается с результат перемножения, пропорциональный при n»1, когда Т/n ®0, действующему значению фазного напряжения через шинный формирователь 20 заносится в определенную ячейку буферного ОЗУ 18, адрес которой формируется аналогично адресу ячейки ПЗУ 14 и подключается к адресным входам ОЗУ 18 мультиплексором 10. Обработка кодов Nig' осуществляется аналогично Nug'. Обработка кода Np' осуществляется аналогично Nug' с исключением операции извлечения корня квадратного. При этом результат преобразования при n>>1, например, для синусоидальных сигналов Ug(t)UmgSin (w t И lg(t)~lmgSin( (w t+ jg) Прoмышленной сети определяется из выражения: то есть пропорционален активной мощности трехфазной сети. Обработка кода Nq' осуществляется аналогично обработке Np' за исключением того, что здесь перед операцией перемножения на масштабный коэффициент I mq вводится операция умножения на код периода NT. Для этого код NT с выходов регистра 30 записывается во второй входной регистр умножителя 17. При этом результат преобразования пропорционален реактивной мощности трехфазной сети: где 23 - коэффициент пересчета счетчика 25. Коды Nig, Np и Nq заносятся в буферное ОЗУ 18 аналогично Nug. Сюда же записывается и значение частоты. Для этого код длительности предыдущего периода Ντ с выходов регистра 30 подается на адресные входы ПЗУ 1 6, с выходов которого снимается соответствующий ему код 1/Ντ. поступающий через шинный формирователь 20 на входы ОЗУ 18. После занесения информации по предыдущему периоду о параметрах соответствующего канала в буферное ОЗУ 18 мультиплексор 9 подключает ко входам ОЗУ 11 "нулевой" уровень напряжения, и ячейки ОЗУ 11, отведенные под хранение текущих сумм квадратов и произведений входных токов и напряжений по очереди (изменяется адрес на адресных входах ОЗУ 11 под действием сигналов с соответствующих выходов ПЗУ 37) обнуляются, после чего преобразователь готов к преобразованию информации по следующему каналу. Считывание информации Νвых из буферного ОЗУ 18 на внешнее устройство осуществляется при подаче от внешнего устройства сигнала запроса Зпр. информации (фиг.3п) на D-вход триггера 33 и кода запрашиваемого параметра А, определяющего адрес хранения этого параметра в буферном ОЗУ 18, на вторые входы мультиплексора 10. При поступлении сигнала запроса информации триггер 33 ближайшим положительным перепадом напряжения с выхода счетчика 26, обозначающего окончание очередного такта, устанавливается в единичное состояние (фиг.3п.в.р). Это приводит к подключению кода запрашиваемого параметра А мультиплексором 10 к адресным входам буферного ОЗУ 18, установление буферного ОЗУ 18 элементом И 36 в режим считывания информации, отключение выводов вход-выход ОЗУ 18 шинным формирователем 20 от схемы преобразователя (выходов умножителя 17), чтобы не было сбоя в выдаче информации и формированию на прямом выходе триггера 33 сигнала Гот. готовности выдачи информации Nвых. на выходах буферного ОЗУ 18 для внешнего устройства (фиг.3р). Как следует из описания работы устройства, к началу очередного периода электрической сети в ОЗУ устройства оказываются подготовленными интегральные значения параметров: фазных токов и напряжений, активной и реактивной мощности для контролируемого в предшествующем периоде канала. Большое (порядка 300) число сделанных в пределах периода; промежуточных преобразований обеспечивает достаточно высокую степень аппроксимации при высокой точности вычислений и таким образом достигается высокое быстродействие.

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog-to-digital converter of intergral characteristics of electrical values

Автори англійськоюLavrov Hennadii Mykolaiovych, Doronina Olha Mykhailivna, Portnov Mykhailo Lvovych

Назва патенту російськоюАналого-цифровой преобразователь интегральных характеристик электрических величин

Автори російськоюЛавров Геннадий Николаевич, Доронина Ольга Михайловна, Портнов Михаил Львович

МПК / Мітки

МПК: H03M 1/06

Мітки: величин, інтегральних, електричних, аналого-цифровий, перетворювач, характеристик

Код посилання

<a href="https://ua.patents.su/7-10794-analogo-cifrovijj-peretvoryuvach-integralnikh-kharakteristik-elektrichnikh-velichin.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач інтегральних характеристик електричних величин</a>

Попередній патент: Фотоелектричний пірометр

Наступний патент: Оправка для волочіння труб

Випадковий патент: Спосіб біологічного контролю шкідливості фітофагів овочевих культур