Пристрій для зміни порядку розрядів послідовних кодів

Номер патенту: 110594

Опубліковано: 12.01.2016

Автори: Нестеренко Сергій Анатолійович, Дрозд Олександр Валентинович, Аль-Дабі Мохаммед Мохаммед Салех, Гончаров Андрій Володимирович, Мілейко Ігор Генрікович

Формула / Реферат

Пристрій для зміни порядку розрядів послідовних кодів, що містить реверсивний регістр, елемент НІ, перший і другий елементи І та комутатор, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, вхід режиму пристрою підключено до першого режимного входу реверсивного регістра, першого входу першого елемента І, управляючого входу комутатора та входу елемента НІ, вихід якого підключено до першого входу другого елемента І та другого режимного входу реверсивного регістра, інформаційний вхід пристрою підключено до других входів першого та другого елементів І, виходи яких підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого підключено відповідно до першого та другого інформаційних входів комутатора, вихід якого є інформаційним виходом пристрою, який відрізняється тим, що введено перший, другий, третій, четвертий, п'ятий, шостий тригери та суматор за модулем два, при цьому тактовий вхід пристрою підключено до входу синхронізації кожного тригера, вхід скидання пристрою підключено до входів скидання першого, третього, четвертого, п'ятого й шостого тригерів та входу встановлення другого тригера, інформаційний вхід пристрою підключено до входу дозволу інвертування першого тригера, вихід якого підключено до інформаційного входу четвертого тригера, вхід режиму пристрою підключено до інформаційного входу другого тригера та першого входу суматора за модулем два, другий вхід якого підключено до виходу другого тригера, а вихід до входів дозволу запису четвертого, п'ятого та шостого тригерів, інформаційний вихід пристрою підключено до входу дозволу інвертування третього тригера, вихід якого підключено до інформаційного входу п'ятого тригера, вихід якого підключено до першого розряду контрольного виходу пристрою, вихід четвертого тригера підключено до інформаційного входу шостого тригера, інверсний вихід якого підключено до другого розряду контрольного виходу пристрою.

Текст

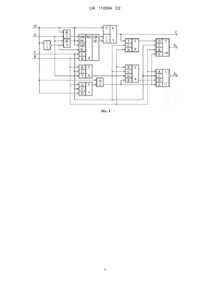

Реферат: Винахід належить до обчислювальної техніки, а саме до арифметичних цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Пристрій для зміни порядку розрядів послідовних кодів, що містить реверсивний регістр, елемент НІ, перший і другий елементи І та комутатор, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, вхід режиму пристрою підключено до першого режимного входу реверсивного регістра, першого входу першого елемента І, управляючого входу комутатора та входу елемента НІ, вихід якого підключено до першого входу другого елемента І та другого режимного входу реверсивного регістра, інформаційний вхід пристрою підключено до других входів першого та другого елементів І, виходи яких підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого підключено відповідно до першого та другого інформаційних входів комутатора, вихід якого є інформаційним виходом пристрою, згідно з винаходом, за рахунок введення шести тригерів та суматора за модулем два забезпечує контроль результату за парністю, що суттєво підвищує достовірність функціонування пристрою. UA 110594 C2 (12) UA 110594 C2 UA 110594 C2 5 10 15 20 25 30 35 40 45 50 55 60 Запропонований винахід належить до обчислювальної техніки, а саме до арифметичних цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Відомий пристрій для зміни порядку розрядів послідовних кодів, який містить реверсивний регістр, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, перший та другий входи режиму пристрою підключено відповідно до першого та другого режимних входів реверсивного регістра, перший та другий інформаційні входи пристрою підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого є відповідно першим та другим виходами пристрою [1]. Недоліки аналога: відсутність контролю обчислюваного результату на виході пристрою, що призводить до низької достовірності функціонування пристрою. Найбільш близьким до запропонованого винаходу по технічній суті та результату, що досягається, є пристрій для зміни порядку розрядів послідовних кодів, що містить реверсивний регістр, елемент НІ, перший і другий елементи І та комутатор, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, вхід режиму пристрою підключено до першого режимного входу реверсивного регістра, першого входу першого елемента І, управляючого входу комутатора та входу елемента НІ, вихід якого підключено до першого входу другого елемента І та другого режимного входу реверсивного регістра, інформаційний вхід пристрою підключено до других входів першого та другого елементів І, виходи яких підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого підключено відповідно до першого та другого інформаційних входів комутатора, вихід якого є інформаційним виходом пристрою [2]. Недоліки прототипу: відсутність контролю обчислюваного результату на виході пристрою, що призводить до низької достовірності функціонування пристрою. Задача винаходу - створення пристрою для зміни порядку розрядів послідовних кодів, в якому шляхом введення шести тригерів та суматора за модулем два забезпечено контроль обчислюваного результату. Поставлена задача вирішується тим, що у пристрій для зміни порядку розрядів послідовних кодів, що містить реверсивний регістр, елемент НІ, перший і другий елементи І та комутатор, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, вхід режиму пристрою підключено до першого режимного входу реверсивного регістра, першого входу першого елемента І, управляючого входу комутатора та входу елемента НІ, вихід якого підключено до першого входу другого елемента І та другого режимного входу реверсивного регістра, інформаційний вхід пристрою підключено до других входів першого та другого елементів І, виходи яких підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого підключено відповідно до першого та другого інформаційних входів комутатора, вихід якого є інформаційним виходом пристрою, згідно з винаходом, введено: перший, другий, третій, четвертий, п'ятий, шостий тригери та суматор за модулем два, при цьому тактовий вхід пристрою підключено до входу синхронізації кожного тригера, вхід скидання пристрою підключено до входів скидання першого, третього, четвертого, п'ятого й шостого тригерів та входу встановлення другого тригера, інформаційний вхід пристрою підключено до входу дозволу інвертування першого тригера, вихід якого підключено до інформаційного входу четвертого тригера, вхід режиму пристрою підключено до інформаційного входу другого тригера та першого входу суматора за модулем два, другий вхід якого підключено до виходу другого тригера, а вихід до входів дозволу запису четвертого, п'ятого та шостого тригерів, інформаційний вихід пристрою підключено до входу дозволу інвертування третього тригера, вихід якого підключено до інформаційного входу п'ятого тригера, вихід якого підключено до першого розряду контрольного виходу пристрою, вихід четвертого тригера підключено до інформаційного входу шостого тригера, інверсний вихід якого підключено до другого розряду контрольного виходу пристрою. Технічний ефект від запропонованого рішення полягає в тому, що шляхом введення шести тригерів та суматора за модулем два забезпечено контроль результату за парністю, що суттєво підвищує достовірність функціонування пристрою. Підвищення достовірності функціонування пристрою можна оцінити наступним чином. Достовірність ДП функціонування прототипу визначається ймовірністю безвідмовної роботи РБР:ДП=РБР. В запропонованому рішенні достовірність функціонування складається із знань про правильне й неправильне функціонування пристрою та визначається за формулою Д З=РБР+(1РБР) РВП, де РВП - ймовірність виявлення помилки контролем за парністю. Для найбільш 1 UA 110594 C2 5 10 15 20 25 30 35 40 45 50 55 60 ймовірної однократної помилки РВП=0,5 та достовірність функціонування складає ДЗ=РБР+0,5 (1РБР), тобто на 0,5 (1-РБР) перевищує достовірність функціонування прототипу. Наприклад, для РБР=0,9 достовірність функціонування ДЗ=0,95 перевищує ДП на 5 %. Суть винаходу пояснюється кресленням на фіг. 1, де зображено пристрій для зміни порядку розрядів послідовних кодів, що містить елемент НІ 1, перший 2 та другий 3 елементи І, реверсивний регістр 4 та комутатор 5, перший 6, другий 7, третій 8, четвертий 9, п'ятий 10 і шостий 11 тригери, суматор 12 за модулем два, вхід Μ режиму пристрою, інформаційний вхід D пристрою, тактовий вхід С пристрою, вхід R скидання пристрою, інформаційний вихід V пристрою та перший Κ1 і другий K2 розряди контрольного виходу пристрою, при цьому вхід Μ пристрою підключено до входу елемента HI 1, першого входу першого елемента І 2, першого режимного входу SR регістра 4, управляючого входу Υ комутатора 5, інформаційного входу D тригера 7 та першого входу суматора 12, другий вхід якого підключено до виходу тригера 7, а вихід до входів Е дозволу запису тригерів 9,…, 11, вхід D пристрою підключено до других входів елементів І 2 та 3 і входу Τ дозволу інвертування тригера 6, вихід якого підключено до інформаційного входу D тригера 9, вхід С пристрою підключено до входів С синхронізації регістра 4 та тригерів 6,…, 11, вхід R пристрою підключено до входів R скидання регістра 4, тригерів 6, 8,…, 11 та входу встановлення S тригера 7, вихід елемента НІ 1 підключено до першого входу елемента І 3 та другого режимного входу SL регістра 4, виходи елементів І 2 та 3 підключено відповідно до першого DR та другого DL інформаційних входів регістра 4, перший QR та другий QL виходи якого підключено відповідно до першого 1 та другого 2 інформаційних входів комутатора 5, вихід якого підключено до виходу V пристрою та входу Τ дозволу інвертування тригера 8, вихід якого підключено до інформаційного входу D тригера 10, вихід якого підключено до розряду К1 контрольного виходу пристрою, вихід тригера 9 підключено до інформаційного входу D тригера 11, інверсний вихід якого підключено до розряду K2 контрольного виходу пристрою. На фіг. 2 показано часові діаграми роботи блоків пристрою для n=4, а саме, для входів R Т, D, Μ пристрою, входів DR і DL та виходів QR і QL регістра 4, виходу V пристрою, тригерів 6 і 7, що позначені, як Τ 6 і Τ 7, суматора 12 (позначено L 12), а також тригерів 8,…, 11, позначених Т 8,Т 9,Т 10, Τ 11. Розряди першого, другого та третього послідовних кодів пронумеровано 1, 2, 3, 4; 1*, 2*, 3*, 4* та 1**, 2**, 3**, 4**, відповідно. Пристрій працює у такий спосіб. На вхід R пристрою та відповідно на вхід R скидання регістра 4, тригерів 6, 8,…, 11 та вхід S встановлення тригера 7 подається сигнал, що встановлює регістр 4, тригери 6, 8,…, 11 у нульове значення та тригер 7 у одиничне значення. На вхід С пристрою та відповідно на вхід С синхронізації регістра 4 та тригерів 6,…, 11 подаються синхроімпульси, що тактують їх роботу. На вхід D пристрою та відповідно на другі входи елементів І 2 і 3 та вхід Τ дозволу інвертування тригера 6 подається послідовність послідовних кодів, кожний з яких має довжину n та приймається у пристрій за n тактів. На вхід Μ пристрою подається сигнал управління роботою елемента HI 1, регістра 4, тригерів 7, 9,…, 11 та суматора 12. Сигнал управління зі входу Μ пристрою та його інверсія з виходу елемента НІ 1 управляють проходженням послідовних кодів зі входу D пристрою через елементи І 2 та 3 відповідно на входи DR та DL регістра 4, а також режимами роботи регістра 4. Кожні n тактів сигнал управління інвертує своє значення. Під цим управлінням перший і наступні непарні (за номером) послідовні коди приходять на вхід DR, а другий і наступні парні - на вхід DL регістра 4. Водночас на режимних входах SR та SL регістра 4 встановлюються комбінації 10 2 та 012 відповідно для непарних та парних послідовних кодів. Ці комбінації визначають просування послідовного коду відповідно праворуч через вхід DR та ліворуч через вхід DL. Таким чином, на перших n тактах в регістр 4 просувається праворуч перший послідовний код, який на наступних n тактах висувається з регістра 4 ліворуч із зворотним порядком розрядів, а на звільнені позиції водночас просувається другий послідовний код, що далі повторюється з наступними непарними та парними за номером послідовними кодами. Непарні та парні за номером послідовні коди висуваються з регістра 4 із зворотним порядком розрядів відповідно через виходи QR та QL, з яких подаються на інформаційні входи 1 та 2 комутатора 5. Під управлінням сигналу зі входу Μ пристрою комутатор 5 вибирає послідовні коди (із зворотним порядком розрядів) підряд у відповідності до номерів кодів та видає на вихід пристрою V. Тригери 6 і 8, що є синхронними Т-тригерами, приймають на входи Τ дозволу інвертування вхідну та вихідну послідовності з входу D та виходу V пристрою, відповідно. Одиничні біти послідовностей дозволяють інвертувати виходи тригерів 6 і 8 за переднім фронтом синхроімпульсів, обчислюючи послідовності сум за модулем два бітів, що вже прийшли: 2 UA 110594 C2 5 10 15 20 25 А1=1; А2=12; А3=123; Α4=1234; Α1*=1…41*…; В1=1; В2=2; В3=123; В4=1234; В1*=1…41*… Тригер 7, як і тригери 9,…, 11, є D-тригером. Він затримує управляючий сигнал Μ на один такт, а суматор 12 знаходить суму за модулем два вихідного та затриманого сигналу М, формуючи сигнал, що одиничними значеннями відмічає прихід останнього біта кожного послідовного коду на вході D та виході V пристрою. Ці значення приходять на входи Ε тригерів 9,…, 11, що отримують дозвіл на прийняття сум за модулем два прийнятих (тригери 9, 11) та виданих (тригер 10) послідовних кодів. Тригер 11 затримує суми за модулем два прийнятих послідовних кодів на n тактів, що дозволяє видавати їх водночас із відповідними сумами виданих послідовних кодів. Суми за модулем два прийнятих та виданих послідовних кодів видаються відповідно у прямому та інверсному значенні з прямого та інверсного виходів тригерів 10 та 11 на розряди K1 та K2 контрольного виходу пристрою. Оскільки послідовні коди, що приймаються та видаються у зворотному порядку розрядів, мають однакові суми за модулем два, то при правильному функціонуванні пристрою на розрядах K1 та K2 будуть обчислюватися взаємно інверсні значення 012 або 102, а однакові значення 002 або 112 вкажуть на виявлення помилки та неправильне функціонування пристрою. Пристрій може бути використаний в машинобудуванні для побудови обчислювальних систем, що обробляють послідовні коди з підвищеною достовірністю функціонування. Джерела інформації: 1. Применение интегральных микросхем в электронной вычислительной технике: Справочник / Р.В. Данилов, С.А. Ельцова, Ю.П. Иванов и др.; Под ред. Б.Н. Файзулаева, Б.В. Тарабрина. - М.: Радио и связь, 1987. - 384 с, стр. 42-43, рис. 3.36; 2. Патент на корисну модель № 98045 Україна, МПК G06F 7/552. Пристрій для зміни порядку розрядів послідовних кодів / О.В. Дрозд, С.А. Нестеренко, С.Г. Антощук, Ю.В. Дрозд. - № u201412908; Опубл. 10.04.2015, Бюл. № 7. ФОРМУЛА ВИНАХОДУ 30 35 40 45 50 Пристрій для зміни порядку розрядів послідовних кодів, що містить реверсивний регістр, елемент НІ, перший і другий елементи І та комутатор, при цьому тактовий вхід пристрою підключено до входу синхронізації реверсивного регістра, вхід скидання пристрою підключено до входу скидання реверсивного регістра, вхід режиму пристрою підключено до першого режимного входу реверсивного регістра, першого входу першого елемента І, управляючого входу комутатора та входу елемента НІ, вихід якого підключено до першого входу другого елемента І та другого режимного входу реверсивного регістра, інформаційний вхід пристрою підключено до других входів першого та другого елементів І, виходи яких підключено відповідно до першого та другого інформаційних входів реверсивного регістра, перший та другий виходи якого підключено відповідно до першого та другого інформаційних входів комутатора, вихід якого є інформаційним виходом пристрою, який відрізняється тим, що введено перший, другий, третій, четвертий, п'ятий, шостий тригери та суматор за модулем два, при цьому тактовий вхід пристрою підключено до входу синхронізації кожного тригера, вхід скидання пристрою підключено до входів скидання першого, третього, четвертого, п'ятого й шостого тригерів та входу встановлення другого тригера, інформаційний вхід пристрою підключено до входу дозволу інвертування першого тригера, вихід якого підключено до інформаційного входу четвертого тригера, вхід режиму пристрою підключено до інформаційного входу другого тригера та першого входу суматора за модулем два, другий вхід якого підключено до виходу другого тригера, а вихід до входів дозволу запису четвертого, п'ятого та шостого тригерів, інформаційний вихід пристрою підключено до входу дозволу інвертування третього тригера, вихід якого підключено до інформаційного входу п'ятого тригера, вихід якого підключено до першого розряду контрольного виходу пристрою, вихід четвертого тригера підключено до інформаційного входу шостого тригера, інверсний вихід якого підключено до другого розряду контрольного виходу пристрою. 3 UA 110594 C2 4 UA 110594 C2 Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/552

Мітки: розрядів, порядку, зміни, кодів, послідовних, пристрій

Код посилання

<a href="https://ua.patents.su/7-110594-pristrijj-dlya-zmini-poryadku-rozryadiv-poslidovnikh-kodiv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для зміни порядку розрядів послідовних кодів</a>

Попередній патент: Спосіб одержання поверхнево-активних речовин

Наступний патент: Спосіб керування асинхронним двигуном

Випадковий патент: Спосіб діагностики рівня психосоціальної дезадаптації хворих на соматичні захворювання