Імпульсний синхронізатор

Номер патенту: 119430

Опубліковано: 25.09.2017

Автори: Щека Володимир Миколайович, Мушаров Андрій Олександрович, Уваров Володимир Миколайович, Куравська Надія Миколаївна, Кононов Борис Тимофійович, Нечаус Андрій Олександрович

Формула / Реферат

Імпульсний синхронізатор, який містить вхідний блок, у складі двох формувачів імпульсів постійної тривалості, які підключені на напруги генератора та мережі, логічну схему збігу, блок вмикання, у складі блока контролю частоти генератора та блока контролю частоти мережі і вихідну логічну схему "АБО", кожен з блоків контролю частоти містить формувач допоміжних імпульсів, проміжну логічну схему збігу, логічний блок і вихідну логічну схему збігу, який відрізняється тим, що в склад кожного з блоків контролю частоти додатково введені проміжний формувач допоміжних імпульсів, схема заборони, перша та друга проміжна логічна схема збігу, при цьому вхід проміжного формувача допоміжних імпульсів з'єднаний з виходом формувача допоміжних імпульсів, вхід якого приєднаний в блоці контролю частоти генератора до виходу формувача імпульсів постійної тривалості, підключеного на напругу генератора, а в блоці контролю частоти мережі вхід формувача допоміжних імпульсів з'єднаний з виходом формувача імпульсів постійної тривалості, підключеного на напругу мережі, вихід проміжного формувача допоміжних імпульсів з'єднаний з першим входом проміжної логічної схеми збігу блока контролю частоти генератора, другий вхід якої з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, а в блоці контролю частоти мережі перший вхід проміжної логічної схеми збігу з'єднаний з виходом проміжного формувача імпульсів постійної тривалості свого блока контролю частоти, а другий вхід цієї схеми з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, вихід проміжної логічної схеми збігу з'єднаний з робочим входом логічного блока свого блока контролю частоти та зі скидаючим входом логічного блока іншого блоку контролю частоти, перший та другий виходи логічного блока з'єднані з входом схеми заборони, вихід якої з'єднаний з входом другої допоміжної логічної схеми збігу, до іншого входу якої приєднаний вихід першої допоміжної логічної схеми збігу, перший вхід якої з'єднаний з виходом формувача допоміжних імпульсів свого блока контролю частоти, а другий вхід з виходом формувача імпульсів постійної тривалості іншого каналу, вихід другої допоміжної логічної схеми збігу з'єднаний з входом вихідної логічної схеми "АБО" блока вмикання, а інші входи цієї схеми з'єднані з виходами других проміжних логічних схем збігу блоків контролю частоти та з виходами вихідних логічних схем збігу блоків контролю частоти, перші входи яких з'єднані з другими виходами логічних блоків свого каналу частоти та з виходом логічної схеми збігу вхідного блока.

Текст

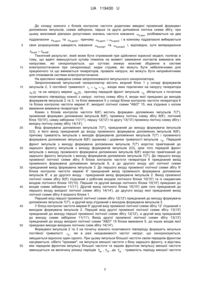

Реферат: Імпульсний синхронізатор містить вхідний блок у складі двох формувачів імпульсів постійної тривалості, які підключені на напруги генератора та мережі, логічну схему збігу, блок вмикання, у складі блока контролю частоти генератора та блока контролю частоти мережі і вихідну логічну схему "АБО". Кожен з блоків контролю частоти містить формувач допоміжних імпульсів, проміжну логічну схему збігу, логічний блок і вихідну логічну схему збігу. В склад кожного з блоків контролю частоти додатково введені проміжний формувач допоміжних імпульсів, схема заборони, перша та друга проміжна логічна схема збігу. При цьому вхід проміжного формувача допоміжних імпульсів з'єднаний з виходом формувача допоміжних імпульсів, вхід якого приєднаний в блоці контролю частоти генератора до виходу формувача імпульсів постійної тривалості, підключеного на напругу генератора. В блоці контролю частоти мережі вхід формувача допоміжних імпульсів з'єднаний з виходом формувача імпульсів постійної тривалості, підключеного на напругу мережі, вихід проміжного формувача допоміжних імпульсів з'єднаний з першим входом проміжної логічної схеми збігу блока контролю частоти генератора, другий вхід якої з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі. В блоці контролю частоти мережі перший вхід проміжної логічної схеми збігу з'єднаний з виходом проміжного формувача імпульсів постійної тривалості свого блока контролю частоти. Другий вхід цієї схеми з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, вихід проміжної логічної схеми збігу з'єднаний з робочим входом логічного блока свого блока контролю частоти та зі скидаючим входом логічного блока іншого блока контролю частоти. Перший та другий виходи логічного блока з'єднані з входом схеми заборони, вихід якої з'єднаний з входом другої допоміжної логічної схеми збігу, До іншого входу якої приєднаний вихід першої допоміжної логічної схеми збігу, перший вхід якої з'єднаний з виходом формувача допоміжних імпульсів свого блока контролю частоти. Другий вхід з виходом формувача імпульсів постійної тривалості іншого каналу, вихід другої допоміжної логічної схеми збігу з'єднаний з входом вихідної логічної схеми "АБО" блока вмикання. Інші входи цієї схеми з'єднані з виходами других проміжних логічних схем збігу блоків контролю частоти та з виходами вихідних логічних схем збігу блоків контролю частоти, перші входи яких з'єднані з другими виходами логічних блоків свого каналу частоти та з виходом логічної схеми збігу вхідного блока. UA 119430 U (12) UA 119430 U UA 119430 U 5 10 15 20 25 30 35 40 45 50 55 Запропонована корисна модель належить до галузі електроенергетики і може бути використана для вмикання на паралельну роботу синхронних генераторів. Відомий пристрій для автоматичної синхронізації синхронних генераторів [1], який містить формувачі імпульсів, блок контролю збігу фаз, блок вмикання у складі блока контролю різниці частот на базі інтегруючої ланки, порогового елемента та виконавчого органу. Недоліком відомого пристрою є низька точність визначення моменту подачі команди на вмикання вимикача генератора, яка обумовлена режимом роботи інтегруючої ланки, де не передбачена можливість скидання інтегруючої ланки у вихідний стан. Крім цього для оцінювання різниці частот в пристрої використовується час, який дорівнює періоду биття, при цьому можлива затримка подачі команди, оскільки на момент першого збігу фаз синхронізованих напруг різниця частот ще може бути не визначена. Найбільш близьким аналогом до запропонованої корисної моделі є імпульсний синхронізатор [2], який містить вхідний блок з логічною схемою збігу з формувачами імпульсів постійної тривалості, які підключені на напруги генератора та мережі, та блок вмикання, який містить блок контролю частоти генератора та блок контролю частоти мережі. Кожний з блоків контролю частоти містить у своєму складі формувач допоміжних імпульсів, вихід якого з'єднаний з входом проміжної логічної схеми збігу, інший вхід якої з'єднаний з виходом відповідного формувача імпульсів. Вихід проміжної схеми збігу приєднаний до робочого входу свого логічного блока та до скидаючого входу логічного блока іншого блока контролю частоти. Вихід логічного блока з'єднаний з входом вихідної логічної схеми збігу, другий вхід якої з'єднаний з виходом логічної схеми збігу вхідного блока. Виходи вихідних логічних схем збігу з'єднані із входами вихідної логічної схеми "АБО" у вихідному колі вмикання генераторного вимикача. Недоліком цього пристрою є можливість появи провалів напруги та кидків струмів при синхронізації, обумовлених тим, що на момент замикання контактів вимикача генератора кут між синхронізованими напругами може не дорівнювати нулю. В основу корисної моделі поставлена задача створити імпульсний синхронізатор, який дозволить зменшити кутову помилку пом на момент замикання контактів вимикача генератора і тим самим зменшити негативні наслідки збурень, які можуть мати місце при цьому. Поставлена задача вирішується тим, що в імпульсному синхронізаторі, який містить вхідний блок, у складі двох формувачів імпульсів постійної тривалості, які підключені на напруги генератора та мережі, логічну схему збігу, блок вмикання, у складі блока контролю частоти генератора та блока контролю частоти мережі і вихідну логічну схему "АБО", кожен з блоків контролю частоти містить формувач допоміжних імпульсів, проміжну логічну схему збігу, логічний блок і вихідну логічну схему збігу, згідно з корисною моделлю, в склад кожного з блоків контролю частоти додатково введені проміжний формувач допоміжних імпульсів, схема заборони, перша та друга проміжна логічна схема збігу, при цьому вхід проміжного формувача допоміжних імпульсів з'єднаний з виходом формувача допоміжних імпульсів, вхід якого приєднаний в блоці контролю частоти генератора до виходу формувача імпульсів постійної тривалості, підключеного на напругу генератора, а в блоці контролю частоти мережі вхід формувача допоміжних імпульсів з'єднаний з виходом формувача імпульсів постійної тривалості, підключеного на напругу мережі, вихід проміжного формувача допоміжних імпульсів з'єднаний з першим входом проміжної логічної схеми збігу блока контролю частоти генератора, другий вхід якої з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, а в блоці контролю частоти мережі перший вхід проміжної логічної схеми збігу з'єднаний з виходом проміжного формувача імпульсів постійної тривалості свого блока контролю частоти, а другий вхід цієї схеми з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, вихід проміжної логічної схеми збігу з'єднаний з робочим входом логічного блока свого блока контролю частоти та зі скидаючим входом логічного блока іншого блока контролю частоти, перший та другий виходи логічного блока з'єднані з входом схеми заборони, вихід якої з'єднаний з входом другої допоміжної логічної схеми збігу, до іншого входу якої приєднаний вихід першої допоміжної логічної схеми збігу, перший вхід якої з'єднаний з виходом формувача допоміжних імпульсів свого блока контролю частоти, а другий вхід з виходом формувача імпульсів постійної тривалості іншого каналу, вихід другої допоміжної логічної схеми збігу з'єднаний з входом вихідної логічної схеми "АБО" блока вмикання, а інші входи цієї схеми з'єднані з виходами других проміжних логічних схем збігу блоків контролю частоти та з виходами вихідних логічних схем збігу блоків контролю частоти, перші входи яких з'єднані з другими виходами логічних блоків свого каналу частоти та з виходом логічної схеми збігу вхідного блока. 1 UA 119430 U До складу кожного з блоків контролю частоти додатково введені проміжний формувач допоміжних імпульсів, схема заборони, перша та друга допоміжна логічна схема збігу, при цьому можливий діапазон допустимих значень частоти ковзання s доп розбивається на два піддіапазони s доп1 та s доп2 , причому s доп1 s доп2 і в кожному піддіапазоні вибирається 5 10 15 20 25 30 35 40 45 50 55 своя розрахункова швидкість ковзання s розр1 та s розр 2 і, відповідно, кути випередження в ип1 в ип2 . Технічний результат, який може бути отриманий при здійсненні корисної моделі, полягає в тому, що вдвічі зменшується кутова помилка на момент замикання контактів вимикача між напругами, які синхронізуються, що суттєво знижує можливі збурення в системі електропостачання при синхронізації, кидки струмів, які можуть бути небезпечними для працюючого та що вмикається генераторів, провали напруги, які можуть бути неприйнятними для споживачів системи електропостачання. На кресленні наведена схема запропонованого імпульсного синхронізатора. Запропонований імпульсний синхронізатор містить вхідний блок 1 у складі формувачів імпульсів 2, 3 постійної тривалості г м 0 , входи яких підключені на напругу генератора uг (t) та на напругу мережі uм (t) , причому передній фронт імпульсів 0 збігається з початком позитивного півперіоду кожної з напруг, логічну схему збігу 4, входи якої приєднані до виходів формувачів імпульсів 2 та 3, та блок вмикання 5 у складі блока контролю частоти генератора 6 та блока контролю частоти мережі 6', вихідної логічної схеми "АБО" 15, яка з'єднана з колом вмикання вимикача генератора 16. Кожен з блоків контролю частоти 6(6') містить формувач допоміжних імпульсів 7(7'), проміжний формувач допоміжних імпульсів 8(8'), проміжну логічну схему збігу 9(9'), логічний блок 10(10'), схему заборони 11(11'), першу 12(12') та другу 13(13') проміжну логічну схему збігу і вихідну логічну схему збігу 14(14'). Вхід формувача допоміжних імпульсів 7(7'), приєднаний до виходу формувача імпульсів 2(3), а його вихід приєднаний до входу проміжного формувача допоміжних імпульсів 8(8'), причому тривалість імпульсів з виходів формувачів допоміжних імпульсів 7(7') і проміжного формувача допоміжних імпульсів 8(8') однакова і дорівнює тривалості імпульсів 0 . Передній фронт імпульсів з виходу формувача допоміжних імпульсів 7(7') жорстко прив'язаний до заднього фронту імпульсів з виходу формувачів імпульсів 2(3), крім того передній фронт імпульсів з виходу проміжного формувача допоміжних імпульсів 8(8') жорстко прив'язаний до заднього фронту імпульсів з виходу формувачів допоміжних імпульсів 7(7'). До першого входу проміжної логічної схеми збігу 9 блока контролю частоти генератора 6 приєднаний вихід проміжного формувача допоміжних імпульсів 8, а до другого входу цієї логічної схеми приєднаний вихід формувача імпульсів 3. До першого входу проміжної логічної схеми збігу 9' блока контролю частоти мережі 6' приєднаний вихід проміжного формувача допоміжних імпульсів 8', а до другого входу - приєднаний вихід формувача імпульсів 2. Вихід проміжної логічної схеми збігу 9(9') з'єднаний з робочим входом логічного блока 10(10') та із скидаючим входом логічного блока 10'(10). Перший та другий виходи логічного блока 10(10') приєднані до входів схеми заборони 11(11'). Другий вихід логічного блока 10(10') крім того приєднаний до першого входу вихідної логічної схеми збігу 14(14'), до другого входу якої приєднаний вихід логічної схеми збігу 4 вхідного блока 1. Перший вхід першої проміжної логічної схеми збігу 12(12') приєднаний до виходу формувача допоміжних імпульсів 7(7'), а другий вхід з'єднаний з виходом формувача імпульсів 3. У блоці контролю частоти мережі 6' другий вхід проміжної логічної схеми збігу 12' з'єднаний з виходом формувача імпульсів 2. Перший вхід другої проміжної логічної схеми збігу 13(13') приєднаний до виходу першої проміжної логічної схеми збігу 12(12'), а другий вхід приєднаний до виходу схеми заборони 11(11'). Вихід другої проміжної логічної схеми збігу 13(13') приєднаний до входу вихідної логічної схеми "АБО" 15 блока вмикання 5, до інших входів якої приєднані виходи вихідних логічних схем збігу 14(14'). Формувачі імпульсів 2 та 3 на початку кожного позитивного півперіоду формують імпульси постійної тривалості 0 , які в разі неоднаковості частот напруг, що синхронізуються, зміщуються відносно один одного. При цьому імпульси більшої частоти своїм переднім фронтом насуваються, нібито "кроками", на імпульси меншої частоти з боку заднього фронту, а відстань між переднім фронтом імпульсу більшої частоти та заднім фронтом імпульсу меншої частоти зменшується на величину різниці періодів Tм Т б , де Tм - тривалість періоду меншої частоти 2 UA 119430 U fм , а Т б - тривалість періоду більшої частоти fб . В момент спрацювання логічної схеми збігу 4 фіксується кут випередження в ип1 , який дорівнює: в ип1 5 (1) а в момент спрацювання першої проміжної логічної схеми збігу 12(12') фіксується кут випередження в ип2 , який дорівнює: в ип2 10 360 0 360 fм 0 , Тм 360 0 360 fм 20 . Тм (2). Оскільки в реальних умовах частота fм змінюється незначно, кути в ип1 та в ип2 рахуються незмінними. Спрацювання першої проміжної логічної схеми збігу 12(12') або логічної схеми збігу 4 є першою обов'язковою умовою формування команди на вмикання вимикача генератора. Другою обов'язковою умовою є поява сигналів на виходах логічних блоків 10(10') одного з блоків контролю частоти 6(6'). Друга умова еквівалента умови дотримання допустимої різниці частот: 15 fг fм fs fs доп , (3) де fs - поточне значення частоти ковзання; fs доп - допустиме по обраному критерію синхронізації значення частоти ковзання. 20 Оцінювання різниці частот здійснюється шляхом визначення кількості "кроків" N, яке необхідно зробити передньому фронту імпульсів більшої частоти для того, щоби пройти шлях довжиною 0 по проміжному допоміжному імпульсуменшої частоти. Кількість "кроків" N визначається за формулою: N 0 f f 0 мб. Tм Т б fs (4) 25 З (4) слідує, що умова (3) трансформується в умову N Nдоп , де Nдоп - мінімально допустима кількість "кроків". Оскільки діапазон допустимих значень кутової частоти ковзання розбитий на два піддіапазони, в логічному блоці 10(10') визначаються значення N1доп та N2 доп . При цьому вибирається що N2доп N1доп , тобто для більших допустимих частот ковзання команда на 30 вмикання буде подана з більшим кутом випередження, який обчислюється співвідношенням (2). В випадку, коли кількість "кроків" більше або дорівнює N2 доп , команда на вмикання подається з 35 40 45 меншим кутом випередження, який обчислюється за допомогою співвідношення (1). Контроль частоти блоками контролю частоти генератора 6 і контролю частоти мережі 6' здійснюється перед фіксацією моменту визначення кута випередження, що дозволяє підвищити швидкодію синхронізатора, особливо в діапазоні малих значень частоти ковзання. Це досягається завдяки тому, що збіг основних імпульсів більшої частоти з допоміжними імпульсами, сформованими проміжним формувачем допоміжних імпульсів 8(8') відбувається раніше збігу основних імпульсів більшої частоти з допоміжними імпульсами меншої частоти. Логічний блок 10(10') може бути реалізований на базі лічильника, дешифратора та тригера. В зв'язку з тим, що синхронізація можлива як при позитивних, так і при негативних значеннях частоти ковзання, блок вмикання 5 містить два повністю ідентичних блоки контролю частоти 6(6'). Робота синхронізатора полягає у наступному. Напруги генератора та мережі на початку кожного періоду запускають формувачі імпульсів 2, 3, які по своєму задньому фронту запускають формувачі допоміжних імпульсів 7(7'), які в свою чергу запускають проміжні формувачі допоміжних імпульсів 8(8'). Проміжна логічна схема збігу 9(9') фіксує моменти збігу 3 UA 119430 U основних імпульсів більшої частоти з допоміжними імпульсами меншої частоти, сформованими проміжним формувачем допоміжних імпульсів 8(8'). Кількість збігів і, відповідно, частоту ковзання визначає логічний блок 10(10'). Поява сигналу на першому виході логічного блока 10(10') означає, що кількість збігів більше або дорівнює N1доп , що відповідає першому 5 10 15 20 25 30 піддіапазону допустимих значень частоти ковзання, для якого кут випередження повинен бути більшим. Поява сигналу на другому виході логічного блока 10(10') означає, що кількість збігів більша або дорівнює N2 доп , що відповідає другому піддіапазону допустимих значень частоти ковзання, для якого кут випередження повинен бути меншим. У випадку появи сигналу лише на першому виході логічного блока 10(10') з'являється сигнал на виході схеми заборони 11(11'), тобто заборона по другому входу цієї схеми, що забезпечує подачу сигналу на другий вхід другої проміжної логічної схеми збігу 13(13'), на перший вхід якої подається сигнал з виходу першої проміжної логічної схеми збігу 12(12'), що фіксує збіг переднього фронту основних імпульсів більшої частоти з заднім фронтом допоміжних імпульсів меншої частоти. Спрацювання другої проміжної логічної схеми збігу 13(13') приводить до спрацювання вихідної логічної схеми "АБО" 15 і подачі команди на вмикання вимикача генератора з більшим кутом випередження. У випадку, коли сигнали з'являються на обох виходах логічного блока 10(10'), сигнал на виході схеми заборони 11(11') відсутній, що не дозволяє спрацювати другій проміжній логічній схемі збігу 13(13'). При цьому спрацьовує вихідна логічна схема збігу 14(14') і команда на вмикання вимикача генератора подається після збігу переднього фронту основних імпульсів більшої частоти з заднім фронтом основних імпульсів меншої частоти, що фіксується логічною схемою збігу 4, сигнал з виходу якої, при наявності сигналу на другому виході логічного блока 10(10'), приводить до спрацювання вихідної логічної схеми збігу 14(14') та подачі команди на вмикання вимикача генератора з меншим кутом випередження. Джерела інформації: 1. АС СРСР № 486419, МПК: H02J 3/42. Устройство для автоматической синхронизации синхронных генераторов / А.К. Васильев, А.В. Воршевский, И.М. Петрузов, В.П. Пляшкевич; опубл. 30.09.1975, БИ №36. 2. АС СРСР № 739698, МПК: H02J 3/42. Импульсный синхронизатор / Н.И. Григоров, Б.Т. Кононов, A.M. Зазнобин, ПП. Найдюк, А.А. Орлов, А.А. Призенцов, В.З. Ройк, А.Е. Церковный. Заявлено 21.10.1979; опубл. 05.06.1980, БИ №21. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 50 55 60 Імпульсний синхронізатор, який містить вхідний блок, у складі двох формувачів імпульсів постійної тривалості, які підключені на напруги генератора та мережі, логічну схему збігу, блок вмикання, у складі блока контролю частоти генератора та блока контролю частоти мережі і вихідну логічну схему "АБО", кожен з блоків контролю частоти містить формувач допоміжних імпульсів, проміжну логічну схему збігу, логічний блок і вихідну логічну схему збігу, який відрізняється тим, що в склад кожного з блоків контролю частоти додатково введені проміжний формувач допоміжних імпульсів, схема заборони, перша та друга проміжна логічна схема збігу, при цьому вхід проміжного формувача допоміжних імпульсів з'єднаний з виходом формувача допоміжних імпульсів, вхід якого приєднаний в блоці контролю частоти генератора до виходу формувача імпульсів постійної тривалості, підключеного на напругу генератора, а в блоці контролю частоти мережі вхід формувача допоміжних імпульсів з'єднаний з виходом формувача імпульсів постійної тривалості, підключеного на напругу мережі, вихід проміжного формувача допоміжних імпульсів з'єднаний з першим входом проміжної логічної схеми збігу блока контролю частоти генератора, другий вхід якої з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, а в блоці контролю частоти мережі перший вхід проміжної логічної схеми збігу з'єднаний з виходом проміжного формувача імпульсів постійної тривалості свого блока контролю частоти, а другий вхід цієї схеми з'єднаний з виходом формувача допоміжних імпульсів, підключеного на напругу мережі, вихід проміжної логічної схеми збігу з'єднаний з робочим входом логічного блока свого блока контролю частоти та зі скидаючим входом логічного блока іншого блоку контролю частоти, перший та другий виходи логічного блока з'єднані з входом схеми заборони, вихід якої з'єднаний з входом другої допоміжної логічної схеми збігу, до іншого входу якої приєднаний вихід першої допоміжної логічної схеми збігу, перший вхід якої з'єднаний з виходом формувача допоміжних імпульсів свого блока контролю частоти, а другий вхід з виходом формувача імпульсів постійної тривалості іншого каналу, вихід другої допоміжної логічної схеми збігу з'єднаний з входом вихідної логічної схеми "АБО" блока вмикання, а інші входи цієї схеми з'єднані з виходами других проміжних логічних схем збігу блоків контролю частоти та з виходами вихідних логічних 4 UA 119430 U схем збігу блоків контролю частоти, перші входи яких з'єднані з другими виходами логічних блоків свого каналу частоти та з виходом логічної схеми збігу вхідного блока. Комп’ютерна верстка А. Крижанівський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H02J 3/00

Мітки: синхронізатор, імпульсний

Код посилання

<a href="https://ua.patents.su/7-119430-impulsnijj-sinkhronizator.html" target="_blank" rel="follow" title="База патентів України">Імпульсний синхронізатор</a>

Попередній патент: Пристрій для лущення та шліфування зерна

Наступний патент: Хірургічний інструмент для вимірювання порожнини та дилятації кавернозних тіл при ендофалопротезуванні

Випадковий патент: Процес прогнозування та ранньої діагностики екологічно детермінованих станів у дітей, що проживають в регіонах із різним характером забруднення довкілля