Двотактний симетричний підсилювач струму

Номер патенту: 120004

Опубліковано: 25.10.2017

Автори: Нікітін Юрій Юрійович, Богомолов Сергій Віталійович, Гарнага Володимир Анатолійович, Азаров Олексій Дмитрович

Формула / Реферат

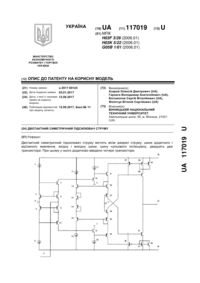

Двотактний симетричний підсилювач струму, що містить шість джерел струму, шини додатного та від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять два транзистори, причому другий вхід першого та перший вхід другого джерела струму з'єднано з колектором першого та другого транзистора відповідно, бази першого та другого транзисторів з'єднано з базами та колекторами четвертого та п'ятого транзисторів відповідно, колектор четвертого транзистора з'єднано з емітером третього транзистора, база якого з'єднана з другим входом першого джерела струму, колектор п'ятого транзистора з'єднано з емітером шостого транзистора, база якого з'єднана з першим входом другого джерела струму, колектор третього транзистора з'єднано з другим входом третього джерела струму і з колектором сьомого та з базою одинадцятого транзисторів відповідно, колектор шостого транзистора з'єднано з першим входом четвертого джерела струму і з колектором десятого та з базою шістнадцятого транзисторів відповідно, емітер шістнадцятого транзистора з'єднано з колектором п'ятнадцятого транзистора, емітер одинадцятого транзистора з'єднано з колектором дванадцятого транзистора, емітери дванадцятого та чотирнадцятого транзисторів з'єднано з емітерами тринадцятого та п'ятнадцятого транзисторів відповідно, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектор тринадцятого об'єднано та з'єднано з базою двадцять першого та колектором вісімнадцятого транзисторів відповідно, колектор чотирнадцятого об'єднано та з'єднано з базою двадцятого та колектором сімнадцятого транзисторів, колектор одинадцятого транзистора з'єднано з базами сімнадцятого та дев'ятнадцятого транзисторів, колектор шістнадцятого транзистора з'єднано з базами вісімнадцятого та двадцять другого транзисторів, бази сімнадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів та другим входом п'ятого джерела струму, бази вісімнадцятого та двадцять другого транзисторів об'єднано та з'єднано з колектором двадцять другого та емітером двадцять першого транзисторів та першим входом шостого джерела струму, перші входи першого, третього та п'ятого джерел струму та емітери сімнадцятого та дев'ятнадцятого транзисторів підключено до шини додатного живлення, другі входи другого, четвертого та шостого джерел струму та емітери вісімнадцятого та двадцять другого транзисторів підключено до шини від'ємного живлення, колектори двадцять першого та двадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що у нього введено чотири транзистори, причому бази двадцять п'ятого та двадцять шостого транзисторів з'єднано з вхідною шиною, емітер двадцять четвертого транзистора з'єднано з емітером другого транзистора, колектор якого під'єднано до шини додатного живлення, емітер першого транзистора з'єднано з емітером двадцять третього транзистора, колектор якого під'єднано до шини від'ємного живлення, бази двадцять третього та двадцять четвертого транзисторів під'єднано до шини нульового потенціалу, емітер четвертого транзистора з'єднано з емітером двадцять п'ятого транзистора, колектор якого під'єднано до шини від'ємного живлення, емітер п'ятого транзистора з'єднано з емітером двадцять шостого транзистора, колектор якого під'єднано до шини додатного живлення, емітер сьомого транзистора з'єднано з емітером восьмого транзистора, емітер дев'ятого транзистора з'єднано з емітером десятого транзистора, бази і колектори восьмого та дев'ятого транзисторів об'єднано, бази сьомого та дванадцятого транзисторів об'єднано і з'єднано з емітером одинадцятого та колектором дванадцятого транзисторів, бази десятого та п'ятнадцятого транзисторів об'єднано і з'єднано з емітером шістнадцятого та колектором п'ятнадцятого транзисторів.

Текст

Реферат: Двотактний симетричний підсилювач струму, в якому перше джерело струму та перший, третій і четвертий транзистори, а також друге джерело струму, другий, п'ятий і шостий транзистори утворюють схему задання напруги зміщення на вхідному каскаді. Сьомий, восьмий, дванадцятий, тринадцятий та дев'ятий, десятий, чотирнадцятий, п'ятнадцятий транзистори утворюють двонаправлений відбивач струму. Одинадцятий та шістнадцятий транзистори утворюють проміжний підсилювальний каскад. Вихідний каскад утворений за допомогою двох відбивачів струму, які складаються з сімнадцятого, дев'ятнадцятого і двадцятого транзисторів та п'ятого джерела струму і відповідно з вісімнадцятого, двадцять першого, двадцять другого транзисторів та шостого джерела струму. UA 120004 U (54) ДВОТАКТНИЙ СИМЕТРИЧНИЙ ПІДСИЛЮВАЧ СТРУМУ UA 120004 U UA 120004 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах і цифрових вимірювальних приладах. Відомо двотактний симетричний підсилювач струму (Multi-stage current feedback amplifier, United States Patent 5,742,154, April 21, 1998), який містить джерело струму, операційний підсилювач, шини додатного і від'ємного живлення, вхідну і вихідну шини, шістнадцять транзисторів, причому вхідну шину з'єднано з емітерами четвертого та п'ятого транзисторів та емітерами дванадцятого та тринадцятого транзисторів відповідно, колектори третього та четвертого транзисторів об'єднано та з'єднано з базами першого та четвертого транзисторів, колектори п'ятого та шостого транзисторів об'єднано та з'єднано з базами другого та п'ятого транзисторів, емітери першого та другого транзистора об'єднано між собою, бази третього та дев'ятого транзисторів об'єднано і з'єднано з колектором дев'ятого транзистора і першим входом джерела струму, бази шостого та десятого транзисторів об'єднано і з'єднано з колектором десятого транзистора і другим входом джерела струму, бази дванадцятого та тринадцятого транзисторів з'єднано з базами четвертого та п'ятого транзисторів відповідно, бази сьомого та одинадцятого транзисторів об'єднано та з'єднано з колекторами сьомого та першого транзисторів, бази восьмого та чотирнадцятого транзисторів об'єднано та з'єднано з колекторами восьмого та другого транзисторів, колектори одинадцятого та дванадцятого транзисторів об'єднано і з'єднано з базою п'ятнадцятого транзистора, колектори тринадцятого та чотирнадцятого транзисторів об'єднано і з'єднано з базою шістнадцятого транзистора, колектори п'ятнадцятого та шістнадцятого транзисторів з'єднано з входом операційного підсилювача, вихід операційного підсилювача з'єднано з вихідною шиною, емітери третього, сьомого, дев'ятого, одинадцятого та п'ятнадцятого транзисторів підключено до шини додатного живлення, емітери шостого, восьмого, десятого, чотирнадцятого та шістнадцятого транзисторів підключено до шини від'ємного живлення. Як найближчий аналог вибрано двотактний симетричний підсилювач струму [Патент України № 107585, бюл. № 11, 2016 р.], який містить вісім джерел струму, шини додатного та від'ємного живлення, вхідну і вихідну шини, дві шини нульового потенціалу, двадцять два транзистори, причому вхідну шину, яку з'єднано з емітерами четвертого та п'ятого транзисторів, бази першого та четвертого транзисторів об'єднано і з'єднано з емітером третього та колектором четвертого транзисторів, бази другого та п'ятого транзисторів об'єднано та з'єднано з емітером шостого та колектором п'ятого транзисторів, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, базу третього транзистора з'єднано з колектором першого транзистора та другим входом першого джерела струму, базу шостого транзистора з'єднано з колектором другого транзистора та першим входом другого джерела струму, колектори третього та сьомого транзистора об'єднано та з'єднано з базою дев'ятого транзистора та другим входом третього джерела струму, колектори шостого та восьмого транзистора об'єднано та з'єднано з базою десятого транзистора та першим входом четвертого джерела струму, емітер сьомого транзистора об'єднано з емітером восьмого транзистора, емітер дев'ятого транзистора з'єднано з базою одинадцятого транзистора та другим входом п'ятого джерела струму, емітер десятого транзистора з'єднано з базою шістнадцятого транзистора та першим входом шостого джерела струму, колектори дев'ятого та десятого транзисторів з'єднані з шиною нульового потенціалу, емітери дванадцятого та тринадцятого транзисторів об'єднано і з'єднано з базою сьомого транзистора, емітери чотирнадцятого та п'ятнадцятого транзисторів об'єднано і з'єднано з базою восьмого транзистора, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітер одинадцятого транзистора з'єднано з колектором та базою дванадцятого транзистора, емітер шістнадцятого транзистора з'єднано з колектором та базою п'ятнадцятого транзистора, колектор одинадцятого транзистора з'єднано з базами сімнадцятого та дев'ятнадцятого транзисторів, колектор шістнадцятого транзистора з'єднано з базами вісімнадцятого та двадцять другого транзисторів, бази сімнадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів та другим входом сьомого джерела струму, бази вісімнадцятого та двадцять другого транзисторів об'єднано та з'єднано з колектором двадцять другого та емітером двадцять першого транзисторів та першим входом восьмого джерела струму, колектори чотирнадцятого та сімнадцятого транзисторів об'єднано та з'єднано з базою двадцятого транзистора, колектори тринадцятого та вісімнадцятого транзисторів об'єднано та з'єднано з базою двадцять першого транзистора, перші входи першого, третього, п'ятого та сьомого джерел струму та емітери сімнадцятого та дев'ятнадцятого транзисторів підключено до шини додатного живлення, другі входи другого, четвертого, шостого та восьмого джерел струму та 1 UA 120004 U 5 10 15 20 25 30 35 40 45 50 55 60 емітери вісімнадцятого та двадцять другого транзисторів підключено до шини від'ємного живлення, колектори двадцятого та двадцять першого транзисторів з'єднано з вихідною шиною. Недоліком найближчого аналога є недостатньо високий коефіцієнт підсилення, що призводить до збільшення похибок при роботі схеми. В основу корисної моделі поставлено задачу створення двотактного симетричного підсилювача струму, в якому за рахунок введення нових елементів та зв'язків між ними підвищується точність роботи завдяки збільшенню коефіцієнта передачі, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у двотактний симетричний підсилювач струму, який містить шість джерел струму, шини додатного та від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять два транзистори, причому другий вхід першого та перший вхід другого джерела струму з'єднано з колектором першого та другого транзистора відповідно, бази першого та другого транзисторів з'єднано з базами та колекторами четвертого та п'ятого транзисторів відповідно, колектор четвертого транзистора з'єднано з емітером третього транзистора, база якого з'єднана з другим входом першого джерела струму, колектор п'ятого транзистора з'єднано з емітером шостого транзистора, база якого з'єднана з першим входом другого джерела струму, колектор третього транзистора з'єднано з другим входом третього джерела струму і з колектором сьомого та з базою одинадцятого транзисторів відповідно, колектор шостого транзистора з'єднано з першим входом четвертого джерела струму і з колектором десятого та з базою шістнадцятого транзисторів відповідно, емітер шістнадцятого транзистора з'єднано з колектором п'ятнадцятого транзистора, емітер одинадцятого транзистора з'єднано з колектором дванадцятого транзистора, емітери дванадцятого та чотирнадцятого транзисторів з'єднано з емітерами тринадцятого та п'ятнадцятого транзисторів відповідно, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектор тринадцятого об'єднано та з'єднано з базою двадцять першого та колектором вісімнадцятого транзисторів відповідно, колектор чотирнадцятого об'єднано та з'єднано з базою двадцятого та колектором сімнадцятого транзисторів, колектор одинадцятого транзистора з'єднано з базами сімнадцятого та дев'ятнадцятого транзисторів, колектор шістнадцятого транзистора з'єднано з базами вісімнадцятого та двадцять другого транзисторів, бази сімнадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів та другим входом п'ятого джерела струму, бази вісімнадцятого та двадцять другого транзисторів об'єднано та з'єднано з колектором двадцять другого та емітером двадцять першого транзисторів та першим входом шостого джерела струму, перші входи першого, третього та п'ятого джерел струму та емітери сімнадцятого та дев'ятнадцятого транзисторів підключено до шини додатного живлення, другі входи другого, четвертого та шостого джерел струму та емітери вісімнадцятого та двадцять другого транзисторів підключено до шини від'ємного живлення, колектори двадцять першого та двадцятого транзисторів з'єднано з вихідною шиною, згідно з корисною моделлю, введено чотири транзистори, причому бази двадцять п'ятого та двадцять шостого транзисторів з'єднано з вхідною шиною, емітер двадцять четвертого транзистора з'єднано з емітером другого транзистора, колектор якого під'єднано до шини додатного живлення, емітер першого транзистора з'єднано з емітером двадцять третього транзистора, колектор якого під'єднано до шини від'ємного живлення, бази двадцять третього та двадцять четвертого транзисторів під'єднано до шини нульового потенціалу, емітер четвертого транзистора з'єднано з емітером двадцять п'ятого транзистора, колектор якого під'єднано до шини від'ємного живлення, емітер п'ятого транзистора з'єднано з емітером двадцять шостого транзистора, колектор якого під'єднано до шини додатного живлення, емітер сьомого транзистора з'єднано з емітером восьмого транзистора, емітер дев'ятого транзистора з'єднано з емітером десятого транзистора, бази і колектори восьмого та дев'ятого транзисторів об'єднано, бази сьомого та дванадцятого транзисторів об'єднано і з'єднано з емітером одинадцятого та колектором дванадцятого транзисторів, бази десятого та п'ятнадцятого транзисторів об'єднано і з'єднано з емітером шістнадцятого та колектором п'ятнадцятого транзисторів. На кресленні представлено принципову схему двотактного симетричного підсилювача струму. Пристрій містить бази першого 2 і четвертого 10 транзисторів, які об'єднано і з'єднано з емітером третього 9 та колектором четвертого 10 транзисторів відповідно, бази другого 6 та п'ятого 13 транзисторів об'єднано та з'єднано з емітером шостого 14 та колектором шостого 14 транзисторів, базу третього 9 транзистора з'єднано з колектором першого 2 транзистора та другим входом першого 1 джерела струму, базу четвертого 6 транзистора з'єднано з 2 UA 120004 U 5 10 15 20 25 30 35 40 45 50 55 60 колектором другого 6 транзистора та першим входом другого 7 джерела струму, бази двадцять п'ятого 11 та двадцять шостого 12 транзисторів з'єднано з вхідної шиною 8, емітер двадцять четвертого 5 транзистора з'єднано з емітером другого 6 транзистора, колектор двадцять четвертого 5 транзистора під'єднано до шини додатного живлення 36, емітер першого 2 транзистора з'єднано з емітером двадцять третього 3 транзистора, колектор двадцять третього 3 транзистора під'єднано до шини від'ємного живлення 37, емітер четвертого 10 транзистора з'єднано з емітером двадцять п'ятого 11 транзистора, колектор двадцять п'ятого 11 транзистора під'єднано до шини від'ємного живлення 37, емітер двадцять шостого 12 транзистора з'єднано з емітером п'ятого 13 транзистора, колектор двадцять шостого 12 транзистора під'єднано до шини додатного живлення 36, колектори тринадцятого 9 та сьомого 16 транзисторів, об'єднано та з'єднано з базою одинадцятого 21 транзистора та другим входом третього 15 джерела струму, колектори шостого 14 та десятого 19 транзисторів об'єднано та з'єднано з базою шістнадцятого 27 транзистора та першим входом четвертого 20 джерела струму, емітер сьомого 16 транзистора з'єднано з емітером восьмого 17 транзистора, емітер дев'ятого 18 транзистора з'єднано з емітером десятого 19 транзистора, бази сьомого 17 та дев'ятого 18 транзисторів об'єднано та з'єднано з колекторами восьмого 17 та дев'ятого 18 транзисторів відповідно, бази сьомого 16 та дванадцятого 22 транзисторів об'єднано і з'єднано з емітером одинадцятого 21 та колектором дванадцятого 22 транзисторів, бази десятого 19 та п'ятнадцятого 26 транзисторів об'єднано і з'єднано з емітером чотирнадцятого 25 та колектором п'ятнадцятого 26 транзисторів, колектор одинадцятого 21 транзистора з'єднано з базами сімнадцятого 28 та дев'ятнадцятого 30 транзисторів, колектор шістнадцятого 27 транзистора з'єднано з базами вісімнадцятого 29 та двадцять другого 33 транзисторів, бази тринадцятого 23 та чотирнадцятого 25 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 24, бази сімнадцятого 28 та дев'ятнадцятого 30 транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого 30 та емітером двадцятого 31 транзисторів та другим входом п'ятого 34 джерела струму, бази вісімнадцятого 29 та двадцять другого 33 транзисторів об'єднано та з'єднано з колектором двадцять другого 33 та емітером двадцять першого 32 транзисторів та першим входом шостого 35 джерела стуму, колектори чотирнадцятого 25 та сімнадцятого 28 транзисторів об'єднано та з'єднано з базою двадцятого 31 транзистора, колектори тринадцятого 23 та вісімнадцятого 29 транзисторів об'єднано та з'єднано з базою двадцять першого 32 транзистора, перші входи першого 1, третього 15 та п'ятого 34 джерел струму та емітери сімнадцятого 28 та дев'ятнадцятого 30 транзисторів підключено до шини додатного живлення 36, другі входи другого 7, четвертого 20 та шостого 35 джерел струму та емітери вісімнадцятого 29 та двадцять другого 33 транзисторів підключено до шини від'ємного живлення 37, колектори двадцятого 31 та двадцять першого 32 транзисторів з'єднано з вихідною шиною 38. Пристрій працює таким чином. Вхідний сигнал у вигляді струму надходить на вхідну шину 8. Якщо вхідний струм втікає у схему, то двадцять шостий 12 та шостий 14 транзистори привідкриваються, а двадцять п'ятий 11 та третій 9 транзистори призакриваються, відповідно шістнадцятий 27 транзистор привідкривається, а одинадцятий 21 транзистор призакривається, відповідно вісімнадцятий 29 та двадцятий 31 привідкриваються, а сімнадцятий 28 та двадцять перший 32 призакриваються. Якщо вхідний струм витікає зі схеми, то двадцять шостий 12 та шостий 14 транзистори призакриваються, а двадцять п'ятий 11 та третій 9 транзистори привідкриваються, відповідно шістнадцятий 27 транзистор призакриваються, а одинадцятий 21 транзистор привідкриваються, відповідно вісімнадцятий 29 та двадцятий 31 призакриваються, а сімнадцятий 28 та двадцять перший 32 привідкриваються. Вхідна 8 та вихідна 38 шини утворюють вхід та вихід схеми. Шини додатного 36 та від'ємного 37 живлення, а також шина нульового потенціалу 4 задають необхідний рівень напруги для живлення схеми. Джерела струму 1 та 7 задають функціонування вхідних каскадів. Основу вхідного каскаду складає комплементарна схема із загальними колектором. Струм вихідного каскаду передається через третій 9 і шостий 14 транзистори на проміжний підсилювальний каскад. Одинадцятий 21 та шістнадцятий 27 транзистори утворюють проміжний підсилювальний каскад. Джерела струму 15 і 20 слугують для компенсації надлишкового струму, який виникає в підсилювальних каскадах. Для того, щоб забезпечити режим їх функціонування використовується двонаправлений відбивач струму, який складається з сьомого 16, восьмого 17, дев'ятого 18, десятого 19, дванадцятого 22, тринадцятого 23, чотирнадцятого 25 та п'ятнадцятого 26 транзисторів. 3 UA 120004 U 5 10 15 20 25 30 35 40 45 50 55 Вихідний каскад утворений за допомогою двох відбивачів струму, які складаються з сімнадцятого 28, дев'ятнадцятого 30 і двадцятого 31 транзисторів та п'ятого 34 джерела струму і відповідно з вісімнадцятого 29, двадцять першого 32, двадцять другого 33 транзисторів та шостого 35 джерела струму. На інверсні входи подається струм з колекторів одинадцятого 21, шістнадцятого 27 транзисторів відповідно, а на прямі входи подається струм відповідно з колекторів тринадцятого 23 та чотирнадцятого 25 транзисторів, при цьому шина нульового потенціалу 24 задає напругу на базах транзисторів тринадцятого 23 та чотирнадцятого 25. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Двотактний симетричний підсилювач струму, що містить шість джерел струму, шини додатного та від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять два транзистори, причому другий вхід першого та перший вхід другого джерела струму з'єднано з колектором першого та другого транзистора відповідно, бази першого та другого транзисторів з'єднано з базами та колекторами четвертого та п'ятого транзисторів відповідно, колектор четвертого транзистора з'єднано з емітером третього транзистора, база якого з'єднана з другим входом першого джерела струму, колектор п'ятого транзистора з'єднано з емітером шостого транзистора, база якого з'єднана з першим входом другого джерела струму, колектор третього транзистора з'єднано з другим входом третього джерела струму і з колектором сьомого та з базою одинадцятого транзисторів відповідно, колектор шостого транзистора з'єднано з першим входом четвертого джерела струму і з колектором десятого та з базою шістнадцятого транзисторів відповідно, емітер шістнадцятого транзистора з'єднано з колектором п'ятнадцятого транзистора, емітер одинадцятого транзистора з'єднано з колектором дванадцятого транзистора, емітери дванадцятого та чотирнадцятого транзисторів з'єднано з емітерами тринадцятого та п'ятнадцятого транзисторів відповідно, бази тринадцятого тачотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектор тринадцятого об'єднано та з'єднано з базою двадцять першого та колектором вісімнадцятого транзисторів відповідно, колектор чотирнадцятого об'єднано та з'єднано з базою двадцятого та колектором сімнадцятого транзисторів, колектор одинадцятого транзистора з'єднано з базами сімнадцятого та дев'ятнадцятого транзисторів, колектор шістнадцятого транзистора з'єднано з базами вісімнадцятого та двадцять другого транзисторів, бази сімнадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів та другим входом п'ятого джерела струму, бази вісімнадцятого та двадцять другого транзисторів об'єднано та з'єднано з колектором двадцять другого та емітером двадцять першого транзисторів та першим входом шостого джерела струму, перші входи першого, третього та п'ятого джерел струму та емітери сімнадцятого та дев'ятнадцятого транзисторів підключено до шини додатного живлення, другі входи другого, четвертого та шостого джерел струму та емітери вісімнадцятого та двадцять другого транзисторів підключено до шини від'ємного живлення, колектори двадцять першого та двадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що у нього введено чотири транзистори, причому бази двадцять п'ятого та двадцять шостого транзисторів з'єднано з вхідною шиною, емітер двадцять четвертого транзистора з'єднано з емітером другого транзистора, колектор якого під'єднано до шини додатного живлення, емітер першого транзистора з'єднано з емітером двадцять третього транзистора, колектор якого під'єднано до шини від'ємного живлення, бази двадцять третього та двадцять четвертого транзисторів під'єднано до шини нульового потенціалу, емітер четвертого транзистора з'єднано з емітером двадцять п'ятого транзистора, колектор якого під'єднано до шини від'ємного живлення, емітер п'ятого транзистора з'єднано з емітером двадцять шостого транзистора, колектор якого під'єднано до шини додатного живлення, емітер сьомого транзистора з'єднано з емітером восьмого транзистора, емітер дев'ятого транзистора з'єднано з емітером десятого транзистора, бази і колектори восьмого та дев'ятого транзисторів об'єднано, бази сьомого та дванадцятого транзисторів об'єднано і з'єднано з емітером одинадцятого та колектором дванадцятого транзисторів, бази десятого та п'ятнадцятого транзисторів об'єднано і з'єднано з емітером шістнадцятого та колектором п'ятнадцятого транзисторів. 4 UA 120004 U Комп’ютерна верстка О. Гергіль Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03F 3/26

Мітки: підсилювач, струму, двотактний, симетричний

Код посилання

<a href="https://ua.patents.su/7-120004-dvotaktnijj-simetrichnijj-pidsilyuvach-strumu.html" target="_blank" rel="follow" title="База патентів України">Двотактний симетричний підсилювач струму</a>

Попередній патент: Спосіб поглибленого експрес-діагностування транспортних засобів за рівнями експлуатаційної безпеки

Наступний патент: Пристрій газового аналізу

Випадковий патент: Спосіб лікування місцевопоширеного раку статевого члена