Цифровий оптоелектронний процесор багаторівневих зображень

Номер патенту: 23431

Опубліковано: 02.06.1998

Автори: Буда Антоніна Героніївна, Заболотна Наталія Іванівна, Кожем'яко Володимир Прокопович, Шолота Владислав Васильович, Мартинюк Тетяна Борисівна, Ліщинська Людмила Броніславівна

Формула / Реферат

1. Цифровой оптоэлектронный процессор многоуровневых изображений, содержащий два запоминающих устройства, устройство управления и сумматор, отличающийся тем, что он содержит логический блок, первый и второй элементы памяти картинного типа, причем запоминающие устройства и сумматор являются устройствами картинного типа, выходы первого и второго запоминающих устройств соединены оптически с первыми вторым входами логического блока, третий, четвертый и пятый, шестой входы которого соединены оптически с прямыми и инверсными выходами первого и второго элемента памяти соответственно, а первый, второй, третий и четвертый выходы оптически подключены к входу первого слагаемого и входу переноса сумматора, информационному выходу устройства и информационному входу второго элемента памяти соответственно, вход второго слагаемого сумматора оптически соединен с выходом второго запоминающего устройства, а выход суммы и выход переноса сумматора оптически подключены к входу второго запоминающего устройства и седьмому входу логическому блока соответственно, информационный вход устройства и вход матрицы знаков операндов устройства соединены оптически, с входами первого запоминающего устройства и первого элемента памяти соответственно, а выход результирующей матрицы знаков устройства подключен оптически к прямому выходу второго элемента памяти, первый и второй выходы устройства управления подключены к управляющим входам первого элемента памяти, третий и четвертый выходы - к управляющим входам логического блока, пятый и шестой выходы - к управляющим входам второго элемента памяти, седьмой и восьмой выходы - к управляющим входам первого и второго запоминающих устройств соответственно.

2. Цифровой оптоэлектронный процессор многоуровневых изображений по п.1, отличающийся тем, что логический блок содержит картинный сумматор, картинный элемент И, первый и второй картинные элементы НЕ, первый и второй картинные элементы 2И-ИЛИ, причем входы первого и второго слагаемых и вход переноса картинного сумматора соединен оптически с третьим, пятым и седьмым входами логического блока соответственно, а выходы суммы и переноса картинного сумматора соединены оптически с четвертым выходом логического блока и первым входом картинного элемента И соответственно, второй вход картинного элемента И соединен оптически с первым управляющим входом логического блока, а выход - с вторым выходом логического блока, первый вход которого через первый картинный элемент НЕ соединен оптические первым входом первого картинного элемента 2И-ИЛИ, второй, третий и четвертый входы которого соединены с третьим, первым и четвертым входами логического блока соответственно, второй вход логического блока через второй картинный элемент НЕ подключен оптически к первому входу второго картинного элемента 2И-ИЛИ, второй и четвертый входы которого соединены оптически со вторым управляющим входом логического блока, а третий, пятый и шестой входы второго картинного элемента 2И-ИЛИ соединены оптически с пятым, шестым и вторым входами логического блока соответственно, выходы первого и второго картинных элементов 2И-ИЛ И подключены оптически к первому и третьему выходам логического блока соответственно.

Текст

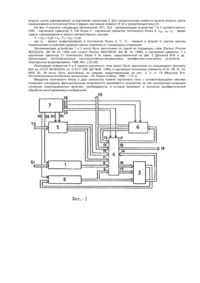

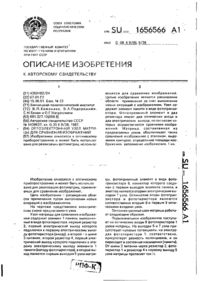

Изобретение относится к вычислительной технике и может быть использовано для параллельной арифметико-логической обработки многоуровневых изображений по пространственно-непрерывным разрядным срезам. Известен цифровой оптоэлектронный процессор для обработки изображений в пространственнонепрерывной форме [Очин Е.Ф. Принципы организации цифрового оптоэлектронного процессора для обработки изображений в пространственно-непрерывной форме. - Электронное моделирование, 1984, №3, с. 16-19], содержащий голографическое оперативное запоминающее устройство, сдви гатель, пространственнологическое устройство и накапливающий регистр, причем оптический выход голографического оперативного запоминающего устройства через сдвигатель соединен с оптическим входом пространственно-логического устройства, оптический выход которого через накапливающий регистр подключен к оптическим входам голографического оперативного запоминающего устройства и пространственно-логического устройства, кроме того управляющие входы устройства подключены соответственно к адресным входам и входам управления записью и чтением голографического оперативного запоминающего устройства, к входам управления сдвигом по координатам х, у сдвигателя и к входам управления микрооперациями пространственно-логического устройства. Недостатком известного процессора являются ограниченные функциональные возможности, поскольку пространственно-логическое устройство процессора выполняет только функционально полный набор логических операций над двухуровневыми изображениями. Известна система для многоканальной параллельной обработки изображений [Твердохлеб П.Е. Организация системы для многоканальной параллельной обработки массивов информации - Автометрия, 1981, №1, с. 19-30, рис.1], содержащая голографическое запоминающее устройство, матричный оптический преобразователь, параллельный страничный процессор и централизованное устройство управления, причем оптический выход голографического запоминающего устройства соединен с оптическим входом матричного оптического преобразователя, оптический выход которого подключен к оптическому входу параллельного страничного процессора, электронный выход которого подключен к входу централизованного устройства управления, выходы которого электрически соединены с управляющими входами голографического запоминающего устройства, матричного оптического преобразователя и параллельного страничного процессора, кроме того канал ввода-вывода устройства подключен к централизованному устройству управления. Недостатком известной системы являются низкие функциональные возможности, ограниченные выполнением трех логических операций (сложение, умножение и сложение по модулю 2). Наиболее близким по технической сущности к предлагаемому является цифровой оптоэлектронный процессор многоуровневых изображений по пространственно-непрерывным разрядным срезам [Денисов В.М. и др. Структура цифрового оптоэлектронного процессора многоуровневых изображений по пространственнонепрерывным разрядным срезам. - Электронное моделирование, 1984, №6, с.99-101, рис.1], содержащий лазер, два запоминающих устройства, устройство управления, два модулятора, четыре дефлектора и операционный автомат, содержащий два дефлектора, сумматор и аналого-цифровой преобразователь, причем лазер оптически через первый модулятор соединен через первый и второй дефлекторы с входами первого и второго запоминающих устройств соответственно, а через второй модулятор – с аналогоцифровым преобразователем, первый и второй выходы которого соединены оптически через третий и четвертый дефлекторы с входами первого и второго запоминающих устройств, выходы которых оптически соединены через пятый и шестой дефлекторы соответственно с входами сумматора, выход которого оптически подключен к входу аналого-цифрового преобразователя, первый, второй, третий и пятый выходы устройства управления электрически подключены к управляющим входам двух модуляторов, первого и второго дефлекторов, пятого и шестого дефлекторов, третьего и четвертого дефлекторов и аналогоцифрового преобразователя соответственно. Недостатком известного процессора является выполнение операции суммирования без учета знака, что сужает его функциональные возможности. В основу изобретения поставлена задача усовершенствования цифрового оптоэлектронного процессора многоуровневых изображений, в котором учет знака при выполнении сложения числовых данныхобеспечивает расширение функциональных возможностей устройства за счет сложения знакопеременных числовых данных. Поставленная задача решается тем, что в цифровой оптоэлектронный процессор многоуровневых преображений, содержащий два запоминающих устройства, устройство управления и сумматор, введены логический блок, первый и второй элементы памяти картинного типа, причем запоминающие устройства и сумматор являются устройствами картинного типа, выходы первого и второго запоминающих устройств оптически соединены с первым и вторым входами логического блока, третий, четвертый и пятый, шестой входы которого оптически соединены с прямыми и инверсными выходами первого и второго элементов памяти соответственно, а первый, второй, третий и четвертый выходы оптически подключены к входу первого слагаемого и входу переноса сумматора, информационному выходу устройства и информационному входу второго элемента памяти соответственно, вход второго слагаемого сумматора оптически соединен с выходом второго запоминающего устройства, а вы ход суммы и выход переноса сумматора оптически подключен к входу второго запоминающего устройства и седьмому входу логического блока соответственно, информационный вход и вход матрицы знаков операндов устройства соединены оптически с входами первого запоминающего устройства и первого элемента памяти соответственно, а выход результирующей матрицы знаков устройства подключен оптически к прямому вы ходу второго элемента памяти, первый и второй выходы устройства управления подключены к управляющим входам первого элемента памяти, третий и четвертый выходы - к управляющим входам логического блока, пятый и шестой выходы - к управляющим входам второго элемента памяти, седьмой и восьмой выходы - к управляющим входам первого и второго запоминающих устройств соответственно. Кроме того, логический блок содержит картинный сумматор, картинный элемент И, первый и второй картинные элементы НЕ, первый и второй картинные элементы 2И-ИЛИ, причем входы первого и второго слагаемых и вход переноса картинного сумматора соединены оптически с третьим, пятым и седьмым входами логического блока соответственно, а выходы суммы и переноса картинного сумматора соединены оптически с четвертым выходом логического блока и первым входом картинного элемента И соответственно, второй вход картинного элемента И соединен оптически с первым управляющим входом логического блока, а выход - с вторым выходом логического блока, первый вход которого через первый картинный элемент НЕ соединен оптически с первым входом первого картинного элемента 2И-ИЛИ, второй, третий и четвертый входы которого соединены оптически с третьим, первым и четвертым входами логического блока соответственно, второй вход логического блока через второй картинный элемент НЕ подключен оптически к первому входу второго картинного элемента 2И-ИЛИ, второй и четвертый входы которого соединены оптически со вторым управляющим входом логического блока, а третий, пятый и шестой входы второго картинного элемента 2И-ИЛИ соединены оптически с пятым, шестым и вторым входами логического блока соответственно, выходы первого и второго картинных элементов 2И-ИЛИ подключены оптически к первому и третьему выходам логического блока соответственно. За счет того, что в цифровом оптоэлектронном процессоре многоуровневых изображений используются логический блок и два элемента памяти картинного типа с соответствующими связями, возможно сложение знакопеременных числовых данных, что расширяет функциональные возможности устройства. На фиг.1 представлена структурная схема цифрового оптоэлектронного процессора; на фиг.2 функциональная схема логического блока сумматора и двух элементов памяти; на фиг.3 - примеры выполнения операции сложения двух знакопеременных операндов с использованием обратного кода отрицательного операнда, на фиг.4 - временные диаграммы работы процессора. Цифровой оптоэлектронный процессор (фиг.1) содержит два запоминающих устройства 1, 2, сумматор 3, логический блок 4, элементы 5 и 6 памяти и устройство 7 управления. Выводы запоминающих устройств 1 и 2 соединены оптически с входами 8 и 9 логического блока 4 соответственно, входы 10, 11 которого подключены оптически к прямому и инверсному выходам элемента 5 памяти соответственно, входы 12,13 - к прямому и инверсному выходам элемента 6 памяти соответственно, вход 14 - к выходу переноса сумматора 3, выход суммы которого оптически соединен с входом запоминающего устройства 2, вы ход которого также соединен оптически с входом второго слагаемого сумматора 3. Выходы 15, 16 блока 4 соединены оптически с входами первого слагаемого и переноса сумматора 3 соответственно, выход 17 - с информационным входом элемента 6 памяти, а выход 18 - с информационным выходом 19 устройства, вы ход 20 знака результата которого соединен оптически с прямым выходом матрицы 6. Информационный вход 21 устройства подключен оптически к входу запоминающего устройства 1, а вход 22 знака операндов - к информационному входу элемента 5 памяти. Выходы 23, 24 устройства 7 управления подключены к входам синхронизации и обнуления элемента 5 памяти соответственно, выходы 25, 26 - к входам управления переносом и чтения логического блока 4 соответственно, выходы 27, 28 - к входам синхронизации и обнуления элемента 6 памяти соответственно, выходы 29, 30 - к входам управления сдвигом (разрешения чтения запоминающих устройств 1 и 2 соответственно. Логический блок 4 преобразования кода (фиг.2) содержит картинный сумматор 31, картинный элемент И 32, картинные элементы НЕ 33, 34, картинные элементы 2И-ИЛИ 35, 36, причем входы первого и второго слагаемых и вход переноса сумматора 32 соединены оптически с входами 10, 12 и 14 блока 4 соответственно, а вы ходы суммы и переноса - с выходом 17 блока 4 и первым входом элемента И 32 соответственно, второй вход элемента И 32 соединен оптически с выходом 25 устройства 7 управления, а выход - с выходом 16 блока 4. Вход 8 блока 4 через элемент НЕ 33 соединен оптически с первым входом элемента 2И-ИЛИ 35, второй, третий и четвертый входы которого соединены оптически с входами 10, 8, 11 блока 4 соответственно, вход 9 которого через элемент НЕ 34 подключен оптически к первому входу элемента 2И-ИЛИ 36, второй и четвертый входы которого соединены оптически с выходом 26 устройства 7 управления, а третий, пятый и шестой входы - с входами 12, 13, 9 блока 4 соответственно. Выходы элементов 2И-ИЛИ 35, 36 подключены оптически к выходам 15 и 18 блока 4 соответственно. Элемент 5 памяти (фиг 2) содержит картинный D-триггер 37, информационный вход которого соединен оптически с информационным входом 22 устройства, входы синхронизации и обнуления - с выходами 23, 24 устройства 7 управления соответственно, а прямой и инверсный выходы - с входами 10 и 11 логического блока 4 соответственно. Элемент 6 памяти (фиг 2) содержит картинный D-триггер 38, информационный вход которого соединен оптически с информационным выходом 17 логического блока 4, входы синхронизации и обнуления - с выходами 27, 28 устройства 7 управления соответственно, а прямой и инверсный выходы - с входом 12 логического блока 4, выходом 20 устройства и входом 13 логического блока 4 соответственно. Сумматор 3 (фиг.2) содержит картинный сумматор 39, картинный узел переноса 40 и картинный элемент ИЛИ 41, причем входы первого и второго слагаемых сумматора 39 соединены оптически с выходом 15 логического блока 4 и выходом запоминающего устройства 2 соответственно, а выходы суммы и переноса - с входом запоминающего устройства 2 и входом 14 логического блока 4 соответственно. Выход переноса сумматора 39 через узел переноса 40 соединен также оптически с первым входом элемента ИЛИ 41, второй вход которого подключен оптически к выходу 16 логического блока 4, а выход - к входу переноса сумматора 39. Цифровой оптоэлектронный процессор работает следующим образом. Запись исходной информации в виде страниц размерностью NxM изображений, представленных 2к уровнями, осуществляется в запоминающее устройство 1 в виде (к-1) наборов двухуровневых оптических картин размерностью NxM. Таким образом,в дальнейшем 2 уровневые изображения размерностью NxM обрабатываются как массив NxM (к-1)-разрядных операндов последовательно по разрядным срезам, начиная с младших н улевых разрядов. Первоначальное состояние аналогично запоминающего устройства 2 - все ее ячейки обнулены. Параллельно с записью информации в запоминающее устройство 1 осуществляется запись к-й двухуровневой оптической картины размерностью NxM, соответствующей знаковой матрице массива NxM (k-1)- разрядных операндов, в элемент 5 памяти картинного типа, элемент 6 памяти картинного типа в первоначальном состоянии обнулен. Затем осуществляется чтение информации, соответствующей срезу младших нулевы х разрядов (k-1)-разрядных чисел из запоминающих устройств 1 и 2. При этом чтение из запоминающего устройства 2 выполняется с задержкой, равной времени прохождения информации из запоминающего устройства через логический блок 4. В логическом блоке 4 происходит преобразование поступающей информации в соответствии со знаковой матрицей исходныхданных, хранящейся в элементе 5 памяти картинного типа. Так при наличии "0" в i-й ячейке NxM-разрядного элемента 5 памяти информация в і-й ячейке NxMразрядного h-го среза (страницы) из запоминающего устройства 1, где h = 0 , 1, 2,...,k-1, без изменений поступает на вход первого слагаемого картинного сумматора 3. В случае присутствия "1" в i-й ячейке NxMразрядного элемента 5 памяти информация в i-й ячейке NxM-разрядного h-го среза инвертируется в логическом блоке 4 и также поступает на вход первого слагаемого картинного сумматора 3. В картинном сумматоре 3 осуществляется суммирование информации, поступающей на его входы первого и второго слагаемых по NxM-разрядным h-м срезам с учетом сигнала переноса, сформированного в предыдущих (h-1)-x срезах. Сформированный в картинном сумматоре 3 NxM-разрядный h-й срез суммы поступает на вход запоминающего устройства 2. Поскольку чтение информации из NxM (k-1)-разрядных стековых запоминающих устройств, составляющи х запоминающие устройства 1,2, осуществляется в результате сдвига информации, то запись информации с выхода суммы картинного сумматора 3 выполняется в освободившийся старший разряд всех NxM стековых запоминающих устройств запоминающего устройства 2. Затем вновь осуществляется сдвиг информации в обоих запоминающих устройства х 1 и 2 и дальнейшая ее обработка логическим блоком 4 и картинным сумматором 3 до тех пор, пока не будет выполнено суммирование NxM разрядного (к-1)-го среза, т.е. старших информационных разрядов (к-1)-разрядных операндов. При этом сформированный картинным сумматором 3 (к-1)-й срез сигналов переноса поступает на вход логического блока 4, где участвует в формировании NxM-разрядной матрицы знаков результатов, которая фиксируется в элементе 6 памяти картинного типа Здесь рассмотрен случай, когда информация в запоминающем устройстве 2 равна н улю. Поскольку при сдвиге информации в запоминающем устройстве 1 возможна последовательная запись по NxM-разрядным hм срезам, то к моменту окончания записи в запоминающее устройство 2 (k-1)-го среза суммы исходных операндов без учета единиц переполнения в (к-1)-м срезе старших разрядов операндов в запоминающем устройстве 1 может быть записан следующий массив NxM (к-1)-разрядных операндов, соответствующий 2к уровневому изображению размерностью NxM, а в элементе 5 памяти соответствующая матрица знаков операндов. Примеры сложения операндов разрядностью k=4, находящихся в 1-х стековых запоминающих устройствах соответственно, где i=1,2,..., N xM, запоминающих устройств 1 и 2, с учетом их знаков приведены на фиг. 3. Суммирование одноименных разрядных срезов, поступающих из запоминающих устройств 1 и 2, выполняется аналогично рассмотренному ранее случаю с той лишь разницей, что в случаях 1, 4, 5 (фиг.3) необходим дополнительный цикл сложения на картинном сумматоре 3 полученных (к-1)-разрядных NxM исходных операндов с к-м срезом возможных единиц переполнения. В этом цикле суммирования не выполняется сдвиг информации в запоминающем устройстве 1, а в конце цикла формируется знаковая матрица логическим блоком 4 и фиксируется в элементе 6 памяти. Дополнительный цикл суммирования с единицей переполнения можно совместить с циклом сложения промежуточного результата со следующим операндом, если он находится в запоминающем устройстве 1. В этом случае выполняется сдвиг информации в запоминающем устройстве 1. Результат сложения всегда фиксируется в запоминающем устройстве 2. В случае необходимости считывания результата сложения осуществляется последовательный сдвиг по разрядным срезам информации в запоминающем устройстве 2 и преобразование ее в логическом блоке 4 с учетом матрицы знаков результатов по каждой из (k-1) сумм. Результирующая информация поступает на выход 19 устройства. Весь процесс сложения и чтения результирующей информации представлен временными диаграммами работы устройства (фиг.4). Логический блок 4 (фиг.2) работает следующим образом. В процессе суммирования при сдвиге в запоминающем устройстве 1 информация в виде разрядного среза размерностью NxM поступает на вход 8 логического блока 4 и с учетом знаковой матрицы, поступающей с элемента 5 памяти на входы 10 и 11 логического блока 4, проходит либо через картинные элементы НЕ 33 и 2И-ИЛИ 35 (в обратном коде) на выход 15 логического блока 4, либо только через картинный элемент 2И-ИЛИ 35 (в прямом коде) на выход 15 логического блока 4. При считывании результата сложения, когда сдвигается информация в запоминающем устройстве 2, она в виде разрядного среза размерностью NxM поступает на вход 9 логического блока 4 и с учетом знаковой матрицы, поступающей с элемента 6 памяти на входы 12 и 13 логического блока 4 и при наличии управляющего сигнала на входе 26 логического блока 4, проходит либо через картинные элементы НЕ 34 и 2И-ИЛИ 36 (в обратном коде) на выход 18 логического блока 4, либо только через картинный элемент 2И-ИЛИ 36 (в прямом коде) на выход 18 логического блока 4. При формировании знаковой матрицы результата, на входы первых и вторых слагаемых и переноса картинного сумматора 31 поступают знаковые матрицы в прямом коде как с элемента 5 памяти на вход 10 логического блока 4, так и с элемента 6 памяти на вход 12 логического блока 4, а также (к-1)-й срез единиц переполнения картинного сумматора 39 на вход 14 логического блока 4. Матрица знаков результата с выхода суммы картинного сумматора 31 через выход 17 логического блока 4 фиксируется в элементе 6 памяти картинного типа. Из примеров сложения двух 4-х разрядных операторов на фиг. 3 видно, что в случаях 1, 4, 5 именно в знаковом разряде формируется Единица переполнения, которая вызывает необходимость выполнения второго цикла суммирования на картинном сумматоре 3. Для синхронизации момента начала второго цикла суммирования в логический блок 4 введен картинный элемент И 32 и управляющий вход 25. На фиг. 4 приняты следующие обозначения: ЗУ1, ЗУ2 - запоминающие устройства 1 и 2 соответственно; СМ3 - картинный сумматор 3; СМ блока 4 - картинный сумматор логического блока 4; tсад, tсм , tзп - время сдвига, суммирования и записи соответственно, причем Т1 = (tсм + tзп)k + t ин , Т 2 = (tсм + tзп)k, где tин - время инвертирования в логическом блоке 4; Т1, Т2 - первый и второй (с учетом единиц переполнения в знаковом разряде) циклы сложения (к-1)-разрядных операндов. Запоминающие устройства 1 и 2 могут быть выполнены по одной из следующи х схем [Патент России №2022334, БИ № 20, 1994 или патент России №2018916, БИ № 16, 1994], а картинный сумматор 3 и картинный сумматор 31 логического блока 4 по схеме, представленной на фиг. 2 [Денисов В.М. и др. Организация оптоэлектронных пространственно-непрерывных арифметико-логических устройств. Электронное моделирование, 1986, №2, с.25-28]. Реализация элементов 5 и 6 памяти картинного типа может быть выполнена по следующему принципу [Авт.св. СССР №1603334, кл. G 02 F 3/00, БИ №40, 1990], а картинные логические элементы И 32, НЕ 33, 34, ИЛИ 35, 36 могут быть выполнены по схемам, представленным на рис. 2, 3, 4, 10 [Морозов В.Н. Оптоэлектронные матричные процессоры. - М.: Радио и связь, 1986. - 112 с]. Введение логического блока и двух элементов памяти картинного типа с соответствующими связями позволяют расширить функциональные возможности заявляемого устройства за счет выполнения операции сложения знакопеременных величин, необходимость в которой возникает в процессе арифметической обработки многоуровневых изображений.

ДивитисяДодаткова інформація

Автори англійськоюKozhemyako Volodymyr Prokopovych, Martyniuk Tetiana Borysivna, Lischynska Liudmyla Bronislavivna, Buda Antonina Heroniivna

Автори російськоюКожемяко Владимир Прокофьевич, Мартынюк Татьяна Борисовна, Лищинская Людмила Брониславовна, Буда Антонина Героньевна

МПК / Мітки

Мітки: процесор, цифровий, зображень, багаторівневих, оптоелектронний

Код посилання

<a href="https://ua.patents.su/7-23431-cifrovijj-optoelektronnijj-procesor-bagatorivnevikh-zobrazhen.html" target="_blank" rel="follow" title="База патентів України">Цифровий оптоелектронний процесор багаторівневих зображень</a>

Попередній патент: Пристрій для електрохімічної обробки

Наступний патент: Спосіб тривимірної сейсморозвідки

Випадковий патент: Сходинка для купе пасажирського вагона