Цифровий автокорелятор

Номер патенту: 76622

Опубліковано: 10.01.2013

Автори: Албанський Іван Богданович, Николайчук Ярослав Миколайович, Волинський Орест Ігорович

Формула / Реферат

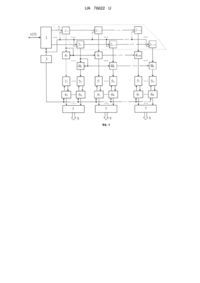

Цифровий автокорелятор, який містить М блоків множення, виходи яких з'єднані з входами відповідних суматорів, аналого-цифровий перетворювач, інформаційних вхід якого є входом автокорелятора, а вихід з'єднаний з інформаційним входом блока пам'яті, керуючі входи аналого-цифрового перетворювача та блока пам'яті об'єднані і підключені до першого виходу генератора імпульсів, який відрізняється тим, що другий додатково введений вихід генератора імпульсів з'єднаний з входами стирання регістрів пам'яті накопичувальних суматорів і синхронізуючим виходом зчитування автокорелятора, додатково на виході аналого-цифрового перетворювача формуються паралельні коди базису Хаара у вигляді кодів залишків системи залишкових класів по взаємно простих модулях р1, р2, …, рk, які надходять на відповідні входи блоку пам'яті, виходи якого по кожному pi модулю перемножують у додатково введених вентильних матрицях по кожному модулю рі у кожному каналі автокорелятора з відповідними текучими кодами Хаара-Крестенсона, які формуються на виходах аналого-цифрового перетворювача, вихідні коди вентильних матриць перемноження по модулю рi підсумовують у додатково ведених вентильних матрицях накопичувальних суматорів з кодами, які накопичують у відповідних регістрах пам'яті кожного каналу, виходи яких у кожному каналі підключені до додатково введених дешифраторів, виходи яких є виходами автокорелятора.

Текст

Реферат: Цифровий автокорелятор, в якому другий вихід генератора імпульсів з'єднаний з входами стирання регістрів пам'яті накопичувальних суматорів і синхронізуючим виходом зчитування автокорелятора, додатково на виході аналого-цифрового перетворювача формують паралельні коди базису Хаара у вигляді кодів залишків системи залишкових класів по взаємно простих модулях р1, р2, …, рk, які надходять на відповідні входи блоку пам'яті, виходи якого по кожному pi модулю перемножуються у додатково введених вентильних матрицях по кожному модулю р і у кожному каналі автокорелятора з відповідними текучими кодами Хаара-Крестенсона, які формують на виходах аналого-цифрового перетворювача, вихідні коди вентильних матриць перемноження по модулю рi підсумовують у додатково ведених вентильних матрицях накопичувальних суматорів з кодами, які накопичують у відповідних регістрах пам'яті кожного каналу, виходи яких у кожному каналі підключені до додатково введених дешифраторів, виходи яких є виходами автокорелятора. UA 76622 U (12) UA 76622 U UA 76622 U Корисна модель належить до галузі обчислювальної техніки і призначена для статистичного аналізу випадкових процесів шляхом обчислення коваріаційної функції, згідно алгоритму 1 N 1 x1 x i j , де N - об'єм вибірки, Хi, Xi-j, відповідно текучі та затримані на j тактів у N i0 пам'яті цифрові відліки вхідних аналогових сигналів на виході аналого-цифрового перетворювача, j=1,2,3/…М, де М число обчислювальних значень автоковаріаційної функції. Відомий аналог - багатоканальний цифровий корелятор - призначений для обчислення автокореляційної функції на основі дискретів центрованих процесів, який містить синхронізатор, багатокаскадний регістр зсуву, накопичувачі, часоімпульсний перетворювач аналог-код [А.С. СССР № 337784, кл. G06F15/34. - Бюллетень № 15,-1972]. Недоліком даного пристрою є низька швидкодія обумовлена тим, що пристрій містить часоімпульсний перетворювач "аналог-код", а операція накопичення суми добутків текучих та зміщених кодів виконується шляхом унітарного сумування кодів, які зсуваються у багатокаскадному регістрі зсуву. Відомий прототип - цифровий автокорелятор, який містить М блоків множення, виходи яких з'єднані з входами відповідних суматорів, аналого-цифровий перетворювач, інформаційний вхід якого є входом автокорелятора, а вихід з'єднаний з інформаційним входом блока пам'яті, керуючі входи аналого-цифрового перетворювача (АЦП) і блока пам'яті об'єднані і підключені до виходу генератора імпульсів [Л.С. СССР № 968819 кл. G06F15/336. - Бюллетень № 39.1982]. Недоліком цифрового автокорелятора низька швидкодія обумовлена тим, що АЦП формує паралельні К - розрядні коди двійкової системи числення теоретико-числового базису Радемахера, при цьому у матричному перемножувачі двійкових чисел за схемою Брауна [Цилькер Б.Я., Орлов С.А. Организация ЭВМ и систем: /учебник для вузов/. - ПИТЕР. - 2004. - С. 353.], який формується на базі КК матриці тривходових суматорів, виникає 3К переносів, причому кожен тривходовий суматор формується не менше ніж з трьох послідовно включених логічних елементів [Майоров С.А. Принципы организации цифровых машин/ С.А. Майоров, Г.И. Новиков -Л.: Машиностроение, 1974. - с. 144, рис. 4.36] плюс один такі переключення логічних елементів "І" на входах суматорів, тобто, загальний час спрацювання К - розрядного матричного перемножувача двійкових чисел визначається згідно виразу 3K 1 . K xx ( j) 5 10 15 20 25 30 35 40 45 Наприклад: - при розрядності АЦП К=4 час спрацювання матричного перемножувача буде рівний 4 9 1 37 тактів, де - час спрацювання мікроелектронного вентиля; - при розрядності АЦП К=8 відповідно 8 9 1 73 . Крім того отримані 2К - розрядні двійкові коди на виході перемножувача сумують в двійкових 2K log N - розрядних накопичувальних суматорах, в яких також виникають наскрізні переноси. При цьому час спрацювання накопичувальних суматорів з врахуванням регістра пам'яті на D-тригерах в їх структурі, розраховується згідно виразу (2K log 2 N) 3 , тобто при К=4 і К=8 і об'ємі вибірки N=256 час спрацювання накопичувального суматора буде рівний відповідно (24+8)3+1=49 та (28+8)3+1=43. Отже, сумарний час виконання операції перемноження та сумування двійкових кодів у відомому кореляторі з врахуванням спрацювання D-тригерів регістра зсуву пам'яті при К=4 та К=8 буде рівний відповідно: 37 49 1 87 та 73 73 1 147 . З урахуванням тривалості спрацювання АЦП відповідно: ав токор АЦП (2 4 8) 3 1 49 , ав токор АЦП (2 8 8) 3 1 73 , де АЦП комп. ЛЕ 10 1 . Тобто при К=4 і К=8: 50 ав токор 11 87 98 , ав токор 11 147 158 . В основу корисної моделі поставлена задача вдосконалення цифрового автокорелятора шляхом підвищення швидкодії та розширення функціональних можливостей, який містить М блоків множення, виходи яких з'єднані з входами відповідних суматорів, аналого-цифровий перетворювач, інформаційних вхід якого с входом автокорелятора, а вихід з'єднаний з інформаційним входом блока пам'яті, керуючі входи аналого-цифрового перетворювача і блока пам'яті об'єднані і підключені до першого виходу генератора імпульсів, другий додатково 1 UA 76622 U 5 10 15 20 введений вихід генератора імпульсів з'єднаний з входами стирання регістрів пам'яті накопичувальних суматорів і синхронізуючим виходом зчитування авто корелятора, додатково на виході аналого-цифрового перетворювача формуються паралельні коди базису Хаара у вигляді кодів залишків системи залишкових класів по взаємно простих модулях p1, p2,…, рk, які поступають на відповідні входи блоку пам'яті, виходи якого по кожному р і модулю перемножуються згідно корисної моделі у додатково введених вентильних матрицях по кожному модулю рі у кожному каналі автокорелятора з відповідними текучими кодами ХаараКрестенсона, які формуються на виходах аналого-цифрового перетворювача, вихідні коди вентильних матриць перемноження по модулю рі сумуються у додатково ведених вентильних матрицях накопичувальних суматорів з кодами, які накопичуються у відповідних регістрах пам'яті кожного каналу, виходи яких у кожному каналі підключені до додатково введених дешифраторів, виходи яких є виходами автокорелятора. Поставлена задача вирішується тим, що кодування та цифрове опрацювання цифрових значень вхідних сигналів у теоретико-числовому базисі (ТЧБ) Хаара-Крестенсона. Тобто в АЦП паралельного типу відсутній шифратор, який перетворює код на виході логічних елементів "Виключне АБО" у двійковий код базису Радемахера. При цьому у матричному шифраторі Хаара-Крестенсона відбувається формування паралельних кодів Хаара залишків по взаємно простих модулів системи залишкових класів базису Крестенсона. Такий принцип кодування інформації в автокореляторі дозволяє виконувати модульні операції множення і сумування за один такт у вентильних матрицях. Таким чином запропоноване рішення забезпечує наступну оцінку швидкодії автокорелятора згідно виразу: ав токор. АЦП КМ М Р Т Н , де АЦП К ЛЕ ; 25 30 35 40 45 50 55 К =10 - тривалість переключення компаратора; ЛЕ =1 - тривалість переключення логічного елемента; КМ =1 - тривалість переключення кодової матриці; М =1 - тривалість переключення D-тригера пам'яті корелятора; Р =2 - тривалість переключення вентильної матриці перемноження по модулю Pі; =2 - тривалість переключення вентильної матриці сумування по модулю Pі; Т =1 - тривалість переключення D-тригера регістра пам'яті накопичувального суматора; Н =2 - тривалість переключення вентильної матриці шифратора. Таким чином сумарний час переключення автокорелятора згідно корисної моделі буде рівний ав токор =20, тобто у 5-7 разів перевищує швидкодію прототипу. Корисна модель ілюструється кресленнями (Фіг. 1), де показано структурну схему автокорелятора, на Фіг. 2 представлена структура аналого-цифрового перетворювача з матричним шифратором для формування вихідних кодів Хаара-Крестенсона, Фіг. 3 ілюструє структуру вентильної матриці перемноження по модулю 11, Фіг. 4 ілюструє приклад вентильної матриці сумування по модулю 11. Цифровий автокорелятор включає в себе: 1 - АЦП паралельного типу з вихідним кодом базису Хаара, 2 - блок пам'яті, 3 - генератор імпульсів, 4 - вентильні матриці перемноження по модулю, 5 - вентильні матриці сумування по модулю, 6 - регістр пам'яті, 7 - шифратор. Автокорелятор працює наступним чином. На початку циклів визначення значень автоковаріаційної функції на другому виході генератора імпульсів 3 формується імпульс, який скидає в нуль D-тригери регістрів пам'яті. Кожен N циклів, де N - об'єм вибірки, сигналами першого виходу генератора імпульсів 3 тактується робота АЦП 1 і виконуються зсуви інформації в пам'яті автокорелятора 2, при цьому в кожному циклі виконується перемноження текучих та зсунутих кодів Хаара по модулю P і у всіх М каналах автокорелятора, які підсумовуються по модулю Pі в матричних суматорах 5 і накопичуються в регістрах пам'яті 6. В кінці N циклів роботи автокорелятора на виході шифраторів 7 формуються двійкові коди базису Радемахера обчислених значень коваріаційної функції Кхх(j), зчитування яких синхронізується імпульсами генератора імпульсів 3 і відбувається стирання інформації, накопиченої в попередньому циклі в регістрах пам'яті 6. Приклади розрахунку параметрів автокорелятора при різній розрядності АЦП К, числа каналів автокорелятора М і об'ємі вибірки N: Приклад 1 2 UA 76622 U Вихідні дані автокорелятора К=4, М=16, N=256. Шукаємо набір взаємно простих модулів (Р1, Р2,…, Рk) добуток яких найменше перевищує суму добутків максимальних значень x i xi j , 5 10 15 20 25 30 k 256 i 1 тобто i 1 Pi x i max x i j max . Для нашого прикладу x i max 2 4 1 15 , отже 256 15 2 57600 . i 1 Вибираємо набір наступних взаємно простих модулів: р1=11, р2=13, р3=15, р4=31. Їх добуток рівний Р=11131531=66495, що задовольняє діапазон кодування чисел в системі залишкових класів. Структура аналого-цифрового перетворювача для формування вихідних кодів ХаараКрестенсона для обраного набору модулів мас вигляд показаний на Фіг. 2. На Фіг. 3 показана структура вентильної матриці перемноження по модулю 11, де точка перетину двох шин відповідає двоходовому логічному елементу "І-НЕ". На Фіг. 4 показаний приклад вентильної матриці сумування по модулю 11. Приклад 2 Вихідні дані автокорелятора К=8, М=16, N=256. Діапазон кодування чисел в кожному каналі 2 2 автокорелятора 255 256 =16646400. Вибраний набір модулів: р1=25, р2=27, р3=28, р4=29, р5=31. Їх добуток рівний Р=2527282931=16991100, що задовольняє умову однозначного кодування результатів обчислень у автокореляторі в системі залишкових класів базису Крестенсона. В шифраторах автокорелятора 7 виконується перетворення кодів залишків базису Хаара у двійкові коди базису Радемахера та перетворення їх з системи залишкових класів у двійкову систему з відкиданням 8-ми молодших розрядів як операції ділення на N згідно формули обчислення коваріаційної функції. Таким чином, наприклад, при тактовій частоті спрацювання мікроелектронних вентилів 100 МГц тактова частота виконання операції додавання та множення, у відомому кореляторі буде приблизно у 100 разів нижчою, що підтверджує низьку швидкодію відомого корелятора, який працює у двійковій системі числення базису Радемахера. За рахунок обчислення коваріаційної функції на основі представлення цифрових відліків х і та хi-j, базису Хаара-Крестенсона системи залишкових класів реалізуються однотактні перемноження та сумування кодів залишків у вентильних матрицях перемноження та сумування, що забезпечує максимально високу швидкодію автокорелятора згідно корисної моделі. Швидкодія автокорелятора згідно корисної моделі не залежить від розрядності АЦП - К, об'єму вибірки - N та числа каналів автокорелятора - М. Матриці модульного перемножувача та суматора реалізуються на основі типових програмовано-логічних матриць (ПЛМ). ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 50 Цифровий автокорелятор, який містить М блоків множення, виходи яких з'єднані з входами відповідних суматорів, аналого-цифровий перетворювач, інформаційних вхід якого є входом автокорелятора, а вихід з'єднаний з інформаційним входом блока пам'яті, керуючі входи аналого-цифрового перетворювача та блока пам'яті об'єднані і підключені до першого виходу генератора імпульсів, який відрізняється тим, що другий додатково введений вихід генератора імпульсів з'єднаний з входами стирання регістрів пам'яті накопичувальних суматорів і синхронізуючим виходом зчитування автокорелятора, додатково на виході аналого-цифрового перетворювача формуються паралельні коди базису Хаара у вигляді кодів залишків системи залишкових класів по взаємно простих модулях р1, р2, …, рk, які надходять на відповідні входи блоку пам'яті, виходи якого по кожному pi модулю перемножують у додатково введених вентильних матрицях по кожному модулю рі у кожному каналі автокорелятора з відповідними текучими кодами Хаара-Крестенсона, які формуються на виходах аналого-цифрового перетворювача, вихідні коди вентильних матриць перемноження по модулю р i підсумовують у додатково ведених вентильних матрицях накопичувальних суматорів з кодами, які накопичують у відповідних регістрах пам'яті кожного каналу, виходи яких у кожному каналі підключені до додатково введених дешифраторів, виходи яких є виходами автокорелятора. 3 UA 76622 U 4 UA 76622 U Комп’ютерна верстка В. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital autocorrelator

Автори англійськоюAlbanskyi Ivan Bohdanovych, Nykolaichuk Yaroslav Mykolaiovych, Volynskyi Orest Ihorovych

Назва патенту російськоюЦифровой автокоррелятор

Автори російськоюАлбанский Иван Богданович, Николайчук Ярослав Николаевич, Волынский Орест Игоревич

МПК / Мітки

МПК: G06F 17/15

Мітки: автокорелятор, цифровий

Код посилання

<a href="https://ua.patents.su/7-76622-cifrovijj-avtokorelyator.html" target="_blank" rel="follow" title="База патентів України">Цифровий автокорелятор</a>

Попередній патент: Лампа на основі світлодіодного модуля acrich2 комбінована

Наступний патент: Пристрій для перетворення чисел з позиційної системи в систему залишкових класів

Випадковий патент: Магнітний підшипник мпа-3