Лічильник імпульсів

Номер патенту: 89153

Опубліковано: 10.04.2014

Автори: Борисенко Олексій Андрійович, Маценко Світлана Михайлівна

Формула / Реферат

Лічильник імпульсів, що містить n - розрядний регістр, кожен розряд якого містить тригер та елемент І, блок аналізу, що містить n-1 елементів І, блок диспозицій, що містить n-1 елементів І з інверторами на входах, блок контролю, що містить n-1 елементів I, об'єднаних елементом АБО, блок установки в нуль, що містить n-1 елементів АБО та елемент І, до першого входу якого приєднана шина тактових імпульсів, виходи n-1 елементів I блока аналізу з'єднані з першими входами n-1 елементів І регістра, другі входи яких та перший вхід елемента І блока установки в нуль з'єднані з вхідною шиною тактовий імпульсів, прямі виходи n-1 тригерів з'єднані з третіми входами елементів І регістра, четверті входи яких з'єднані з виходами n-2 елементів І блока диспозицій, вихід n-1-го елемента І блока диспозицій з'єднаний з третім входом елемента І блока установки в нyль, виходи елементів І регістра з'єднані з входами установки тригерів в одиничний стан, інверсні виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока аналізу, прямі виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока контролю, прямий вихід n-го тригера з'єднаний з другим входом елемента І блока установки в нyль, виходи елементів І блока контролю з'єднані з входом елемента АБО, який відрізняється тим, що в елементи І блока диспозицій з другого по n-1 введені додаткові kn-входи з інверторами, при цьому в другий та третій елементи І введено kn-1+2 входів з інверторами, а в n-1 елемент I введено kn-1+1 входів з інверторами, перший вхід першого елемента I з'єднаний з першими входами другого, третього та n-1-го елементів I блока диспозицій та з виходом першого елемента І блока аналізу, другий вхід першого елемента І блока диспозицій з'єднаний з другими входами другого, третього та n-1-го елементів І блока диспозицій та з виходом другого елемента І блока аналізу, третій вхід другого елемента І блока диспозицій з'єднаний з третіми входами третього та n-1-го елементів І блока диспозицій та з виходом другогоелемента І блока аналізу, четвертий вхід другого елемента І блока диспозицій з'єднаний з четвертими входами третього та n-1-гo елементів І блока диспозицій та з виходом третього елемента І блока аналізу, п'ятий вхід третього елемента І блока диспозицій з'єднаний з п'ятим входом n-1-го елемента І блока диспозицій та з виходом третього елемента І блока аналізу, шостий вхід третього елемента І блока диспозицій з'єднаний з шостим входом n-1-го елемента І блока диспозицій та з виходом n-1-го елемента І блока аналізу, сьомий вхід n-1-го елемента І блока диспозицій з'єднаний з виходом n-1-го елемента І блока аналізу, крім того, в елементи АБО блока установки в нуль з першого по n-2 введені додаткові ki входи, кількість яких зменшується на ki-1-1, перший вхід першого елемента АБО з'єднаний з виходом другого елемента І регістра, другий вхід першого елемента АБО з'єднаний з другим входом другого елемента АБО блока установки в нуль та з виходом третього елемента І регістра, третій вхід першого елемента АБО з'єднаний з третіми входами другого та третього елементів АБО та з виходом четвертого елемента І регістра, четвертий вхід першого елемента АБО з'єднаний з четвертими входами другого, третього та n-1-го елементів АБО та з виходом n-го елемента І регістра, п'ятий вхід першого елемента АБО з'єднаний з п'ятими входами другого, третього та n-1-го елементів АБО, з входом установки в нульовий n-го тригера та з виходом елемента І блока установки в нуль, виходи n-1 елементів АБО з'єднані з входами установки в нульовий стан n-1 тригерів регістра.

Текст

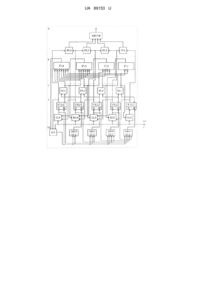

Реферат: UA 89153 U UA 89153 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної, інформаційно-вимірювальної техніки та автоматики і може використовуватися В пристроях дискретної обробки інформації, зокрема, як лічильники та розподільники імпульсів з підвищеною швидкодією та можливістю виправлення помилок. Відомий лічильник імпульсів Фібоначчі (журнал "Вісник СумДУ". Серія "Технічні науки", № 3, 2012, с. 165-170), що містить n - розрядний регістр, кожен розряд якого містить тригер та елемент І, блок аналізу, що містить n-1 елементів І, блок диспозицій, що містить n-1 елементів І з інверторами на входах, блок контролю, що містить n-1 елементів, об'єднаних елементом АБО, блок установки в нуль, що містить n-1 елементів АБО та елемент І, до першого входу якого приєднана шина тактових імпульсів, виходи n-1 елементів І блока аналізу з'єднані з першими входами n-1 елементів І регістра, другі входи яких та перший вхід елемента І блока установки в нуль з'єднані з вхідною шиною тактовий імпульсів, прямі виходи n-1 тригерів з'єднані з третіми входами елементів І регістра, четверті входи яких з'єднані з виходами n-2 елементів І блока диспозицій, вихід n-1-го елемента І блока диспозицій з'єднаний з третім входом елемента І блока установки в нуль, виходи елементів І регістра з'єднані з входами установки тригерів в одиничний стан, інверсні виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока аналізу, прямі виходи тригерів з'єднані з першими а другими входами n-1 елементів І блока контролю, прямий вихід n-го тригера з'єднаний з другим входом елемента І блока установки в нуль, виходи елементів І блока контролю з'єднані з входами елемента АБО блока контролю. Цей пристрій наближений до того, що заявляється, за технічною суттю та результатом, що досягається, тому він був вибраний як найближчий аналог. Недоліком найближчого аналога є його невисока швидкодія при зростанні розрядності вхідної кодової комбінації. В основу корисної моделі поставлена задача удосконалення лічильника імпульсів шляхом введення додаткових інверторів, які утворюють блок диспозицій та додаткових зв'язків в елементах АБО блоку установки в нуль, за рахунок чого з'являється можливість підвищення його швидкодії. Поставлена задача вирішується тим, що у відомий лічильник імпульсів, що містить nрозрядний регістр, кожен розряд якого містить тригер та елемент І, блок аналізу, що містить n-1 елементів 1, блок диспозицій, що містить n-1 елементів І з інверторами на входах, блок контролю, що містить n-1 елементів І, об'єднаних елементом АБО, блок установки в нуль, що містить n-1 елементів АБО та елемент І, до першого входу якого приєднана шина тактових імпульсів, виходи n-1 елементів І блока аналізу з'єднані з першими входами n-1 елементів I регістра, другі входи яких та перший вхід елемента І блока установки в нуль з'єднані з вхідною шиною тактових імпульсів, прямі виходи n-1 тригерів з'єднані з третіми входами елементів І регістра, четверті входи яких з'єднані з виходами n-2 елементів І блока диспозицій, вихід n-1-го елемента І блока диспозицій з'єднаний з третім входом елемента І блока установки в нуль, виходи елементів І регістра з'єднані з входами установки тригерів в одиничний стан, інверсні виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока аналізу, прямі виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока контролю, прямий вихід n-го тригера з'єднаний з другим входом елемента І блока установки в нуль, виходи елементів І блока контролю з'єднані з входом елемента АБО, згідно із корисною моделлю, в елементи І блока диспозицій з другого по n-1 введені додаткові kn-входи з інверторами, при цьому в другий та третій елементи І введено k n-1+2 входів з інверторами, а в n-1 елемент І введено kn-1+1 входів з інверторами, перший вхід першого елемента І з'єднаний з першими входами другого, третього та n-1-го елементів І блока диспозицій та з виходoм першого елемента І блока аналізу, другий вхід першого елемента І блока диспозицій з'єднаний з другими входами другого, третього та n-1-го елементів І блока диспозицій та з виходом другого елемента І блока аналізу, третій вхід другого елемента І блока диспозицій з'єднаний з третіми входами третього та n-1-го елементів І блока диспозицій та з виходом другого елемента І блока аналізу, четвертий вхід другого елемента І блока диспозицій з'єднаний з четвертими входами третього та n-1-го елементів І блока диспозицій та з виходом третього елемента І блока аналізу, п'ятий вхід третього елемента І блока диспозицій з'єднаний з п'ятим входам n-1-го елемента І блока диспозицій та з виходом третього елемента І блока аналізу, шостий вхід третього елемента І блока диспозицій з'єднаний з шостим входом n-1-го елемента І блока диспозицій та з виходом n-1-го елемента І блока аналізу, сьомий вхід n-1-го елемента І блока диспозицій з'єднаний з виходом n-1-го елемента I блока аналізу, крім того в елементи АБО блоку установки в нуль з першого по n-2 введені додаткові ki входи, кількість як їх зменшується на ki-1-1, перший вхід першого елемента АБО з'єднаний з виходом другого елемента І регістра, другий вхід 1 UA 89153 U 5 10 першого елемента АБО з'єднаний з другим входом другого елемента АБО блока установки в нулі, та з виходом третього елемента І регістра, третій вхід першого елемента АБО з'єднаний з третіми входами другого та третього елементів АБО та з ВИХОДOМ четвертого елемента I регістра, четвертий вхід першого елемента АБО з'єднаний з четвертими входами другого, третього та n-1-го елементів АБО та з виходом n-го елемента І регістра, п'ятий вхід першого елемента АБО з'єднаний з п'ятими входами другого, третього та n-1-го елементів АБО, з входом установки в нульовий n-го тригера та з виходом елемента І блока установки в нуль, виходи n-1 елементів АБО з'єднані з входами установки в нульовий стан n-1 тригерів регістра. Виконання пристрою в сукупності з усіма суттєвими ознаками, включаючи відмінності, забезпечує підвищення швидкодії, що досягається зa рахунок утворення сигналу паралельного переносу у зв'язку із введенням додаткових елементів та зв'язків, що дозволяє суттєво скоротити ЧАС розповсюдження сигналів у схемі. Суть корисної моделі пояснюється схемою лічильника імпульсів з кількістю розрядів n=5. Стани лічильника імпульсів, при n=5 розрядів наведені в таблиці 1. 15 Таблиця 1 Стани лічильника імпульсів при n=5 розрядів № імпульсу 0 1 2 3 4 5 6 7 8 9 10 11 12 20 25 30 35 40 5 0 0 0 0 0 0 0 0 1 1 1 1 1 4 0 0 0 0 0 1 1 1 0 0 0 0 0 Стани лічильника імпульсів 3 2 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 1 0 1 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 Лічильник імпульсів, що містить регістр 1, що містить тригери ТТ 2.1 - ТТ 2.5 та елементи І 3.1 - І 3.5, блок 4 аналізу, що містить елементи І 5.1 - І 5.4, блок 6 диспозицій, що містить елементи І 7.1 - І 7.4 з інверторами на входах, блок 8 контролю, що містить елементи І 9.1 - І 9.4, об'єднані елементом АБО 10, блок 11 установки в нуль, що містить елементи АБО 12.1 АБО 12.4 та елемент І 13, до першого входу якого приєднана шина 14 тактових імпульсів. Виходи елементів І 5.1 - І 5.4 з'єднані з першими входами елементів І 3.1 - І 3.4, другі входи яких та перший вхід елемента І 13 з'єднані з вхідною шиною тактовий імпульсів. Прямі виходи тригерів ТТ 2.1 - ТТ 2.4 з'єднані з третіми входами елементів І 3.1 - І 3.5, четверті входи яких з'єднані з виходами елементів І 7.1 - І 7.3, вихід елемента І 7.4 з'єднаний з третім входом елемента І 13, виходи елементів І 3.1 - І 3.5 з'єднані з входами установки тригерів ТТ 2.1 - ТТ 2.5 в одиничний стан. Інверсні виходи тригерів ТТ 2.1 - ТТ 2.5 з'єднані з першими та другими входами елементів І 5.1 - І 5.4, прямі виходи тригерів ТТ 2.1 - ТТ2.4 з'єднані з першими та другими входами елементів І 9.1 - І 9.4, прямий вихід тригера ТТ 2.5 з'єднаний з другим входом елемента І 13, виходи елементів І 9.1 - І 9.4 з'єднані з входом елемента АБО 10. Перший вхід елемента І 7.1 з'єднаний з першими входами елементів І 7.2 - І 7.4 та з'єднаний з виходом елемента І 5.1, другий вхід елемента І 7.1 з'єднаний з другими входами елементів І 7.2 - І 7.4 та з виходом елемента І 5.2, третій вхід елемента І 7.2 з'єднаний з третіми входами елементів І 7.3 та І 7.4 та з виходом елемента І 5.2, четвертий вхід елемента І 7.2 з'єднаний з четвертими входами елементів І 7.3 та І 7.4 та з виходом елемента І 5.3, п'ятий вхід елемента І 7.3 з'єднаний з п'ятим входам елемента І 7.4 та з виходом елемента І 5.3, шостий вхід елемента І 7.3 з'єднаний з шостим входом елемента І 7, та з виходом елемента І 5.4, сьомий вхід елемента І 5.4 з'єднаний з виходом елемента І 5.4. Перший вхід елемента АБО 12.1 з'єднаний з виходом елемента І 3.2, другий вхід елемента АБО 12.1 з'єднаний з другим входом елемента АБО 12.2 та з виходом елемента І 3.3, третій вхід елемента АБО 12.1 з'єднаний з третіми входами елементів АБО 12.1 та АБО 12.3 та і ВИХОДОМ елемента І 3.4, четвертий вхід елемента АБО 12.1 2 UA 89153 U 5 10 15 20 25 30 35 40 45 50 55 60 з'єднаний з четвертими входами елементів АБО 12.2 - АБО 12.4 та з виходом елемента І 3.5, п'ятий вхід елемента АБО 12.1 з'єднаний з п'ятими входами елементів АБО 12.2 - АБО 12.4, з входом установки в нульовий тригера ТТ 2.5 та з виходом елемента І, виходи елементів АБО 12.1 - АБО 12.4 з'єднані з входами установки в нульовий стан тригерів ТT 2.1 - ТТ 2.5. Лічильник імпульсів працює наступним чином. У початковому стані всі тригери ТТ 2.1 - ТТ 2.5 регістра 1 знаходяться в нулі, що відповідає кодовій комбінації 00000. При надходженні першого тактового імпульсу здійснюється запис 1 в тригер ТТ 2.1 регістра 1 через перший вхід елемента І 3.1 на який надходить одиничний сигнал з шини 14 тактових імпульсів, на другий вхід елемента І 3.1 надходить одиниця з виходу елемента І 5.1 блока 4 аналізу і встановлює перший тригер ТТ 2.1 в одиничний стан 00001. Решта тригерів ТТ 2.2 - ТТ 2.5 регістра 1 знаходяться в нульовому стані, так як на перші входи елементів І 3.2 - І 3.5 надходять нульові сигнали з прямих виходів тригерів ТT 2.1 - ТТ 2.4. При надходженні другого тактового імпульсу одиничний сигнал з прямого виходу тригера ТТ 2.1 надходить на третій вхід елемента І 3.2, на перший вхід якого надходить сигнал з виходу елемента І 5.2 блока 4 аналізу, на входи якого з інверсних виходів тригерів ТT 2.1, ТT 2.3 регістра надходять дві 1. Одночасно 1 з виходу елемента І 3.2 подається на перший вхід елемента АБО 12.1 блока 11 установки в нуль, на інші входи якого надходять нульові сигнали з елементів І 3.3 - І 3.5. В результаті одиничний сигнал надійде на прямий вхід другого тригера ТТ 2.2, а перший тригер ТТ 2.1 встановиться в нульовий стан, що відповідає кодовій комбінації 00010. Третій тактовий імпульс встановлює тригер ТТ 2.3 в одиничний стан. Це відбувається тому, що на третій вхід елемента І 3.3 надходить одиничний сигнал з прямого виходу тригера ТТ 2.2, на перший вхід якого надходить сигнал з виходу елемента І 5.3 блока 4 аналізу, так як з інверсних виходів тригерів ТT 2.3, ТТ 2.4 на вхід елемента I 5.3 блока 4 аналізу надходить 1. Нa перший вхід елемента І 3.3 надходить 1 з виходу елемента І 7.1 блоку 6 диспозицій, так як на вхід елемента І 3.2 подається нульовий сигнал з виходу прямого тригера ТТ 2.1, в результаті чого на інверсних виходах тригерів ТТ 2.1 - ТТ 2.3 буде нульовий сигнал, який надходить на елементи І 5.1 - І 5.2 блока 4 аналізу, а з його виходу на перший та другий інвертори, що знаходяться на вході елемента І 7.1 блока 6 диспозицій. Одночасно з виходу елемента І 3.3 одиничний сигнал надходить на перший вхід елемента АБО 12.2 і з його виходу на другий вхід елемента АБО 12.1 блока установки нуля 11, вихід якого з'єднаний з входом установки в нуль тригерів ТT 2.1 - ТT 2.5. Таким чином тригери ТТ 2.1 і ТТ 2.2 перейдуть в нульовий стан, а тригер ТТ 2.3 в одиничний. Цей перехід відповідає стану лічильника 00100. Після появи максимального числа Фібоначчі на виході елемента І 7.4 блока 6 диспозицій з'явиться 1, яка спільно з 1 на прямому виході тригера ТТ 2.5 подається на вхід елемента І 13 і встановлює всі тригери ТТ 2.1 - ТТ 2.5 регістра 1 в нульовий стан. Після цього лічба закінчується, регістр встановлюється в нульовий стан, після чого починається новий цикл лічби. Наявні у пристрої послідовно з'єднані схеми з двома входами елементів І 9.1 - І 9.4 блоку 8 контролю слугують для аналізу вірності роботи лічильника, виходи яких об'єднані елементом АБО 10, а входи з'єднані з прямими виходами тригерів, які знаходяться поруч. Якщо в результаті лічби відбудеться помилка, що характеризується появою двох одиниць, які знаходяться поруч у розрядах числа Фібоначчі, то на один з елементів І 9.1 - І 9.4 надійде одиничний сигнал, в результаті чого на виході елемента АБО 10 з'явиться 1, що буде характеризувати наявність помилки. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Лічильник імпульсів, що містить n - розрядний регістр, кожен розряд якого містить тригер та елемент І, блок аналізу, що містить n-1 елементів І, блок диспозицій, що містить n-1 елементів І з інверторами на входах, блок контролю, що містить n-1 елементів I, об'єднаних елементом АБО, блок установки в нуль, що містить n-1 елементів АБО та елемент І, до першого входу якого приєднана шина тактових імпульсів, виходи n-1 елементів I блока аналізу з'єднані з першими входами n-1 елементів І регістра, другі входи яких та перший вхід елемента І блока установки в нуль з'єднані з вхідною шиною тактовий імпульсів, прямі виходи n-1 тригерів з'єднані з третіми входами елементів І регістра, четверті входи яких з'єднані з виходами n-2 елементів І блока диспозицій, вихід n-1-го елемента І блока диспозицій з'єднаний з третім входом елемента І блока установки в нyль, виходи елементів І регістра з'єднані з входами установки тригерів в одиничний стан, інверсні виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока аналізу, прямі виходи тригерів з'єднані з першими та другими входами n-1 елементів І блока контролю, прямий вихід n-го тригера з'єднаний з другим входом елемента І блока установки в нyль, виходи елементів І блока контролю з'єднані з входом 3 UA 89153 U 5 10 15 20 25 елемента АБО, який відрізняється тим, що в елементи І блока диспозицій з другого по n-1 введені додаткові kn-входи з інверторами, при цьому в другий та третій елементи І введено kn1+2 входів з інверторами, а в n-1 елемент I введено kn-1+1 входів з інверторами, перший вхід першого елемента I з'єднаний з першими входами другого, третього та n-1-го елементів I блока диспозицій та з виходом першого елемента І блока аналізу, другий вхід першого елемента І блока диспозицій з'єднаний з другими входами другого, третього та n-1-го елементів І блока диспозицій та з виходом другого елемента І блока аналізу, третій вхід другого елемента І блока диспозицій з'єднаний з третіми входами третього та n-1-го елементів І блока диспозицій та з виходом другого елемента І блока аналізу, четвертий вхід другого елемента І блока диспозицій з'єднаний з четвертими входами третього та n-1-гo елементів І блока диспозицій та з виходом третього елемента І блока аналізу, п'ятий вхід третього елемента І блока диспозицій з'єднаний з п'ятим входом n-1-го елемента І блока диспозицій та з виходом третього елемента І блока аналізу, шостий вхід третього елемента І блока диспозицій з'єднаний з шостим входом n-1-го елемента І блока диспозицій та з виходом n-1-го елемента І блока аналізу, сьомий вхід n-1-го елемента І блока диспозицій з'єднаний з виходом n-1-го елемента І блока аналізу, крім того, в елементи АБО блока установки в нуль з першого по n-2 введені додаткові ki входи, кількість яких зменшується на ki-1-1, перший вхід першого елемента АБО з'єднаний з виходом другого елемента І регістра, другий вхід першого елемента АБО з'єднаний з другим входом другого елемента АБО блока установки в нуль та з виходом третього елемента І регістра, третій вхід першого елемента АБО з'єднаний з третіми входами другого та третього елементів АБО та з виходом четвертого елемента І регістра, четвертий вхід першого елемента АБО з'єднаний з четвертими входами другого, третього та n-1-го елементів АБО та з виходом n-го елемента І регістра, п'ятий вхід першого елемента АБО з'єднаний з п'ятими входами другого, третього та n1-го елементів АБО, з входом установки в нульовий n-го тригера та з виходом елемента І блока установки в нуль, виходи n-1 елементів АБО з'єднані з входами установки в нульовий стан n-1 тригерів регістра. 4 UA 89153 U Комп’ютерна верстка І. Мироненко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Автори англійськоюBorysenko Oleksii Andriiovych

Автори російськоюБорисенко Алексей Андреевич

МПК / Мітки

МПК: H03K 23/00

Код посилання

<a href="https://ua.patents.su/7-89153-lichilnik-impulsiv.html" target="_blank" rel="follow" title="База патентів України">Лічильник імпульсів</a>

Попередній патент: Пристрій для видалення електропровідних немагнітних часток із потоку сипучого матеріалу

Наступний патент: Стрічкопротяжний механізм

Випадковий патент: Стенд для випробування транспортних засобів з відтворенням профілю дорожнього полотна