Формувач одиначної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами

Номер патенту: 92187

Опубліковано: 11.08.2014

Автори: Коробкова Олена Миколаївна, Коробков Микола Григорович, Рубанов Василь Григорович, Харченко Вячеслав Сергійович

Формула / Реферат

Формувач одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, який містить двійковий реверсивний лічильник, налагоджений на режим віднімання, зі входами синхронного паралельного завантаження, входом дозволу режиму рахування і входом асинхронної установки у нульовий стан, вихід переповнення якого з'єднаний зі входом дозволу синхронної паралельної установки його в стан, визначуваний змінними, що подаються на входи паралельного завантаження, який відрізняється тим, що введено двійковий суматор, чотири інвертори, компаратор, перший і другий синхронні D- і JK-тригери зі входом асинхронної установки у нульовий стан, тривходовий елемент АБО-НІ, двовходовий елемент І-НІ, перший і другий двовходові елементи І, двовходовий елемент АБО, ланцюжок, що складається з резистора і конденсатора, при цьому входи· першої групи входів суматора з'єднано з відповідними входами завантаження лічильника, які утворюють входи налагодження формувача на задану тривалість триімпульсної серії; входи другої групи суматора з'єднано з виходами інверторів, входи яких утворюють входи налагодження формувача на задані паузи між імпульсами в серії; входи першої групи входів компаратора з'єднано з відповідними виходами лічильника; входи другої групи входів компаратора з'єднано з відповідними виходами суматора; вхід D першого тригера з'єднано з виходом елемента АБО-НІ, перший вхід якого з'єднано з виходом молодшого (нульового) розряду лічильника, другий - з виходом другого розряду, третій - з виходом старшого(третього) розряду; інверсний вихід першого D-тригера і вихід компаратора з'єднано зі входами елемента І-НІ, вихід якого утворює вихід формувача; тактові входи лічильника, JK-тригера і першого D-тригера з'єднані між собою, утворюючи вхід формувача - вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; ланцюжок, що складається з послідовно з'єднаних резистора і конденсатора, з'єднано з джерелом живлення, а загальна точка його з'єднана з першими входами першого та другого елементів І і входом D другого D-тригера, вихід якого з'єднано з першим входом елемента АБО, другий вхід якого з'єднано з виходом JK-тригера, третій - з виходом переповнення лічильника і входами J і К JK-тригера; вихід елемента АБО з'єднано з другим входом другого елемента І, вихід якого з'єднано зі входами асинхронної установки у нульовий стан лічильника і першого D-тригера; тактовий вхід другого D-тригера утворює вхід подачі імпульсів запуску; другий вхід першого елемента І з'єднано виходом компаратора; вихід першого елемента І з'єднано зі входом асинхронної установки у нульовий стан другого D-тригера.

Текст

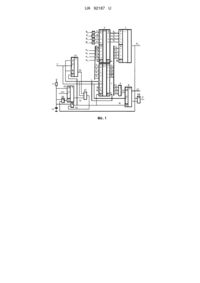

Реферат: Формувач одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, який містить двійковий реверсивний лічильник, налагоджений на режим віднімання, зі входами синхронного паралельного завантаження, входом дозволу режиму рахування і входом асинхронної установки у нульовий стан, вихід переповнення якого з'єднаний зі входом дозволу синхронної паралельної установки його в стан, визначуваний змінними, що подаються на входи паралельного завантаження. Введено двійковий суматор, чотири інвертори, компаратор, перший і другий синхронні D- і JKтригери зі входом асинхронної установки у нульовий стан, тривходовий елемент АБО-НІ, двовходовий елемент І-НІ, перший і другий двовходові елементи І, двовходовий елемент АБО, ланцюжок, що складається з резистора і конденсатора. UA 92187 U (12) UA 92187 U UA 92187 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до автоматики, імпульсної, обчислювальної і вимірювальної техніки, та призначена для формування одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що одаються на її вхід з виходу кварцового генератора. Відомі формувачі, що містять кварцовий задавальний генератор, працюючий у безперервному режимі, пристрій синхронізації і вихідний пристрій, що забезпечує формування необхідних серій імпульсів, часові параметри яких визначаються часовими параметрами імпульсів, що подаються на вхід (Авторське свідоцтво СРСР №307502. - Бюлетень винаходів №20, 1971, Авторське свідоцтво СРСР №354544. - Бюлетень винаходів №30, 1972). Недолік відомих пристроїв - обмежені функціональні можливості, обумовлені налагодженням на фіксований режим часових параметрів вихідної послідовності імпульсів. Найбільш близьким за технічною суттю і результатом, що досягається, є формувач імпульсів, виконаний на двійковому лічильнику (рис. 7.94. Пухальський Г.І., Новосельцева Т.Я. Цифровые устройства. - Спб.: Политехника 1986. - 485 с), який містить двійковий реверсивний лічильник, налагоджений на режим віднімання, з входами синхронного паралельного завантаження, входом дозволу режиму рахування і входом асинхронної установки в нульовий стан, вихід переповнення якого з'єднаний з входом дозволу синхронної паралельної установки його в стан, визначуваний конфігураційними змінними, що подаються на входи паралельного завантаження, що забезпечує можливість програмування числа станів лічильника. Недолік відомого пристрою - обмежені функціональні можливості. У основу корисної моделі поставлено задачу удосконалення формувача одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, за допомогою введення нового складу елементів і нової сукупності взаємних з'єднань між ними, забезпечити розширення функціональних можливостей. Поставлена задача вирішується тим, що в формувач одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, який містить двійковий реверсивний лічильник, налагоджений на режим віднімання, зі входами синхронного паралельного завантаження, входом дозволу режиму рахування і входом асинхронної установки у нульовий стан, вихід переповнення якого з'єднаний зі входом дозволу синхронної паралельної установки його в стан, визначуваний змінними, що подаються на входи паралельного завантаження, відповідно до корисної моделі введено двійковий суматор, чотири інвертори, компаратор, перший і другий синхронної D- і JK-тригери зі входом асинхронної установки у нульовий стан, тривходовий елемент АБО-НІ, двовходовий елемент І-НІ, перший і другий двовходові елементи І, двовходовий елемент АБО, ланцюжок, що складається з резистора і конденсатора, при цьому входи першої групи входів суматора з'єднано з відповідними входами завантаження лічильника, які утворюють входи налагодження формувача на задану тривалість триімпульсної серії; входи другої групи суматора з'єднано з виходами інверторів, входи яких утворюють входи налагодження формувача на заданої паузи між імпульсами в серії; входи першої групи входів компаратора з'єднано з відповідними виходами лічильника; входи другої групи входів компаратора з'єднано з відповідними виходами суматора; вхід D першого тригера з'єднано з виходом елемента АБО-НІ, перший вхід якого з'єднано з виходом молодшого (нульового) розряду лічильника, другий - з виходом другого розряду, третій - з виходом старшого(третього) розряду; інверсний вихід першого D-тригера і вихід компаратора з'єднано зі входами елемента І-НІ, вихід якого утворює вихід формувача; тактові входи лічильника, JK-тригера і першого D-тригера з'єднані між собою, утворюючи вхід формувача вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; ланцюжок, що складається з послідовно з'єднаних резистора і конденсатора з'єднано з джерелом живлення, а загальна точка його з'єднана з першими входами першого та другого елементів І і входом D другого D-тригера, вихід якого з'єднано з першим входом елемента АБО, другий вхід якого з'єднано з виходом JK-тригера, третій - з виходом переповнення лічильника і входами J і К JK-тригера; вихід елемента АБО з'єднано з другим входом другого елемента І вихід якого з'єднано зі входами асинхронної установки у нульовий стан лічильника і першого Dтригера; тактовий вхід другого D-тригера утворює вхід подачі імпульсів запуску; другий вхід першого елемента І з'єднано виходом компаратора; вихід першого елемента І з'єднано зі входом асинхронної установки у нульовий стан другого D-тригера. Заявлений формувач має новий склад елементів і нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості. Технічний 1 UA 92187 U 5 10 15 20 25 30 35 40 45 50 55 60 результат, як наслідок цих властивостей, розширення області використання і функціональних можливостей формувача. На фіг. 1 приведена схема формувача. Формувач містить: двійковий реверсивний лічильник (1), налагоджений на режим віднімання (U=0), зі входами синхронного паралельного завантаження D 0-D3, входом дозволу режиму рахування Р0, входом подачі тактових імпульсів С, входом асинхронної установки у нульовий стан R, виходами разрядів Q0-Q3, виходом переповнення Р4; двійковий суматор (2), чотири інвертори (3-6), компаратор (7), перший (8) та другий (13) синхронної D-тригери і JK-тригер (17) зі входами асинхронної установки у нульовий стан, тривходовий елемент АБО-НІ (9), двовходовий елемент І-НІ (10), ланцюжок, що складається з резистора (11) і конденсатора (12), перший (14) та другий (16) двовходові елементи І, двовходовий елемент АБО (15). Вихід Р4 лічильника 1 з'єднаний зі входом L дозволу синхронного паралельного завантаження. Входи А0 - А3 суматора 2, які з'єднано з відповідними входами D0-D3 завантаження лічильника, утворюють входи а0 - а3 налагодження формувача на задану тривалість кодової серії. Входи інверторів 2-6, виходи яких з'єднано зі входами В0-В3, утворюють входи b0-b3 налагодження формувача на заданої паузи проміж імпульсами в серії. Входи А0-А3 компаратора 7 з'єднано з відповідними виходами Q0-Q3 лічильника. Входи В0 - В3 компаратора з'єднано з відповідними виходами S0-S3 суматора. Вхід D тригера 8 з'єднано з виходом елемента АБО-НІ 9, перший вхід якого з'єднано з виходом Q0 лічильника, другий - з виходом Q2, треті - з виходом Q3. Інверсний вихід першого D-тригера і вихід компаратора з'єднано зі входами елемента І-НІ 10, вихід якого утворює вихід F формувача. Тактові входи С лічильників, JK-тригера і першого D-тригера з'єднані між собою, утворюючи вхід формувача - вхід подачі безперервної періодичної послідовності імпульсів С з виходу зовнішнього генератора. Ланцюжок, що складається з послідовно з'єднаних резистора 11 і конденсатора 12 з'єднано з джерелом живлення +Е, а загальна точка ланцюжка з'єднана з першими входами першого (14) та другого (16) елементів І і входом D другого D-тригера, вихід якого з'єднано з першим входом елемента АБО 15, другий вхід якого з'єднано з виходом переповнення лічильника і входами J і К JKтригера, третій - з виходом JK-тригера; вихід елемента АБО 14 з'єднано з другим входом елемента І 16, вихід якого з'єднано зі входами асинхронної установки у нульовий стан лічильника, JK-тригера і першого D-тригера; тактовий вхід другого D-тригера утворює вхід подачі імпульсів запуску (Start); другий вхід елемента 115 з'єднано з виходом компаратора, вихід елемента І 15 з'єднано зі входом асинхронної установки у нульовий стан другого Dтригера. Працює формувач в наступній послідовності. Наявність ланцюжка, що складається із поєднаних послідовно резистора 11 і конденсатора 12 підключеною до шини живлячої напруги (+Е), при включенні джерела живлення протягом деякого проміжку часу формує рівень логічного нуля на входах елементів 14 та 16, забезпечуючи формування рівня логічного нуля на їх виходах, приєднаних до входів асинхронної установки в нульовий стан відповідно першого і другого D - тригерів (9, 13), лічильника 1 і JK-тригера. Після закінчення перехідного процесу, пов'язаного з включенням джерела живлення тригери 9, 13, 17 і лічильник 1 переходять в нульовий стан, формуючи рівень логічного нуля відповідно на виході (Q) D - тригерів і на виходе переповнювання лічильника, що веде до формування рівня логічного нуля на виході двовходового елемента 15, приєднаного до входу елемента 16, що забезпечує підтвердження (блокування) рівня логічного нуля на його виході і по закінченню перехідного процесу, пов'язаного із зарядом конденсатора 12, коли напруга на нім перевищить рівень логічного нуля, що забезпечує рівень логічного нуля на входах на входах R асинхронної установки у нульовий стан лічильника, JK-тригера і першого D-тригера, забезпечуючи формування рівня логічного нуля на виходах Q 0-Q3, Ρ4 лічильника, прямому виході JK-тригера і першого D-тригера і рівень логічної одиниці на його інверсному виході, що веде до формування рівня логічного нуля на вході L лічильника і JK-тригера, готуючи лічильник до прийому інформації зі входів D0-D3, а JK-тригер до переходу в одиничний стан і рівня логічної одиниці на вході першого D-тригера, готуючи його також до переходу в одиничний стан. Оскільки режим асинхронної установки лічильників у нульовий стан має пріоритет по відношенню до всіх останніх режимів, то до тих пір, поки на вході елементу 16 (а отже і на його виході) зберігатиметься рівень логічного нуля, нульовий стан лічильника, JK-тригера і першого D-тригера не зміниться. Під час вступу імпульсу запуску (Start) на тактовий вхід другого D-тригера по його фронту він переходить в одиничний стан (Q=1), формуючи рівень логічної одиниці на виході елементу 15, а отже на вході і виході елементу І 16, що забезпечує рівень логічного одиниці на входах R 2 UA 92187 U 5 10 15 20 25 30 35 40 45 50 55 60 лічильника 1, JK-тригера і першого D-тригера, знімаючи блокування нульового стану. Активний сигнал з виходу переповнювання лічильника 1, тобто на вході дозволу синхронного паралельного завантаження лічильника (L) і входах J і К JK-тригера, готуючи JK-тригер к переходу в одиничній стан, а лічильник - до прийому інформації зі входів а0 -а3. І тоді під час вступу першого (після закінчення перехідного процесу, пов'язаного з переходом другого тригера в одиничний стан) тактового імпульсу С по його фронту відбувається перехід JK-тригера в одиничній стан і паралельне завантаження лічильника значеннями сигналів, що подаються на відповідні входи, тобто лічильник переходить у стан а3а2а1а0, формуючи одиничне значення на виході Р4, що веде до переходу лічильника у режим лічби, а JK-тригера в режим зберігання одиниці. Перший тригер переходить в одиничний стан, що веде до формування нульового значення на його інверсному виході, тобто на вході елемента І-НІ 10, формуючи одиничне значення на його виході тобто на виході F формувача. Оскільки тривалість триімпульсної серії не може бути менше 5 Τ (Τ - період прямування тактових імпульсів), то значення лічильника в розрядах Q 3 або Q2 або обидва будуть вміщувати одиницю, і тоді при переході лічильника у стан а3а2а1а0 на виході елемента АБО-НІ, тобто на вході тригера, формується рівень логічного нуля. Під час вступу другого (після закінчення перехідного процесу, пов'язаного із переходом другого тригера в одиничний стан) перший тригер переходе у нульовий стан, що веде к формуванню рівня логічного нуля на виході F формувача, зміст лічильника зменшиться на одиницю, одиничний стан JK-тригера залишиться не змінним. Під час вступу подальших тактових імпульсів зміст лічильника буде зменшуватися, а нульовий стан першого D-тригера і одиничний стан JK-тригера залишаться незмінними. Нульове значення сигналу на виході формувача також буде залишитися незмінним до тих пір доки зміст лічильника не стане рівнім а3а2а1а0-b3b2b1b0, на інверсному виході компаратора (на вході елемента І-НІ 10) буде сформовано рівень логічного нуля, у результаті чого другий тригер переходе у нульовий стан, що веде к формуванню рівня логічної одиниці на виході F формувача, тобто к формуванню другого імпульсу в серії, і переходу другого тригера у нульовий стан. Під час вступу подальших тактових імпульсів зміст лічильника буде зменшуватися, а нульовий стан першого і другого тригера залишиться незмінним. Нульове значення сигналу на виході формувача також буде залишитися незмінним до тих пір доки зміст лічильника не стане рівнім 0010, що веде к формуванню рівня логічної одиниці на вході першого D-тригера, готуючи його до переходу в одиничний стан. І тоді під час вступу наступного тактового імпульсу лічильник переходить у стан 0001, а тригер переходить в одиничний стан, що веде к формуванню рівня логічного нуля на його інверсному виході і рівня логічної одиниці на виході елемента І-НІ 10, тобто формування третього імпульсу на виході формувача. Зі вступом наступного тактового імпульсу лічильник переходить у нульовий стан, що веде к формуванню рівня логічного нуля на його виході переповнення, тобто на вході L лічильника і входах J і К JK-тригера, готуючи JK-тригер к переходу у нульовий стан, а лічильник - до прийому інформації зі входів а0-а3. І тоді під час вступу наступного тактового імпульсу лічильник переходить у стан а 0 - а3, JK-тригер - у нульовий стан. Під час вступу подальших тактових імпульсів процеси аналогічні розглянутим вище, тобто формується друга триимпульсна кодова серія. При цьому, як тільки лічильник знову перейде у нульовий стан на його виході переповнення, на входах елементів 15, 16, на входах асинхронної установки у нульовий стан лічильника, JK-тригера і першого D-тригера формується рівень логичного нуля, що веде до блокування вихідного нульового стану. Зі вступом наступного імпульсу запуску усі процеси повторюються. Таким чином, після закінчення перехідного процесу, пов'язаного з переходом другого тригера в одиничний стан, під час вступу на вхід С формувача періодичної послідовності імпульсів з періодом Τ на виході формувача генерується одиночна пачка з двох триімпульсних кодових серій імпульсів фіксованої тривалості, рівної періоду тактових імпульсів Т, з програмованою тривалістю серії Т с = а3а2а1а0Т і програмованою тривалістю першої і другої паузи в серії (tп1,tп2), які визначаються значеннями змінних b3b2b1b0 і а3а2а1а0: tп1 = (b3b2b1b0-1)Т, tп2 = (а3а2а1а0-b3b2b1b0-2)1. На фіг. 2 приведений граф переходів формувача, що складається з двох кілець (верхнє кільце - граф переходів тригера 17, середнє кільце - граф переходів лічильника із загальною вершиною, відповідною нульовому стану тригера 17 і лічильника, а на фіг. 3 - епюри, що ілюструють роботу, для варіанту налагодження а3а2а1а0=1010, b3b2b1b0=0011 (Тс = 10Т, tп1=2T, tп2=5T). На відміну від відомого пристрою формування одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, а 3 UA 92187 U також наявність старт/стопного пристрою розширює область використання і функціональні можливості формувача. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 30 35 Формувач одиночної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами, кратними періоду безперервної періодичної послідовності імпульсів, що подаються на її вхід з виходу кварцового генератора, який містить двійковий реверсивний лічильник, налагоджений на режим віднімання, зі входами синхронного паралельного завантаження, входом дозволу режиму рахування і входом асинхронної установки у нульовий стан, вихід переповнення якого з'єднаний зі входом дозволу синхронної паралельної установки його в стан, визначуваний змінними, що подаються на входи паралельного завантаження, який відрізняється тим, що введено двійковий суматор, чотири інвертори, компаратор, перший і другий синхронні D- і JK-тригери зі входом асинхронної установки у нульовий стан, тривходовий елемент АБО-НІ, двовходовий елемент І-НІ, перший і другий двовходові елементи І, двовходовий елемент АБО, ланцюжок, що складається з резистора і конденсатора, при цьому входи· першої групи входів суматора з'єднано з відповідними входами завантаження лічильника, які утворюють входи налагодження формувача на задану тривалість триімпульсної серії; входи другої групи суматора з'єднано з виходами інверторів, входи яких утворюють входи налагодження формувача на задані паузи між імпульсами в серії; входи першої групи входів компаратора з'єднано з відповідними виходами лічильника; входи другої групи входів компаратора з'єднано з відповідними виходами суматора; вхід D першого тригера з'єднано з виходом елемента АБО-НІ, перший вхід якого з'єднано з виходом молодшого (нульового) розряду лічильника, другий - з виходом другого розряду, третій - з виходом старшого (третього) розряду; інверсний вихід першого D-тригера і вихід компаратора з'єднано зі входами елемента І-НІ, вихід якого утворює вихід формувача; тактові входи лічильника, JK-тригера і першого Dтригера з'єднані між собою, утворюючи вхід формувача - вхід подачі безперервної періодичної послідовності імпульсів з виходу зовнішнього генератора; ланцюжок, що складається з послідовно з'єднаних резистора і конденсатора, з'єднано з джерелом живлення, а загальна точка його з'єднана з першими входами першого та другого елементів І і входом D другого Dтригера, вихід якого з'єднано з першим входом елемента АБО, другий вхід якого з'єднано з виходом JK-тригера, третій - з виходом переповнення лічильника і входами J і К JK-тригера; вихід елемента АБО з'єднано з другим входом другого елемента І, вихід якого з'єднано зі входами асинхронної установки у нульовий стан лічильника і першого D-тригера; тактовий вхід другого D-тригера утворює вхід подачі імпульсів запуску; другий вхід першого елемента І з'єднано виходом компаратора; вихід першого елемента І з'єднано зі входом асинхронної установки у нульовий стан другого D-тригера. 4 UA 92187 U Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Автори англійськоюKorobkov Mykola Hryhorovych, Korobkova Olena Mykolaivna, Rubanov Vasyl Hryhorovych, Kharchenko Viacheslav Serhiiovych

Автори російськоюКоробков Николай Григорьевич, Коробкова Елена Николаевна, Рубанов Василий Григорьевич, Харченко Вячеслав Сергеевич

МПК / Мітки

МПК: H03K 3/78

Мітки: триімпульсних, пачки, двох, формувач, одиначної, серій, кодових, часовими, параметрами, програмованими

Код посилання

<a href="https://ua.patents.su/7-92187-formuvach-odinachno-pachki-z-dvokh-triimpulsnikh-kodovikh-serijj-z-programovanimi-chasovimi-parametrami.html" target="_blank" rel="follow" title="База патентів України">Формувач одиначної пачки з двох триімпульсних кодових серій з програмованими часовими параметрами</a>

Попередній патент: Формувач одиночної триімпульсної кодової серії з програмованими часовими параметрами

Наступний патент: Волоконно-оптичний датчик тиску

Випадковий патент: Пристрій для визначення статичної твердості деревини