Синтезатор з цифровим процесом частотного циклу

Номер патенту: 102570

Опубліковано: 10.11.2015

Автори: Грамарчук Юрій Олександрович, Кобак Микола Миколайович, Слесаренко Сергій Сергійович, Петренко В'ячеслав Петрович

Формула / Реферат

Синтезатор з цифровим процесом частотного циклу, що містить подільники частоти N÷1 та N÷2, модулі пам'яті, процесор, генератор, керований напругою, цифро-аналоговий перетворювач, який відрізняється тим, що додатково містить цифровий компаратор, який введено в канал перетворення частоти між вихідними каналами та цифро-аналоговим перетворювачем.

Текст

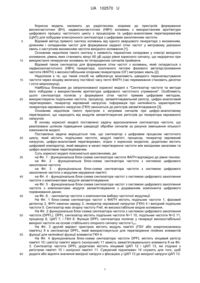

Реферат: Синтезатор з цифровим процесом частотного циклу містить подільники частоти N÷1 та N÷2, модулі пам'яті, процесор, генератор, керований напругою, цифро-аналоговий перетворювач. Додатково синтезатор містить цифровий компаратор, який введено в канал перетворення частоти між вихідними каналами та цифро-аналоговим перетворювачем. UA 102570 U (54) СИНТЕЗАТОР З ЦИФРОВИМ ПРОЦЕСОМ ЧАСТОТНОГО ЦИКЛУ UA 102570 U UA 102570 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до радіотехніки, зокрема до пристроїв формування високочастотних (ВЧ), надвисокочастотних (НВЧ) коливань з використанням архітектури цифрового процесу частотного циклу з процесором та цифро-аналоговим перетворювачем (ЦАП) для побудови електронного синтезатора з цифровим захопленням частоти. Відомий метод прямого синтезу коливань від одного кварцового генератора з множенням, діленням і складанням частот для формування заданої сітки частот у метровому діапазоні хвиль з наступним множенням частоти вихідного коливання [1]. Основним недоліком такого синтезу є наявність паразитних складових у спектрі вихідного коливання, рівень яких становить мінус 60 дБ щодо рівня корисного сигналу, що недоречно при використанні генеруючих коливань як гетеродинних сигналів приймача. Відомий також синтезатор для формування сітки частот з коливань, який складається з надвисокочастотного (НВЧ) генератора, охопленого петлею фазового автопідстроювання частоти (ФАПЧ) з високостабільним опорним генератором (ОГ) метрових хвиль [2]. Недоліком є те, що такий спосіб не забезпечує можливість швидкого переналаштування частоти через кінцеву величину постійної часу петлі ФАПЧ (час перемикання становить десятки і сотні мікросекунд). Найбільш близьким до запропонованої корисної моделі є "Синтезатор частоти та методи його побудови з використанням архітектури цифрового частотного утримання". Особливість цього синтезатора полягає у формуванні сітки частот прямим цифровим методом, використовуючи подільники частоти, процесор, запам'ятовувальний регістр, цифро-аналоговий перетворювач, генератор керований напругою. Інформація про нелінійність характеристик генератора керованого напругою (ГКН) заноситься до регістрів запам'ятовування [3]. Основним недоліком такого пристрою є затримка сигналів при цифро-аналоговому перетворенні, що надходять від модулів запам'ятовуючих регістрів до генератора керованого напругою. В основу корисної моделі поставлено задачу вдосконалення синтезатора частоти, що реалізовано шляхом підвищення швидкодії обробки сигналів за рахунок зменшення кількості компонентів моделі. Поставлена задача вирішується тим, що синтезатор з цифровим процесом частотного циклу, який містить подільники частоти, модулі пам'яті, процесор, генератор керований напругою, цифро-аналоговий перетворювач, згідно з корисною моделлю, додатково містить цифровий компаратор, який введено в канал перетворення частоти між вихідними каналами та цифро-аналоговим перетворювачем. Суть корисної моделі пояснюється кресленнями, де: на Фіг. 1 - функціональна блок-схема синтезатора частоти ФАПЧ відповідно до рівня техніки; на Фіг. 2 - функціональна блок-схема синтезатора частоти з системою цифрового захоплення частоти; на Фіг. 3 - функціональна блок-схема синтезатора частоти з системою цифрового захоплення частоти з модулем керування пам'яті; на Фіг. 4 - функціональна блок-схема синтезатора частот з системою цифрового захоплення частоти з компонентами модуля запам'ятовування; на Фіг. 5 - функціональна блок-схема синтезатора частот з системою цифрового захоплення частоти з компонентами модуля запам'ятовування з додаванням компонента цифрового порівнювання даних; на Фіг. 6. - синтезатор частоти з компонентом вибору частотної модуляції. На Фіг. 1 блок-схема синтезатора частот з ФАПЧ містить подільник частоти 1, фазовий детектор 2, ФНЧ накачки заряду 3, генератор керований напругою (ГКН) 4 і вихідний подільник частоти 5. Синтезатор має опорну частоту Fref, як високостабільне вхідне коливання. На Фіг. 2 функціональна блок-схема синтезатора частоти з системою цифрового захоплення частоти (DPFL). DPFL синтезатор містить подільник частоти N÷1 10, подільник частоти N÷2 11, процесор 6, ЦАП 7, і ГКН 8. Функція DPFL синтезатора полягає у генерації високостабільної вихідної частоти на основі стабільного опорного сигналу частоти f ОП. На Фіг. 3 другий варіант пристрою містить модуль пам'яті (ПЗУ або енергонезалежну пам'ять) 9 в синтезаторі DPFL, який використовується для перетворення лінійних елементів функції для нелінійної функції елемента ГКН 4. На Фіг. 4 функціональна блок-схема синтезатора частоти DPFL містить кінцевий регістр пам'яті 10 і регістр пам'яті верн'є (ноніусний) 11 замість замап'ятовувального елемента 9 на Фіг. 3. Синтезатор частоти DPFL додатково містить кінцевий ЦАП 12 і ЦАП 13, які з'єднані з регістром пам'яті 10 і ноніусної пам'яті 11. Сумуючий підсилювач 14 служить для того, щоб додати або відняти значення вихідної напруги з фіксацією у ЦАП 13 до вихідної напруги ЦАП 13. 1 UA 102570 U 5 10 15 20 25 30 35 40 45 50 55 На Фіг. 5 блок-схема синтезатора з додавання цифрового компаратора 15, що поєднує у своєму складі елементи запам'ятовуючих регістрів, як було зазначено на Фіг. 4. Таке поєднання підвищує швидкодію перетворення сигналів, що надходять від елементів пам'яті 10 та 11. Значення надходить в регістр ЦАП 8 та після перетворення потрапляє в ГКН 4. На Фіг. 6 показано ще одну перевагу синтезатора DPFL, що використовується в FMмодуляції. Коли виконується корекція, перш ніж частота втрачається, утримуючий/записуючий вхідний порт ЦАП регістра тимчасового зберігання 7 встановлений в режимі утримання. При цьому регістр ЦАП 7 не оновлюється і має ту ж адресу в пам'яті, що і ГКН 4 налаштовується на те саме значення. Синтезатор частоти працює наступним чином. Високостабільна опорна частота подається на один з входів фазового детектора 2 або через подільник частоти 1, який виділяє частоту нижче опорної, перш ніж вона потрапляє на вхід фазового детектора 2. Інша частота, яка генерується з ГКН 4 синтезатора частоти, менша за опорну, з виходу подільника частоти 5 подається на інший вхід фазового детектора 2. Функція фазового детектора 2 - генерувати напругу в кількості, пропорційній кількості різниці фаз між двома входами фазового детектора 2, коли опорна частота збільшується чи зменшується. Напруга, що генерується, проходить через фільтр низьких частот (ФНЧ) накачки заряду 3, щоб налаштувати ГКН 4 на генерацію частот, що надходять на вхід фазового детектора 2. В результаті вихідну частоту ГКН 4 фіксують на величині опорної частоти. Фазовий детектор 2 не має вихідної напруги, коли два сигнали збігаються за фазою. Він спирається на ФНЧ накачки заряду 3 для підтримки вхідної напруги ГКН 4. Накачка заряду 3 втрачає свою напругу через струм витоку, що керує ГКН 4, щоб змінити його частоту доки різниця фаз є достатньою для фазового детектора 3 для початку генерування відповідної напруги накачки заряду 3, щоб подати її на орієнтовну частоту. Подільник N÷2 2 виділяє вихідну частоту ГКН 4. Після того як від подільника N÷1 1 надходять сигнали "1" або "0" відносно fОП подільник N÷2 2 коригує вихідну частоту досить точно. Виміряна частота надходить в процесор 6. Для пояснення функцій елемента пам'яті 9 синтезатора частоти DPFL згідно з другим варіантом здійснення відповідно до цієї корисної моделі зазначимо, що синтезатор має робочий діапазон 2,1-8,1 ГГц. Значення цільової частоти, запрограмованої в регістр зберігання 12, передаються на ЦАП 8 регістр тимчасового зберігання 13. Поки ЦАП 8 в регістрі зберігання 12 знаходиться в режимі очікування, вихідні дані ЦАП в регістрі зберігання 13 не будуть змінюватися. Значення частоти записується в регістр ЦАП 8 для управління ГКН 4, що близька до заданої частоти системи. Після встановлення роботи ГКН 8, подільник частоти N÷2 2 починає виділяти вихідну частоту ГКН 4. Якщо подільник частоти N÷2 2 не збігається із значенням у встановлений регістр зберігання 7, до ЦАП 8 надійде нове значення від системи і подільник N÷2 2 повторюватиме процес вимірювання, поки дані подільника N÷2 2 не будуть збігатися з регістром зберігання 7. Це значення в регістрі ЦАП 8 зчитується і потім зберігається у модулі пам'яті 9 зі значенням в регістрі зберігання 7 як адреса пам'яті. Послідовно значення в ЦАП 4 змінюється у відповідності до очікуваної частоти і весь процес перетворення повторюється, поки всі значення частот від 90 МГц до 100 МГц не встановляться і збережуться в модулі пам'яті 9. Синтезатор частоти повинен досягти заданої частоти в той момент, коли програмується запам'ятовуючий регістр 7. Адреса пам'яті 10 має розмір 16 біт і адреса ноніусної пам'яті 11 12 біт, у вищезазначеному робочому діапазоні частот ноніусна пам'ять 11 потребує об'єму 4096 комірок для зберігання кожного значення частоти. Кожне значення частоти, що зберігається в пам'яті 10, відділено від значення 4096 Гц. Об'єм кінцевої пам'яті 60 зменшується до 2442 комірок (по 16 біт) для робочого діапазону частот. 4096 комірок ноніусної пам'яті необхідні для зберігання кожного значення пам'яті. Частотна модуляція може використовуватися, так як напругу модуляції додано до ЦАП 12 і ЦАП 13 відносно модуляційного підсилювача. Такий синтезатор дозволяє збільшити швидкість формування сигналів, оскільки модифікація дозволила зменшити кількість компонентів, що необхідні для генерації вихідних коливань ГКН. Зменшення часу проходження інформаційних сигналів дозволяє підвищити швидкість обміну сигналами між компонентами усієї моделі. Джерела інформації: 1. Рыжков А.В., Попов В.Н. "Синтезаторы частот в технике радиосвязи", М.: Радио и связь, 1991. 2. Южаков В.В. "Малошумящие синтезаторы для РЛС с быстрой перестройкой частоты". Журнал "Зарубежная радиоэлектроника", 1985, 6. М.: Радио и связь. 2 UA 102570 U 3. Патент США US 7609096 "Frequency synthesizer and method for constructing the same", 2009 p. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 Синтезатор з цифровим процесом частотного циклу, що містить подільники частоти N÷1 та N÷2, модулі пам'яті, процесор, генератор, керований напругою, цифро-аналоговий перетворювач, який відрізняється тим, що додатково містить цифровий компаратор, який введено в канал перетворення частоти між вихідними каналами та цифро-аналоговим перетворювачем. 3 UA 102570 U 4 UA 102570 U 5 UA 102570 U Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

Назва патенту англійськоюSynthesizer with a digital frequency loop process

Автори англійськоюHramarchuk Yurii Oleksandrovych, Kobak Mykola Mykolaiovych, Petrenko Viacheslav Petrovych, Slesarenko Serhii Serhiiovych

Назва патенту російськоюСинтезатор с цифровым процессом частотного цикла

Автори російськоюГрамарчук Юрий Александрович, Кобак Николай Николаевич, Петренко Вячеслав Петрович, Слесаренко Сергей Сергеевич

МПК / Мітки

МПК: H03B 19/00

Мітки: синтезатор, процесом, циклу, частотного, цифровим

Код посилання

<a href="https://ua.patents.su/8-102570-sintezator-z-cifrovim-procesom-chastotnogo-ciklu.html" target="_blank" rel="follow" title="База патентів України">Синтезатор з цифровим процесом частотного циклу</a>

Попередній патент: Спосіб лікування собак службових порід з гепатодистрофією

Наступний патент: Спосіб виробництва солоду

Випадковий патент: Застосування ботулінового токсину для профілактики та лікування бромідрозу