Пристрій для сумування тривалостей імпульсів

Номер патенту: 14223

Опубліковано: 25.04.1997

Автори: Кожем'яко Володимир Прокопович, Білан Лариса Валентинівна, Короновський Алім Іванович, Білан Степан Миколайович

Формула / Реферат

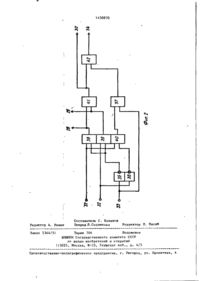

1. Устройство для суммирования длительностей импульсов, содержащее К блоков суммирования, каждый из которых содержит n бистабильных элементов, два элемента запрета, два формирователя импульсов, две группы по n элементов И и две группы по n элементов ИЛИ, причем в каждом j-м (j=1, K) блоке суммирования единичный выход i-го (i=1, n) бистабильного элемента подключен к первому входу i-го элемента И первой группы, соединенного выходом с первым входом (i+1)-го элемента ИЛИ первой группы, выход которого подключен к входу установки в "1" (i+1)-го бистабильного элемента, соединенного нулевым выходом с первым входом (i+1)-го элемента И второй группы, подключенного выходом к первому входу i-го элемента ИЛИ второй группы, выход которого соединен с входом установки в "О" i-го бистабильного элемента, причем выход первого элемента ИЛИ первой группы подключен к входу установки в "1" первого бистабильного элемента, соединенного нулевым выходом с первым входом первого элемента И второй группы, подключенного выходом к входу первого формирователя импульсов, причем вторые входы элементов И первой группы и первый вход первого элемента ИЛИ первой группы соединены с выходом первого элемента запрета, подключенного первым входом к вторым входам с третьего по n-й элементов ИЛИ второй группы и выходу второго формирователя импульсов, соединенного входом с выходом n-го элемента И первой группы, а вторые входы элементов И второй группы и второй вход n-го элемента ИЛИ второй группы подключены к выходу второго элемента запрета, соединенного первым входом с выходом первого формирователя импульсов и вторыми входами с первого по (n-1)-й элементов ИЛИ первой группы, причем в каждом j-м блоке суммирования, за исключением первого блока, выход первого формирователя импульсов подключен к второму входу n-го элемента ИЛИ первой группы, выход второго формирователя импульсов соединен с вторыми входами первого и второго элементов ИЛИ второй группы, вторые входы первого и второго элементов запрета j-го блока суммирования подключены к выходам второго и первого формирователей импульсов (j-1)-го блока суммирования соответственно, а вторые входы первого и второго элементов запрета первого блока суммирования соединены с шинами сложения и вычитания устройства соответственно, отличающееся тем, что, с целью повышения быстродействия и расширения области применения за счет параллельного суммирования или вычитания длительностей импульсов, в негр введен блок формирования длительностей импульсов, а первый блок суммирования дополнительно содержит третью группу из (n-2)/2 элементов И, четвертую группу из четырех элементов И, два элемента НЕ и элемент И-НЕ, при этом блок формирования длительностей импульсов подключен первым и вторым сигнальными входами к первому. и второму импульсным входам устройства, управляющим входом - к входу управления режимами сложения и вычитания устройства, первым и вторым выходами соответственно к первым и вторым входам элементов И третьей группы, первому и второму входам первого элемента И четвертой группы и первому и второму входам элемента И-НЕ, третьим выходом - к входу первого элемента НЕ, а четвертым выходом - к второму входу первого элемента запрета первого блока суммирования, причем в первом блоке суммирования выход первого элемента И четвёртой группы соединен с третьими входами первого и второго элементов ИЛИ первой группы, второй элемент И четвертой группы подключен выходом к второму входу второго элемента ИЛИ второй группы, первым входом - к выходу элемента И-НЕ, а вторым входом - к выходу второго формирователя импульсов и первому входу третьего элемента И четвертой группы, соединенного вторым входом с выходом первого элемента НЕ, а выходом - с вторым входом первого элемента ИЛИ второй группы, при этом четвертый элемент И четвертой группы подключен выходом к второму входу n-го элемента ИЛИ первой группы, первым входом - к выходу первого формирователя импульсов, а вторым входом - к выходу второго элемента НЕ, соединенного входом с шиной вычитания устройства, при этом каждый 1-й [1 £ 1 £ (n-2) = -2] элемент И третьей группы подключен третьим входом к выходу (2-1)-го элемента И первой группы, а выходом - к третьему входу 2 (1+1)-го элемента ИЛИ первой группы.

2. Устройство по п. 1, отличающееся тем, что блок формирования длительностей импульсов содержит четыре элемента И, два элемента ИЛИ и два элемента НЕ, причем первый элемент НЕ подключен входом к управляющему входу блока формирования длительностей импульсов и первому входу первого элемента И, а выходом - к первым входам второго и третьего элементов И, причем второй элемент И соединен вторым входом с первым сигнальным входом блока формирования длительностей импульсов и первым входом четвертого элемента И, а выходом - с первым выходом блока формирования длительностей импульсов и первым входом первого элемента ИЛИ, подключенного вторым входом к выходу третьего элемента И и второму выходу блока формирования длительностей импульсов, а выходом - к первому входу второго элемента ИЛИ, соединенного вторым входом с выходов первого элемента И, второй вход которого подключен к выходу четвертого элемента И, соединенного вторым входом с выходом второго элемента НЕ, подключенного входом к второму входу третьего элемента И и второму сигнальному входу блока формирования длительностей импульсов, а выходы первого и второго элементов ИЛИ соединены соответственно с третьим и четвертым выходами блока формирования длительностей импульсов.

Текст

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЦВМ. Целью изобретения является повышение быстродействия и расширение области при менения за счет параллельного суммирования или вычитания длительностей' импульсов. Устройство содержит К блоков суммирования,каждый из которых содержит п бистабильных элементов, группы элементов ИЛИ,группы элементов И, и формирователи импульсов,элементы запрета, шины сложения,вычитания,переноса, заема.Кроме того,устройство содержит блок формирования длительностей импульсов, импульсные входы, вход управления режимами сложения и вычитания, а первый блок суммирования дополнительно содержит группы элементов И, элемент И-НЕ и два элемента НЕ. Информация н устройстве представляется в единично-нормальном коде. Сложение и вычитание длительностей импульсов может производиться как параллельно, так и последовательно. 1 з.п. ф-лы, 2 ил. s •Л ' • V ' і _ _ 1 1430970 выход 34, поступающий оттуда на шину Изобретение относится к автомати12 сложения, при этом сигнал с выхоке и вычислительной технике и может да элемента 10 запрета через элемент быть использовано в ЦВМ. ИЛИ 5 поступает на вход 3 установки Цель изобретения - повышение быств единичное состояние бистабильного родействия и расширение области приэлемента 2 f , вызывая его установку менения устройства за счет параллельв состояние логической "1", которая ного суммирования или вычитания длипоявляется на единичном выходе, дательностей импульсов. вая разрешение на переключение следуНа фиг. 1 изображена блок-схема ющего бистабильного элемента и т.д. предлагаемого устройства; на фиг.2 схема блока Формирования длительноПоследний бистабильный элемент стей импульсов. 2^ при установке в состояние логической " 1 " дает разрешение на формироваУстройство содержит К блоков 1--1- суммирования, каждый из кото- 15 ние импульса переноса с выхода схемы второго формирователя 9 импульсов, рых содержит п бистабильных элемензтїдо же импульсом все бистабильные тов 2 2^,-2 п с входами 3 и 4 устаэлементы, кроме первого в первой новки 1tв " I1"" и "0 м соответственно, " и "U" первую группу элементов ИЛИ 5, вторую группу элементов ИЛИ 6, первую груп- 20 пу .элементов Й 7, вторую группу элементов И 8, два формирователя 9 импульсов, первый 10 и второй И элегменты запрета, щину 12 сложения, шину 13 вычитания, шину 14 переноса, шину 25 15 заема, блок 16 формирования длительностей импульсов, первый 17 и второй 18 импульсные входы1 и вход 19 управления режимами сложения и вычитания. 30 В первый блок Ц суммирования дополнительно входят третья группа элементов И 20, четвертая группа из элементов Й 21-24, элемент И-НЕ 25 и два элемента НЕ 26 и 27. Блок 16 фор- 3 5 .мирования длительностей импульсов мирования длительностей импульсов, содержит с первого по третий выходы 28-30, сигнальные входы 31 и 32, управляющий вход 33, четвертый выход 34, элементы НЕ 35 и 36, элементы И 40 37-40 и элементьр И И 41 и 42. Л Устройство работает следующим образом. Каждый блок 1, - 1 ^ содержит четное количество бистабильных элементов, 45 т . е . п = 2 і (і » 1,К). Информация в устройстве представляется в единично-нормальном коде. Сложение и вычитание длительностей импульсов может производиться как па50 раллельно, так и последовательно. Для последовательного сложения длительностей импульсов на вход Ї9 устройства подается логический " 0 " , а на первый 17 либо второй 18 входы устройства подают первый импульс, по- „ ступающий на первый 31 или второй 32 входы блока 16 формирования длительностей импульсов и проходящий на его группе, устанавливаются в состояние логического " 0 " воздействием на входы 4 установки в нулевое состояние через элементы ИЛИ 6, при этом длительность £Срм ш , с импульса определяется максимальным временем переключения бистабильных элементов 2 1 - 2 h . Первый t бистабильный элемент 2, не устанавли-* вается в состояние логического 0 . только в том случае, когда входной і" импульс продолжает присутствовать на одном из двух входов Ї 7 или 18 устройства и по окончании времени установки в состояние логической " последнего бистабильного элемента \ первой группы, через время р ьр.мок первый бистабильный элемент 2 1 сле дующей группы перейдет в состояние еей т логической " і " , а первый бистабильный элемент 2, первой группы останется в состоянии логической " I " лишь только в том случае, если где t - длительность импульса на входе 17 или 18 устройства; ^ср ср ~ среднее время срабатывания одного бистабильного элемента. Первый бистабильный элемент %i первой группы остается в состоянии 1 логической "Г , так как с выхода 30 блока 16 на вход первого элемента НЕ 26 поступает сигнал логической "1", который преобразуется в логический 0 и поступает на первый вход третьего элемента И 23, на выходе которого также будет присутствовать лом гический " 0 , поступающий через второй элемент ИЛИ 6 на нулевой вход первого бистабильного элемента 2и 1430970 Через шину J5 заема в нулевое сокоторый, в свою очередь, не перехостояние переходит старший бистабильдит в состояние логического " 0 " . ный элемент второй группы, находящийДля последовательного вычитания длися в состоянии логической " 1 " . тельностей импульсов в устройство Для одновременного сложения двух заносят импульс уменьшаемый. Процесс длительностей импульсов на вход 19 записи импульса уменьшаемого аналоустройства подается логический "О", гичен вышеописанному режиму последоа на первый 17 и второй 18 входы вательного сложения, суммируемые импульсы. Все они постуПри поступлении информации на шипают на входы 31-33 блока 16. В рену 13 вычитания сигнал с выхода э л е зультате на выходе 34 блока 16 будет мента ІЇ запрета поступает на элеменприсутствовать импульс с длительноты И 8 и появляется на выходах тех стью, равной наибольшей длительности ' элементов И 8, на вторые входы котоодного из суммируемых импульсов. рых с нулевых выходов бистабилькых элементов поступает сигнал логической Таким образом, устройство может ' ' I м , т . е . эти бистабильные элементы суммировать длительности импульсов, находятся в состоянии логического "О". совпадающие по передьим фронтам, а Допустим, в декаде в состоянии лосуммирование происходит за время, гической " 1 " находится і бистабильных равное времени импульса с большей 20 элементов 2.,-2. , следовательно, в содлительностью. стоянии логического " 0 " находится Если на первые два входа 17 и 18 п - і бистабильных элементов 21> + 1 - 2 п . устройства одновременно подаются сумС нулевого выхода (і+1)-го бистабильмируемые импульсы, то первых два ного элемента 2j + J через элемент И 8 25 бистабильных элемента 2Т и 2 2 первой сигнал логической " 1 " поступает ч е группы одновременно устанавливаются рез элемент И И 6 на вход 4 установЛ в единичное состояние за счет того, ки в нулевое состояние бистабильного что с двух выходов 28 и 29 блока 16 элемента 2^, вызывая его установку на входы элемента И 21 подаются лов состояние логического " 0 м , т . е . на гические " I й , а с выхода элемента 30 его нулевом выходе появляется логиИ 21 через элементы И И 5 единичный Л ческая п ! п , давая разрешение на песигнал поступает на единичные входы реключение следующего бистабильного 3 первых двух бистабильных элементов элемента 21.! . и т . д . Пртч этом на и 2 г , вызывая их установку в соединичном выходе і т о бистабнльного стояние логической "1", которая появэлемента 2,' поярляется логический *'0" 35 ляется на единичных выходах, давая и т.д. разрешение на переключение следующих двух бистабильных элементов 2 Э и 2 4 . Первый бистабильный элемент 2. при и Единичный сигнал с выхода элемента установке в состояние логического 0 " И 7, первый вход которого подключен разрешает формирование импульса пе40 реноса с выхода схемы первого формик единичному выходу бистабильного рователя импульсов, этим же импульэлемента 2^ поступает на третий вход сом вес бистабильные элементы 2 1 -2 f l второго элемента И 20, сигнал с выхоустанавливаются в состояние логичесда которого через элементы ИЛИ 5 покой " I " воздействием на входы 3 уста- 45 ступает на единичные входы 3 бистановки в единичное состояние через бильных элементов 2 3 и 2 Ф , тем самым элементы И И 6, при этом длительность Л вызывая их установку в состояние лоимпульса определяется максимальным гической " 1 " и т.д. временем переключения. Последний бистабильный элемент 2 П Последний бистабильный элемент 2 п при установке в состояние логической 50 устанавливается в состояние логичес"і" дает разрешение на формирование кой " і " лишь в том случае, если с импульса переноса с выхода второго тины 13 вычитания в этот момент не формирователя 9 импульсов. Этим же подается единичный сигнал. На выходе импульсом все бистабильные элементы второго элемента Н 27 присутствует Е устанавливаются в состояние логичес55 сигнал логической " 1 " , который через кого " 0 " воздействием на входы 4 усчетвертый элемент И 24 и элемент И И Л тановки в нулевое состояние через 5 поступает на единичный вход 3 поэлементы ИЛИ 6, при этом длительность следнего бистабильного элемента 2 to . импульса определяется максимальным 1430970 временем переключения бистабильных элементов. Если на первых двух входах 17 и !8 устройства продолжают присутствовать два импульса, то в состояние логической " 1 " переходит бистабильный элемент следующей группы, а в первой группе остаются в том же единичном состоянии первые бистабильные 10 элементы 21 и 2 2 , так как с выходов 28-30 блока I6 на входы элемента И-НЕ 25 и элемента НЕ 26 подаются сигналы логической "I". На выходах элементов НЕ 26 и И-НЕ 25 появляются 15 логические " 0 " , поступающие через элементы И 23 и 22 и элементы ИЛИ 6 на нулевые входы 4 первых двух бистабильных элементов 2Л и 2., тем самым не вызывая их переключения. В даль20 нейшем процесс сложения происходит аналогичным образом. С момента времени, когда импульс с меньшей длительностью заканчивается, сложение происходит так же, как 25 и сложение при последовательном суммировании, до окончания импульса с большей длительностью. Для параллельного вычитания двух длительностей импульсов на вход 19 30 устройства подают сигнал логической "I", а на первый 17 и второй 18 входы устройства соответственно подают импульс-уменьшаемого и импульс вычитаемого, причем моменты присутствия 35 обоих импульсов должны соответствовать условиям ' 1 Lo где Ці при • при Сі " 1 40 ~ 0, - время присутствия импульса 45 вычитаемого; t 1 ~ время присутствия импульса уменьшаемого. Таким образом, время присутствия вычитаемого импульса не выходит за рамки времени присутствия уменьшаемо- 50 го импульса. Блок 16 на выходе 34 формирует импульс, длительность которого соответствует времени t з = t , - t . присутствия только уменьшаемого импульса. Вре-55 мя присутствия одновременно двух импульсов не учитывается. Если импульсы по передним фронтам не совпадают, то на выходе блока і 6 будет присутствовать два импульса с длительностями, соответственно равными длительности от переднего Фронта уменьшаемого импульса до переднего фронта вычитаемого импульса и от заднего фронта вычитаемого импульса до заднего фронта уменьшаемого импульса, т.е. блок !б вырезает длительность импульса (двух импульсов), полученного в результате вычитания. Полученный импульс поступает на шину сложения и в дальнейшем процесс записи происходит аналогично процессу последовательного суммирования , описанного выше. Таким образом, устройство может последовательно и параллельно суммировать и вычитать длительности импульсов. Блок 16 формирования импульса сложения и вычитания работает следующим образом. В режимах сложения на вход^ЗЗ подается логический "0", а на входы 31 и 32 подаются логические " I м , поступающие через элементы И 38 и 39 (за счет присутствия на выходе элемента НЕ логического "0") на входы элемента ИЛИ 41 и на выходы 28 и 29. С выхода элемента ИЛИ 41 единичный сигнал поступает на выход 30 и через элемент ИЛИ 42 - на выход 34 блока І6. Если присутствует один импульс на одном из двух входов блока 16, то на выходе элемента ИЛИ 41 также будет присутствовать логическая " 1 " . Б режиме параллельного вычитания на вход 32 блока 16 подается логическая "і", поступающая также на вход элемента И 37. С выхода элемента НЕ 35 на вторые выходы первого и второго элементов И 38 и 39 поступает логический "0". Следовательно, на выходе элемента ИЛИ 41 и выходах 28 и 29 присутствует логический "О". Если на выходе 30 присутствует импульс, а на входе 31 импульс не присутствует, то на первый вход элемента И 40 с первого выхода 30 блока J6 и на второй вход с выхода второго элемента НЕ 36 поступает логическая "1". С выхода элемента И 40 через элемент И 37 и второй элемент ИЛИ 42 единичный сигнал поступает на выход 34 блока 16. Если импульсы присутствуют на первых двух входах 31 и 32 блока 16, то на выходе элемента И 40 будет присутствовать логичегкий 430970 1f Tr 0 , который также поступает на" "вы-" ход 34 блока 16. Формула и з о б р е т е н и я , І. Устройство для суммирования длительностей импульсов, содержащее К блоков суммирования, каждый из которых содержит п бистабильных элемен-ю тов, два элемента запрета, два формирователя импупьсов, две группы по и . элементов И и две группы по п элементов ИЛИ, причем в каждом j - м ( j e l . К) блоке суммирования единичный выход 15 і-го (і = 1,п) бистабильного элемента подключен к первому входу і-го элемента И первой группы, соединенного выходом с первым зходом (і+і)~го элемента И И первой группы, выход ко-20 Л торого подключен к входу установки в " 1 " (і-И)-го бистабильного элемента, соединенного нулевым выходом с первым входом (1+1)-го элемента И второй группы, подключенного выходом к пер- 25 вому входу і-го элемента И И второй Л группы, выход которого соединен с входом установки в "О" і-го бистэбильного элемента * причем выход первого элемента И И первой группы под- 30 Л ключей к входу установки в "1 п первого бистабнльного элемента, соединенного нулевым выходом с первым входом первого элемента И второй группы, подключенного выходом к входу'перво- ,с го формирователя импульсов, причем вторые входы элементов И первой группы и первый вход первого элемента И И Л первой группы соединены с РЫХОДОМ первого элемента запрета, подключенАП ного первым входом к вторым входам с третьего по n-й элементов И И втоЛ рой группы и выходу второго' формирователя импульсов, соединенного входом с выходом п-го -элемента И первой группы, а вторые входы элементов И второй группы и второй вход п-го элемента ИЛИ второй группы подключены к выходу второго элемента запрета, соединенного первым входом с выходом первого формирователя импульсов и 50 вторыми входами с первого по (п-1)-й элементов И И первой группы, причем Л в каждом j'-M блоке суммирования, за исключением первого блока, выход первого формирователя импульсов подклю- 55 чен к второму входу п-го элемента И И первой группы, выход второго форЛ мирователя импульсов соединен с вто рыми входами первого и второго элементов И И второй группы, вторые вхоЛ ды первого и второго элементов запрета j - r o блока суммирования тюдкпючены к выходам второго н первого формирователей импульсов ( j - l ) - r o блока суммирования соответственно, а вторые чходы первого и второго элементов запрета первого блока суммирования соединены с шинами сложения и вычитания устройства соответственно, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения области применения за счет параллельного суммирования или вычитания длительностей импульсов, в него введен блок формирования длительностей импульсов, а первый блок суммирования дополнительно содержит третью группу из ( п - 2 ) / 2 элементов И, четвертую группу из четырех элементов И, два элемента НЕ и элемент И-НЕ, при этом блок формирования длительностей импульсов подключен первым и вторым сигнальными входами к первому и второму импульсным входам устройства, управляющим входом - к входу управления режимами сложения и вычитания устройства, первым и вторым выходами ' соответственно к первым и вторым входам элементов И третьей группы, первому и второму входам первого элемента И четвертой группы и первому и второму входам элемента И-НЕ, третьим выходом - к входу первого элемента ' НЕ, а четвертым выходом - к второму входу первого элемента запрета первого блока суммирования, причем в первом блоке суммирования выход первого элемента И четвертой группы соединен с третьими входами первого и второго элементов И И первой группы, второй Л элемент И четвертой группы подключен выходом к второму входу второго элемента И И второй группы, первым вхоЛ дам - к выходу элемента И~НЕ, а вторым входом - к выходу второго формирователя импульсов и первому входу третьего элемента И четвертой группы, соединенного вторым входом с выходом первого элемента НЕ, а выходом - с вторым входом первого элемента И И Л второй группы, при этом четвертый элемент И четвертой группы подключен выходом к второму входу п т о элемента И И первой группы, первым входом Л к выходу первого формирователя импульсов, а вторым входом - к выходу 1430970 второго элемента НЕ, соединенного входом с шиной вычитания устройства, при этом каждый 1-й f l ±Ц ( n - 2 ) » - 2 j элемент И третьей группы подключен третьим входом к выходу (2 - 1 ) - г о элемента И первой группы, а выходом к третьему входу 2*(1+1)-го элемента ИЛИ первой группы. 2. Устройство п о п . 1, о т л и ч а ю щ е е с я тем, что блок формирования длительностей импульсов с о держит четыре элемента И» два элемента ИЛИ и два элемента НЕ, причем пер~ вый элемент НЕ подключен входом к управляющему входу блока формирования длительностей импульсов и первому входу первого элемента И, а выходом к первым входам второго и третьего элементов И, причем второй элемент И соединен вторым входом с первым сиг- 20 нальным входом блока формирования длительностей импульсов и первым э х о 10 дом четвертого элемента И, а выхо- . дом - с первым выходом блока формирования длительностей импульсов н первым входом первого элемента ИЛИ, подключенного вторым входам к выходу третьего элемента И и второму выходу блока формирования длительностей импульсов, а выходом - к первому входу второго элемента ИЛИ, соединенного вторым входом с выходов первого элемента И, второй вход которого подключен к выходу четвертого элемента И, соединенного вторым входом с выходом второго элемента НЕ, подключенного входом к второму входу третьего элемента И и второму сигнальному входу блока формирования длительностей импульсов, а выходы первого и второго элементов ИЛИ соединены соответственно с третьим и четвертым выходами блока формирования длительностей импупьсов. 1430970 Si* I «6 Редактор А. Ревин Заказ 5344/51 Составитель С. Казинов Техред Л.Сердюкова Корректор Л. Патай Тираж 704 Подписное ВІІИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.» д . 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ДивитисяДодаткова інформація

Назва патенту англійськоюSummator of pulse duration

Автори англійськоюKozhemyako Volodymyr Prokopovych, Bilan Stepan Mykolaiovych, Koronovskyi Alim Ivanovych, Bilan Larysa Valentynivna

Назва патенту російськоюУстройство для суммирования продолжительности импульсов

Автори російськоюКожемяко Владимир Прокофьевич, Билан Степан Николаевич, Короновский Алим Иванович, Билан Лариса Валентиновна

МПК / Мітки

МПК: G06G 7/14

Мітки: пристрій, імпульсів, тривалостей, сумування

Код посилання

<a href="https://ua.patents.su/8-14223-pristrijj-dlya-sumuvannya-trivalostejj-impulsiv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для сумування тривалостей імпульсів</a>