Пристрій для складання і віднімання чисел за модулем m системи залишкових класів

Номер патенту: 39417

Опубліковано: 25.02.2009

Автори: Краснобаєв Віктор Анатолійович, Кошман Сергій Олександрович, Яськова Катерина Вікторовна, Сіора Олександр Андрійович

Формула / Реферат

Пристрій для складання і віднімання чисел за модулем m системи залишкових класів, який містить перший (1) та другий (2) входи відповідно першого та другого операндів, перший (3) та другий (4) вхідні регістри, дешифратор (13), першу (14) групу двоходових елементів І, яка містить m (m - це значення, яке дорівнює модулю) елементів І, другу групу триходових елементів І (15), яка містить m елементів І, третю (26) та четверту (29) групи двоходових елементів І, кожна з яких містить n (n=[log2(m-l)]+l, це значення, яке залежить від величини m) елементів І, шифратор (16), вихідний регістр (17), кільцевий регістр зсуву (18), шину запуску пристрою (19), генератор імпульсів (20), перший (21) та другий (23) двоходові елементи І, помножувач частоти (22), шину керування складанням (24), шину керування відніманням (25), суматор (27), вхід подачі модуля m (28), першу двоходову групу елементів АБО (30), яка містить n елементів, приймаючий регістр (31), першу двоходову схему порівняння (32), лічильник (33), вихід пристрою (34), при цьому перший (1) та другий (2) входи пристрою відповідно з'єднані з входами першого (3) та другого (4) вхідних регістрів, перший вихід дешифратора (13) з'єднаний відповідно з першим входом першого елемента першої групи елементів І (14), m-1 вихід дешифратора (13) з'єднаний відповідно з першим входом m-1 елемента першої групи елементів І (14), m вихід дешифратора (13) з'єднаний відповідно з першим входом m елемента першої групи елементів І (14), вихід першого елемента першої групи елементів І (14) з'єднаний з першим входом першого елемента другої групи елементів І (15), вихід m-1 елемента першої групи елементів І (14) з'єднаний відповідно з першим входом m-1 елемента другої групи елементів І (15), вихід m елемента першої групи елементів І (14) з'єднаний відповідно з першим входом m елемента другої групи елементів І (15), виходи першого, m-1 та m елементів другої групи елементів І (15) з'єднані з відповідними входами шифратора (16), вхід кільцевого регістру зсуву (18) з'єднаний з виходом помножувача частоти (22), виходи кільцевого регістру зсуву з'єднані відповідно з другими входами першого, m-1 та m елементів другої групи елементів І (15), шина запуску пристрою (19) з'єднана з входом генератора імпульсів (20), вихід генератора імпульсів (20) з'єднаний з першими входами першого (21) та другого (23) елементів І, вихід першого елемента І (21) з'єднаний з входом помножувача частоти (22), вихід другого елемента І (23) відповідно з'єднаний з входом лічильника (33), вихід лічильника (33) відповідно з'єднаний з першим входом першої схеми порівняння (32), вихід схеми порівняння (32) з'єднаний відповідно з другим входом першого елемента І входом другого елемента І (23), з другими входами першого, m-1, m елементів першої групи елементів І (14) та третіми входами першого, m-1, m елементів другої групи елементів І (15), шина керування складанням (24) з'єднана з першим входом першого та n-го елементів третьої групи елементів І (26), вихід першого та n-го елементів третьої групи елементів І (26) відповідно з'єднаний з першими входами першого та n-го елементів першої групи елементів АБО (30), виходи першого та n-го елементів АБО першої групи елементів АБО (30) з'єднані з входом приймаючого регістру (31), вихід приймаючого регістру (31) з'єднаний з другим входом схеми порівняння (32), шина керування відніманням (25) відповідно з'єднана з першим входом першого та n-го елементів четвертої групи елементів І (29), вихід першого та n-го елементів четвертої групи елементів І (29) з'єднаний відповідно з другим входом першого та n-го елементів першої групи елементів АБО (30), вхід подачі модуля m (28) з'єднаний з першим входом суматора (27), вихід суматора (27) з'єднаний з другими входами першого та n-го елементів четвертої групи елементів І (29), вихід шифратора (16) з'єднаний з входом вихідного регістру (17), вихід вихідного регістру (17) з'єднаний з виходом пристрою (34), який відрізняється тим, що містить другу схему порівняння (5), один елемент АБО (6), п'яту (7), шосту (8), сьому (9), восьму (10) двоходову групу елементів І, кожна з яких містить n елементів І, другу (11) та третю (12) двоходову групу елементів АБО, кожна з яких містить n елементів, при цьому перший вихід першого вхідного регістру (3) з'єднаний з першими входами перших елементів п'ятої (7), шостої (8) групи елементів І та з першим входом першого операнда другої схеми порівняння (5), n-ий вихід першого вхідного регістру (3) з'єднаний з першими входами n-их елементів п'ятої (7), шостої (8) групи елементів І та з n входом першого операнда другої схеми порівняння (5), перший вихід другого вхідного регістру (4) з'єднаний з другими входами перших елементів сьомої (9), восьмої (10) групи елементів І та з першим входом другого операнда схеми порівняння (5), n-ий вихід другого вхідного регістру (4) з'єднаний з другими входами n-их елементів сьомої (9), восьмої (10) групи елементів І та з n входом другого операнда другої схеми порівняння (5), перший вихід другої схеми порівняння (5) з'єднаний з другими входами першого та n-го елемента п'ятої (7) та з першими входами першого та n-го елемента восьмої (10) групи елементів І, другий та третій виходи другої схеми порівняння (5) з'єднаний відповідно з другим та третім входами елемента АБО (6), вихід елемента АБО (6) з'єднаний з другими входами першого та n-го елементів шостої (8) та з першими входами першого та n-го елементів сьомої (9) групи елементів І, виходи першого та n-го елементів сьомої (9) групи елементів І з'єднані відповідно з другими входами першого та n-го елементів другої (11) групи елементів АБО, виходи першого та n-го елементів п'ятої (7) групи елементів І відповідно з'єднані з першими входами першого та n-го елементів другої (11) групи елементів АБО, виходи першого та n-го елементів другої (11) групи елементів АБО відповідно з'єднані з першими та n-ми входами дешифратора (13), виходи першого та n-го елементів восьмої (10) групи елементів І відповідно з'єднані з другими входами першого та n-го елемента третьої (12) групи елементів АБО, виходи першого та n-го елементів шостої (8) групи елементів І з'єднані з першими входами першого та n-го елементів третьої (12) групи елементів АБО, виходи першого та n-го елементів третьої (12) групи елементів АБО відповідно з'єднані з другими входами першого та n-го елементів третьої (26) групи елементів І та з другим та третім входами суматора (27).

Текст

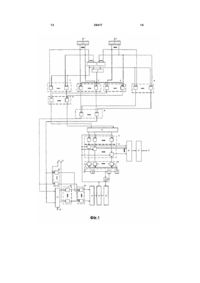

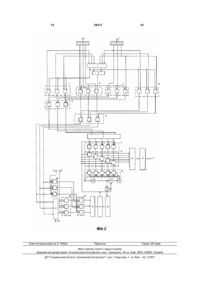

Пристрій для складання і віднімання чисел за модулем m системи залишкових класів, який містить перший (1) та другий (2) входи відповідно першого та другого операндів, перший (3) та другий (4) вхідні регістри, дешифратор (13), першу (14) групу дво ходових елементів І, яка містить m (m - це значення, яке дорівнює модулю) елементів І, другу гр уп у три ходових елементів І (15), яка містить m елементів І, третю (26) та четверту (29) групи дво ходових елементів І, кожна з яких містить n (n=[log2(m-l)]+l, це значення, яке залежить від величини m) елементів І, шифратор (16), ви хідний регістр (17), кільцевий регістр зсуву (18), шин у запуску пристрою (19), генератор імпульсів (20), перший (21) та другий (23) двоходові елементи І, помножувач частоти (22), шин у керування складанням (24), шину керування відніманням (25), суматор (27), вхід подачі модуля m (28), першу двоходову гр упу елементів АБО (30), яка містить n елементів, приймаючий регістр (31), першу дво ходову схему порівняння (32), лічильник (33), вихід пристрою (34), при цьому перший (1) та другий (2) входи пристрою відповідно з'єднані з входами першого (3) та другого (4) вхідних регістрів, перший вихід дешифратора (13) з'єднаний відповідно з першим входом першого елемента першої групи елементів І (14), m-1 вихід дешифратора (13) з'єднаний відповідно з першим входом m-1 елемента першої групи елементів І (14), m вихід деши фратора (13) з'єднаний відповідно з першим входом m елемента першої групи елементів І (14), ви хід першого елемента першої групи елементів І (14) з'єднаний з першим входом першого елемента другої гр упи елементів І (15), вихід m-1 елемента першої групи елементів І (14) з'єднаний відповідно 2 (19) 1 3 39417 4 пристрою (34), який відрізняється тим, що містить другу схему порівняння (5), один елемент АБО (6), п'яту (7), шосту (8), сьому (9), восьму (10) двоходову груп у елементів І, кожна з яких містить n елементів І, другу (11) та третю (12) дво ходову груп у елементів АБО, кожна з яких містить n елементів, при цьому перший вихід першого вхідного регістру (3) з'єднаний з першими входами перших елементів п'ятої (7), шостої (8) гр упи елементів І та з першим входом першого операнда другої схеми порівняння (5), n-ий вихід першого вхідного регістру (3) з'єднаний з першими входами n-их елементів п'ятої (7), шостої (8) групи елементів І та з n входом першого операнда другої схеми порівняння (5), перший вихід другого вхідного регістру (4) з'єднаний з другими входами перших елементів сьомої (9), восьмої (10) групи елементів І та з першим входом другого операнда схеми порівняння (5), n-ий вихід др угого вхідного регістру (4) з'єднаний з другими входами n-их елементів сьомої (9), восьмої (10) групи елементів І та з n входом другого операнда другої схеми порівняння (5), перший вихід др угої схеми порівняння (5) з'єднаний з другими входами першого та n-го елемента п'ятої (7) та з першими входами першого та n-го елемента восьмої (10) групи елементів І, другий та третій виходи другої схеми порівняння (5) з'єднаний відповідно з другим та третім входами елемента АБО (6), вихід елемента АБО (6) з'єднаний з другими входами першого та n-го елементів шостої (8) та з першими входами першого та n-го елементів сьомої (9) групи елементів І, ви ходи першого та n-го елементів сьомої (9) групи елементів І з'єднані відповідно з другими входами першого та n-го елементів другої (11) групи елементів АБО, ви ходи першого та n-го елементів п'ятої (7) групи елементів І відповідно з'єднані з першими входами першого та n-го елементів другої (11) групи елементів АБО, виходи першого та n-го елементів другої (11) групи елементів АБО відповідно з'єднані з першими та n-ми входами дешифратора (13), виходи першого та n-го елементів восьмої (10) групи елементів І відповідно з'єднані з другими входами першого та n-го елемента третьої (12) групи елементів АБО, виходи першого та n-го елементів шостої (8) групи елементів І з'єднані з першими входами першого та n-го елементів третьої (12) групи елементів АБО, виходи першого та n-го елементів третьої (12) групи елементів АБО відповідно з'єднані з другими входами першого та n-го елементів третьої (26) групи елементів І та з другим та третім входами суматора (27). Корисна модель відноситься до обчислювальної техніки і призначена для складання і віднімання чисел за довільним модулем m системи залишкових класів. Відомий пристрій для складання та віднімання чисел по довільному модулю m і, що містить вхідні та ви хідний регістри, прийомний регістр, схему порівняння, кільцевий регістр зсуву, групи елементів АБО та І, елементи АБО та І [а.с. СРСР №1383341, кл G06F7/79, 1979, Б.В. №11, 1988р.]. Недоліком відомого пристрою (аналога) є значний час виконання арифметичних операцій складання і віднімання за модулем m. Це зумовлено тим, що не враховується числова величина другого операнда В. Найбільш близьким за технічною суттю (прототипом) до запропонованої корисної моделі є пристрій для складання і віднімання чисел по модулю р [а.с. СРСР №1168934, кл G06F7/72, Б.В. №27, 1985р.], що містить перший та другий входи відповідно першого та другого операндів, перший та другий вхідні регістри, дешифратор, першу групу дво ходових елементів І, яка містить m (m - це значення яке дорівнює модулю) елементів І, другу груп у трьох ходових елементів І, яка містить m елементів І, третю та четверту групи двоходових елементів І, кожна з яких містить n (n=[log 2(m-1)]+ +1, це значення яке залежить від величини m) елементів І, шифратор, вихідний регістр, кільцевий регістр зсуву, шину запуску пристрою, генератор імпульсів, перший та другий двоходовий елементи І, помножувач частоти, шину управління складанням, шину управління відніманням, суматор, вхід подачі модуля m, першу дво ходову груп у елемен тів АБО, яка містить n елементів, приймаючий регістр, першу дво ходову схему порівняння, лічильник, вихід пристрою, при цьому перший та другий входи пристрою відповідно з'єднані з входами першого та другого вхідних регістрів, перший вихід дешифратора з'єднаний відповідно з першим входом першого елементу першої групи елементів І, m-1 вихід дешифратора з'єднаний відповідно з першим входом m-1 елемента першої групи елементів І, m вихід дешифратора з'єднаний відповідно з першим входом m елемента першої групи елементів І, ви хід першого елементу першої групи елементів І з'єднаний з першим входом першого елементу другої гр упи елементів І, вихід m-1 елемента першої групи елементів І з'єднаний відповідно з першим входом m-1 елемента другої гр упи елементів І, ви хід m елемента першої групи елементів І з'єднаний відповідно з першим входом m елемента другої гр упи елементів І, виходи першого, m-1 та m елементів другої гр упи елементів І з'єднанні з відповідними входами шифратора, вхід кільцевого регістру зсуву з'єднаний з виходом помножувача частоти, виходи кільцевого регістру зсуву з'єднанні відповідно з другими входами першого, m-1 та m елементів другої гр упи елементів І, шина запуску пристрою з'єднана з входом генератора імпульсів, вихід генератора імпульсів з'єднаний з першими входами першого та другого елементів І, ви хід першого елементу І з'єднаний з входом помножувача частоти, ви хід другого елементу І відповідно з'єднаний з входом лічильника, вихід лічильника відповідно з'єднаний з першим входом першої схеми порівняння, вихід схеми порівняння з'єднаний відповідно з другим входом 5 39417 першого елементу І, з др угим входом другого елементу І, з другими входами першого, m-1, m елементів першої групи елементів І та третіми входами першого, m-1, m, елементів другої групи елементів І, шина управління складанням з'єднана з першим входом першого та n-го елементів третьої групи елементів І, вихід першого та n-го елементів третьої групи елементів І відповідно з'єднаний з першими входами першого та n-го елементів першої групи елементів АБО, виходи першого та n-го елементів АБО першої гр упи елементів АБО з'єднані з входом приймаючого регістра, вихід приймаючого регістра з'єднаний з другим входам схеми порівняння, шина управління відніманням відповідно з'єднана з першим входом першого та n-го елементів четвертої гр упи елементів І, ви хід першого та n-го елементів четвертої групи елементів І з'єднаний відповідно з другим входом першого та n-го елементів першої групи елементів АБО, вхід подачі модуля m з'єднаний з першим входом суматора, вихід суматора з'єднаний з другими входами першого та n-го елементів четвертої гр упи елементів І, вихід ши фратора з'єднаний з входом вихідного регістру, ви хід ви хідного регістру з'єднаний з виходом пристрою. Недоліком відомого пристрою (прототипу) є значний час виконання арифметичних операцій складання і віднімання за модулем m. Це зумовлено тим, що не враховується числова величина другого операнда В. В основу корисної моделі поставлено задачу зменшити час виконання операцій складання і віднімання за модулем m; шляхом вибору найменшого з операндів А і В. Це досягається за рахунок попереднього порівняння цих операндів та вибору найменшого з них. Найменше числове значення операндів А чи В використовується в якості другого операнда. Поставлена задача вирішується тим, що у пристрій складання і віднімання чисел за модулем m системи залишкових класів який містить перший та другий входи відповідно першого та другого операндів, перший та другий вхідні регістри, дешифратор, першу гр уп у дво ходових елементів І, яка містить m (m - це значення яке дорівнює модулю) елементів І, другу гр упу трьох ходових елементів І, яка містить m елементів І, третю та четверту групи дво ходових елементів І, кожна з яких містить n (n=[log2(m-1)]+1, це значення яке залежить від величини m) елементів І, шифратор, вихідний регістр, кільцевий регістр зсуву, шину запуску пристрою, генератор імпульсів, перший та другий двоходовий елементи І, помножувач частоти, шину управління складанням, шину управління відніманням, суматор, вхід подачі модуля m, першу двоходову гр упу елементів АБО, яка містить n елементів, приймаючий регістр, першу дво ходову схему порівняння, лічильник, вихід пристрою, при цьому перший та другий входи пристрою відповідно з'єднані з входами першого та другого вхідних регістрів, перший вихід дешифратора з'єднаний відповідно з першим входом першого елементу першої групи елементів І, m-1 ви хід дешифратора з'єднаний відповідно з першим входом m-1 елемента першої групи елементів І, m вихід дешифрато 6 ра з'єднаний відповідно з першим входом m елемента першої групи елементів І, ви хід першого елементу першої гр упи елементів І з'єднаний з першим входом першого елементу другої гр упи елементів І, ви хід m-1 елемента першої групи елементів І з'єднаний відповідно з першим входом m-1 елемента другої групи елементів І, вихід m елемента першої групи елементів І з'єднаний відповідно з першим входом m елемента другої групи елементів І, виходи першого, m-1 та m елементів другої гр упи елементів І з'єднанні з відповідними входами шифратора, вхід кільцевого регістру зсуву з'єднаний з виходом помножувача частоти, виходи кільцевого регістру зсуву з'єднанні відповідно з другими входами першого, m-1 та m елементів другої гр упи елементів І, шина запуску пристрою з'єднана з входом генератора імпульсів, вихід генератора імпульсів з'єднаний з першими входами першого та другого елементів І, вихід першого елементу І з'єднаний з входом помножувача частоти, ви хід другого елементу І відповідно з'єднаний з входом лічильника, вихід лічильника відповідно з'єднаний з першим входом першої схеми порівняння, вихід схеми порівняння з'єднаний відповідно з другим входом першого елементу І, з другим входом другого елементу І, з др угими входами першого, m-1, m елементів першої групи елементів І та третіми входами першого, m-1, m, елементів другої гр упи елементів І, шина управління складанням з'єднана з першим входом першого та n-го елементів третьої групи елементів І, вихід першого та n-го елементів третьої групи елементів І відповідно з'єднаний з першими входами першого та n-го елементів першої групи елементів АБО, ви ходи першого та n-го елементів АБО першої групи елементів АБО з'єднані з входом приймаючого регістра, вихід приймаючого регістра з'єднаний з другим входам схеми порівняння, шина управління відніманням відповідно з'єднана з першим входом першого та n-го елементів четвертої гр упи елементів І, вихід першого та n-го елементів четвертої групи елементів І з'єднаний відповідно з другим входом першого та n-го елементів першої групи елементів АБО, вхід подачі модуля m з'єднаний з першим входом суматора, вихід суматора з'єднаний з другими входами першого та n-го елементів четвертої групи елементів І, вихід ши фратора з'єднаний з входом вихідного регістру, ви хід ви хідного регістру з'єднаний з виходом пристрою, згідно з корисною моделлю, введені другу схему порівняння, один елемент АБО, п'яту, шосту, сьому, восьму двоходову груп у елементів І, кожна з яких містить n елементів І, другу та третю дво ходову гр уп у елементів АБО, кожна з яких містить n елементів, при цьому перший вихід першого вхідного регістру з'єднаний з першими входами перших елементів п'ятої, шостої групи елементів І та з першим входом першого операнда другої схеми порівняння, n-ий вихід першого вхідного регістру з'єднаний з першими входами n-их елементів п'ятої, шостої групи елементів І та з n входом першого операнда другої схеми порівняння, перший вихід другого вхідного регістру з'єднаний з другими входами перших елементів сьомої, восьмої групи елементів І та з першим входом 7 39417 другого операнда схеми порівняння, n-ий вихід другого вхідного регістру з'єднаний з другими входами n-их елементів сьомої, восьмої групи елементів І та з n входом другого операнда другої схеми порівняння, перший вихід другої схеми порівняння з'єднаний з другими входами першого та n-го елемента п'ятої та з першими входами першого та nго елемента восьмої групи елементів І, другий та третій виходи другої схеми порівняння з'єднаний відповідно з другим та третім входами елементу АБО, вихід елементу АБО з'єднаний з другими входами першого та n-го елементів шостої та з першими входами першого та n-го елементів сьомої групи елементів І, виходи першого та n-го елементів сьомої групи елементів І з'єднанні відповідно з другими входами першого та n-го елементів другої гр упи елементів АБО, ви ходи першого та n-го елементів п'ятої групи елементів І відповідно з'єднанні з першими входами першого та n-го елементів другої гр упи елементів АБО, виходи першого та n-го елементів другої гр упи елементів АБО відповідно з'єднанні з першими та nми входами дешифратора, виходи першого та n-го елементів восьмої групи елементів І відповідно з'єднанні з другими входами першого та n-го елемента третьої групи елементів АБО, виходи першого та n-го елементів шостої групи елементів І з'єднанні з першими входами першого та n-го елементів третьої групи елементів АБО, ви ходи першого та n-го елементів третьої групи елементів АБО відповідно з'єднані з другими входами першого та n-го елементів третьої групи елементів І та з другим та третім входами суматора. Введення вказаних ознак дозволяє зменшити час виконання операцій складання і віднімання за модулем m, шляхом попереднього порівняння двох числових значень операндів А і В. На Фіг.1 представлена блок-схема пристрою для складання і віднімання за модулем m системи залишкових класів. Пристрій складання і віднімання за модулем m системи залишкових класів містить перший 1 та другий 2 входи відповідно першого та другого операндів, перший 3 та другий 4 вхідні регістри, другу схему порівняння 5, один елемент АБО 6, п'яту 7, шосту 8, сьому 9, восьму 10 двоходову гр уп у елементів І, кожна з яких містить n елементів І, другу 11 та третю 12 двоходову гр упу елементів АБО, кожна з яких містить n елементів, дешифратор 13, першу 14 групу дво ходових елементів І, яка містить m (m - це значення яке дорівнює модулю) елементів І, другу гр уп у трьох ходови х елементів 115, яка містить m елементів І, третю 26 та четверту 29 гр упи двоходови х елементів І, кожна з яких містить n (n=[log2(m-1)]+1, це значення яке залежить від величини m) елементів І, шифратор 16, вихідний регістр 17, кільцевий регістр зсуву 18, шину запуску пристрою 19, генератор імпульсів 20, перший 21 та другий 23 двоходовий елементи І, помножувач частоти 22, шину управління складанням 24, шину управління відніманням 25, суматор 27, вхід подачі модуля m 28, першу дво ходову груп у елементів АБО 30, яка містить n елементів, приймаючий регістр 31, першу дво ходову схему порівняння 32, лічильник 33, вихід пристрою 34. 8 Перший 1 та другий 2 входи пристрою відповідно з'єднані з входами першого 3 та другого 4 вхідних регістрів. Перший вихід дешифратора 13 з'єднаний відповідно з першим входом першого елементу першої гр упи елементів І 14. m-1 ви хід дешифратора 13 з'єднаний відповідно з першим входом m-1 елемента першої групи елементів І 14. m вихід дешифратора 13 з'єднаний відповідно з першим входом m елемента першої групи елементів І 14. Ви хід першого елементу першої гр упи елементів І 14 з'єднаний з першим входом першого елементу другої групи елементів 115. Вихід m-1 елемента першої групи елементів І 14 з'єднаний відповідно з першим входом m-1 елемента другої групи елементів І 15. Вихід m елемента першої групи елементів І 14 з'єднаний відповідно з першим входом m елемента другої групи елементів І 15. Виходи першого, m-1 та m елементів другої групи елементів 115 з'єднані з відповідними входами шифратора 16. Вхід кільцевого регістру зсуву 18 з'єднаний з виходом помножувача частоти 22. Виходи кільцевого регістру зсуву з'єднанні відповідно з другими входами першого, m-1 та m елементів другої групи елементів І 15. Шина запуску пристрою 19 з'єднана з входом генератора імпульсів 20. Вихід генератора імпульсів 20 з'єднаний з першими входами першого 21 та другого 23 елементів І. Вихід першого елементу І 21 з'єднаний з входом помножувача частоти 22. Вихід другого елементу І (23) відповідно з'єднаний з входом лічильника 33. Вихід лічильника 33 відповідно з'єднаний з першим входом першої схеми порівняння 32. Вихід схеми порівняння 32 з'єднаний відповідно з другим входом першого елементу 1 21, з другим входом другого елементу І 23, з другими входами першого, m-1, m елементів першої групи елементів І 14 та третіми входами першого, m-1, m, елементів другої гр упи елементів 115. Шина управління складанням 24 з'єднана з першим входом першого та n-го елементів третьої групи елементів І 26. Вихід першого та n-го елементів третьої групи елементів І 26 відповідно з'єднаний з першими входами першого та n-го елементів першої групи елементів АБО 30. Виходи першого та nго елементів АБО першої групи елементів АБО 30 з'єднані з входом приймаючого регістра 31. Вихід приймаючого регістра 31 з'єднаний з другим входам схеми порівняння 32. Шина управління відніманням 25 відповідно з'єднана з першим входом першого та n-го елементів четвертої групи елементів І 29. Вихід першого та n-го елементів четвертої гр упи елементів І 29 з'єднаний відповідно з другим входом першого та n-го елементів першої групи елементів АБО 30. Вхід подачі модуля m 28 з'єднаний з першим входом суматора 27. Вихід суматора 27 з'єднаний з другими входами першого та n-го елементів четвертої гр упи елементів І 29. Вихід ши фратора 16 з'єднаний з входом вихідного регістру 17. Вихід вихідного регістру 17 з'єднаний з виходом пристрою 34. Перший вихід першого вхідного регістру 3 з'єднаний з першими входами перших елементів п'ятої 7, шостої 8 групи елементів І та з першим входом першого операнда другої схеми порівняння 5. n-ий вихід першого вхідного регістру 3 з'єднаний з першими входами n-их еле 9 39417 ментів п'ятої 7, шостої 8 групи елементів І та з n входом першого операнда другої схеми порівняння 5. Перший вихід другого вхідного регістру 4 з'єднаний з другими входами перших елементів сьомої 9, восьмої 10 групи елементів І та з першим входом другого операнда схеми порівняння 5. n-ий вихід др угого вхідного регістру 4 з'єднаний з другими входами n-их елементів сьомої 9, восьмої 10 групи елементів І та з n входом другого операнда другої схеми порівняння 5. Перший вихід другої схеми порівняння 5 з'єднаний з другими входами першого та n-го елемента п'ятої 7 та з першими входами першого та n-го елемента восьмої 10 групи елементів І. Другий та третій виходи другої схеми порівняння 5 з'єднаний відповідно з другим та третім входами елементу АБО 6. Ви хід елементу АБО 6 з'єднаний з другими входами першого та n-го елементів шостої 8 та з першими входами першого та n-го елементів сьомої 9 групи елементів І. Ви ходи першого та n-го елементів сьомої 9 групи елементів І з'єднанні відповідно з другими входами першого та n-го елементів другої 11 гр упи елементів АБО. Ви ходи першого та n-го елементів п'ятої 7 групи елементів І відповідно з'єднанні з першими входами першого та n-го елементів другої 11 групи елементів АБО. Виходи першого та nго елементів другої 11 групи елементів АБО відповідно з'єднанні з першими та n-ми входами дешифратора 13. Виходи першого та n-го елементів восьмої 10 групи елементів І відповідно з'єднанні з другими входами першого та n-го елемента третьої 12 групи елементів АБО. Ви ходи першого та n-го елементів шостої 8 гр упи елементів І з'єднанні з першими входами першого та n-го елементів третьої 12 групи елементів АБО. Ви ходи першого та n-го елементів третьої 12 групи елементів АБО відповідно з'єднані з другими входами першого та n-го елементів третьої 26 групи елементів І та з другим та третім входами суматора 27. Друга схема порівняння 5 порівнює значення операндів А та В, та на виходах видає такі сигнали: на першому виході присутній сигнал А>В, на другому виході А=В, на третьому А

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for addition and subtraction of numbers by module m of system of residual classes

Автори англійськоюYaskova Kateryna Viktorivna, Koshman Serhii Oleksandrovych, Siora Oleksandr Andriiovych, Krasnobaiev Viktor Anatoliiovych

Назва патенту російськоюУстройство для сложения и вычитания чисел по модулю m системы остаточных классов

Автори російськоюЯськова Катерина Викторовна, Кошман Сергей Александрович, Сиора Александр Андреевич, Краснобаев Виктор Анатольевич

МПК / Мітки

МПК: G06F 7/00

Мітки: модулем, складання, залишкових, класів, пристрій, чисел, системі, віднімання

Код посилання

<a href="https://ua.patents.su/8-39417-pristrijj-dlya-skladannya-i-vidnimannya-chisel-za-modulem-m-sistemi-zalishkovikh-klasiv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для складання і віднімання чисел за модулем m системи залишкових класів</a>

Попередній патент: Спосіб виготовлення пінополістирольних плит

Наступний патент: Пристрій для визначення траєкторії сегментації ембріона

Випадковий патент: Дозиметричний інгалятор для альбутеролу та дозуюча інгаляційна система