Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів

Формула / Реферат

Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів, що містить блоки регістрів діленого, дільника та суматори, який відрізняється тим, що пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподільником імпульсів, першим блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим елементом АБО пристрою, блоком допоміжних peгістрів, другими елементами АБО пристрою, блоком елементів І, другим блоком модульних дільників, блоками перших, других, третіх, четвертих та п'ятих елементів АБО, блоком модульних множників по модулях системи, блоком модульних суматорів по модулях системи, вхідною шиною пристрою, блоком шин констант по модулях системи, причому виходи регістрів блока регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх перших модульних дільників, другі входи яких з'єднані із виходами регістрів блока регістрів дільника, починаючи із першого по (к-1)-й, а їх треті входи та другий вхід другого елемента і пристрою зв’язані із першим виходом розподільника імпульсів, а перший вхід другого елемента І пристрою підключений до виходу k-го регістра блока регістрів діленого, вихід другого елемента І пристрою зв’язаний із другим входом першого елемента АБО пристрою, перший вхід якого з'єднаний із виходом k–го модульного суматора, а вихід першого елемента АБО пристрою підключений до входу к-го регістра блока регістрів результату, вихід якого зв’язаний із другим входом к-го модульного суматора, виходи перших модульних дільників, починаючи із першого по (к-1)-й, підключені до входів своїх регістрів блока регістрів результату та до входів своїх регістрів блока допоміжних регістрів, причому до першого регістра безпосередньо, а до інших - через другі входи других елементів АБО пристрою, перші входи яких з'єднані із виходами своїх модульних суматорів, вихід першого регістра блока допоміжних регістрів числа зв’язаний з першим входом суматора другого регістра блока допоміжних регістрів, а виходи регістрів блока допоміжних регістрів, починаючи з другого регістра, з'єднані із другими входами своїх суматорів, виходи регістрів блока допоміжних регістрів, починаючи з другого по (к-1)-й включно, підключені до перших входів своїх дільників, другі входи котрих зв’язані із виходами своїх елементів І, перші входи яких з'єднані із шинами блока шин констант, а другі входи - із відповідними виходами розподільника імпульсів та входами скиду попередніх регістрів блока допоміжних регістрів, другий вхід другого дільника підключений безпосередньо до другого входу третього множника, а другі входи дільників другого блока дільників, починаючи із третього, підключені до других входів наступних множників через другі елементи АБО, треті входи дільників другого блока дільників зв’язані із відповідним виходами розподільника імпульсів, а виходи дільників другого блока дільників з'єднані із першими входами наступних множників, причому другий дільник безпосередньо, а всі наступні - через перші елементи АБО, треті входи множників приєднані до відповідних виходів розподільника імпульсів, причому третій множник безпосередньо, а всі наступні - через треті елементи АБО, вихід першого регістра блока допоміжних регістрів також зв’язаний із першими входами суматорів, починаючи із третього по к-й, через перші входи четвертих елементів АБО, виходи суматорів, починаючи із другого по к-й, з'єднані із входами своїх регістрів блока допоміжних, перші входи суматорів, починаючи їз третього по к-й, підключені до виходів відповідних множників, треті входи яких – для другого суматора безпосередньо, а для всіх наступних через п'яті елементи АБО приєднані до відповідних виходів розподільника імпульсів, вхід якого зв’язаний із виходом елемента І, перший вхід якого підключений до вхідної шини пристрою, а другий - до виходу генератора тактових імпульсів.

Текст

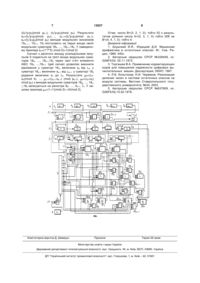

Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів, що містить блоки регістрів діленого, дільника та суматори, який відрізняється тим, що пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподільником імпульсів, першим блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим елементом АБО пристрою, блоком допоміжних peгістрів, другими елементами АБО пристрою, блоком елементів І, другим блоком модульних дільників, блоками перших, других, третіх, четвертих та п'ятих елементів АБО, блоком модульних множників по модулях системи, блоком модульних суматорів по модулях системи, вхідною шиною пристрою, блоком шин констант по модулях системи, причому виходи регістрів блока регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх перших модульних дільників, другі входи яких з'єднані із виходами регістрів блока регістрів дільника, починаючи із першого по (к-1)-й, а їх треті входи та другий вхід другого елемента і пристрою зв’язані із першим виходом розподільника імпульсів, а перший вхід другого елемента І пристрою підключений до виходу k-го регістра блока регістрів діленого, вихід другого елемента І пристрою зв’язаний із другим входом першого елемента АБО пристрою, перший вхід якого з'єднаний із виходом k–го модульного суматора, а вихід першого елемента АБО пристрою підключений до входу к-го регістра блока регістрів результату, вихід якого зв’язаний із другим входом к-го модульного суматора, виходи перших модульних дільників, починаючи із першого по (к-1)-й, підключені до входів своїх регістрів блока регістрів результату та до входів своїх регістрів блока допоміжних регістрів, причому до першого регістра безпосередньо, а 2 (19) 1 3 Корисна модель відноситься до автоматики та обчислювальній техніки і може бути використана для оброблення даних у схемах цифрової автоматики та цифрових обчислювальних машинах, що працюють в системі залишкових класів (СЗК). Системою обчислення в СЗК називається система обчислення [1], в якій число А представляється у вигляді набору найменших залишків по модулях р1, р2, ..., рк, тобто A=[A(mod p1), A(mod р2), ..., А(mod рк)] або А=( 1, 2, ..., k), де 1=А(mod pi). При цьому, якщо числа рі прості, то представлення числа А є єдиним, а об'єм діапазону (0, М] чисел дорівнює М=p1p2…рк. Надалі розглядаються саме такі числа. До переваг СЗК відносять максимальний паралелизм при виконанні операцій по обробці інформації. Але виникають значні труднощі при реалізації ділення на число, що кратне одному із модулів системи, бо виникає невизначеність типу 0/0. Відомий пристрій для перетворювання коду із СЗК у поліадичний код містить в собі вхідний регістр, суматори, елементи 1, АБО [2]. Недоліком цього пристрою є значна кількість обладнання. Недоліком пристрою для перетворювання коду із СЗК у поліадичний код [3], що містить в собі регістри, суматори, елементи 1, АБО, шифратори, є його невисока швидкодія, обумовлена тим, що для отримання результату порівняння необхідно витратити значну кількість модульних операцій. Пристрій для реалізації ділення чисел у СЗК [4] визначає цифри частки, крім цифр по модулях системи, на які виконується ділення. Для визначення останніх пристрій потребує розширення набору модулів з використанням досить складних операцій та устаткування та надає лише деякі часткові результати. Найбільш близькім по технічній суттєвості до корисної моделі є пристрій для перетворювання коду із СЗК у поліадичний код [5], що містить в собі розряди регістру числа, суматори, функціональні перетворювачі та шифратори, причому вихід першого розряду регістра числа пов'язаний із третім входом свого суматора, а виходи розрядів регістру числа, починаючи з другого розряду, з'єднані із першими входами своїх суматорів. Недоліком цього пристрою, який має по відношенню до пристроїв [2] та [3] підвищену швидкодію та меншу кількість обладнання, є те, що цей пристрій не має можливості ділення числа на дільник, кратний одному із модулів. В основу корисної моделі поставлено задачу: пристрій, функціонуючий у системі залишкових класів, шляхом введення додаткових елементів та встановлення відповідних зв'язків між елементами пристрою забезпечити можливість ділення числа на дільник, кратний одному із модулів. Для цього пристрій додатково устаткований генератором тактових імпульсів, першим елементом І пристрою, розподільником імпульсів, першим блоком модульних дільників, другим елементом І пристрою, блоком регістрів результату, першим еле 13027 4 ментом АБО пристрою, блоком допоміжних регістрів, другими елементами АБО пристрою, блоком елементів І, другим блоком модульних дільників, блоками перших, других, третіх, четвертих та п'ятих елементів АБО, блоком модульних множників по модулях Системи, блоком модульних суматорів по модулях системи, вхідною шиною пристрою, блоком шин констант по модулях системи. При цьому виходи регістрів блоку регістрів діленого, починаючи із першого по (к-1)-й, підключені до перших входів своїх перших модульних дільників другі входи яких з'єднані із виходами регістрів блоку регістрів дільника, починаючи із першого по (к1)-й, а їх треті входи та другий вхід другого елементу І пристрою пов’язані із першим виходом розподільника імпульсів, а перший вхід другого елементу І пристрою підключений до виходу k-гo регістру блоку регістрів діленого, вихід другого елементу І пристрою пов'язаний із другим входом першого елементу АБО пристрою, перший вхід якого з'єднаний із виходом k-гo модульного суматора, а вихід першого елементу АБО пристрою підключений до входу k-гo регістру блоку регістрів результату, вихід якого пов'язаний із другим входом k-гo модульного суматору, виходи перших модульних дільників, починаючи із першого по (к1)-й, підключені до входів своїх регістрів блоку регістрів результату та до входів своїх регістрів блоку допоміжних регістрів, причому до першого регістру безпосередньо, а до інших – через другі входи других елементів АБО пристрою, перші входи яких з'єднані із виходами своїх модульних суматорів, вихід першого регістру блоку допоміжних регістрів числа пов'язаний із першим входом суматора другого регістру блоку допоміжних регістрів, а виходи регістрів блоку допоміжних регістрів, починаючи з другого регістру, з'єднані із другими входами своїх суматорів, виходи регістрів блоку допоміжних регістрів, починаючи з другого по (к-1)-й включно, підключені до перших входів своїх дільників, другі входи котрих пов'язані із виходами своїх елементів І, перші входи яких з'єднаю із шинами блоку шин констант, а другі входи - із відповідними виходами розподільника імпульсів та входами скиду попередніх регістрів блоку допоміжних регістрів, другий вхід другого дільника підключений безпосередньо до другого входу третього множника, а другі входе дільників другого блоку дільників, починаючи із третього, підключені до других входів наступних множників через другі елементи АБО, треті входи дільників другого блоку дільників пов'язані із відповідними виходами розподільника імпульсів, а виходи дільників другого блоку дільників з'єднані із першими входами наступних множників, причому другий дільник безпосередньо, а всі наступні - через перші елементи АБО, треті входи множників приєднані до відповідних виходів розподільника імпульсів, причому третій множник безпосередньо, а всі наступні - через треті елементи АБО, вихід першого регістру блоку допоміжних регістрів також пов'язаний із першими входами суматорів, починаючи із третього по к-й, через 5 перші входи четвертих елементів АБО, виходи суматорів, починаючи із другого по к-й, з'єднані із входами своїх регістрів блоку допоміжних, перші входи суматорів, починаючи їх третього по к-й, підключені до виходів відповідних множників, треті входи яких – для другого суматора безпосередньо, а для всіх наступних через п'яті елементи АБО приєднані до відповідних виходів розподільника імпульсів, вхід якого пов'язаний із виходом елементу І, перший вхід якого підключений до вхідної шини пристрою, а другий - до виходу генератора тактових імпульсів. На кресленні зображена функціональна схема пристрою. Пристрій містить генератор тактових імпульсів 1, перший елемент І пристрою 2, розподільник імпульсів 3, блок 4 регістрів 41, 42, 43,...,4к-1, 4к числа А=( 1, 2, 3, ..., к-1, k) для залишків 1, 2, 3, ..., к-1, к відповідно по модулях системи р1, р2, р3, …, рк-1, рк, блок модульних дільників 51, 52, 53,..., 5к1, другий елемент І пристрою 6, блок 7 регістрів 71, 72, 73, ... 7к-1, 7к результату, перший елемент АБО пристрою 8, блок 9 допоміжних регістрів 91, 92, 93,..., 9к-1, другі елементи АБО пристрою 102, 103,…,10к-1, блок елементів І 112, 113,...,11к-1, блок модульних дільників 122, 123, …, 12k-1, відповідно по модулях системи p2, р3, …, рk-1, блок перших елементів АБО 133, …, 13к-1 відповідно по модулях системи р3, …, рk-1, блок других елементів АБО 143, ..., 14к-1 відповідно по модулях системи р3, …, рk-1, блок модульних множників 153,..., 15к-1, 15к, відповідно по модулях системи р3, …, рk-1, pk, блок третіх елементів АБО 163, ..., 16к-1 відповідно по модулях системи р3, …, рk-1, блок четвертих елементів АБО 173, ..., 17к відповідно по модулях системи р3, …, pk блок модульних суматорів 182,183, ...,18к-1, 18к відповідно по модулях системи p2, р3, …, рk-1, pk блок п'ятих елементів АБО 192, 193, ..., 19к-1 відповідно по модулях системи p2, р3, …, рk-1, вхідну 20 шину пристрою, блок шин констант 212, 213, ...,21к-1 відповідно по модулях системи p2, р3, …, pk, блок 22 регістрів 221, 222, 223, ..., 22к-1, 22к числа В=( 1, 2, 3, ..., к-1, к) для залишків 1, 2, 3, ..., к-1, к відповідно по модулях системи р1, p2, р3, …, рk-1, pk. При цьому порядок розташування модулів p1, р2, …, рk-1 вільний, але модуль рк, якому кратний дільник, повинен бути останнім. Роботу пристрою розглянемо для модулів p1=7; р2=5, р3=3, р4=2. Пристрій працює наступним чином. До моменту початку ділення на регістрах 41, 42, 43,...,4к-1, 4к написане число А=( 1, 2, 3, ..., к1, k). Нехай А=208, тобто 1=5, 2=3, 3=1, 4=0. На регістрах 221, 222, 223, ...,22к записане число В=( 1, 2, 3, ..., к-1, к). Нехай В=4, тобто 1=4, 2=4, 3=1, 4=0. Після включення сигналом по шині 20 здійснюється подача через елемент І 2 сигналу на вхід розподільника імпульсів 3. Сигнал з першого виходу розподільника імпульсів 3 поступає на треті входи модульних дільників 51, 52, 53,..., 5к-1, дозволяючи виконання формального ділення 1, 2, 3 на 1, 2, 3, 1=( 1/ 1)(mod 7) =(5/4) (mod 13027 6 7)=3(mod 7), 2=( 2/ 2) (mod 5)=(3/4) (mod 5)=2 (mod 5), 3=( 3/ 3) (mod 3)=(1/1) (mod 3) = 1 (mod 3) записується відповідно на допоміжні регистри 91, 92, 93 та у вигляді 1 = 3 (mod 7), 2=2(mod 5), 3 = 1(mod 3) на регістри 71, 72, 73 результату. Сигнал з другого виходу розподільника імпульсів 3 поступає на треті входи модульних суматорів 182, 183, ...,18к-1, 18к, дозволяючи виконання віднімання залишку 1 від залишків 2, 3, ..., к-1 та додання залишку 1 до залишу к відповідно по модулях системи р2, р3, …, рк-1, рк. Результати 2=( 2- 1), ..., к-і=( к-1- 1) з виходів модульних суматорів 182, 183, ... 18к-1 записуються на регістри 92, 93, ..., 9к-1. Результат к=( к+ 1) записується на регистр 7к. Для наведеного числа 2=(2-3) (mod 5), 3=(1-0) (mod 3), 4=(0+1) (mod 2),тобто 2=4, 3=1, 4=1. Наступний сигнал з третього виходу розподільника імпульсів 3 здійснює скид регістру 91 та подається на другий вхід елементу І 112, дозволяючи подачу константи р1 на другий вхід дільника 112 та на другий вхід множника 153. Наступний сигнал з четвертого виходу розподільника імпульсів 3 подається на третій вхід дільника 122, дозволяючи виконання модульної операції ( 2/p1)(mod р2). Результат t2=( 2/p1)(mod р2)=(4/7) (mod 5)=2 (mod 5) з виходу 122 подасться на перші входи модульних множників 153,..., 15к-1, 15к. Сигнал з п'ятого виходу розподільника імпульсів 3 подасться на треті входи модульних множників 153,..., 15к1, 15к, завдяки чому виконуються модульні операції (t2*p1)(mod р3), ..., (t2*p1)(mod рк-1), (t2*pi)(mod pk). Результати r3=(t2*p1)(mod р3), … rk-1=(t2*p1)(mod р3), rk=(t2*p1)(mod рk) з виходів модульних множників 153,..., 15к-1, 15к поступають на перші входи своїх модульних суматорів 183, ...,18к-1, 18к. У наведеному прикладі r3=(2*7) (mod 3)=2 (mod 3), r4 = (2*7) (mod 2)=0 (mod 2). Сигнал з шостого виходу розподільника імпульсів 3 подасться на треті входи модульних суматорів 183, ...,18к-1, 18к через свої п'яті елементи АБО 192, 193, ..., 19к-1. Цей сигнал дозволяє виконати віднімання у суматорі 183, величини r3 від 3, у суматорі 18k-1 величини rk-1 від k1, у суматорі 18k додання величини rk до k. Результати 3=( 3-r3)(mod 3), …, k-1=( k-1-rk-1)(mod pk1), k=( k+rk)(mod pk) виходів модульних суматорів 183, ...,18к-1, 18к записуються на регистри 93,..., 9к-1, 7k. У наведеному прикладі 3=(1-2)(mod 3)=2(mod 3), 4=(1+0)(mod 2)=1(mod 2) Наступний сигнал з сьомого виходу розподільника імпульсів 3 здійснює скид регістру 92 та подається на другий вхід елементу І 113, дозволяючи подачу константи р1р2 на другий вхід дільника 123 та на другий вхід множника 154. Наступний сигнал з восьмого виходу розподільника імпульсів 3 подається на третій вхід дільника 12з, дозволяючи виконання модульної операції ( 3/p1р2)(mob p3). Результат t3=( 3/p1р2)(mob p3), а у наведеному прикладі t3=(2/7*5)(mod 3)=l(mod 3) з виходу 123 подається на перші входи модульних множників 154,..., 15к-1, 15к. Сигнал з дев'ятого виходу розподільника імпульсів 3 подається на треті входи модульних множників 154,..., 15к-1, 15к, завдяки чому виконуються модульні операції (t3*p1p2)(mod р4), ..., 7 13027 ((t3*p1p2)(mod рk-1), (t3*p1p2)(mod рk). Результати s4=(t3*p1p2)(mod р4),…, sk-1=(t3*p1p2)(mod рk-1), sk=(t3*p1p2)(mod рk) виходів модульних множників 154,..., 15к-1, 15к поступають на перші входи своїх модульних суматорів 184, ..., 18к-1,18к. У наведеному прикладі s4=(1*7*5) (mod 2)=1(mod 2) Сигнал з десятого виходу розподільника імпульсів З подається на треті входи модульних суматорів 184, ..., 18к-1,18к через свої п’яті елементи АБО 193, ...,19к-1. Цей сигнал дозволяє виконати віднімання у суматорі 184, величини s4 від 4, у суматорі 18k-1 величини sk-1 від k-1, у суматорі 18k додання величини sк до к. Результати 4=( 4s4)(mod 4), ..., к-1=( k-1-sk-1) (mod pk-1), k=( k+sk) (mod pk) з виходів модульних суматорів 184, ..., 18к1,18к записуються на регистри 94, …, 9к-1, 7к. У нашому прикладі 4=(1+1)(mob 2)–=0(mod 2). Комп’ютерна верстка Д. Шеверун 8 Отже, число В=(3, 2, 1, 0), тобто 52 є результатом ділення числа А=(5, 3, 1, 0) тобто 208 на В=(4, 4, 1, 0), тобто 4. Джерела інформації 1. Акушский И.Я., Юдицкий Д.И. Машинная арифметика в остаточных классах- М.: Сов. Радио, 1968. 440с. 2. Авторське свідоцтво СРСР №328448, кл. G06F5/02, 02.11.1972. 3. Торгашев В.А. Применение корректирующих кодов для повышения надежности цифровых вычислительных машин. Диссертация, ЛИАП, 1967. 4. Л.Б. Копыткоаа, Н.И. Червяков. Реализация деления чисел в системе остаточных классов на модули системы. Вестник Ставропольского государственного университета, №34, 2003. 5. Авторське свідоцтво СРСР №637809, кл. G06F5/02,15.52.1978. Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for dividing a number by a divisor that is a multiple of one of the number residue modules, by using residue arithmetic

Назва патенту російськоюУстройство для деления числа на делитель, кратный одному из модулей при определении остатка числа, с помощью арифметики в остаточных классах

МПК / Мітки

Мітки: кратний, класів, дільник, системі, модулів, ділення, одному, залишкових, чисел, пристрій

Код посилання

<a href="https://ua.patents.su/4-13027-pristrijj-dlya-dilennya-chisel-u-sistemi-zalishkovikh-klasiv-na-dilnik-kratnijj-odnomu-iz-moduliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для ділення чисел у системі залишкових класів на дільник, кратний одному із модулів</a>

Попередній патент: В’яжуче

Наступний патент: Спосіб консервації каталізатора

Випадковий патент: Спосіб медичної реабілітації хворих на виразкову хворобу дванадцятипалої кишки, поєднану з хронічним безкам'яним холециститом