Багатофазний пристрій для формування імпульсів синхронізації

Номер патенту: 114744

Опубліковано: 25.07.2017

Автори: Буров Олексій Миколайович, Шитов Олександр Леонідович

Формула / Реферат

1. Багатофазний пристрій для формування імпульсів синхронізації, що містить послідовно з'єднані ![]() -канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор і

-канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор і ![]() -фазний дільник частоти, який відрізняється тим, що додатково введені

-фазний дільник частоти, який відрізняється тим, що додатково введені ![]() двійкових лічильників,

двійкових лічильників, ![]() -фазний датчик напруги, цифро-аналоговий перетворювач, формувач функції і вузол скидання, причому кожен з

-фазний датчик напруги, цифро-аналоговий перетворювач, формувач функції і вузол скидання, причому кожен з ![]() двійкових лічильників з'єднаний лічильним входом з відповідним виходом

двійкових лічильників з'єднаний лічильним входом з відповідним виходом ![]() -фазного дільника частоти, а виходом старшого розряду - з управляючим входом відповідного каналу

-фазного дільника частоти, а виходом старшого розряду - з управляючим входом відповідного каналу ![]() -канального фазового детектора, а вихід

-канального фазового детектора, а вихід ![]() -фазного датчика напруги з'єднаний з першим додатковим входом суматора і входом опорної напруги цифро-аналогового перетворювача, вихід якого з'єднаний з другим додатковим входом суматора, крім того, формувач функції з'єднаний входами з виходом керованого генератора і з виходами розрядів принаймні першого двійкового лічильника, а цифровим виходом - з цифровим входом цифро-аналогового перетворювача, вузол скидання з'єднаний входами з виходами розрядів принаймні першого двійкового лічильника і з цифровим виходом формувача функції, крім того, виходи вузла скидання з'єднані з входами установки в нуль відповідних двійкових лічильників з другого по

-фазного датчика напруги з'єднаний з першим додатковим входом суматора і входом опорної напруги цифро-аналогового перетворювача, вихід якого з'єднаний з другим додатковим входом суматора, крім того, формувач функції з'єднаний входами з виходом керованого генератора і з виходами розрядів принаймні першого двійкового лічильника, а цифровим виходом - з цифровим входом цифро-аналогового перетворювача, вузол скидання з'єднаний входами з виходами розрядів принаймні першого двійкового лічильника і з цифровим виходом формувача функції, крім того, виходи вузла скидання з'єднані з входами установки в нуль відповідних двійкових лічильників з другого по ![]() -ний.

-ний.

2. Багатофазний пристрій за п. 1, який відрізняється тим, що ![]() -фазний датчик напруги виконаний у вигляді послідовно з'єднаних додаткових суматора і елемента вибірки-зберігання, при цьому вхід додаткового суматора з'єднаний з виходом

-фазний датчик напруги виконаний у вигляді послідовно з'єднаних додаткових суматора і елемента вибірки-зберігання, при цьому вхід додаткового суматора з'єднаний з виходом ![]() -канального фазового детектора.

-канального фазового детектора.

3. Багатофазний пристрій за будь яким з пп. 1-2, який відрізняється тим, що формувач функції виконаний у вигляді одновібратора, вхід якого з'єднаний принаймні з виходом старшого розряду першого двійкового лічильника, і додатково введеного двійкового лічильника, у якому вхід установки в нуль з'єднаний з виходом одновібратора, лічильний вхід з'єднаний з виходом керованого генератора, причому лічильний вхід і виходи розрядів є цифровим виходом формувача функцій.

4. Багатофазний пристрій за будь яким з пп. 1-2, який відрізняється тим, що формувач функції і вузол скидання виконані у вигляді постійного запам'ятовуючого пристрою або у вигляді програмованої логічної матриці.

Текст

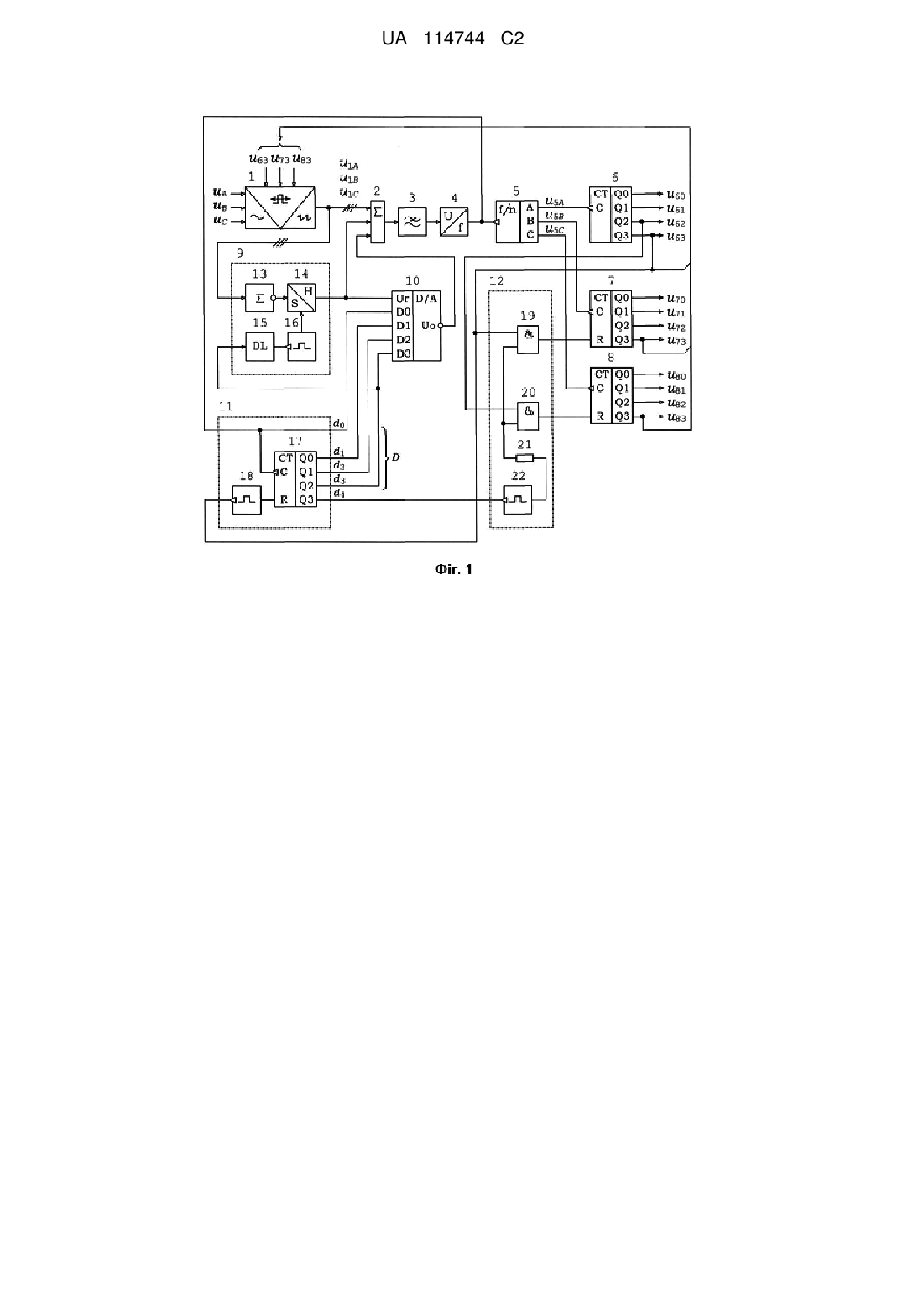

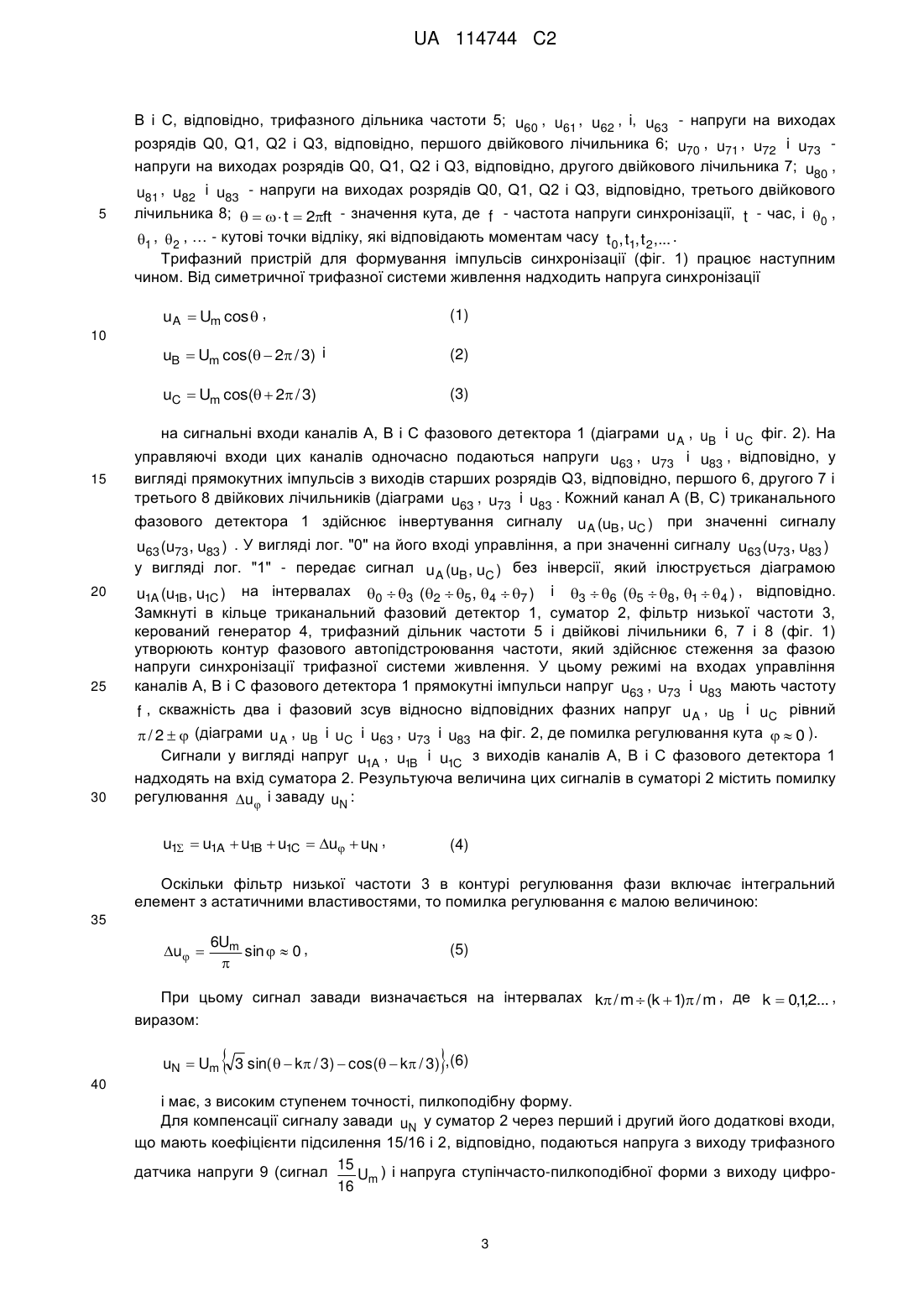

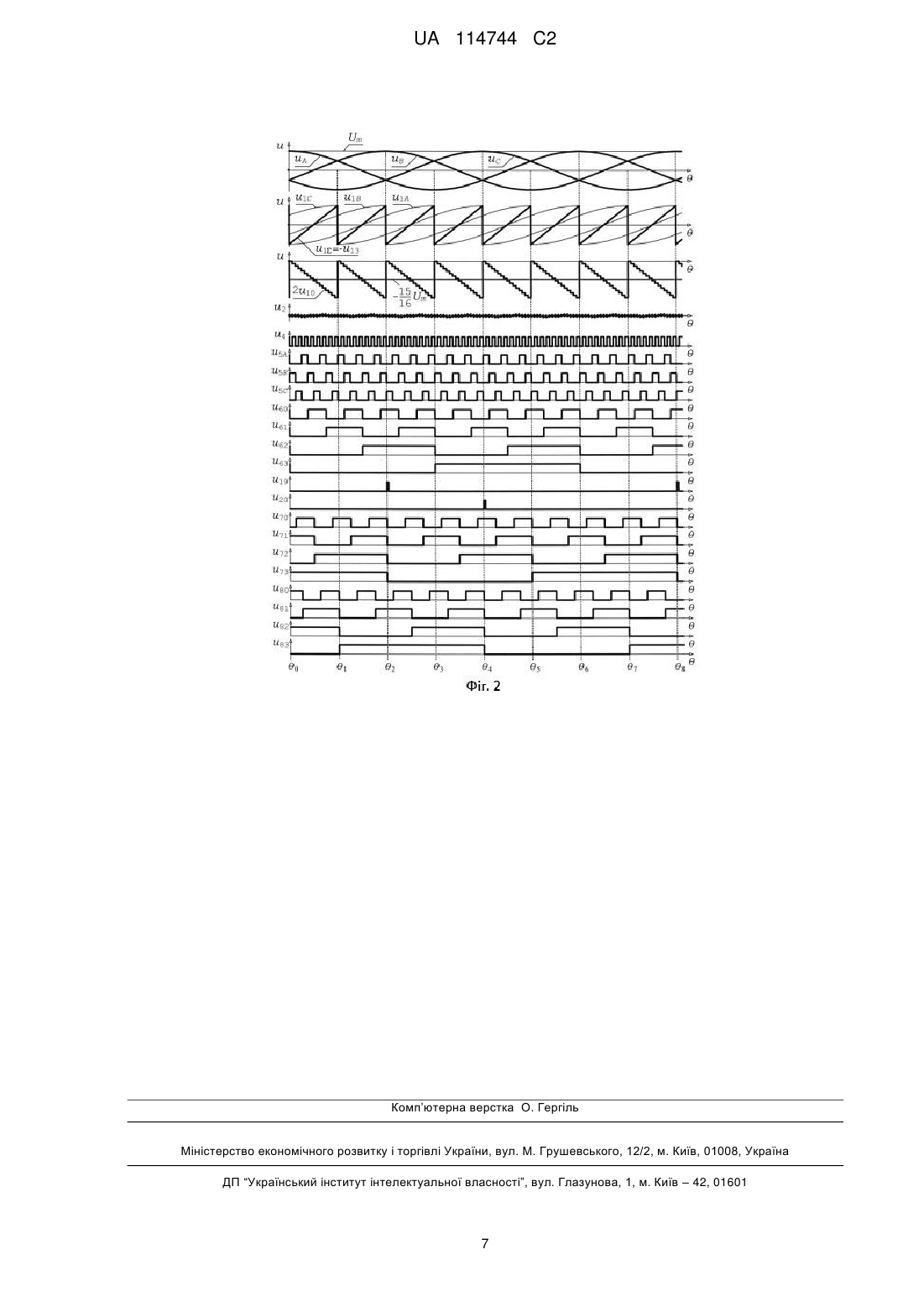

Реферат: Багатофазний пристрій для формування імпульсів синхронізації належить до електротехніки, зокрема для синхронізації симетричних систем управління тиристорними перетворювачами постійного і змінного струму. Багатофазний пристрій містить послідовно з'єднані m-канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор і m-фазний дільник частоти та додатково введені m двійкових лічильників, m-фазний датчик напруги, цифроаналоговий перетворювач, формувач функції і вузол скидання. Кожний двійковий лічильник з'єднаний лічильним входом з відповідним виходом m-фазного дільника частоти, а виходом старшого розряду - з управляючим входом відповідного каналу m-канального фазового детектора. Вихід m-фазного датчика напруги з'єднаний з першим додатковим входом суматора і входом опорної напруги цифро-аналогового перетворювача, вихід якого з'єднаний з другим додатковим входом суматора. Формувач функції з'єднаний входами з виходом керованого генератора і з виходами розрядів принаймні першого двійкового лічильника, а цифровим виходом - з цифровим входом цифро-аналогового перетворювача. Вузол скидання з'єднаний входами з виходами розрядів принаймні першого двійкового лічильника і з цифровим виходом формувача функції. Крім того, виходи вузла скидання з'єднані з входами установки в нуль відповідних двійкових лічильників з другого по m-ний. Технічним результатом є підвищення точності формування синхроімпульсів і розширення функціональних можливостей пристрою. UA 114744 C2 (12) UA 114744 C2 UA 114744 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до області електротехніки і може бути використаний для синхронізації симетричних систем управління тиристорними перетворювачами постійного і змінного струму. Відомий багатоканальний пристрій для управління вентильним перетворювачем (аналог) за патентом SU 1777216А1 (Int. С1. Н02М 7/12, 1992), який містить послідовно з'єднані фазовий детектор, фільтр низької частоти, керований генератор і дільник частоти, що включає кільцевий регістр зсуву на фазних JK-тригерах, вихід одного з яких з'єднаний з управляючим входом фазового детектора, і т. д. В даному випадку регулювання трьох фаз пристрою здійснюється за напругою однієї з фаз мережі, яка надходить на сигнальний вхід фазового детектора, а імпульси синхронізації для кожного каналу системи управління формуються на виходах фазних JK-тригерів дільника частоти. Ці імпульси синхронізації зсунуті відносно один одного на 120 ел. градуса. Недоліком вказаного пристрою є несиметрія імпульсів синхронізації через значні пульсації у вигляді другої і ін. гармонік в сигналі на виході фільтру низької частоти при мінімально допустимій його швидкодії. Відомий пристрій (прототип) за патентом US 4042873 A (Int. С1. Н02М 7/00, 1977), що містить послідовно з'єднані m-канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор, дільник частоти і фазуючий засіб, вихід кожної фази якого з'єднаний з управляючим входом відповідного каналу фазового детектора, і т. д. Регулювання m фазами пристрою здійснюється за напругами m фаз мережі, які надходять на сигнальні входи mканального фазового детектора, а імпульси синхронізації для кожного каналу системи управління формуються на виходах фазуючого засобу. Ці імпульси синхронізації зсунуті відносно один одного на 360/m ел. градусів для m-фазної системи живлення. Недоліком вказаного пристрою є невисока точність симетрії синхроімпульсів через наявність 2m-ної і інших вищих гармонік в сигналі на виході фільтра низької частоти при мінімально допустимій його швидкодії. Фази пристрою не формують синхроімпульси, тривалість яких дорівнює 1/4, 1/8, 1/16, … від періоду напруги мережі T . Технічний результат пропонованого винаходу полягає в підвищенні точності формування синхроімпульсів і розширенні функціональних можливостей пристрою. Вказаний технічний результат досягається тим, що у багатофазний пристрій для формування імпульсів синхронізації, який містить послідовно з'єднані m-канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор і m-фазний дільник частоти (дільник частоти + фазуючий засіб), введені m двійкових лічильників, m-фазний датчик напруги, цифро-аналоговий перетворювач, формувач функції і вузол скидання, причому кожен двійковий лічильник з'єднаний рахунковим входом з відповідним виходом m-фазного дільника частоти, а виходом старшого розряду - з управляючим входом відповідного каналу m-канального фазового детектора; m-фазний датчик напруги з'єднаний входами з відповідними сигнальними входами або виходами m - канального фазового детектора, а виходом - з першим додатковим входом суматора і входом опорної напруги цифро-аналогового перетворювача, вихід якого з'єднаний з другим додатковим входом суматора; формувач функції з'єднаний входами з виходом керованого генератора і з виходами розрядів або першого двійкового лічильника або першого і декількох подальших двійкових лічильників, а цифровим виходом - з цифровим входом цифроаналогового перетворювача; вузол скидання з'єднаний входами з виходами розрядів першого двійкового лічильника (або першого і подальших двійкових лічильників) і або з виходами mфазного дільника частоти або з цифровим виходом формувача функції, крім того, виходи вузла скидання з'єднані з входами установки в нуль відповідних двійкових лічильників з другого по mний. У пропонованому пристрої цифро-аналоговий перетворювач виконує множення аналогового сигналу з виходу m-фазного датчика напруги і цифрового сигналу з виходу формувача функції. В результаті на виході цифро-аналогового перетворювача формується напруга, змінна складова якої знаходиться в протифазі із змінною складовою суми сигналів з виходів mканального фазового детектора. Ці різнополярні сигнали за допомогою суматора взаємно компенсуються. Постійна складова напруги з виходу цифро-аналогового перетворювача також компенсується в суматорі сигналом з виходу m-фазного датчика напруги. Таким чином, сигнал з виходу суматора надходить на вхід фільтра практично без завад. Цифровий сигнал на відповідному вході цифро-аналогового перетворювача має дискретно-лінійну залежність від часу на заданих інтервалах часу. Цю залежність задає формувач функції за цифровою інформацією з виходів керованого генератора і розрядів двійкових лічильників і т. д. Двійкові лічильники формують синхроімпульси, тривалість яких складає 1/4, 1/8, 1/16 від значення T , причому зсув за часом імпульсів однієї фази відносно сусідніх складає T / m з високою точністю при підвищеній швидкодії фільтра низької частоти. Вузол скидання забезпечує нульові 1 UA 114744 C2 5 10 15 20 25 30 35 40 45 50 55 початкові умови роботи другого і подальших двійкових лічильників через проміжки часу рівні T/m. На фіг. 1 зображена функціональна схема трифазного пристрою для формування імпульсів синхронізації, як одного з прикладів виконання багатофазного пристрою. На фіг. 2 зображені часові діаграми, що пояснюють принцип роботи вказаного пристрою. Трифазний пристрій для формування імпульсів синхронізації (фіг. 1) містить фазовий детектор 1, що включає три канали А, В і С, кожен з яких виконаний у вигляді фазочутливого випрямляча, що має сигнальний вхід, управляючий вхід і вихід, які є відповідними входами і виходом каналу; суматор 2 (виконаний на операційному підсилювачі); фільтр низької частоти 3 (виконаний на операційному підсилювачі), що включає елемент інтеграції; керований генератор 4 (виконаний на основі мультивібратора і керованих джерел струму); трифазний дільник частоти 5 (виконаний на двійковому лічильнику і дешифраторі); перший 6, другий 7 і третій 8 двійкові лічильники, кожен з яких має чотири розряди; трифазний датчик напруги 9; цифро-аналоговий перетворювач 10; формувач функції 11 і вузол скидання 12. Крім того, трифазний датчик напруги 9 включає послідовно з'єднані додатковий (другий) суматор 13 (виконаний на операційному підсилювачі) і елемент вибірки-зберігання 14 (мікросхема LF298, Philips), а також послідовно з'єднані елемент затримки 15 (послідовно з'єднані RC-коло і тригер Шмітта) і перший одновібратор 16, виходом підключений до управляючого входу елемента вибіркизберігання 14, при цьому входи додаткового суматора 13, вхід елемента затримки 15 і вихід елемента вибірки-зберігання 14 є, відповідно, сигнальним входом, управляючим входом і виходом трифазного датчика напруги 9; формувач функції 11 включає додатковий (четвертий) двійковий лічильник 17, що має чотири розряди, і другий одновібратор 18 (у формулі винаходу просто одновібратор), з'єднаний виходом з R-входом установки в нуль додаткового двійкового лічильника 17, при цьому перший вхід і перший вихід формувача функції 11 з'єднані з лічильним С-входом додаткового двійкового лічильника 17, у якому виходи Q0, Q1, Q2 і Q3 розрядів є, відповідно, другим, третім, четвертим і п'ятим виходами формувача функції 11, вхід другого одновібратора 18 є другим входом формувача функції 11, крім того, з першого по четвертий виходи формувача функції 11 є його цифровим виходом (сигнал D); вузол скидання 12 включає перший елементAND 19, перший вхід і вихід якого є, відповідно, першим входом і першим виходом вузла скидання 12, другий елемент AND 20, перший вхід і вихід якого є, відповідно, другим входом і другим виходом вузла скидання 12, резистор 21 і третій одновібратор 22, вхід якого є третім входом вузла скидання 12, а вихід з'єднаний через резистор 21 з другими входами першого 19 і другого 20 елементів AND. Причому, канали А, В і С фазового детектора 1 з'єднані сигнальними входами з відповідними фазами джерела напруг синхронізації (напруги u A , uB і uC ), а виходами - з відповідними входами суматора 2 і трифазного датчика напруги 9, який управляючим входом з'єднаний з четвертим виходом (сигнал d3 ) формувача функції 11; вихід суматора 2 підключений через послідовно з'єднані фільтр низької частоти 3 і керований генератор 4 до входу трифазного дільника частоти 5; виходи фаз А, В і С дільника частоти 5 з'єднані з лічильними С-входами, відповідно, першого 6, другого 7 і третього 8 двійкових лічильників, старші розряди Q3 яких підключені до управляючих входів каналів А, В і С, відповідно, фазового детектора 1; цифро-аналоговий перетворювач 10 з'єднаний входом опорної напруги Ur з виходом датчика напруги 9 і з першим додатковим входом суматора 2, а виходом Uo - з другим додатковим входом суматора 2; перший і другий входи формувача функції 11 з'єднані з виходами, відповідно, керованого генератора 4 і третього (старшого) розряду Q3 першого двійкового лічильника 6; цифровий вихід, який формується з першого по четвертий виходами d0…d3 (сигнал D) формувача функції 11 і з'єднаний з цифровим входом D0…D3 цифро-аналогового перетворювача 10; перший, другий і третій входи вузла скидання 12 з'єднані, відповідно, з виходами третього Q3 і другого Q2 розрядів першого двійкового лічильника 6 і з п'ятим виходом (сигнал d4 ) формувача функції 11, а перший і другий виходи вузла скидання 12 з'єднані з R-входами установки в нуль, відповідно, другого 7 і третього 8 двійкових лічильників. Слід зазначити, що з метою спрощення пристрою для формування імпульсів синхронізації (фіг. 1) (переважно при кількості фаз m6) замість формувача функції 11 і вузла скидання 12 може використовуватися постійний запам'ятовуючий пристрій або програмована логічна матриця. На фіг. 1 і фіг. 2 введені наступні позначення: u A , uB і uC - фазні напруги синхронізації з амплітудою Um ; u1A , u1B і u1C - відповідно, напруги каналів А, В і С фазового детектора 1; u1 u1A u1B u1C ; u2 , u 4 і u10 - напруги на виходах суматора 2, керованого генератора 4 і цифро-аналогового перетворювача 10, відповідно; u5 A , u5B і u5C - напруги на виходах фаз А, 2 UA 114744 C2 В і С, відповідно, трифазного дільника частоти 5; u60 , u61 , u62 , і, u63 - напруги на виходах розрядів Q0, Q1, Q2 і Q3, відповідно, першого двійкового лічильника 6; u70 , u71 , u72 і u73 напруги на виходах розрядів Q0, Q1, Q2 і Q3, відповідно, другого двійкового лічильника 7; u80 , 5 u81 , u82 і u83 - напруги на виходах розрядів Q0, Q1, Q2 і Q3, відповідно, третього двійкового лічильника 8; t 2ft - значення кута, де f - частота напруги синхронізації, t - час, і 0 , 1 , 2 , … - кутові точки відліку, які відповідають моментам часу t 0 , t1, t 2,... . Трифазний пристрій для формування імпульсів синхронізації (фіг. 1) працює наступним чином. Від симетричної трифазної системи живлення надходить напруга синхронізації uA Um cos , (1) uB Um cos( 2 / 3) і (2) uC Um cos( 2 / 3) (3) 10 15 на сигнальні входи каналів А, В і С фазового детектора 1 (діаграми u A , uB і uC фіг. 2). На управляючі входи цих каналів одночасно подаються напруги u63 , u73 і u83 , відповідно, у вигляді прямокутних імпульсів з виходів старших розрядів Q3, відповідно, першого 6, другого 7 і третього 8 двійкових лічильників (діаграми u63 , u73 і u83 . Кожний канал А (В, С) триканального фазового детектора 1 здійснює інвертування сигналу uA (uB , uC ) при значенні сигналу u63 (u73 , u83 ) . У вигляді лог. "0" на його вході управління, а при значенні сигналу u63 (u73 , u83 ) 20 25 у вигляді лог. "1" - передає сигнал uA (uB , uC ) без інверсії, який ілюструється діаграмою u1A (u1B, u1C ) на інтервалах 0 3 (2 5, 4 7 ) і 3 6 (5 8, 1 4 ) , відповідно. Замкнуті в кільце триканальний фазовий детектор 1, суматор 2, фільтр низької частоти 3, керований генератор 4, трифазний дільник частоти 5 і двійкові лічильники 6, 7 і 8 (фіг. 1) утворюють контур фазового автопідстроювання частоти, який здійснює стеження за фазою напруги синхронізації трифазної системи живлення. У цьому режимі на входах управління каналів А, В і С фазового детектора 1 прямокутні імпульси напруг u63 , u73 і u83 мають частоту f , скважність два і фазовий зсув відносно відповідних фазних напруг u A , uB і uC рівний 30 / 2 (діаграми u A , uB і uC і u63 , u73 і u83 на фіг. 2, де помилка регулювання кута 0 ). Сигнали у вигляді напруг u1A , u1B і u1C з виходів каналів А, В і С фазового детектора 1 надходять на вхід суматора 2. Результуюча величина цих сигналів в суматорі 2 містить помилку регулювання u і заваду uN : u1 u1A u1B u1C u uN , (4) Оскільки фільтр низької частоти 3 в контурі регулювання фази включає інтегральний елемент з астатичними властивостями, то помилка регулювання є малою величиною: 35 u 6Um sin 0 , (5) При цьому сигнал завади визначається на інтервалах k / m (k 1) / m , де k 0,12... , , виразом: uN Um 3 sin( k / 3) cos( k / 3) ,(6) 40 і має, з високим ступенем точності, пилкоподібну форму. Для компенсації сигналу завади uN у суматор 2 через перший і другий його додаткові входи, що мають коефіцієнти підсилення 15/16 і 2, відповідно, подаються напруга з виходу трифазного датчика напруги 9 (сигнал 15 Um ) і напруга ступінчасто-пилкоподібної форми з виходу цифро16 3 UA 114744 C2 5 аналогового перетворювача 10 (діаграма 2u10 ), Результуюча напруга з виходу суматора 2 (діаграма u2 ) надходить на вхід фільтра низької частоти 3, де додатково згладжується до значення помилки регулювання, що визначається виразом (5), і перетворюється пропорційноінтегральною частиною в сигнал для управління генератором 4. Керований генератор 4 формує прямокутні імпульси (діаграма u 4 ) з частотою f4 fN5 2N1 , (7) 10 де N 3 - номер старшого розряду двійкового лічильника 6 (7, 8); N5 3 - коефіцієнт ділення трихфазного дільника частоти 5. Ці імпульси перетворюються трифазним дільником частоти 5 так, що на виходах його фаз А, В і С формуються послідовності прямокутних 15 імпульсів з частотою f 2N1 , скважністю три, при цьому імпульси однієї послідовності зсунуті відносно іншої на тривалість одного імпульсу діаграми ( u5 A , u5B і u5C ) для зчитування їх, відповідно, першим 6, другим 7 і третім 8 двійковими лічильниками. На виходах розрядів з номером п кожного двійкового лічильника 6, 7 і 8 формуються прямокутні імпульси з частотою проходження f6,7,8 (n) f 2Nn , 20 25 (8) де N 3 і n 0,1 2, 3 (див. діаграми и60, u60 , u61 , u62 , u63 , u70 , u71 , u72 , u73 , u80 , u81 , , u82 , і u83 ). Послідовність заповнення (скидання) першого 6, другого 7 і третього 8 двійкових лічильників, а також додаткового двійкового лічильника 17 формувача функції 11 протягом відповідних інтервалів часу з тривалістю Т напруги синхронізації здійснюється наступним чином. Перший двійковий лічильник 6 заповнюється і скидається по закінченні кожного періоду (діаграми u60 , u61 , u62 , і, u63 , моменти 0 і 6 ), при цьому сигнал u63 з виходу старшого розряду Q3 надходить на формувач функції 11, де запускає спадом одновібратор 18, який коротким імпульсом встановлює за R-входом додатковий двійковий лічильник 17 в нуль. На інтервалі 0 6 додатковий чотирирозрядний двійковий лічильник 17 тричі через інтервал 2 / 3 заповнюється і скидається в моменти 2 , 4 і 6 при підрахунку імпульсів частотою f4 (див. вираз (7)) з виходу керованого генератора 4: 30 2 0 4 2 6 4 35 40 45 4 2 , (9) 2 f4 3 На виходах (з першого по п'ятий) формувача функції 11 додатковий двійковий лічильник 17 формує двійковий код d0 ...d4 лінійно наростаючого цифрового сигналу, частина якого d0 ...d3 використовується як цифровий сигнал D для цифро-аналогового перетворювача 10, а сигнал d4 з п'ятого виходу використовується у вузлі скидання 12 для запуску одновібратора 22. Одновібратор 22 по спаду сигналу d4 формує в моменти 0 , 2, 4 ,... короткі імпульси, що надходять через резистор 21 на другі входи елементів AND 19 і 20, на перші входи яких з виходів розрядів Q3 і Q2 першого двійкового лічильника 6 надходять сигнали u63 і u62 для здійснення передачі імпульсів з виходу одновібратора 22 на R-входи установки в нуль другого двійкового лічильника 7 в моменти 2, 8,... і третього двійкового лічильника 8-у моменти 4 , … (діаграми u19 , u20 ). Таким чином, другий 7 і третій 8 двійкові лічильники встановлюються в стан нуль через 2 / 3 з метою забезпечення синхронізації в їх роботі. Це відбувається кожного разу при включенні живлення пристрою, далі вказані лічильники скидаються самостійно в результаті їх переповнення. Резистор 21 і ємність входів елементів AND 19 і 20 забезпечують мінімальну затримку ( 1s) для виключення збоїв в роботі вузла скидання 12. Компенсація сигналу завади uN (вираз (6)) здійснюється наступним чином. Трифазний датчик напруги 9 вимірює амплітуду Um напруги синхронізації. Для цього фазні напруги u1A , 4 UA 114744 C2 u1B і u1C з виходів каналів А, В і С фазового детектора 1 підсумовуються додатковим суматором 13: u13 u1A u1B u1C u1 , 5 (10) (див. діаграму u1 на фіг. 2). Потім сумарний сигнал u13 фіксується елементом вибіркизберігання 14 в моменти часу 0 , 1 , 2 ,... , які відповідають моментам, затриманих на , спадів сигналу d3 з четвертого виходу формувача функції 11: u14 u9 u13 10 15 20 k / 3 Um , (11) де k 0,1 2,... . Величина затримки 0 має бути більше часу встановлення напруги u13 на , виході додаткового суматора 13 (~ 2 4s) з одного рівня на іншій при перемиканнях фазочутливих випрямлячів каналів А, В і С фазового детектора 1 під дією управляючих сигналів. Ця затримка забезпечується елементом 15, від якого перший одновібратор 16 запускається і формує короткий імпульс для управління елементом вибірки-зберігання 14. З виходу трьохфазного датчика напруги 9 напруга, пропорційна амплітуді Um напруги синхронізації, надходить на вхід Ur опорної напруги цифро-аналогового перетворювача 10, на цифровий вхід якого D04D3 надходить цифровий сигнал D з першого по четвертий виходів формувача функції 11. На виході цифро-аналогового перетворювача 10 на інтервалах , k / m (k 1) / m , де k 0,1 2,... , формується ступінчасто-лінійний сигнал: U u10 m d3 23 d2 22 d121 d0 20 , (12) 16 постійна складова якого на інтервалі / 3 дорівнює: U 1 15 Um , U0 m 1 4 2 32 2 25 30 35 40 45 (13) Подвоєне поточне значення напруги, що обчислюється за виразом (12) і ілюструється діаграмою 2u10 на фіг. 2, має змінну складову, яка знаходиться в протифазі із завадою uN відповідно до виразу (6), і постійну складову 15 Um , що є додатковою завадою. Сигнали u9 і 32 з виходів датчика напруги 9 і цифро-аналогового перетворювача 10 надходять, відповідно, u10 на перший і другий додаткові входи суматора 2, що мають коефіцієнти підсилення 15/16 і 2, відповідно. В результаті їх дії напруга завади uN і постійна складова 15 Um значною мірою 32 компенсуються і на виході суматора 2 формується сигнал практично без завад (діаграма u2 ). Якщо перший 6, другий 7 і третій 8 двійкові лічильники мають більшу кількість розрядів, ніж в прикладі виконання пристрою, то відповідно більшу кількість розрядів має додатковий (четвертий) двійковий лічильник 17, який в результаті задає менший ступінь дискретизації напруги на виході цифро-аналогового перетворювача 10 і дозволяє більш точно компенсувати заваду uN . Підвищена кількість синхроімпульсів на виходах двійкових лічильників збільшує можливості синхронізації. Відзначимо те, що пропонований пристрій можна спростити шляхом реалізації суматора 2 і фільтра низької частоти 3 у вигляді послідовних з'єднаних підсумовуючого RC-кола і неінвертуючого ПІ-регулятора (виконаний на операційному підсилювачі), а також цифроаналогового перетворювача 10 у вигляді КМОП перемикачів і масштабуючих резисторів, які є складовою частиною вказаного вище підсумовуючого RC-кола. При цьому суть заявки пристрою не змінюється. Крім того, при використанні даного пристрою в системах управління для тиристорних перетворювачів, що включають багатофазну систему живлення з великою кількістю фаз (m>3), наприклад, для 12-пульсного тиристорного випрямляча з вхідним трансформатором, виконаним 5 UA 114744 C2 за схемою Y / Y (m=6), елементи і вузли пропонованого пристрою виконуються з урахуванням цього значення фаз m, що не значно ускладнює пристрій. З метою спрощення пристрою (переважно при m6) використовується постійний запам'ятовуючий пристрій або програмована логічна матриця замість формувача функції 11 і вузла скидання 12 і т. д. 5 ФОРМУЛА ВИНАХОДУ 10 15 20 25 30 1. Багатофазний пристрій для формування імпульсів синхронізації, що містить послідовно з'єднані m-канальний фазовий детектор, суматор, фільтр низької частоти, керований генератор і m-фазний дільник частоти, який відрізняється тим, що додатково введені m двійкових лічильників, m-фазний датчик напруги, цифро-аналоговий перетворювач, формувач функції і вузол скидання, причому кожен з m двійкових лічильників з'єднаний лічильним входом з відповідним виходом m-фазного дільника частоти, а виходом старшого розряду - з управляючим входом відповідного каналу m-канального фазового детектора, а вихід m-фазного датчика напруги з'єднаний з першим додатковим входом суматора і входом опорної напруги цифро-аналогового перетворювача, вихід якого з'єднаний з другим додатковим входом суматора, крім того, формувач функції з'єднаний входами з виходом керованого генератора і з виходами розрядів принаймні першого двійкового лічильника, а цифровим виходом - з цифровим входом цифро-аналогового перетворювача, вузол скидання з'єднаний входами з виходами розрядів принаймні першого двійкового лічильника і з цифровим виходом формувача функції, крім того, виходи вузла скидання з'єднані з входами установки в нуль відповідних двійкових лічильників з другого по m-ний. 2. Багатофазний пристрій за п. 1, який відрізняється тим, що m-фазний датчик напруги виконаний у вигляді послідовно з'єднаних додаткових суматора і елемента вибірки-зберігання, при цьому вхід додаткового суматора з'єднаний з виходом m-канального фазового детектора. 3. Багатофазний пристрій за будь-яким з пп. 1-2, який відрізняється тим, що формувач функції виконаний у вигляді одновібратора, вхід якого з'єднаний принаймні з виходом старшого розряду першого двійкового лічильника, і додатково введеного двійкового лічильника, у якому вхід установки в нуль з'єднаний з виходом одновібратора, лічильний вхід з'єднаний з виходом керованого генератора, причому лічильний вхід і виходи розрядів є цифровим виходом формувача функцій. 4. Багатофазний пристрій за будь-яким з пп. 1-2, який відрізняється тим, що формувач функції і вузол скидання виконані у вигляді постійного запам'ятовуючого пристрою або у вигляді програмованої логічної матриці. 6 UA 114744 C2 Комп’ютерна верстка О. Гергіль Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 7

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H02M 1/08

Мітки: формування, імпульсів, багатофазній, пристрій, синхронізації

Код посилання

<a href="https://ua.patents.su/9-114744-bagatofaznijj-pristrijj-dlya-formuvannya-impulsiv-sinkhronizaci.html" target="_blank" rel="follow" title="База патентів України">Багатофазний пристрій для формування імпульсів синхронізації</a>

Попередній патент: Спосіб приготування пивного сусла та пристрій для його реалізації

Наступний патент: Заміщені аміноазоли як регулятори росту рослин

Випадковий патент: Спосіб одержування тонкодисперсного вапна