Пристрій для алгебраїчного додавання

Номер патенту: 22787

Опубліковано: 25.04.2007

Автори: Лакєєв Володимир Володимирович, Кирилко Олександр Володимирович, Наконечний Олександр Миколайович, Мартинюк Тетяна Борисівна

Формула / Реферат

Пристрій для алгебраїчного додавання, який містить суматор, регістр і блок керування, що містить вузол аналізу співвідношення знаків операндів, вузол формування знака результату і вузол формування сигналів керування, причому виходи суматора з'єднані з виходами пристрою, вузол аналізу співвідношення знаків операндів містить три елементи НІ, шість елементів І, чотири елементи АБО, вузол формування знака результату містить елемент НІ, три елементи І і елемент АБО, при цьому виходи першого і другого елементів НІ вузла аналізу співвідношення знаків операндів з'єднані відповідно з першим і другим входами першого елемента І вузла аналізу співвідношення знаків операндів, вихід якого з'єднаний з першим входом першого елемента АБО вузла аналізу співвідношення знаків операндів, другий вхід якого підключений до виходу другого елемента І вузла аналізу співвідношення знаків операндів, а вихід з'єднаний з першим входом першого елемента І вузла формування знака результату, вихід елемента НІ вузла формування знака результату підключений до першого входу другого елемента І вузла формування знака результату, вихід якого з'єднаний з першим входом елемента АБО вузла формування знака результату, вузол формування сигналів керування містить генератор тактових імпульсів, регістр зсуву, елемент НІ, елемент І, елемент АБО, причому інформаційні входи регістра з'єднані з входами другого операнда пристрою, вихід знакового розряду суматора з'єднаний з входом першого елемента НІ і першими входами третього, четвертого, п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів, вихід знакового розряду регістра з'єднаний з входом другого елемента НІ, першим входом другого елемента І і другими входами четвертого і шостого елементів І вузла аналізу співвідношення знаків операндів, вхід коду операції пристрою з'єднаний з входом третього елемента НІ, третіми входами першого і четвертого елементів І і другим входом п'ятого елемента І вузла аналізу співвідношення знаків операндів, другий і третій входи другого елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами першого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, другий і третій входи третього елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, треті входи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, виходи третього і четвертого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами другого елемента АБО вузла аналізу співвідношення знаків операндів, виходи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами третього елемента АБО вузла аналізу співвідношення знаків операндів, виходи першого і другого елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з входами четвертого елемента АБО вузла аналізу співвідношення знаків операндів, вихід якого підключений до входу ознаки запису інформації суматора, вихід позики старшого розряду якого з'єднаний з входом елемента НІ і другим входом першого елемента І вузла формування знака результату, вихід елемента НІ вузла формування знака результату з'єднаний з першим входом третього елемента І вузла формування знака результату, виходи другого і третього елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з другими входами другого і третього елементів І вузла формування знака результату відповідно, виходи першого і третього елементів І вузла формування знака результату підключені відповідно до другого і третього входів елемента АБО вузла формування знака результату, вхід запуску пристрою з'єднаний з установним входом регістра зсуву вузла формування сигналів керування, вихід першого розряду якого з'єднаний з першим входом елемента АБО вузла формування сигналів керування, вихід якого з'єднаний з входом дозволу запису суматора, вихід другого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу запису регістра, вихід третього розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування регістра і з другим входом елемента АБО вузла формування сигналів керування, вихід елемента НІ вузла формування сигналів керування з'єднаний з першим входом елемента І вузла формування сигналів керування, другий вхід і вихід якого з'єднані відповідно з виходом генератора тактових імпульсів і входом зсуву регістра зсуву вузла формування сигналів керування, який відрізняється тим, що у вузол формування знака результату введено RS-тригер, S-вхід якого з'єднаний з виходом елемента АБО цього вузла, R-вхід з'єднаний з виходом першого розряду регістра зсуву вузла формування сигналів керування, а вихід є виходом знака результату пристрою, вихід четвертого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування суматора і входом елемента НІ вузла формування сигналів керування.

Текст

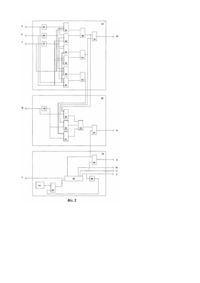

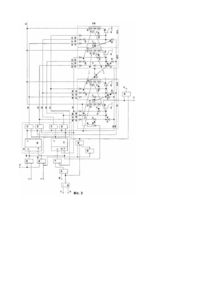

Корисна модель відноситься до області обчислювальної техніки і може бути використана при побудові оптоелектронних арифметичних пристроїв для додавання та віднімання десяткових чисел. Відомий пристрій для додавання та віднімання чисел [а. с. СРСР №842798, G06F7/50, 1981], які представлені паралельними кодами. Пристрій складається з суматора і блока керування, перший і другий входи блока керування з'єднані з шинами знакових розрядів операндів, вихід переносу старшого розряду суматора з'єднаний з третім входом блока керування, вхід переносу молодшого розряду суматора з'єднаний з виходом циклічного переносу блока керування, пристрій також складається з блоків інвертування, а блок керування має вузол аналізу відношення знаків операндів і вузол формування знака результату, ознаки переповнення і циклічного переносу, причому інформаційні входи блоків інвертування першого і другого операндів з'єднані з відповідними входами пристрою, виходи блоків інвертування першого і другого операндів з'єднані відповідно з першим і другим інформаційними входами суматора, вихід якого є виходом результату пристрою, входи вузла аналізу відношення знаків операндів з'єднані відповідно з першим і другим входами блока керування, перший і другий входи ознаки наявності тільки одного від'ємного знака операнда вузла аналізу відношення знаків операндів є відповідними виходами блока керування, які з'єднані з керуючими входами відповідно блоків інвертування першого і другого операндів, перший, другий, третій, четвертий входи вузла формування знака результату, ознаки переповнення і циклічного переносу з'єднані відповідно з третім входом блока керування і виходами ознаки наявності двох від'ємних знаків операндів, співпадання знаків операндів і неспівпадання знаків вузла аналізу відношення знаків операндів, виходи знака результату і ознаки переповнення вузла формування знака результату, ознаки переповнення і циклічного переносу є відповідними входами блока керування пристрою, вихід циклічного переносу вузла формування знака результату, ознаки переповнення і циклічного переносу є відповідним виходом блока керування, який з'єднаний з першим входом корекції суматора і керуючим входом вихідного блока інвертування, другий вихід корекції суматора підключений до виходу ознаки співпадання знаків вузла аналізу відношення знаків. Недоліком відомого пристрою є низька швидкодія, оскільки операції додавання-віднімання над числами виконуються на двійково-десятковому суматорі, який потребує корекції результату обчислення. Крім того, операції додавання-віднімання операндів, які представлені паралельними кодами, виконуються порозрядно, це призводить до збільшення часу виконання операції, який залежить від розрядності операндів. Найбільш близьким за технічною суттю є пристрій для додавання та віднімання [а.с. СРСР 1193664, G06F7/50, 1985], який містить суматор-віднімач, далі поіменований як суматор, регістр і блок керування, що містить вузол аналізу співвідношення знаків операндів, вузол формування знака результату, вузол формування сигналів синхронізації, далі поіменований як вузол формування сигналів керування, причому перша група інформаційних входів суматора з'єднана з входами першого операнда пристрою, виходи суматора з'єднані з виходами пристрою, вузол аналізу співвідношення знаків операндів містить три елементи НІ, шість елементів І, чотири елементи АБО, вузол формування знака результату містить елемент НІ, три елементи І і елемент АБО, при цьому ви ходи першого і другого елементів НІ вузла аналізу співвідношення знаків операндів з'єднані відповідно з першим і другим входами першого елемента І вузла аналізу співвідношення знаків операндів, вихід якого з'єднаний з першим входом першого елемента АБО вузла аналізу співвідношення знаків операндів, другий вхід якого підключений до виходу другого елемента І вузла аналізу співвідношення знаків операндів, а вихід з'єднаний з першим входом першого елемента І вузла формування знака результату, ви хід елемента НІ вузла формування знака результату підключений до першого входу другого елемента І вузла формування знака результату, вихід якого з'єднаний з першим входом елемента АБО вузла формування знака результату, вузол формування сигналів керування містить генератор тактових імпульсів, регістр зсуву, елемент НІ, елемент І, елемент АБО, причому інформаційні входи регістра з'єднані з входами другого операнда пристрою, виходи регістра з'єднані з першою і другою гр упами інформаційних входів суматора, вихід знакового розряду якого з'єднаний з входом першого елемента НІ і першими входами третього, четвертого, п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів, вихід знакового розряду регістра з'єднаний з входом другого елемента НІ, першим входом другого елемента І і другими входами четвертого і шостого елементів І вузла аналізу співвідношення знаків операндів, вхід коду операції пристрою з'єднаний з входом третього елемента НІ, третіми входами першого і четвертого елементів І і другим входом п'ятого елемента І вузла аналізу співвідношення знаків операндів, другий і третій входи другого елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами першого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, другий і третій входи третього елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, треті входи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, виходи третього і четвертого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами другого елемента АБО вузла аналізу співвідношення знаків операндів, виходи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами третього елемента АБО вузла аналізу співвідношення знаків операндів, виходи першого і другого елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з входами четвертого елемента АБО вузла аналізу співвідношення знаків операндів, вихід якого підключений до входу ознаки запису інформації суматора, вихід позики старшого розряду якого з'єднаний з входом елемента НІ і другим входом першого елемента І вузла формування знака результату, ви хід елемента НІ вузла формування знака результату з'єднаний з першим входом третього елемента І вузла формування знака результату, виходи др угого і третього елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з другими входами другого і третього елементів І вузла формування знака результату відповідно, виходи першого і третього елементів І вузла формування знака результату підключені відповідно до другого і третього входів елемента АБО вузла формування знака результату, ви хід якого з'єднаний з інформаційним входом знакового розряду суматора, вхід запуску пристрою з'єднаний з установним входом регістра зсуву вузла формування сигналів керування, вихід першого розряду якого з'єднаний з першим входом елемента АБО вузла формування сигналів керування, вихід якого з'єднаний з входом дозволу запису суматора, вихід другого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу запису регістра, вихід третього розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування регістра і з другим входом елемента АБО вузла формування сигналів керування, вихід четвертого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу запису знакового розряду суматора, вихід п'ятого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування суматора і входом елемента НІ вузла формування сигналів керування, вихід якого з'єднаний з першим входом елемента І вузла формування сигналів керування, другий вхід і вихід якого з'єднані відповідно з виходом генератора тактових імпульсів і входом зсуву регістра зсуву вузла формування сигналів керування. Недоліком цього пристрою є обмежена обчислювальна потужність, оскільки для реалізації операцій додавання та віднімання у суматорі використовуються два відповідні інформаційні входи, на які одночасно подають один операнд, але задіяним є один з них. В основу корисної моделі поставлена задача створення пристрою для алгебраїчного додавання десяткових чисел, в якому за рахунок введення нових вузлів і зв'язків досягається можливість підвищення обчислювальної потужності пристрою, а саме, виконання регістра та суматора на оптоелектронних модулях, що мають розширені функціональні можливості, забезпечує необхідну швидкість оброблення, яка не залежить від розрядності операндів, оскільки всі розряди обробляються паралельно. Крім того, суматор має один інформаційних вхід, а для комутації операндів використовують керований мультиплексор. Поставлена задача вирішується тим, що у пристрій для алгебраїчного додавання, який містить суматор, регістр і блок керування, що містить вузол аналізу співвідношення знаків операндів, вузол формування знака результату і вузол формування сигналів керування, причому виходи суматора з'єднані з виходами пристрою, вузол аналізу співвідношення знаків операндів містить три елементи НІ, шість елементів І, чотири елементи АБО, вузол формування знака результату містить елемент НІ, три елементи І і елемент АБО, при цьому виходи першого і другого елементів НІ вузла аналізу співвідношення знаків операндів з'єднані відповідно з першим і другим входами першого елемента І вузла аналізу співвідношення знаків операндів, вихід якого з'єднаний з першим входом першого елемента АБО вузла аналізу співвідношення знаків операндів, другий вхід якого підключений до виходу другого елемента І вузла аналізу співвідношення знаків операндів, а вихід з'єднаний з першим входом першого елемента І вузла формування знака результату, вихід елемента НІ вузла формування знака результату підключений до першого входу др угого елемента І вузла формування знака результату, ви хід якого з'єднаний з першим входом елемента АБО вузла формування знака результату, вузол формування сигналів керування містить генератор тактових імпульсів, регістр зсуву, елемент НІ, елемент І, елемент АБО, причому інформаційні входи регістра з'єднані з входами другого операнда пристрою, вихід знакового розряду суматора з'єднаний з входом першого елемента НІ і першими входами третього, четвертого, п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів, вихід знакового розряду регістра з'єднаний з входом другого елемента НІ, першим входом другого елемента І і другими входами четвертого і шосто го елементів І вузла аналізу співвідношення знаків операндів, вхід коду операції пристрою з'єднаний з входом третього елемента НІ, третіми входами першого і четвертого елементів І і другим входом п'ятого елемента І вузла аналізу співвідношення знаків операндів, другий і третій входи другого елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами першого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, другий і третій входи третього елемента І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, треті входи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з виходами другого і третього елементів НІ вузла аналізу співвідношення знаків операндів відповідно, виходи третього і четвертого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами другого елемента АБО вузла аналізу співвідношення знаків операндів, виходи п'ятого і шостого елементів І вузла аналізу співвідношення знаків операндів з'єднані з входами третього елемента АБО вузла аналізу співвідношення знаків операндів, виходи першого і другого елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з входами четвертого елемента АБО вузла аналізу співвідношення знаків операндів, вихід якого підключений до входу ознаки запису інформації суматора, вихід позики старшого розряду якого з'єднаний з входом елемента НІ і другим входом першого елемента І вузла формування знака результату, ви хід елемента НІ вузла формування знака результату з'єднаний з першим входом третього елемента І вузла формування знака результату, виходи др угого і третього елементів АБО вузла аналізу співвідношення знаків операндів з'єднані з другими входами другого і третього елементів І вузла формування знака результату відповідно, виходи першого і третього елементів І вузла формування знака результату підключені відповідно до другого і третього входів елемента АБО вузла формування знака результату, вхід запуску пристрою з'єднаний з установним входом регістра зсуву вузла формування сигналів керування, вихід першого розряду якого з'єднаний з першим входом елемента АБО вузла формування сигналів керування, вихід якого з'єднаний з входом дозволу запису суматора, вихід др угого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу запису регістра, вихід третього розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування регістра і з другим входом елемента АБО вузла формування сигналів керування, вихід елемента НІ вузла формування сигналів керування з'єднаний з першим входом елемента І вузла формування сигналів керування, другий вхід і вихід якого з'єднані відповідно з виходом генератора тактових імпульсів і входом зсуву регістра зсуву вузла формування сигналів керування, введено у вузол формування знака результату RS-тригер, S-вхід якого з'єднаний з виходом елемента АБО цього вузла, R-вхід з'єднаний з виходом першого розряду регістра зсуву вузла формування сигналів керування, а вихід є виходом знака результату пристрою, вихід четвертого розряду регістра зсуву вузла формування сигналів керування з'єднаний з входом дозволу зчитування суматора і входом елемента НІ вузла формування сигналів керування. На Фіг.1 представлено блок-схему пристрою для алгебраїчного додавання, на Фіг.2 представлено структурну схему блока керування, на Фіг.3 подано принципову схему однорозрядного суматора, на Фіг.4 показано часові діаграми роботи однорозрядного суматора. Пристрій для алгебраїчного додавання (Фіг.1) містить суматор 1, регістр 2 і блок 3 керування. Вхід 4 блока 3 керування з'єднаний з входом запуску пристрою, знакові розряди суматора 1 і регістра 2 зв'язані відповідно з входами 5 і 6 блока 3 керування, вхід 7 якого є входом коду операції пристрою. Виходи 8 і 9 блока 3 керування з'єднані відповідно з входами дозволу запису і дозволу зчитування суматора 1, а виходи 10 і 11 з'єднані відповідно з входами дозволу запису і дозволу зчитування регістра 2. Вихід позики 12 старшого розряду суматора 1 підключений до входу 13 блока 3 керування, вихід 14 якого є виходом знака результату пристрою. Інформаційні входи 15 регістра 2 з'єднані з входами другого операнда пристрою, виходи 16 регістра 2 з'єднані з інформаційними входами 17 суматора 1, інформаційні входи 18 якого підключені до входів першого операнда пристрою, виходи 19 суматора 1 з'єднані з виходами пристрою. Вихід 20 блока 3 керування підключений до входу 21 ознаки запису інформації суматора 1. Блок 3 керування (Фіг.2) містить вузол 22 аналізу співвідношення знаків операндів, вузол 23 формування знака результату і вузол 24 формування сигналів керування. У вузлі 22 аналізу співвідношення знаків операндів входи 5, 6 і 7 блока З керування з'єднані відповідно з входами елементів НІ 25-27. Вхід 5 блока 3 керування з'єднаний з першими входами елементів І 28-31, вхід 6 з'єднаний з другими входами елементів І 29, 31, 32, вхід 7 з'єднаний з другими входами елементів І 30, 33 і третім входом елемента І 29. Вихід елемента НІ 25 з'єднаний з першими входами елементів І 32, 33, вихід елемента НІ 26 з'єднаний з третіми входами елементів І 28, 30, 33, вихід елемента НІ 27 з'єднаний з третіми входами елементів І 31, 32 і другим входом елемента І 28. Виходи елементів І 32, 33 підключені до входів елемента АБО 34, виходи елементів І 28, 29 підключені до входів елемента АБО 35, виходи елементів І 30, 31 підключені до входів елемента АБО 36. Входи елемента АБО 37 з'єднані з виходами елементів АБО 34, 35, а його вихід є виходом 20 блока 3 керування. У вузлі 23 формування знака результату вхід 13 блока 3 керування з'єднаний з входом елемента НІ 38 і першим входом елемента І 39, ви хід елемента НІ 38 підключений до перших входів елементів І 40, 41. Др угі входи елементів І 39-41 з'єднані відповідно з виходами елементів АБО 34-36 вузла 22 аналізу співвідношення знаків операндів, а виходи з'єднані з входами елемента АБО 42, вихід якого підключений до S-входу RS-тригера 43, вихід якого є виходом 14 блока 3 керування. Вузол 24 формування сигналів керування містить генератор 44 тактових імпульсів, регістр зсуву 45 і елементи НІ 46,1 47, АБО 48, причому вхід 4 блока 3 керування з'єднаний з установним входом регістра зсуву 45, виходи генератора 44 тактових імпульсів і елемента НІ 46 з'єднані з входами елемента І 47, вихід якого підключений до тактового входу регістра зсуву 45, що містить чотири розряди. Виходи першого і третього розрядів регістра зсуву 45 з'єднані з входами елемента АБО 48, вихід якого є виходом 8 блока З керування, виходи др угого, третього, четвертого розрядів регістра зсуву 45 є виходами 10, 11, 9 блока 3 керування відповідно, крім того, вихід четвертого розряду регістра зсуву 45 з'єднаний з входом елемента НІ 46, а вихід першого розряду підключений до R-входу RS-тригера 43 вузла 23 формування знака результату блока 3 керування. Суматор 1 (Фіг.3), до складу якого входить один десятковий розряд, містить розрядні комірки 49.1, ..., 49.9, комірку 50 початкового стану, D-тригер 51, вузол 52 перемикання напрямку лічби, першу шин у 53 непарних імпульсів, першу шину 54 парних імпульсів, другу шину 55 непарних імпульсів, другу шину 56 парних імпульсів, третю шин у 57 непарних імпульсів, третю шин у 58 парних імпульсів, RS-тригер 59, вхід 60 прямої лічби, вхід 61 зворотної лічби, чотири елементи І 62-65. Відповідно розрядні комірки 49.1, ..., 49.9 і комірка 50 початкового стану мають три входи 66-68 керування і містять транзистор 69, джерело 70 світла з п'ятьма оптичними виходами 7175, крім комірки 50 початкового стану, яка містить джерело 70 світла з чотирма оптичними виходами 71, 72, 74, 75, та розрядної комірки 49.9, яка містить джерело 70 світла з чотирма оптичними виходами 71-74, п'ять фотоприймачів 76-80, крім комірки 50 початкового стану, яка містить чотири фотоприймачі 76-79, та розрядної комірки 49.9, яка містить чотири фотоприймачі 76-78,80, три розділові діоди 81-83. Суматор 1 містить загальну шину 84, шину 85 живлення, елемент рівнозначності 86, три елементи І 87-89, елемент АБО-НІ 90, елемент АБО 91, генератор 92 тактових імпульсів, елемент АБО 93. Крім того, суматор 1 містить четверту шин у 94 непарних імпульсів і четверту шин у 95 парних імпульсів, вхід 96 тактових імпульсів, а комірка 50 початкового стану містить резистор 97 та світлодіод 98. Перший вхід вузла 52 перемикання напрямку лічби підключений до прямого виходу D-тригера 51, другий його вхід підключений до інверсного виходу D-тригера 51, перший вихід вузла 52 перемикання напрямку лічби підключений до першої шини 53 непарних імпульсів, другий-четвертий виходи підключені до першої шини 54 парних імпульсів, другої шини 55 непарних імпульсів і до другої шини 56 парних імпульсів відповідно. Перша шина 53 непарних імпульсів підключена до входів 66 керування непарних розрядних комірок 49.1,..., 49.9, перша шина 54 парних імпульсів підключена до входів 66 керування парних розрядних комірок 49.2,..., 49.8 та комірки 50 початкового стану, друга шина 55 непарних імпульсів підключена до входів 67 керування непарних розрядних комірок 49.1,..., 49.9, др уга шина 56 парних імпульсів підключена до входів 67 керування парних розрядних комірок 49.2,..., 49.8 та комірки 50 початкового стану. У розрядних комірках 49.1,..., 49.9 і комірці 50 початкового стану перший вивід джерела 70 світла підключений до шини 85 живлення, другий вивід підключений до колектора транзистора 69, емітер якого підключений до загальної шини 84, база підключена до перших виводів фотоприймачів 76-80, крім розрядної комірки 49.9, в якій база підключена до перших виводів фотоприймачів 76-78, 80 і комірки 50 початкового стану, в якій база підключена до перших виводів фотоприймачів 76-79. Оптичний вихід 71 джерела 70 з'єднаний з фотоприймачем 76 своєї комірки, оптичний вихід 72 з'єднаний з фотоприймачем 77 наступної розрядної комірки, оптичний вихід 73 з'єднаний з фотоприймачем 79 попередньої розрядної комірки, крім комірки 50 початкового стану, оптичний вихід 74 з'єднаний з фотоприймачем 78 попередньої розрядної комірки, оптичний вихід 75 з'єднаний з фотоприймачем 80 наступної розрядної комірки, крім останньої розрядної комірки 49.9. Прямий вихід RS-тригера 59 підключений до перших входів елементів І 62, 63, інверсний вихід підключений до перших входів елементів І 64, 65, перший вхід вузла 52 перемикання напрямку лічби підключений до други х входів елементів І 62, 64, другий вхід підключений до других входів елементів І 63, 65, виходи елементів І 62-65 підключені відповідно до першогочетвертого ви ходів вузла 52 перемикання напрямку лічби. Третя шина 57 непарних імпульсів підключена до прямого виходу D-тригера 51 і до входу 68 керування непарних розрядних комірок 49.1,..., 49.9, третя шина 58 парних імпульсів підключена до інверсного виходу Dтригера 51, до його D-входу і до входу 68 керування парних розрядних комірок 49.2, ..., 49.8 і комірки 50 початкового стану, в якій світлодіод 96 оптично зв'язаний з фотоприймачем 77, анод світлодіода 98 через резистор 97 підключений до шини 85 живлення, катод підключений до інверсного R-входу D-тригера 51 і до входу 60 прямої лічби пристрою, який з'єднаний з інверсним S-входом RS-тригера 59, інверсний R-вхід якого підключений до входу 61 зворотньої лічби. Четверта шина 94 непарних імпульсів підключена до прямого виходу RS-тригера 59 і до других виводів фотоприймачів 80 розрядних комірок 49.1, ..., 49.9, а четверта шина 95 парних імпульсів підключена до інверсного виходу RS-тригера 59 і до других виводів фотоприймачів 79 розрядних комірок 49.1,..., 49.8 і комірки 50 початкового стану. У всіх розрядних комірках 49.1,..., 49.9 і у комірці 50 початкового стану між входами 66-68 керування і другими виводами фотоприймачів 77, 78, 76 включені відповідно розділові діоди 81-83, а в якості п'ятьох фотоприймачів 76-80 використовуються фотодіоди. С-вхід D-тригера 51 підключений до виходу елемента АБО 91, перший вхід якого підключений до виходу елемента І 87, а другий вхід підключений до виходу елемента І 88. Оптичний вихід 74 джерела 70 світла комірки 50 початкового стану є оптичним виходом позики суматора, оптичний вихід 72 джерела 70 світла останньої розрядної комірки 49.9 є оптичним виходом переносу суматора 1, вивід з колектора транзистора 69 комірки 50 початкового стану є електричним виходом позики суматора 1, який з'єднаний з входом 12 блока З керування. Вхід 21 ознаки запису інформації суматора 1 з'єднаний з першим входом елемента рівнозначності 86 і першим входом елемента АБО-НІ 90, другі входи яких з'єднані відповідно з входом 8 дозволу запису та входом 9 дозволу зчитування суматора 1, вихід елемента АБО-НІ 90 підключений до входу 61 зворотньої лічби, а вихід елемента рівнозначності 86 підключений до входу 60 прямої лічби. Вхід 9 дозволу зчитування суматора 1 підключений до входу запуску генератора 92 тактових імпульсів і до першого входу елемента І 88, другий вхід якого з'єднаний з виходом генератора 92 тактових імпульсів, а інверсний вхід з'єднаний з виходом елемента АБО 93. Вихід елемента І 88 з'єднаний також з першим входом елемента І 89, другий вхід якого з'єднаний з колекторним виводом транзистора 69 комірки 50 початкового стану, а вихід елемента І 89 є виходом 19 суматора 1, перший вхід елемента І 87 з'єднаний з входом 93 тактових імпульсів, а його другий вхід з'єднаний з виходом елемента АБО 93, входи якого з'єднані з інформаційними входами 17 і 18 суматора 1 відповідно. Пристрій для алгебраїчного додавання (Фіг.1) працює в такий спосіб. У початковий момент часу суматор 1 і регістр 2 обнулен!. Запис першого операнда А в суматор 1 виконується з появою керуючого сигналу на ви ході 8 блока 3 керування; цей сигнал формується при наявності сигналу запуску на вході 4 блока 3 керування. Потім виконується запис другого операнда В у регістр 2 за керуючим сигналом, що надходить з виходу 10 блока 3 керування. Запис інформації в суматор 1 і регістр 2 здійснюється по інформаційних входах 18 і 15 відповідно. Інформація про знаки операндів по входах 5 і 6 подається в блок 3 керування, на вхід 7 якого надходить код операції. Блок 3 керування формує відповідно до цього сигнал на виході 20, що дозволяє запис інформації з виходів 16 регістра 2 у суматор 1 по його інформаційних входах 17 при наявності сигналів одночасно на виходах 8 і 11 блока 3 керування, які керують записом інформації в суматорі 1 і зчитуванням інформації з регістра 2. При записі по інформаційних входах 17 у суматор 1 другого операнда В відбувається паралельне підсумовування або паралельне віднімання операндів в залежності від сигналу на вході 21 ознаки запису інформації суматора 1. На виході 14 блока 3 керування формується знак результату. Зчитування результату виконується з інформаційних виходів 19 суматора 1 при наявності керуючого сигналу на виході 9 блока 3 керування. Керуючий сигнал Y на виході 20 блока 3 керування і знак результату ЗнRформуються відповідно до даних табл. 1, в якій представлена залежність сигналу Y і знака результату ЗнR від комбінацій знаків операндів ЗнА, ЗнВ, коду операції КОП і сигналу позики Рк старшого інформаційного розряду суматора 1. Для ЗнА, ЗнВ, ЗнR і КОП додатний знак "+" кодується "0", а від'ємний знак "-" кодується "1". Рівність керуючого сигналу Y одиниці означає виконання операції віднімання, при рівності керуючого сигналу Y н улю дозволяється виконання операції додавання. У табл. 1 не використано чотири комбінації вхідних величин Зн А, ЗнВ, КОП і Рк , які не мають сенсу, оскільки при додаванні двох операндів не може бути випадку, коли Рк =1, тому що Рк є сигналом позики, тобто формується при відніманні. Блок керування (Фіг.2) працює в такий спосіб. У початковому стані Таблиця 1 ЗнА 0 0 0 0 0 0 1 1 1 1 1 1 ЗнВ 0 0 0 1 1 1 0 0 0 1 1 1 КОП 0 1 1 0 0 1 0 0 1 0 1 1 PК 0 0 1 0 1 0 0 1 0 0 0 1 Y 0 1 1 1 1 0 1 1 0 0 1 1 ЗнR 0 0 1 0 1 0 1 0 1 1 1 0 регістр зсуву 45 знаходиться в нульовому стані. З появою на вході 4 одиничного сигналу запуску відбувається запуск генератора 44 тактових імпульсів і запис одиниці в перший розряд регістра зсуву 45, що приводить до скидання у н ульовий стан RS-тригера 43 вузла 23 формування знака результату і до появи одиничного керуючого сигналу на виході 8, що дозволяє запис першого операнда А в суматор 1 по його інформаційних входах 18. З надходженням наступного тактового імпульсу відбувається зсув інформації на один розряд праворуч в регістрі зсуву 45, що приводить до появи одиничного керуючого сигналу на виході 10, який дозволяє запис другого операнда В в регістр 2. У третій такт роботи відбувається встановлення в одиничний стан третього розряду регістра зсуву 45, що викликає появу одиничних керуючих сигналів на вихода х 8 і 11, які дозволяють зчитування інформації з регістра 2 і запис її в суматор 1. На цей час на виході 20 вузла 22 аналізу співвідношення знаків операндів сформований сигнал Y, який дозволяє запис інформації в суматор 1 по його інформаційних входах 17. З появою сигналу позики Рк , що подається на вхід 13 блока 3 керування, у його вузлі 23 формується знак результату ЗнR, який записується по Sвходу в RS-тригер 43 цього вузла 23, а отже, з'являється на виході 14 блока 3 керування. Поява одиничного сигналу на виході 9 четвертого розряду регістра зсуву 45 дозволяє зчитування результату із суматора 1 по його інформаційних ви ходах 19. Одночасно з цим нульовий сигнал з'являється на виході елемента НІ 46 і відбувається заборона надходження тактових імпульсів через елемент І 47 на вхід регістра зсуву 45 і, таким чином, зупиняється робота пристрою. Суматор (Фіг.3), який розглянуто у вигляді одного десяткового розряду, працює в такий спосіб. Для готовності суматора 1 до запису інформації на шину 85 живлення подається напруга живлення. Для встановлення початкового стану на вхід 8 дозволу запису подається одиничний сигнал, при цьому при наявності нульового сигналу на вході 21 ознаки запису інформації суматора 1, на виході елемента рівнозначності 86 формується нульовий сигнал, а отже, RS-тригер 59 встановлюється в "одиничний" стан, а D-тригер 51 встановлюється в "нульовий" стан. В результаті на перший вхід елемента І 63 надходить "1" із прямого виходу RS-тригера 59, а на другий вхід надходить "1" з інверсного виходу D-тригера 51. Отже, на виході елемента І 63 з'являється високий потенціал, на виходах елементів І 62, 64, 65 з'являються низькі потенціали, на шині 94 фіксується високий потенціал, а на шині 95 - низький потенціал. Одночасно з цим відбувається збудження комірки 50 початкового стану. На катоді світлодіода 98 присутній "0", по колу шина 85 живлення - резистор 97 - світлодіод 98 тече струм, що збуджує світлодіод 98, який, у свою чергу, оптично діє на фотоприймач 77 комірки 50 початкового стану. Під дією цього зв'язку і високого потенціалу на шині 54 опір фотоприймача 77 різко зменшується й в результаті транзистор 69 відкривається. По колу джерело 70 світла-колектор-емітер транзистора 69 тече струм, джерело 70 світла випромінює світло, по колу ви хід 71фотоприймач 76 забезпечується позитивний зворотній зв'язок, комірка 50 початкового стану запам'ятовує інформацію, тобто зберігає одиничний сигнал. З ви ходу 72 джерела 70 світла комірки 50 початкового стану оптичний сигнал впливає на фотоприймач 77 наступної розрядної комірки 49.1, підготовляючи її до роботи. При виконанні операції додавання для запису операнду необхідно подати одиничний сигнал на вхід 8 дозволу запису і нульовий сигнал на вхід 21 ознаки запису інформації суматора 1, тобто на інверсний S-вхід RS-тригера 59 через елемент рівнозначності 86 подати низький потенціал, що встановлює його в "одиничний" стан. В результаті шини 53, 54, 94 підключені, а шини 55, 56, 95 відключені, крім того, шини 53 і 54, 57 і 58 мають високі потенціали попарно попереміннo, в залежності від величини тривалості сигналу на інформаційних входах 17 або 18. На перший вхід елемента І 87 через елемент АБО 93 з інформаційних входів 17 або 18 суматора 1 надходять інформаційні сигнали, а на його другий вхід надходять тактові імпульси зі входу 96. D-тригер 51 починає працювати в режимі лічби. З приходом одиничного сигналу з інформаційного входу 17 або 18, а отже, при наявності одиничного сигналу на виході елемента АБО 93 тактовий імпульс зі входу 96 через елементи І 87 і АБО 91 подається на С-вхід Dтригера 51. В результаті D-тригер 51 перейде в "одиничний" стан, тобто на його прямому виході з'являється "1", а на інверсному з'являється "0". В результаті на виході елемента І 63 з'явиться низький потенціал, тому що на його другий вхід надходить "0" з інверсного виходу D-тригера 51, а на виході елемента І 62 з'явиться високий потенціал, тому що на його перший вхід надходить "1" із прямого виходу RS-тригера 59, а на другий вхід надходить "1" із прямого виходу D-тригера 51. Під дією оптичного сигналу з виходу 72 джерела 70 світла комірки 50 початкового стану і високого потенціалу, що надходить з шини 53, опір фотоприймача 77 розрядної комірки 49.1 різко зменшується. В результаті транзистор 69 розрядної комірки 49.1 відкривається, по колу джерело 70 світла-колектор-емітер транзистора 69 тече стр ум, джерело 70 світла випромінює світло і через вихід 71 впливає на фотоприймач 76, забезпечуючи позитивний зворотній зв'язок. Розрядна комірка 49.1 запам'ятовує сигнал запису. Обнуління комірки 50 початкового стану відбувається завдяки наявності фотоприймача 79 та нульового потенціалу з шин 54, 56, 95, що приводить до запирання транзистора 69. З приходом наступного тактового імпульсу зі входу 96 D-тригер 51 перейде в нульовий стан, тобто на його прямому ви ході з'явиться "0", а на інверсному ви ході з'явиться "1". В результаті на шині 53 з'я виться низький потенціал, а на шині 54 з'явиться високий потенціал. Під дією оптичного зв'язку з ви ходу 72 розрядної комірки 49.1 на фотоприймач 77 розрядної комірки 49.2 і високого потенціалу з шини 54 опір фотоприймача 77 розрядної комірки 49.2 різко зменшується, транзистор 69 відкривається, записується одиничний сигнал у розрядну комірку 49.2 і обнулюється розрядна комірка 49.1 аналогічно наведеному вище. Аналогічним способом відбувається спрацювання наступних розрядних комірок 49.3,..., 49.9 суматора 1, тобто пряме (праворуч) просування одиничного сигналу. Кількість розрядних комірок 49.1,..., 49.9, що спрацювали, визначається тривалістю сигналу на інформаційних входах 17 або 18 суматора 1. При переповненні розрядної сітки суматора 1 одиниця переносу з'являється на оптичному виході 72 останньої розрядної комірки 49.9. При операції віднімання перший операнд записується як і при додаванні, а для запису другого операнда на інверсний S-вхід RS-тригера 59 подається одиничний потенціал, оскільки на входах елемента рівнозначності 86 присутні одиничні сигнали, а на інверсний R-вхід RS-тригера 59 подається нульовий потенціал, оскільки на вхід 9 дозволу зчитування подається нульовий сигнал, а на вхід 21 ознаки запису інформації суматора 1 подається одиничний сигнал, що формує нульовий сигнал на виході елемента АБО-НІ 90. В результаті RS-тригер 59 встановлюється в "н ульовий" стан, отже, шини 53, 54, 94 відключені, тобто мають низькі потенціали, а шини 55, 56, 95 підключені, крім того, шини 55 і 56, 57 і 58 мають високі потенціали попарно поперемінно, в залежності від величини тривалості сигналу на інформаційному вході 17. В результаті реалізуються зворотні зв'язки, тобто при відніманні другого операнда від записаного першого операнда стани розрядних комірок 49.1, ..., 49.9 змінюються у зворотному напрямку, що свідчить про зворотне (ліворуч) просування одиничного сигналу. Перед виконанням операції зчитування інформація записується як при додаванні, а потім на інверсний S-вхід RS-тригера 59 подається одиничний потенціал, оскільки на входах елемента рівнозначності присутні нульові сигнали, а на вхід 9 дозволу зчитування суматора 1 подається одиничний сигнал, який з виходу елемента АБО-НІ 90 як нульовий потенціал подається на інверсний R-вхід RS-тригера 59. Далі виконуються аналогічні дії, як при операції віднімання з тією різницею, що одиничний сигнал зі входу 9 дозволу зчитування суматора 1 запускає генератор 92 тактових імпульсів, який формує серію імпульсів тривалістю 9 t , де t -час спрацьовування однієї розрядної комірки 49.1,..., 49.9. Ці сигнали з'являються на виході елемента І 88 лише у випадку наявності нульового сигналу на виході елемента АБО 93, тобто коли відсутні сигнали на інформаційних входа х 17 і 18 суматора 1, що свідчить про відсутність будь-якого операнда на вході суматора 1. Отже, послідовність імпульсів з виходу генератора 92 тактових імпульсів через елементи І 88, АБО 91 подається на С-вхід D-тригера 51. В результаті відбувається зворотнє (ліворуч) просування одиничного сигналу у розрядних комірках 49.1, ..., 49.9 до їх обнуления. Одночасно тактові імпульси з виходу генератора 92 тактових імпульсів через елемент І 88 подаються на вхід елемента І 89 і з'являються на його виході за умови, що присутній ненульовий потенціал на колекторному виводі транзистора 69 комірки 50 початкового стану, а це можливо, коли в цій комірці відсутня інформація, тобто джерело 70 світла цієї комірки не випромінює світло. За час, що дорівнює рt, де р - кількість розрядних комірок, що спрацювали під час запису операнда перед зчитуванням, обнуляться всі р розрядних комірок 49.1,...,49.9 (р=1,...9), а головне, спрацює комірка 50 початкового стану, що призведе до припинення проходження сигналу на вихід елемента І 89, оскільки з колекторного виводу транзистора 69 цієї комірки на вхід елемента І 89 подається нульовий потенціал. Отже, на виході елемента І 89 буде сформовано одиничний сигнал тривалістю рt, який буде дорівнювати тривалості інформації, що зберігалась у суматорі 1. Таким чином у суматорі 1 пристрою виконується оброблення одного десяткового розряду операнда. При розрядності п десяткових операндів суматор 1 і регістр 2 містять відповідно n десяткових розрядів(Фіг.3), при цьому оброблення розрядів операндів виконується одночасно (паралельно), але послідовно по розрядних комірках 49.1,...,49.9. На часових діаграмах (Фіг.4) наведено приклад реалізації чотирьох операцій: а) запис числа А=3; б) додавання числа В=3; в) віднімання числа С=4; г) зчитування числа R=2. Отже, в якості операндів використано операнд А, як перший доданок, операнд В, як другий доданок, операнд С в якості від'ємника і операнд R в якості результату. З часових діаграм (Фіг.4) видно, що запис числа А=3 виконується за час tЗП=3t, додавання числа В=3 відбувається за час tДОД=3t, віднімання числа С=4 виконується за час tвід=4t і зчитування результату R=2 відбувається за tЗЧ=2t. Отже, максимальний час оброблення буде дорівнювати 9t без обмежень на розрядність n десяткових операндів.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice fir algebraically adding numbers

Автори англійськоюMartyniuk Tetiana Borysivna

Назва патенту російськоюУстройство для алгебраического суммирования чисел

Автори російськоюМартынюк Татьяна Борисовна

МПК / Мітки

МПК: G06F 7/50

Мітки: алгебраїчного, додавання, пристрій

Код посилання

<a href="https://ua.patents.su/9-22787-pristrijj-dlya-algebrachnogo-dodavannya.html" target="_blank" rel="follow" title="База патентів України">Пристрій для алгебраїчного додавання</a>

Попередній патент: Сирок на печиві глазурований

Наступний патент: Спосіб прогнозування перебігу туберкульозу у хворих на вперше діагностований туберкульоз легень, поєднаний з цукровим діабетом

Випадковий патент: Одяг для захисту від кровосисних і жалких комах