Адаптивний корелятор

Номер патенту: 36769

Опубліковано: 16.04.2001

Автори: Погрібний Володимир Олександрович, Грень Ярослав Володимирович, Рожанківський Ігор Володимирович

Текст

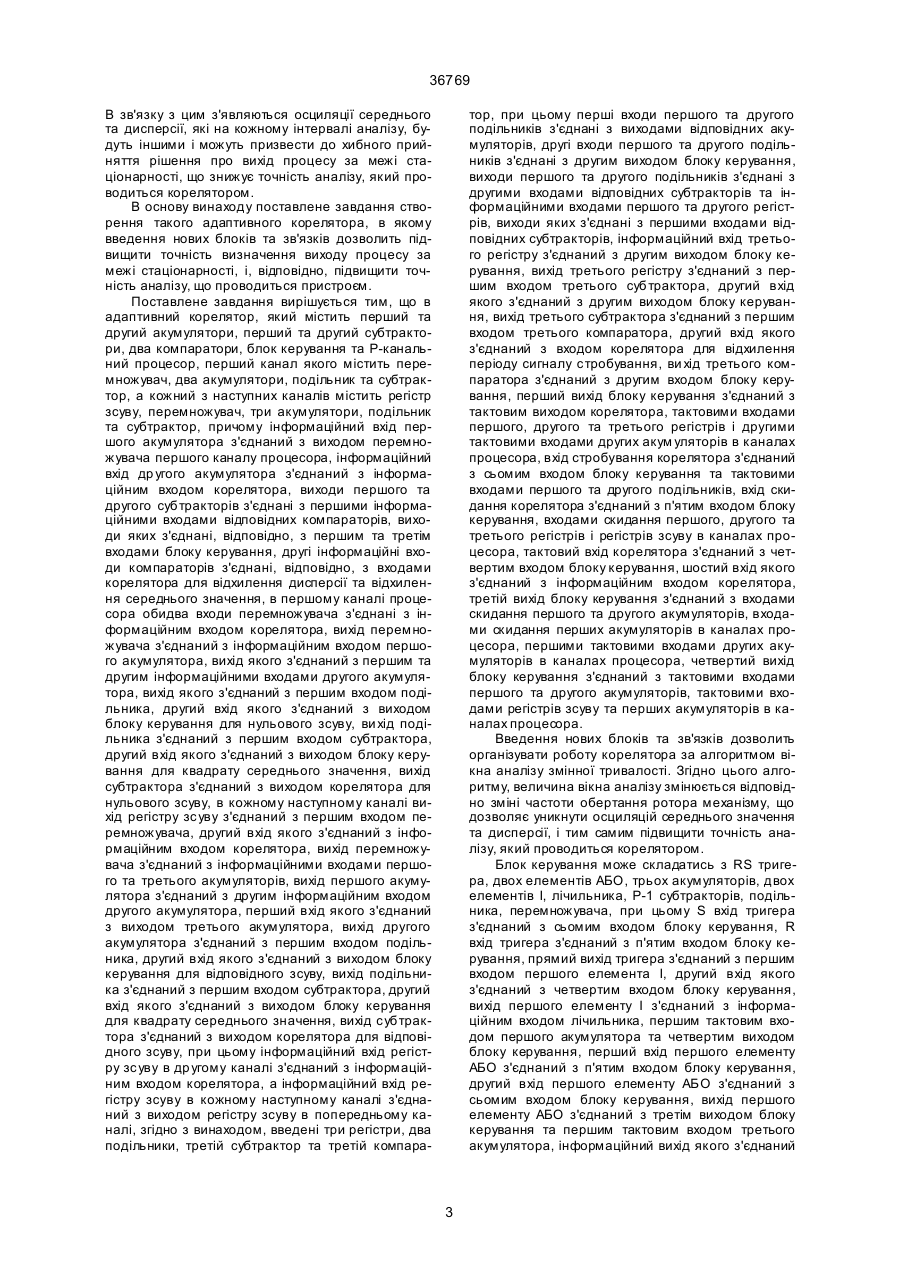

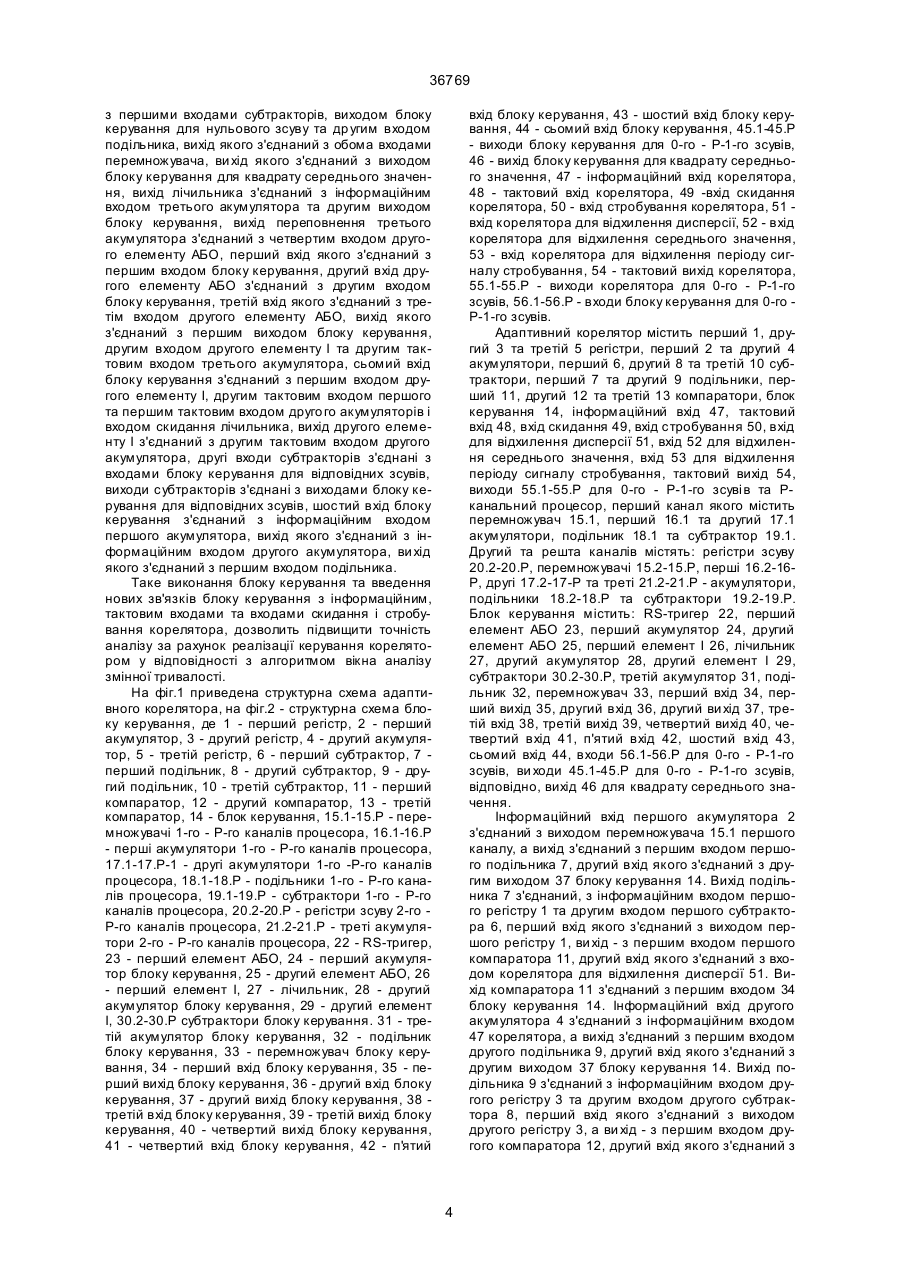

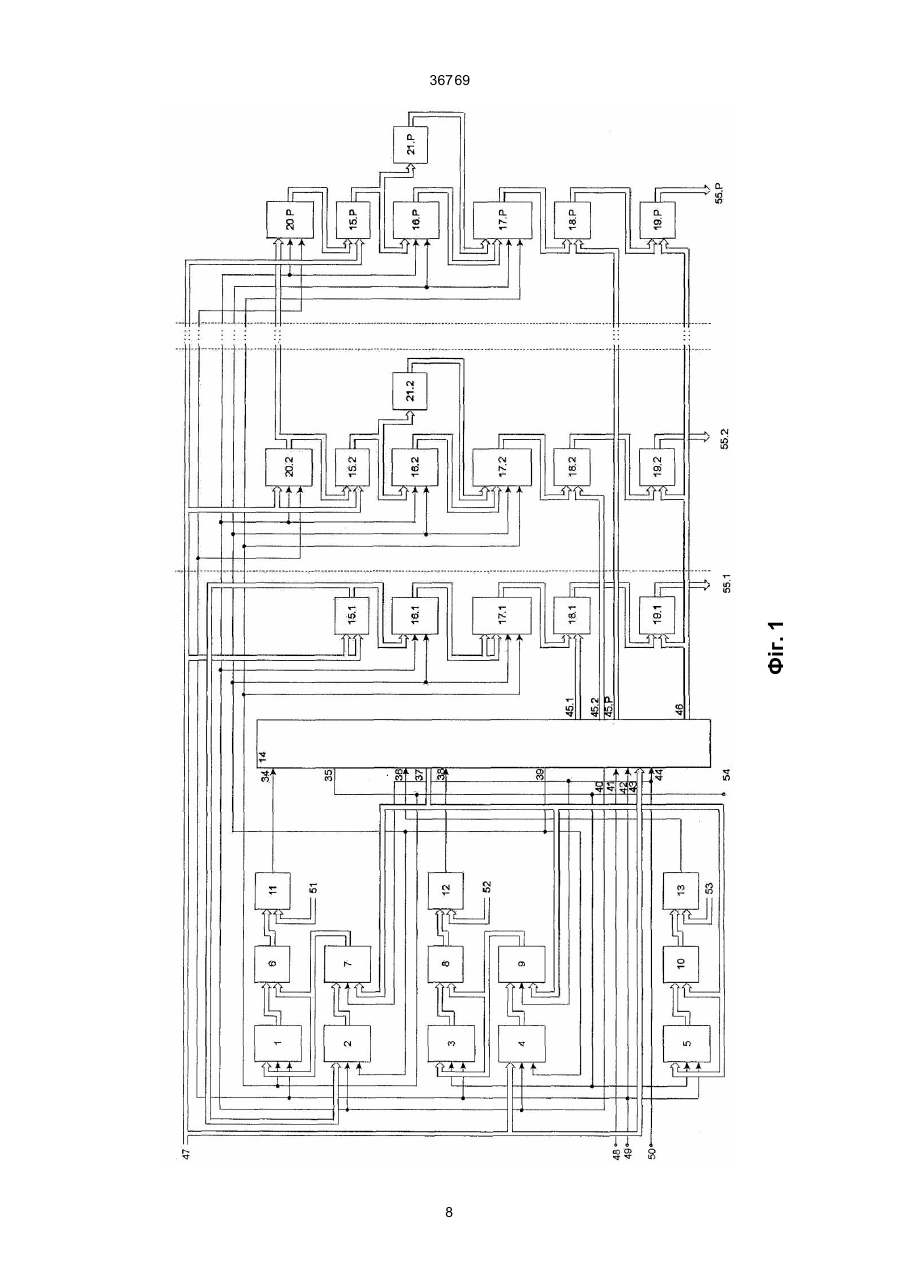

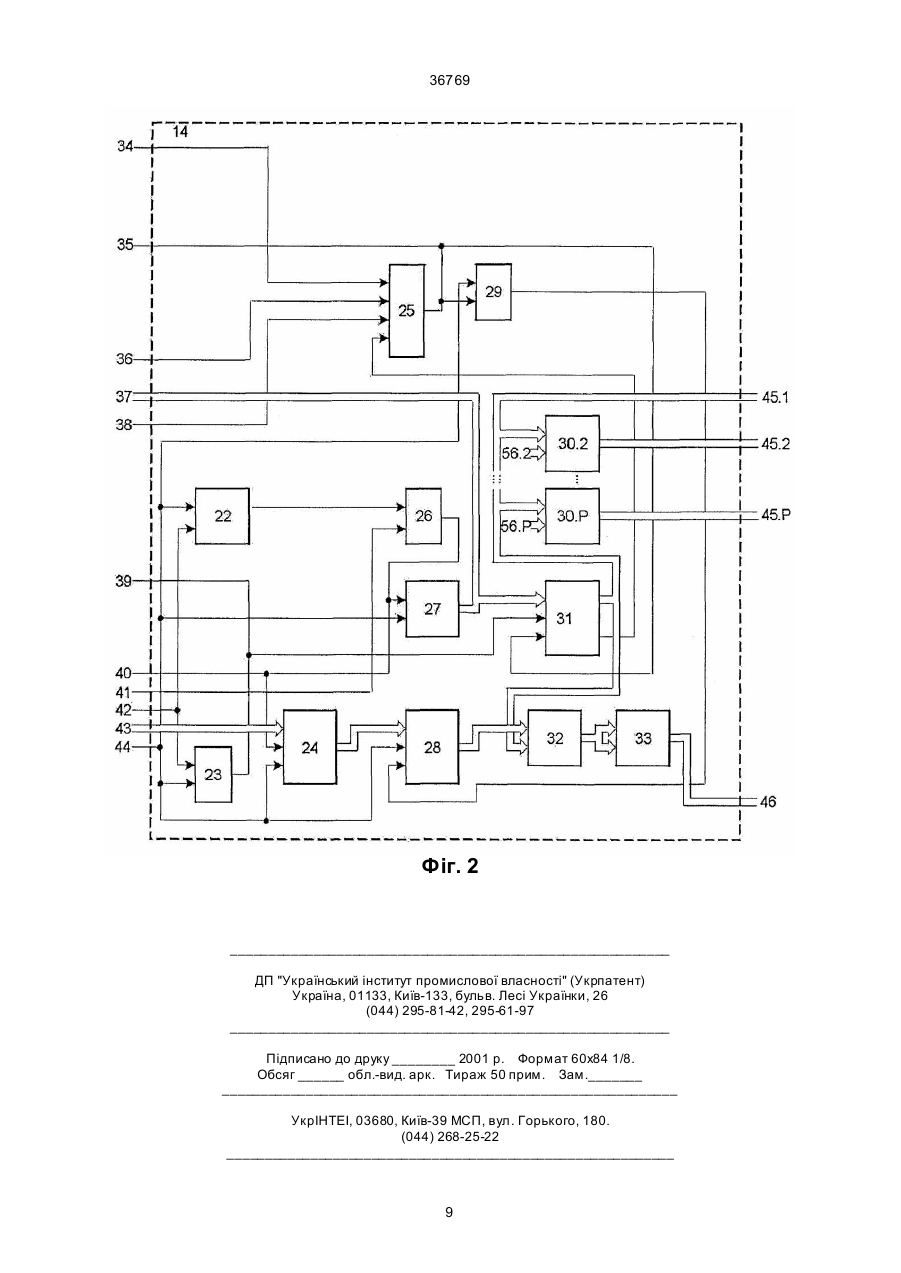

1. Адаптивний корелятор, що містить перший та другий акумулятори, перший та другий субтрактори, два компаратори, блок керування та Р-канальний процесор, перший канал якого містить перемножувач, два акумулятори, подільник та субтрактор, а кожний з наступних каналів містить регістр зсуву, перемножувач, три акумулятори, подільник та субтрактор, причому інформаційний вхід першого акумулятора з'єднаний з виходом перемножувача першого каналу процесора, інформаційний вхід другого акумулятора з'єднаний з інформаційним входом корелятора, виходи першого та другого субтракторів з'єднані з першими інформаційними входами відповідних компараторів, виходи яких з'єднані, відповідно, з першим та третім входами блоку керування, другі інформаційні входи компараторів з'єднані, відповідно, з входами корелятора для відхилення дисперсії та відхилення середнього значення, в першому каналі процесора обидва входи перемножувача з'єднані з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційним входом першого акумулятора, вихід якого з'єднаний з першим та другим інформаційними входами другого акумулятора, вихід якого з'єднаний з першим входом подільника, другий вхід якого з'єднаний з виходом блоку керування для нульового зсуву, ви хід подільника з'єднаний з першим входом субтрактора, другий вхід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід субтрактора з'єднаний з виходом корелятора для нульового зсуву, в кожному наступному каналі вихід регістру зсуву з'єднаний з першим входом перемножувача, другий вхід якого з'єднаний з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційними входами першого та третього акумуляторів, вихід першого акумулятора з'єднаний з другим інформаційним входом другого акумулятора, перший вхід якого з'єднаний з виходом третього акумулятора, вихід другого акумулятора з'єднаний з першим входом поділь A (54) АДАПТИВНИЙ КОРЕЛЯТОР 36769 першого та другого акумуляторів, тактовими входами регістрів зсуву та перших акумуляторів в каналах процесора. 2. Адаптивний корелятор за п. 1, який відрізняється тим, що блок керування містить RS тригер, два елементи АБО, три акумулятори, два елементи І, лічильник, Р-1 субтракторів, подільник, перемножувач, при цьому S вхід тригера з'єднаний з сьомим входом блоку керування, R вхід тригера з'єднаний з п'ятим входом блоку керування, прямий вихід тригера з'єднаний з першим входом першого елементу І, другий вхід якого з'єднаний з четвертим входом блоку керування, вихід першого елементу І з'єднаний з інформаційним входом лічильника, першим тактовим входом першого акумулятора та четвертим виходом блоку керування, перший вхід першого елементу АБО з'єднаний з п'ятим входом блоку керування, другий вхід першого елементу АБО з'єднаний з сьомим входом блоку керування, вихід першого елементу АБО з'єднаний з третім виходом блоку керування та першим тактовим входом третього акумулятора, інформаційний вихід якого з'єднаний з першими входами субтракторів, виходом блоку керування для нульового зсуву та др угим входом подільника, вихід якого з'єднаний з обома входами перемножувача, ви хід якого з'єднаний з виходом блоку ке рування для квадрату середнього значення, вихід лічильника з'єднаний з інформаційним входом третього акумулятора та другим ви ходом блоку керування, вихід переповнення третього акумулятора з'єднаний з четвертим входом другого елементу АБО, перший вхід якого з'єднаний з першим входом блоку керування, другий вхід другого елементу АБО з'єднаний з другим входом блоку керування, третій вхід якого з'єднаний з третім входом другого елементу АБО, ви хід якого з'єднаний з першим виходом блоку керування, другим входом другого елементу І та другим тактовим входом третього акумулятора, сьомий вхід блоку керування з'єднаний з першим входом другого елементу І, другим тактовим входом першого та першим тактовим входом другого акумуляторів і входом скидання лічильника, вихід другого елементу І з'єднаний з другим тактовим входом другого акумулятора, другі входи субтракторів з'єднані з входами блоку керування для відповідних зсувів, ви ходи субтракторів з'єднані з виходами блоку керування для відповідних зсувів, шостий вхід блоку керування з'єднаний з інформаційним входом першого акумулятора, вихід якого з'єднаний з інформаційним входом другого акумулятора, вихід якого з'єднаний з першим входом подільника. Винахід належить до інформаційно-вимірювальних систем та може бути використаний для кореляційного аналізу локально-стаціонарних випадкових процесів. Відомий адаптивний корелятор (Погрибной В.А., Рожанковский И.В., Джицимски 3., Собульски А. Адаптивный корреляционный анализ локально-стационарных случайных процесов // Известия высших учебных заведений. – Радиоэлектроника. 1996. - № 5. - С.24-32.), який містить перший та другий акумулятори, перший та другий субтрактори, два компаратори, блок керування та Р-канальний процесор, перший канал якого містить перемножувач, два акумулятори, подільник та субтрактор, а кожний з наступних каналів містить регістр зсуву, перемножувач, три акумулятори, подільник та субтрактор, причому інформаційний вхід першого акумулятора з'єднаний з виходом перемножувача першого каналу процесора, інформаційний вхід другого акумулятора з'єднаний з інформаційним входом корелятора, виходи першого та другого субтракторів з'єднані з першими інформаційними входами відповідних компараторів, виходи яких з'єднані відповідно з першим та третім входами блоку керування, другі інформаційні входи компараторів з'єднані, відповідно, з входами корелятора для відхилення дисперсії та відхилення середнього значення, в першому каналі процесора обидва входи перемножувача з'єднані з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційним входом першого акумулятора, вихід якого з'єднаний з першим та другим інформаційними входами другого акумулятора, вихід якого з'єднаний з першим входом подільника, другий вхід якого з'єднаний з виходом блоку керування для нульового зсуву, вихід подільника з'єднаний з першим входом субтра ктора, другий вхід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід субтрактора з'єднаний з виходом корелятора для нульового зсуву, в кожному наступному каналі вихід регістр у зсуву з'єднаний з першим входом перемножувача, другий вхід якого з'єднаний з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційними входами першого та третього акумуляторів, вихід першого акумулятора з'єднаний з другим інформаційним входом другого акумулятора, перший вхід якого з'єднаний з виходом третього акумулятора, вихід другого акумулятора з'єднаний з першим входом подільника, другий вхід якого з'єднаний з виходом блоку керування для відповідного зсуву, ви хід подільника з'єднаний з першим входом субтрактора, другий вхід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід субтрактора з'єднаний з виходом корелятора для відповідного зсуву, при цьому інформаційний вхід регістру зсуву в др угому каналі з'єднаний з інформаційним входом корелятора, а інформаційний вхід регістр у зсуву в кожному наступному каналі з'єднаний з виходом регістру зсуву в попередньому каналі. Відомий адаптивний корелятор працює за алгоритмом, який визначає ділянку локальної стаціонарності як суму чергових, рівних за довжиною елементарних стаціонарних інтервалів випадкового сигналу. Сигнали вібрацій обертових механізмів містять так звану обертову складову, частота якої рівна частоті обертання ротора машини. При дослідженні випадкових вібраційних сигналів зі змінною частотою, використання цього алгоритму призводить до значного спотворення їх статистичних параметрів. Це обумовлено тим, що розмір вікна аналізу не є кратним періоду обертової складової. 2 36769 В зв'язку з цим з'являються осциляції середнього та дисперсії, які на кожному інтервалі аналізу, будуть іншими і можуть призвести до хибного прийняття рішення про вихід процесу за межі стаціонарності, що знижує точність аналізу, який проводиться корелятором. В основу винаходу поставлене завдання створення такого адаптивного корелятора, в якому введення нових блоків та зв'язків дозволить підвищити точність визначення виходу процесу за межі стаціонарності, і, відповідно, підвищити точність аналізу, що проводиться пристроєм. Поставлене завдання вирішується тим, що в адаптивний корелятор, який містить перший та другий акумулятори, перший та другий субтрактори, два компаратори, блок керування та Р-канальний процесор, перший канал якого містить перемножувач, два акумулятори, подільник та субтрактор, а кожний з наступних каналів містить регістр зсуву, перемножувач, три акумулятори, подільник та субтрактор, причому інформаційний вхід першого акумулятора з'єднаний з виходом перемножувача першого каналу процесора, інформаційний вхід др угого акумулятора з'єднаний з інформаційним входом корелятора, виходи першого та другогосубтракторів з'єднані з першими інформаційними входами відповідних компараторів, виходи яких з'єднані, відповідно, з першим та третім входами блоку керування, другі інформаційні входи компараторів з'єднані, відповідно, з входами корелятора для відхилення дисперсії та відхилення середнього значення, в першому каналі процесора обидва входи перемножувача з'єднані з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційним входом першого акумулятора, вихід якого з'єднаний з першим та другим інформаційними входами другого акумулятора, вихід якого з'єднаний з першим входом подільника, другий вхід якого з'єднаний з виходом блоку керування для нульового зсуву, ви хід подільника з'єднаний з першим входом субтрактора, другий вхід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід субтрактора з'єднаний з виходом корелятора для нульового зсуву, в кожному наступному каналі вихід регістру зсуву з'єднаний з першим входом перемножувача, другий вхід якого з'єднаний з інформаційним входом корелятора, вихід перемножувача з'єднаний з інформаційними входами першого та третього акумуляторів, вихід першого акумулятора з'єднаний з другим інформаційним входом другого акумулятора, перший вхід якого з'єднаний з виходом третього акумулятора, вихід другого акумулятора з'єднаний з першим входом подільника, другий вхід якого з'єднаний з виходом блоку керування для відповідного зсуву, вихід подільника з'єднаний з першим входом субтрактора, другий вхід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід субтрактора з'єднаний з виходом корелятора для відповідного зсуву, при цьому інформаційний вхід регістру зсуву в др угому каналі з'єднаний з інформаційним входом корелятора, а інформаційний вхід регістру зсуву в кожному наступному каналі з'єднаний з виходом регістру зсуву в попередньому каналі, згідно з винаходом, введені три регістри, два подільники, третій субтрактор та третій компара тор, при цьому перші входи першого та другого подільників з'єднані з виходами відповідних акумуляторів, другі входи першого та другого подільників з'єднані з другим виходом блоку керування, виходи першого та другого подільників з'єднані з другими входами відповідних субтракторів та інформаційними входами першого та другого регістрів, виходи яких з'єднані з першими входами відповідних субтракторів, інформаційний вхід третього регістру з'єднаний з другим виходом блоку керування, вихід третього регістру з'єднаний з першим входом третього субтрактора, другий вхід якого з'єднаний з другим виходом блоку керування, вихід третього субтрактора з'єднаний з першим входом третього компаратора, другий вхід якого з'єднаний з входом корелятора для відхилення періоду сигналу стробування, ви хід третього компаратора з'єднаний з другим входом блоку керування, перший вихід блоку керування з'єднаний з тактовим виходом корелятора, тактовими входами першого, другого та третього регістрів і другими тактовими входами других акум уляторів в каналах процесора, вхід стробування корелятора з'єднаний з сьомим входом блоку керування та тактовими входами першого та другого подільників, вхід скидання корелятора з'єднаний з п'ятим входом блоку керування, входами скидання першого, другого та третього регістрів і регістрів зсуву в каналах процесора, тактовий вхід корелятора з'єднаний з четвертим входом блоку керування, шостий вхід якого з'єднаний з інформаційним входом корелятора, третій вихід блоку керування з'єднаний з входами скидання першого та другого акумуляторів, входами скидання перших акумуляторів в каналах процесора, першими тактовими входами других акумуляторів в каналах процесора, четвертий вихід блоку керування з'єднаний з тактовими входами першого та другого акумуляторів, тактовими входами регістрів зсуву та перших акумуляторів в каналах процесора. Введення нових блоків та зв'язків дозволить організувати роботу корелятора за алгоритмом вікна аналізу змінної тривалості. Згідно цього алгоритму, величина вікна аналізу змінюється відповідно зміні частоти обертання ротора механізму, що дозволяє уникнути осциляцій середнього значення та дисперсії, і тим самим підвищити точність аналізу, який проводиться корелятором. Блок керування може складатись з RS тригера, двох елементів АБО, трьох акумуляторів, двох елементів І, лічильника, Р-1 субтракторів, подільника, перемножувача, при цьому S вхід тригера з'єднаний з сьомим входом блоку керування, R вхід тригера з'єднаний з п'ятим входом блоку керування, прямий вихід тригера з'єднаний з першим входом першого елемента І, другий вхід якого з'єднаний з четвертим входом блоку керування, вихід першого елементу І з'єднаний з інформаційним входом лічильника, першим тактовим входом першого акумулятора та четвертим виходом блоку керування, перший вхід першого елементу АБО з'єднаний з п'ятим входом блоку керування, другий вхід першого елементу АБО з'єднаний з сьомим входом блоку керування, вихід першого елементу АБО з'єднаний з третім виходом блоку керування та першим тактовим входом третього акумулятора, інформаційний вихід якого з'єднаний 3 36769 з першими входами субтракторів, виходом блоку керування для нульового зсуву та др угим входом подільника, вихід якого з'єднаний з обома входами перемножувача, ви хід якого з'єднаний з виходом блоку керування для квадрату середнього значення, вихід лічильника з'єднаний з інформаційним входом третього акумулятора та другим виходом блоку керування, вихід переповнення третього акумулятора з'єднаний з четвертим входом другого елементу АБО, перший вхід якого з'єднаний з першим входом блоку керування, другий вхід другого елементу АБО з'єднаний з другим входом блоку керування, третій вхід якого з'єднаний з третім входом другого елементу АБО, вихід якого з'єднаний з першим виходом блоку керування, другим входом другого елементу І та другим тактовим входом третього акумулятора, сьомий вхід блоку керування з'єднаний з першим входом другого елементу І, другим тактовим входом першого та першим тактовим входом друго го акумуляторів і входом скидання лічильника, вихід другого елементу І з'єднаний з другим тактовим входом другого акумулятора, другі входи субтракторів з'єднані з входами блоку керування для відповідних зсувів, виходи субтракторів з'єднані з виходами блоку керування для відповідних зсувів, шостий вхід блоку керування з'єднаний з інформаційним входом першого акумулятора, вихід якого з'єднаний з інформаційним входом другого акумулятора, ви хід якого з'єднаний з першим входом подільника. Таке виконання блоку керування та введення нових зв'язків блоку керування з інформаційним, тактовим входами та входами скидання і стробування корелятора, дозволить підвищити точність аналізу за рахунок реалізації керування корелятором у відповідності з алгоритмом вікна аналізу змінної тривалості. На фіг.1 приведена структурна схема адаптивного корелятора, на фіг.2 - структурна схема блоку керування, де 1 - перший регістр, 2 - перший акумулятор, 3 - другий регістр, 4 - другий акумулятор, 5 - третій регістр, 6 - перший субтрактор, 7 перший подільник, 8 - другий субтрактор, 9 - другий подільник, 10 - третій субтрактор, 11 - перший компаратор, 12 - другий компаратор, 13 - третій компаратор, 14 - блок керування, 15.1-15.Р - перемножувачі 1-го - Р-го каналів процесора, 16.1-16.Р - перші акумулятори 1-го - Р-го каналів процесора, 17.1-17.Р-1 - другі акумулятори 1-го -Р-го каналів процесора, 18.1-18.Р - подільники 1-го - Р-го каналів процесора, 19.1-19.Р - субтрактори 1-го - Р-го каналів процесора, 20.2-20.Р - регістри зсуву 2-го Р-го каналів процесора, 21.2-21.Р - треті акумулятори 2-го - Р-го каналів процесора, 22 - RS-тригер, 23 - перший елемент АБО, 24 - перший акумулятор блоку керування, 25 - другий елемент АБО, 26 - перший елемент І, 27 - лічильник, 28 - другий акумулятор блоку керування, 29 - другий елемент І, 30.2-30.Р субтрактори блоку керування. 31 - третій акумулятор блоку керування, 32 - подільник блоку керування, 33 - перемножувач блоку керування, 34 - перший вхід блоку керування, 35 - перший вихід блоку керування, 36 - другий вхід блоку керування, 37 - другий вихід блоку керування, 38 третій вхід блоку керування, 39 - третій вихід блоку керування, 40 - четвертий вихід блоку керування, 41 - четвертий вхід блоку керування, 42 - п'ятий вхід блоку керування, 43 - шостий вхід блоку керування, 44 - сьомий вхід блоку керування, 45.1-45.Р - виходи блоку керування для 0-го - P-1-го зсувів, 46 - вихід блоку керування для квадрату середнього значення, 47 - інформаційний вхід корелятора, 48 - тактовий вхід корелятора, 49 -вхід скидання корелятора, 50 - вхід стробування корелятора, 51 вхід корелятора для відхилення дисперсії, 52 - вхід корелятора для відхилення середнього значення, 53 - вхід корелятора для відхилення періоду сигналу стробування, 54 - тактовий вихід корелятора, 55.1-55.Р - виходи корелятора для 0-го - P-1-го зсувів, 56.1-56.Р - входи блоку керування для 0-го P-1-го зсувів. Адаптивний корелятор містить перший 1, другий 3 та третій 5 регістри, перший 2 та другий 4 акумулятори, перший 6, другий 8 та третій 10 субтрактори, перший 7 та другий 9 подільники, перший 11, другий 12 та третій 13 компаратори, блок керування 14, інформаційний вхід 47, тактовий вхід 48, вхід скидання 49, вхід стробування 50, вхід для відхилення дисперсії 51, вхід 52 для відхилення середнього значення, вхід 53 для відхилення періоду сигналу стробування, тактовий вихід 54, виходи 55.1-55.Р для 0-го - P-1-го зсуві в та Рканальний процесор, перший канал якого містить перемножувач 15.1, перший 16.1 та другий 17.1 акумулятори, подільник 18.1 та субтрактор 19.1. Другий та решта каналів містять: регістри зсуву 20.2-20.Р, перемножувачі 15.2-15.Р, перші 16.2-16Р, другі 17.2-17-Р та треті 21.2-21.Р - акумулятори, подільники 18.2-18.Р та субтрактори 19.2-19.Р. Блок керування містить: RS-тригер 22, перший елемент АБО 23, перший акумулятор 24, другий елемент АБО 25, перший елемент І 26, лічильник 27, другий акумулятор 28, другий елемент І 29, субтрактори 30.2-30.Р, третій акумулятор 31, подільник 32, перемножувач 33, перший вхід 34, перший вихід 35, другий вхід 36, другий ви хід 37, третій вхід 38, третій вихід 39, четвертий вихід 40, четвертий вхід 41, п'ятий вхід 42, шостий вхід 43, сьомий вхід 44, входи 56.1-56.Р для 0-го - P-1-го зсувів, ви ходи 45.1-45.Р для 0-го - P-1-го зсувів, відповідно, вихід 46 для квадрату середнього значення. Інформаційний вхід першого акумулятора 2 з'єднаний з виходом перемножувача 15.1 першого каналу, а вихід з'єднаний з першим входом першого подільника 7, другий вхід якого з'єднаний з другим виходом 37 блоку керування 14. Вихід подільника 7 з'єднаний, з інформаційним входом першого регістру 1 та другим входом першого субтрактора 6, перший вхід якого з'єднаний з виходом першого регістру 1, ви хід - з першим входом першого компаратора 11, другий вхід якого з'єднаний з входом корелятора для відхилення дисперсії 51. Вихід компаратора 11 з'єднаний з першим входом 34 блоку керування 14. Інформаційний вхід другого акумулятора 4 з'єднаний з інформаційним входом 47 корелятора, а вихід з'єднаний з першим входом другого подільника 9, другий вхід якого з'єднаний з другим виходом 37 блоку керування 14. Вихід подільника 9 з'єднаний з інформаційним входом другого регістру 3 та другим входом другого субтрактора 8, перший вхід якого з'єднаний з виходом другого регістру 3, а ви хід - з першим входом другого компаратора 12, другий вхід якого з'єднаний з 4 36769 входом корелятора для відхилення середнього значення 52. Вихід другого компаратора 12 з'єднаний з третім входом 38 блоку керування 14. Інформаційний вхід 47 корелятора з'єднаний з шостим входом 43 блоку керування 14, другий ви хід якого з'єднаний з інформаційним входом третього регістру 5 та другим входом субтрактора 10. Перший вхід субтрактора 10 з'єднаний з виходом третього регістру 5, а вихід - з першим входом третього компаратора 13, другий вхід якого з'єднаний з входом 53 корелятора для відхилення періоду сигналу стробування, а ви хід - з др угим входом 36 блоку керування 14. В першому каналі процесора обидва входи перемножувача 15.1 з'єднані з інформаційним входом 47 корелятора, а вихід з'єднаний з інформаційним входом першого акумулятора 16.1, вихід якого з'єднаний з двома інформаційними входами другого акумулятора 17.1. В другому каналі інформаційний вхід регістру зсуву 20.2 з'єднаний з інформаційним входом 47 корелятора, а в решті каналів інформаційні входи регістрів зсуву 20.3-20.Р з'єднані з виходами аналогічних регістрів зсуву в попередньому каналі. Виходи регістрів зсуву 20.2-20.Р в другому та решті каналів з'єднані з першими інформаційними входами перемножувачів 15.2-15.Р, другі ін формаційні входи яких з'єднані з інформаційним входом 47 корелятора, а виходи з інформаційними входами перших 16.216.Р та третіх 21.2-21.Р акумуляторів. Виходи перших акумуляторів 16.2-16.Р з'єднані з другим інформаційним входом других акумуляторів 17.217.Р, перші інформаційні входи яких з'єднані з виходами третіх акумуляторів 21.2-21.Р. У всі х каналах процесора виходи други х акумуляторів 17.117.Р з'єднані з першими інформаційними входами субтракторів 18.1-18.Р, другі інформаційні входи яких з'єднані з виходами блоку керування для 0-гоР-1-го зсувів 45.1-45.Р, а виходи - з першими інформаційними входами подільників 19.1-19.Р. Другі ін формаційні входи подільників 19.1-19.Р з'єднані з виходом блоку керування для квадрату середнього значення 46, а виходи подільників є виходами корелятора 0-го-Р-1 зсувів. Перший вихід 35 блоку керування 14 з'єднаний з тактовим виходом 24 корелятора, тактовими входами першого 1, другого 3 та третього 5 регістрів і другими тактовими входами других акумуляторів 17.1-17.Р в каналах процесора. Вхід стробування 50 корелятора з'єднаний з сьомим входом 44 блоку керування 14 та тактовими входами першого 7 та другого 9 подільників, вхід скидання 49 корелятора з'єднаний з п'ятим входом 42 блоку керування 14, входами скидання першого 1, другого 3 та третього 5 регістрів і регістрів зсуву 20.220.Р в каналах процесора. Тактовий вхід корелятора 48 з'єднаний з четвертим входом 41 блоку керування 14. Третій вихід 39 блоку керування 14 з'єднаний з входами скидання першого 2 та другого 4 акумуляторів, входами скидання перших 16.116.Р акумуляторів в каналах процесора, першими тактовими входами других 17.1-17.Р акумуляторів в каналах процесора. Четвертий вихід 40 блоку керування 14 з'єднаний з тактовими входами першого 2 та другого 4 акумуляторів, тактовими входами регістрів зсуву 20.2-20.Р та перших акумуляторів 17.1-17.Р в каналах процесора. S вхід RS тригера 22 з'єднаний з сьомим вхо дом 44 блоку керування 14. R вхід RS тригера 22 з'єднаний з п'ятим входом 42 блоку керування 14. Прямий RS вихід тригера 22 з'єднаний з першим входом першого 26 елемента І, другий вхід якого з'єднаний з четвертим входом 41 блоку керування 14. Вихід першого 26 елементу І з'єднаний з інформаційним входом лічильника 27, першим тактовим входом першого акумулятора 24 та четвертим виходом 40 блоку керування 14. Перший вхід першого 23 елементу АБО з'єднаний з п'ятим входом 42 блоку керування 14, другий вхід першого 23 елементу АБО з'єднаний з сьомим входом 44 блоку керування 14. В вихід першого 23 елементу АБО з'єднаний з третім виходом 39 блоку керування 14 та першим тактовим входом третього 31 акумулятора, вихід якого з'єднаний з першими інформаційними входами субтракторів 30.2-30.Р, виходом блоку керування для нульового зсуву 45.1 та другим входом подільника 32, вихід якого з'єднаний з обома входами перемножувача 33, вихід якого з'єднаний з виходом блоку керування для квадрату середнього значення 46. Вихід лічильника 27 з'єднаний з інформаційним входом третього 31 акумулятора та другим виходом 37 блоку керування 14. Вихід переповнення третього акумулятора 31 з'єднаний з четвертим входом другого 25 елементу АБО, перший вхід якого з'єднаний з першим входом 34 блоку керування 14, другий - з другим входом 36 блоку керування 14, третій вхід якого з'єднаний з третім входом другого 25 елементу АБО, ви хід якого з'єднаний з першим виходом 35 блоку керування 14, другим входом другого 29 елементу І та другим тактовим входом третього 31 акумулятора. Сьомий вхід 44 блоку керування 14 з'єднаний з першим входом другого 29 елементу І, другим тактовим входом першого 24 та першим тактовим входом другого 28 акумуляторів і входом скидання лічильника 27. Вихід другого 29 елементу І з'єднаний з другим тактовим входом другого 28 акумулятора. Другі інформаційні входи субтракторів 30.2-30.Р з'єднані з входами блоку керування 14 для відповідних зсувів 56.2-56.Р. Виходи субтракторів 30.2-30.Р з'єднані з виходами блоку керування 14 для відповідних зсувів 45.2-45.Р, шостий вхід 43 блоку керування 14 з'єднаний з інформаційним входом першого 24 акумулятора, вихід якого з'єднаний з інформаційним входом другого 28 акумулятора, вихід якого з'єднаний з першим входом подільника 32. Адаптивний корелятор працює наступним чином. З появою першого імпульсу опорного сигналу на вході стробування 50 корелятора починається формування першого довірчого інтервалу. СумуNвік 2 вання з нагромадженням x та = 1 a N вік x , де N вік - величина вікна аналізу, xa = 1 a a - відлік сигналу, здійснюється в першому 2 та другому 4 акумуляторах, відповідно. Одночасно починається робота процесора, в кожному з Р каналів якого вираховується оцінка кореляційної функції для відповідних часових зсувів m, які забезпечуються регістрами зсуву 20.2 - 20.Р. Добуток å å x a x a-m формується в перемножувачах 15.1-15.Р і нагромаджується в акумуляторах 16.1-16.Р. Після 5 36769 закінченні формування першого довірчого інтервалу блок керування 14 генерує тактовий сигнал і сума відліків, яка нагромаджена в першому 2 та другому 4 акумуляторах і поділена в першому 7 та другому 9 подільниках на кількість відліків вікна аналізу, переписується в перший 1 та другий 3 регістри для зберігання там до закінчення стаціонарної ділянки. Одночасно в третій регістр 5 записується значення кількості відліків вікна аналізу, що обернено пропорційна частоті опорного сигналу. Після закінчення формування довірчого інтервалу перший 2 та др угий 4 акумулятори очищуються. Одночасно в кожному каналі процесора результат обчислень з перших акумуляторів 16.116.Р переписується в другі акумулятори 17.1-17.Р, які забезпечують нагромадження добутків i -m x x , де і - кількість відліків від почат= 1 a a +m a ку інтервалу аналізу до початку поточного вікна аналізу. Одночасно з цим очищуються перші акумулятори 16.1-16.Р в кожному каналі процесора, а на відповідних виходах 45.1-45.Р блоку керування 2 встановлюються значення i-m та x A , які використовуються лише в момент закінчення інтервалу аналізу. В наступному вікні аналізу (поточному інтервалі) в першому 2 та др угому 4 акумуляторах корелятора нагромаджуються i + Nвік 2 i + Nвік суми x та x . Після закінa= i +1 a a= i +1 a чення поточного інтервалу вміст цих акумуляторів ділиться на кількість відліків вікна аналізу в першому 7 та др угому 9 подільниках відповідно, а отримані результати віднімаються від вмісту першого 1 та другого 3 регістрів у першому 6 та другому 8 субтракторах відповідно. Отримані різниці муляторів 17.1-17.Р надходить тактовий імпульс і нагромадженні в цих акумуляторах суми i x x діляться в подільниках 18.1-18.Р = 1 a a -m a на відповідні значення і-m. Від отриманого значення в субтракторах 19.1-19.Р віднімається квадрат 2 середнього значення x A і на виходах корелятора для 0-го 55.1 - Р-го 55.Р отримаємо значення кореляційної функції для відповідного часового зсуву. З надходженням тактового сигналу на другий тактовий вхід други х 17.2-17.Р акумуляторів другого - Р-го каналів ці акумулятори очищаються і в них переписується вміст третіх 21.2-21.Р акумуляторів другого - Р-го каналів процесора, відповідно. Оскільки в першому каналі часовий зсув дорівнює 0, то в другий 17.1 переписується значення з виходу першого акумулятора 16.1. Одночасно з цим очищуються перші акумулятори 16.1-16.Р. Після цього повторюється робота корелятора на першому інтервалі аналізу. Блок керування працює наступним чином. Перед початком роботи корелятора сигналом загального скидання обнулюються всі регістри 1, 3, 5, 20.2-20.Р та акумулятори 2, 4, 16.1-16.Р, 17.217.Р, 21.2-21.Р, 24, 28, 31, a RS-тригер 22 встановлюється в "0". Цим самим через перший елемент І 26 блокується тактовий вхід 48 корелятора, який залишається заблокованим до появи першого імпульсу на вході стробування 50 корелятора. Цим імпульсом RS-тригер 22 перекидається в "1" і тактовий вхід корелятора 48 розблоковується. Блокування необхідне для запобігання прийняття за довірчий інтервал інтервалу, що не рівний періоду опорного сигналу. З розблокуванням тактового входу 48 починається робота корелятора. В лічильнику 27 визначається кількість відліків вікна аналізу (кількість відліків між двома імпульсами опорного сигналу). З надходженням кожного нового опорного імпульсу лічильник 27 обнулюється, а значення з його виходу додається до вмісту третього акумулятора 31, в якому визначається кількість відліків інтервалу аналізу. Третій акумулятор 31 працює наступним чином: дані з його інформаційного входу, які надходять разом з тактовими імпульсами на його перший тактовий вхід акумулятора, додаються до вмісту акумулятора 31. Якщо тактовий імпульс надходить на другий тактовий вхід, то на вихід акумулятора 31 виставляється його вміст, а сам акумулятор 31 очищається і в нього записуються дані з інформаційного входу. Акумулятор має вихід переповнення, а місткість цього акумулятора 31 визначає довжину інтервалу аналізу. В першому акумуляторі 24 блоку керування визначається сума відліків вікна налізу. Ак умулятор 24 працює наступним чином: дані з його інформаційного входу, які надходять разом з тактовими імпульсами на його перший тактовий вхід додаються до вмісту акумулятора 24. Якщо тактовий імпульс надходить на другий тактовий вхід, то на вихід акумулятора 24 виставляється його вміст, а сам акумулятор 24 очищається. В другому акумуляторі 28 блоку керування визначається сума відліків інтервалу аналізу. Акумулятор 28 працює наступним чином: дані з його інформаційного входу, які надходять разом з такто {å { {å å å порівнюються з допустимими відхиленнями eD та ex у першому 11 та другому 12 компараторах, відповідно. Результати порівняння поступають, відповідно, на перший 34 та третій 38 входи блоку керування 14. Одночасно в третьому субтракторі 10 від вмісту третього регістру 5 віднімається кількість відліків вікна аналізу. Отримана різниця порівнюються з допустимим відхиленням ef у тре тьому компараторі 13. Результат порівняння поступає на другий вхід 36 блоку керування 14. Якщо блок керування 14 приймає рішення про стаціонарність ділянки реалізації то повторюється робота корелятора, описана вище. Якщо система керування приймає рішення про закінчення інтервалу аналізу (вихід процесу за межі стаціонарності, зміна робочої швидкості вища за допустиму межу, або переповнення лічильника 27), то значення з виходів першого 2 та другого 4 акумуляторів переписуються в перший 1 та другий 3 регістри, відповідно, а акумулятори 2 та 4 очищаються. Одночасно значення кількості відліків вікна аналізу записується в третій регістр 5. Таким чином, інтервал, що перекривається вікном аналізу в даний момент стає новим довірчим інтервалом. В цей час на другий тактовий вхід других аку 6 36769 вими імпульсами на його перший тактовий вхід, додаються до вмісту акумулятора 28. Якщо тактовий імпульс надходить на другий тактовий вхід, то на вихід акумулятора 28 виставляється його вміст, а сам акумулятор 28 очищається і в нього записуються дані з інформаційного входу. В подільнику 32 визначається середнє значення сигналу на інтервалі аналізу, а в перемножувачі 33 воно підноситься до квадрату. В субтракторах 30.2-30.Р визначаються значення і-m для відповідного каналу. Результати порівняння контрольованих параметрів (дисперсії, середнього значення, величини вікна) з відповідними допустимими відхиленнями та сигнал переповнення третього акумулятора 31 блоку керування поступають на входи першого 23 елемента АБО. Якщо хоч один з цих сигналів свідчить про перевищення допустимого відхилення то приймається рішення про закінчення інтервалу аналізу в кінці попереднього поточного інтервалу, а інтервал, який перекривається вікном стає новим довірчим інтервалом. Щоб рішення про закінчення інтервалу аналізу не було прийняте при несформованому вікні аналізу, в схемі передбачено другий 29 елемент І. Перший 23 елемент АБО забезпечує обнулення відповідних блоків як опорним сигналом, так і сигналом загального скидання. Тактовий вихід 54 корелятора є тактовим виходом для кореляційної функції. 7 Фіг. 1 36769 8 36769 Фіг. 2 __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2001 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 9

ДивитисяДодаткова інформація

Назва патенту англійськоюAdaptive correlator

Автори англійськоюHren Yaroslav Volodymyrovych, Pohribnyy Volodymyr Oleksandrovych, Rozhankivskyy Ihor Volodymyrovych

Назва патенту російськоюАдаптивный коррелятор

Автори російськоюГрень Ярослав Владимирович, Погрибный Владимир Александрович, Рожанковский Игорь Владимирович

МПК / Мітки

МПК: G06F 15/00

Мітки: корелятор, адаптивний

Код посилання

<a href="https://ua.patents.su/9-36769-adaptivnijj-korelyator.html" target="_blank" rel="follow" title="База патентів України">Адаптивний корелятор</a>

Попередній патент: Спосіб лікування атрофії зорового нерва та дистрофії сітчатої оболонки ока

Наступний патент: Спосіб припливно-відпливного дренування при остеомієліті трубчастих кісток

Випадковий патент: Шумозахисний екран і спосіб його виготовлення