Об’єднавчий модуль цифрової обробки сигналів

Номер патенту: 38235

Опубліковано: 25.12.2008

Автори: Слюсар Вадим Іванович, Малащук Володимир Петрович, Бондаренко Максим Васильович, Гриценко Віктор Миколайович, Шацман Леонід Георгієвич, Нікітін Микола Михайлович, Волощук Ігор Вікторович

Формула / Реферат

1. Об'єднавчий модуль цифрової обробки сигналів, який містить сигнальні входи, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль комутації сигналів, цифровий буфер, контролер передачі даних на інтерфейсну шину, модуль керування пам'яттю, модуль формування сигналів синхронізації та керування, модуль цифрової обробки сигналів, що містить модуль цифрового діаграмоутворення, при цьому вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, шини даних модулів оперативної пам'яті підключені через модуль керування пам'яттю (входить до складу ПЛІС) до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та керування модулів оперативної пам'яті підключені до відповідних виходів модуля керування пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля комутації сигналів, входи цифрового буфера підключені до відповідних виходів контролера передачі даних на інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до першого виходу (виходу переключення режимів "Вибір режиму") модуля формування сигналів синхронізації та керування, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, тактові входи модуля перетворення послідовного коду у паралельний, а також модуля цифрового діаграмоутворення, перші входи керування модуля керування пам'яттю підключені до другого виходу модуля формування сигналів синхронізації та керування (входить до складу ПЛІС), тактовий вхід модуля формування сигналів синхронізації та керування підключений до виходу комутатора тактових сигналів, входи керування модуля формування сигналів синхронізації та керування підключені до другої групи виходів контролера передачі даних на інтерфейсну шину, який відрізняється тим, що до складу ПЛІС додатково введені приймачі-передавачі інтерфейсів Rocket I/O, а до складу модуля цифрової обробки сигналів - модуль вилучення відгуків активних завад, модуль синтезу частотних фільтрів, модуль формування квадратів або абсолютних значень напруг для виявлення сигналів, крім того, модуль цифрового діаграмоутворення виконаний у вигляді послідовно з'єднаних модуля завершення цифрового діаграмоутворення за першою з кутових координат та модуля цифрового діаграмоутворення за другою з кутових координат, при цьому сигнальні входи підключені до відповідних входів приймачів-передавачів інтерфейсів Rocket I/O (входять до складу ПЛІС), виходи яких підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи якого підключені до першої групи входів модуля завершення цифрового діаграмоутворення за першою з кутових координат, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення за другою з кутових координат, виходи якого підключені до першої групи входів модуля вилучення відгуків активних завад, виходи якого підключені до першої групи входів модуля синтезу частотних фільтрів, виходи якого підключені до першої групи входів модуля формування квадратів або абсолютних значень напруг для виявлення сигналів, тактові входи приймачів-передавачів інтерфейсів Rocket I/O і контролера передачі даних на інтерфейсну шину підключені до другого виходу модуля формування сигналів синхронізації та керування (входить до складу ПЛІС), до якого також підключені об'єднані тактові входи модуля вилучення відгуків активних завад, модуля синтезу частотних фільтрів, модуля формування квадратів або абсолютних значень напруг для виявлення сигналів, тактовий вхід модуля цифрового діаграмоутворення утворений об'єднаними тактовими входами модуля завершення цифрового діаграмоутворення за першою з кутових координат та модуля цифрового діаграмоутворення за другою з кутових координат, друга група входів модуля вилучення відгуків активних завад підключена до третьої групи виходів модуля формування сигналів синхронізації та керування, другі входи модуля завершення цифрового діаграмоутворення за першою з кутових координат, модуля цифрового діаграмоутворення за другою з кутових координат, модуля синтезу частотних фільтрів та модуля формування квадратів або абсолютних значень напруг для виявлення сигналів підключені відповідно до четвертого, п'ятого, шостого та сьомого виходів модуля формування сигналів синхронізації та керування.

2. Об'єднавчий модуль цифрової обробки сигналів за п. 1, який відрізняється тим, що як інтерфейсну шину використовують паралельну інтерфейсну шину, наприклад стандарту CompactPCI або CompactPCI Express, а як модулі оперативної пам'яті застосовують зовнішні по відношенню до ПЛІС мікросхеми пам'яті, наприклад, статичного або динамічного типу.

3. Об'єднавчий модуль цифрової обробки сигналів за п. 1, який відрізняється тим, що як інтерфейсну шину використовують послідовний інтерфейс Rocket I/O або мідний чи оптичний варіанти виконання лінії Ethernet 1(10)Гбіт/с, а як модулі оперативної пам'яті застосовують зовнішні по відношенню до ПЛІС мікросхеми пам'яті, наприклад, динамічного типу.

Текст

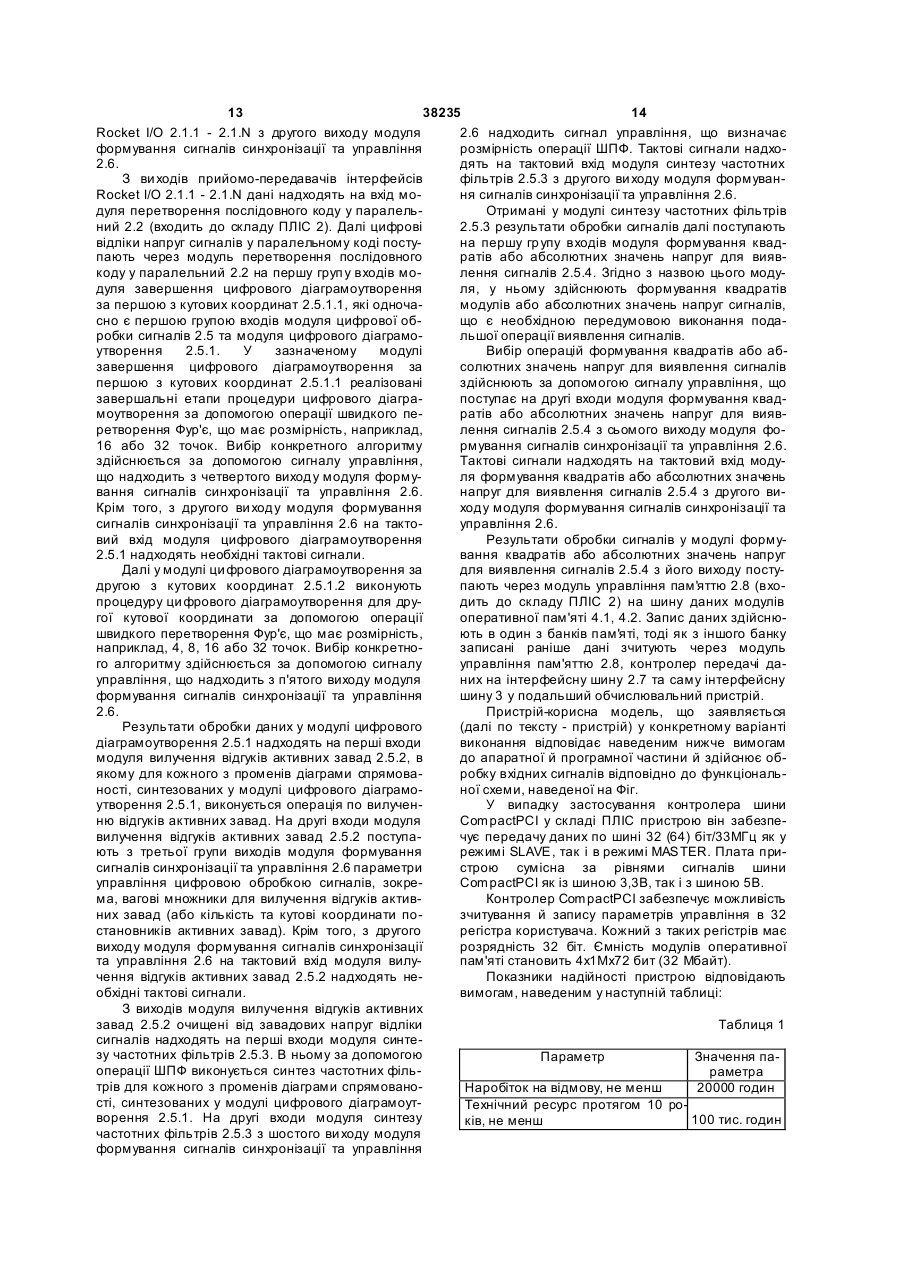

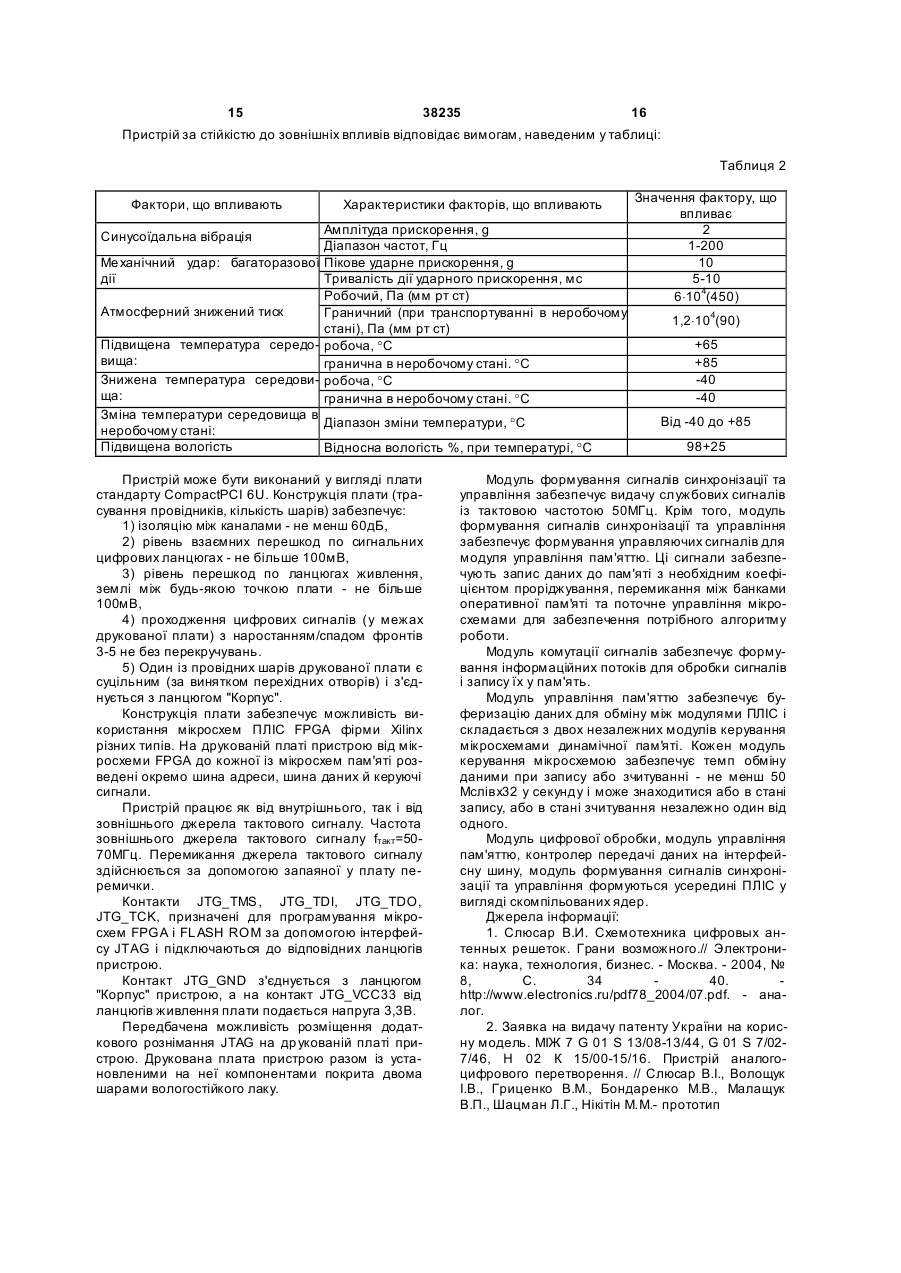

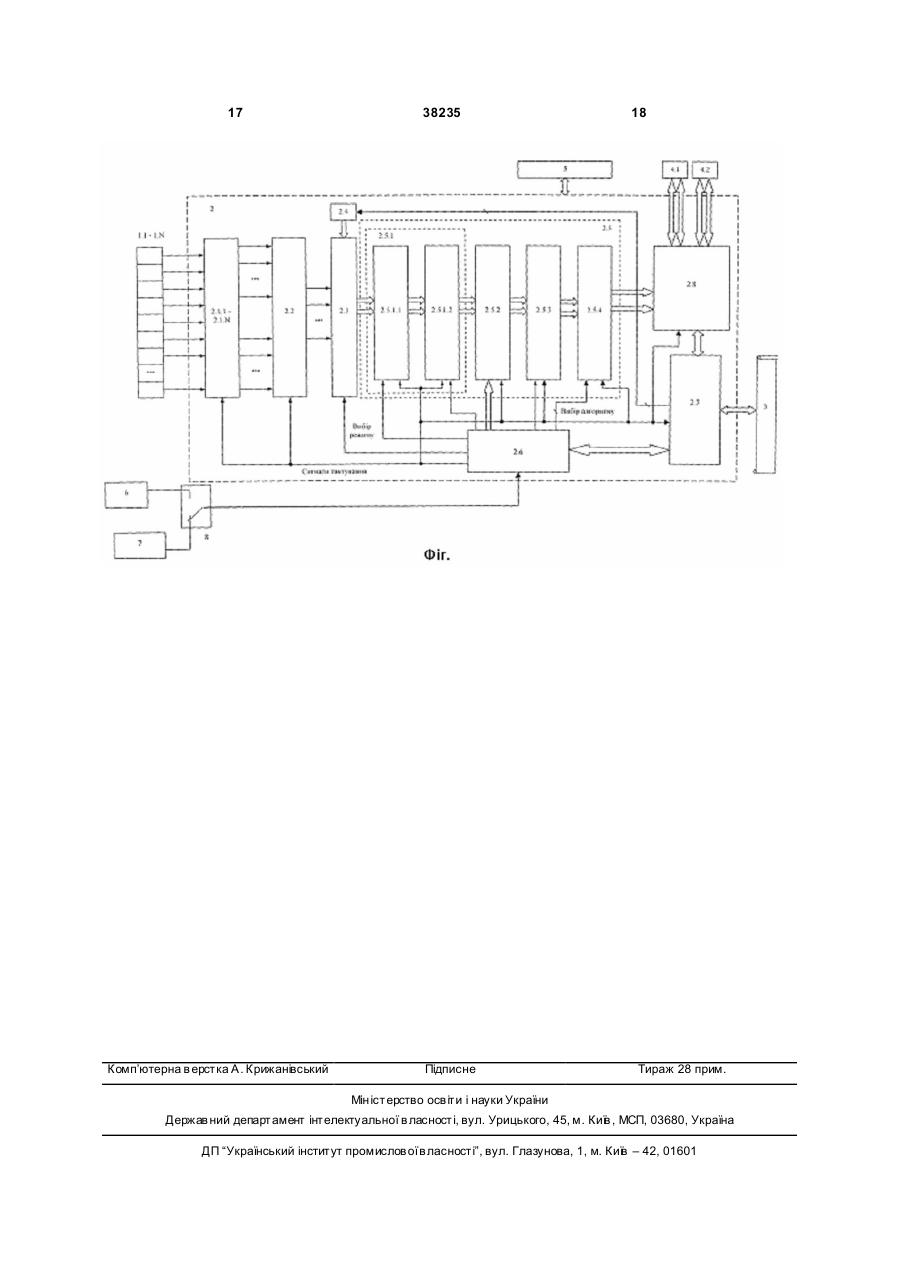

1. Об'єднавчий модуль цифрової обробки сигналів, який містить сигнальні входи, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль комутації сигналів, цифровий буфер, контролер передачі даних на інтерфейсну шину, модуль керування пам'яттю, модуль формування сигналів синхронізації та керування, модуль цифрової обробки сигналів, що містить модуль цифрового діаграмоутворення, при цьому вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, шини даних модулів оперативної пам'яті підключені через модуль керування пам'яттю (входить до складу ПЛІС) до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та керування модулів оперативної пам'яті підключені до відповідних виходів модуля керування пам'яттю (входить до складу ПЛІС), постійний запам'я товуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля комутації сигналів, входи цифрового буфера підключені до відповідних виходів контролера передачі даних на інтерфейсну шину, а ви ходи - до друго ї гр упи входів модуля комутації сигналів, третій вхід якого підключений до першого виходу (ви ходу переклю 2 (19) 1 3 38235 4 формування сигналів синхронізації та керування лення сигналів підключені відповідно до четверто(входить до складу ПЛІС), до якого також підклюго, п'ятого, шостого та сьомого виходів модуля чені об'єднані тактові входи модуля вилучення формування сигналів синхронізації та керування. відгуків активних завад, модуля синтезу частотних 2. Об'єднавчий модуль цифрової обробки сигналів фільтрів, модуля формування квадратів або абсоза п. 1, який відрізняється тим, що як інтерфейслютних значень напруг для виявлення сигналів, ну шин у використовують паралельну інтерфейсну тактовий вхід модуля цифрового діаграмоутвошину, наприклад стандарту CompactPCI або рення утворений об'єднаними тактовими входами CompactPCI Express, а як модулі оперативної памодуля завершення цифрового діаграмоутворення м'яті застосовують зовнішні по відношенню до за першою з кутових координат та модуля цифроПЛІС мікросхеми пам'яті, наприклад, статичного вого діаграмоутворення за другою з кутови х коорабо динамічного типу. динат, друга гр упа входів модуля вилучення відгу3. Об'єднавчий модуль цифрової обробки сигналів ків активних завад підключена до третьої групи за п. 1, який відрізняється тим, що як інтерфейсвиходів модуля формування сигналів синхронізації ну шину використовують послідовний інтерфейс та керування, другі входи модуля завершення циRocket I/O або мідний чи оптичний варіанти викофрового діаграмоутворення за першою з кутових нання лінії Ethernet 1(10)Гбіт/с, а як модулі операкоординат, модуля цифрового діаграмоутворення тивної пам'яті застосовують зовнішні по відношенза другою з кутових координат, модуля синтезу ню до ПЛІС мікросхеми пам'яті, наприклад, частотних фільтрів та модуля формування кваддинамічного типу. ратів або абсолютних значень напруг для вияв Корисна модель відноситься до галузі радіотехніки, зокрема, до пристроїв багатоканальної цифрової обробки сигналів, і може бути використана для цифрової обробки сигналів в системах радіолокації, зв'язку, то що. Відомий модуль передачі даних LVDS SETLINK-22RL [1] російської фірми ЗАО "Скан Инжиниринг Телеком", який виконує роль сполучної ланки (об'єднавчого модуля (ОМ)) між платами аналого-цифрового перетворення сигналів і керуючим комп'ютером. Модуль призначений для вирішення завдань цифрової обробки сигналів високої продуктивності й високошвидкісної передачі даних у стандарті LVDS. До складу зазначеного модуля, зокрема, входять сигнальні входи, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмовані логічні інтегральні схеми (ПЛІС), в яких містяться прийомо-передавачі інтерфейсів LVDS, модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів, контролер передачі даних на інтерфейсну шину, модуль формування сигналів синхронізації та управління, при цьому постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, сигнальні входи підключені до відповідних входів прийомо-передавачів інтерфейсів LVDS (входять до складу ПЛІС), виходи яких підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС). Перехід до використання об'єднавчих плат SETLINK-22RL, як вказано у [1], є далекоглядним схемотехнічним рішенням. Зв'язок між платами аналого-цифрового перетворення сигналів та ОМ у версії "Скан Инжиниринг Телеком" здійснюється по оптоволоконним гальванично розв'язаним лініям, що дозволяє мінімізувати вплив цифрової частини на аналоговий сегмент обробки сигналів. При цьому реалізований протокол LVDS дозволяє досягти пропускної здатності, притаманної інтерфейсній шині CompactPCI 64 біт/33 МГц, а завдяки розпаралеленню завантаження даних одночасно з усі х пристроїв аналого-цифрового перетворення загальний виграш у продуктивності у порівнянні з інтерфейсом CompactPCI, дорівнює кількості задіяних каналів послідовної передачі. Модуль, маючи 12 каналів передачі даних на відстань до 4 метрів, представляє ефективне рішення для організації високошвидкісної передачі даних у системах, конструктивно скомпонованих у технологічній шафі або кількох шафа х типорозміру 6U. Недоліком пристрою-аналогу SETLINK-22RL є відсутність у його складі модулів оперативної пам'яті, що надто обмежує можливості реалізації операцій з цифрової обробки сигналів. Крім того, використання у складі пристрою п'я ти ПЛІС призводить до надмірного споживання електроенергії та потребує вирішення проблеми тепловідведення. Відомий модуль передачі даних LVDS SETLINK-22TL [1] російської фірми ЗАО "Скан Инжиниринг Телеком", що призначений для цифрової обробки сигналів. До складу зазначеного модуля, зокрема, входять сигнальні входи, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмовані логічні інтегральні схеми (ПЛІС), в яких містяться прийомо-передавачі інтерфейсів LVDS, модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну 5 38235 6 шину підключені до інтерфейсної шини пристрою, аналог має обмежений перелік операцій з цифросигнальні входи підключені до відповідних входів вої обробки сигналів. прийомо-передавачів інтерфейсів LVDS (входять Відомий об'єднавчий модуль цифрової обробдо складу ПЛІС), виходи яких підключені до відпоки сигналів [1], виконаний на базі ПЛІС. Цей об'єдвідних входів модуля перетворення послідовного навчий модуль призначений для збору по послідокоду у паралельний (входить до складу ПЛІС). вних інтерфейсах результатів первинної обробки На відміну від пристрою SETLINK-22RL пересигналів у пристроях аналого-цифрового перетвовагою технічного рішення SETLINK-22TL є наяврення сигналів, виконання операції цифрового ність у його складі модулів оперативної пам'яті. діаграмоутворення, вилучення сигналів завад за Аналіз структури ОМ типу SETLINK-22TL привовідомими кутовими координатами завадопостанодить до висновку про можливість реалізації за довників, що завантажуються з керуючого процесопомогою ОМ операції цифрового діаграмоутвора, формування сітки частотних фільтрів і передарення, синтезу частотних фільтрів по кожному із чі оброблених масивів даних в оперативну пам'ять просторових променів діаграми спрямованості у модуля керуючого комп'ютера по шині випадку цифрової антенної решітки. CompactPCI. Недоліком пристрою-аналогу SETLINK-22TL є До складу модуля - аналогу, згідно зі схемою, використання кількох ПЛІС, що призводить до наведеною у [1], входять сигнальні входи, модулі надмірного споживання електричної енергії приоперативної пам'яті, інтерфейсна шина, програмостроєм, ускладнює розведення сигнальних ліній на вані логічні інтегральні схеми (ПЛІС), в яких місдрукованій платі. Крім того, пристрій-аналог має тяться прийомо-передавачі інтерфейсів Rocket I/O, обмежений перелік операцій з цифрової обробки модуль перетворення послідовного коду у парасигналів. лельний, модуль цифрової обробки сигналів, конВідомий модуль цифрової обробки сигналів на тролер передачі даних на інтерфейсну шину, моПЛІС серии Virtex-II ПЛИСАР-002М [1] російської дуль управління пам'яттю, модуль формування фірми ЗАО "Скан Инжиниринг Телеком". сигналів синхронізації та управління. До складу зазначеного модуля, зокрема, вхоВідмінною рисою пристрою-аналогу є параледять сигнальні входи, вхід зовнішньої синхронізальна цифрова обробка сигналів з багатьох вхідних ції, модулі оперативної пам'яті, постійний запам'я каналів за допомогою сукупності з дво х послідовно товуючий пристрій, інтерфейсна шина, з'єднаних ПЛІС, використання ешелонованого розпрограмовані логічні інтегральні схеми (ПЛІС), в ташування ПЛІС на платі, що дозволяє розділити яких містяться прийомо-передавачі інтерфейсів функції між різними ПЛІС відповідно до етапів циLVDS, модуль перетворення послідовного коду у фрової обробки даних. Для передачі даних між паралельний, контролер передачі даних на інтерешелонами ПЛІС використовується послідовний фейсну шину, модуль управління пам'яттю, моінтерфейс Rocket I/O, що істотно спрощує розведуль формування сигналів синхронізації та управдення друкованої плати. ління, модуль цифрової обробки сигналів, при У ПЛІС першого ешелону, можуть бути реаліцьому шини даних модулів оперативної пам'яті зовані операції цифрового діаграмоутворення над підключені через модуль управління пам'яттю вихідними даними кількох плат аналого-цифрового (входить до складу ПЛІС) до відповідних входів перетворення, а також вилучення завадових сигконтролера передачі даних на інтерфейсну шину, налів по відомих кутових координатах завадопоса шини адресації та управління модулів оперативтановників, що завантажуються з керуючого проної пам'яті підключені до відповідних виходів моцесора. дуля управління пам'яттю (входить до складу У другому е шелоні ПЛІС може здійснюватись ПЛІС), постійний запам'ятовуючий пристрій підформування сітки частотних фільтрів, а також моключений до входів загрузки архітектури ПЛІС, жуть бути реалізовані модуль управління пам'ятвиходи контролера передачі даних на інтерфейсну тю, модуль формування сигналів синхронізації та шину підключені до інтерфейсної шини пристрою, управління, контролер передачі даних на інтерсигнальні входи підключені до відповідних входів фейсну шину, що забезпечує передачу результаприйомо-передавачів інтерфейсів LVDS (входять тів цифрової обробки сигналів через шину до складу ПЛІС), виходи яких підключені до відпоCompactPCI на подальший обчислювальний привідних входів модуля перетворення послідовного стрій. коду у паралельний (входить до складу ПЛІС). Для проведення контролю функціонування ОМ Наявність входу зовнішньої синхронізації доможуть використовуватися нарівні з основними зволяє використовувати пристрій ПЛИСАР-002М у також спеціальні тестові архітектури ПЛІС, записаскладі систем когерентної обробки сигналів. В ні у постійний запам'я товуючий пристрій, що доньому може бути реалізоване цифрове діаграмоузволяють діагностувати правильність функціонутворення, синтез частотних фільтрів по кожному із вання ПЛІС на конкретних фазах обробки сигналів. просторових променів діаграми спрямованості у До недоліків пристрою-аналогу слід віднести випадку цифрової антенної решітки. використання ешелонованого розташування моНедоліком пристрою-аналогу ПЛИСАР-002М, дулів обробки даних у різних ПЛІС, що призводить як і згаданих раніше SETLINK-22RL та SETLINKдо надмірного теплового розсіювання ними потуж22TL, є використання кількох ПЛІС, що призводить ності та додаткового споживання електричної енедо надмірного споживання електричної енергії ргії пристроєм, надто ускладнює розведення елекпристроєм, ускладнює розведення сигнальних тричних сигнальних ліній на друкованій платі, ліній на друкованій платі. Крім того, пристрійспонукає виготовляти її з великою кількістю друкованих шарів. Це призводить до збільшення собіва 7 38235 8 ртості пристрою. Крім того, наявність надмірної До недоліків пристрою-прототипу слід віднести кількості ПЛІС погіршує електромагнітну сумісність його спрямованість лише на аналого-цифрове модулів, що застосовуються у пристрої, через виперетворення сигналів, що не дозволяє викориспромінювання додаткових завад послідовними товувати його в якості об'єднавчого модуля, й фуінтерфейсними шинами, що з'єднують мікросхеми нкціонально обмежений перелік модулів цифрової ПЛІС і виконують роль своєрідних антен та погіробробки сигналів у складі ПЛІС. шують імпеданс ліній розповсюдження сигналів. В основу корисної моделі покладене завдання Найбільш близьким технічним рішенням до підвищення основних технічних характеристик заявленої корисної моделі, є пристрій, запропонооб'єднавчого модуля цифрової обробки сигналів. ваний у [2], до складу якого, зокрема, входять сигОчікуваний технічний результат від заявленої нальні входи, вхід зовнішньої синхронізації, внуткорисної моделі полягає у забезпеченні можливосрішній тактовий генератор, комутатор тактових ті паралельної багатоканальної цифрової обробки сигналів (з внутрішнього тактового генератора та сигналів за широкою номенклатурою алгоритмів у входу зовнішньої синхронізації), модулі оперативскладі ПЛІС, поліпшення електромагнітної сумісної пам'яті, постійний запам'ятовуючий пристрій, ності мікросхем, що застосовуються у пристрої. інтерфейсна шина, програмована логічна інтеграСуть нововведень до корисної моделі порівняльна схема (ПЛІС), в якій містяться модуль перено з прототипом полягає у тому, що до складу творення послідовного коду у паралельний, моПЛІС додатково введені прийомо-передавачі індуль комутації сигналів, цифровий буфер, терфейсів Rocket I/O, а до складу модуля цифроконтролер передачі даних на інтерфейсну шину, вої обробки сигналів - модуль вилучення відгуків модуль управління пам'яттю, модуль формування активних завад, модуль синтезу частотних фільтсигналів синхронізації та управління, модуль цифрів, модуль формування квадратів або абсолютрової обробки сигналів, що містить модуль цифроних значень напруг для виявлення сигналів, крім вого діаграмоутворення, при цьому вхід зовнішньої того, модуль цифрового діаграмоутворення викосинхронізації та вихід внутрішнього тактового генаний у вигляді послідовно з'єднаних модуля занератора підключені до відповідних входів комутавершення цифрового діаграмоутворення за пертора тактових сигналів, шини даних модулів опешою з кутових координат та модуля цифрового ративної пам'яті підключені через модуль діаграмоутворення за другою з кутових координат, управління пам'яттю (входить до складу ПЛІС) до при цьому сигнальні входи підключені до відповідвідповідних входів контролера передачі даних на них входів прийомо-передавачів інтерфейсів інтерфейсну шину, а шини адресації та управління Rocket I/O (входять до складу ПЛІС), виходи яких модулів оперативної пам'яті підключені до відповіпідключені до відповідних входів модуля перетводних ви ходів модуля управління пам'я ттю (входить рення послідовного коду у паралельний (входить до складу ПЛІС), постійний запам'ятовуючий придо складу ПЛІС), виходи якого підключені до перстрій підключений до входів загрузки архітектури шої гр упи входів модуля завершення цифрового ПЛІС, виходи модуля перетворення послідовного діаграмоутворення за першою з кутових коордикоду у паралельний (входить до складу ПЛІС) піднат, ви ходи якого підключені до першої групи вхоключені до першої групи входів модуля комутації дів модуля цифрового діаграмоутворення за друсигналів, входи цифрового буфера підключені до гою з кутових координат, виходи якого підключені відповідних виходів контролера передачі даних на до першої групи входів модуля вилучення відгуків інтерфейсну шину, а ви ходи - до другої гр упи вхоактивних завад, виходи якого підключені до першої дів модуля комутації сигналів, третій вхід якого групи входів модуля синтезу частотни х фільтрів, підключений до першого виходу (виходу переклювиходи якого підключені до першої групи входів чення режимів "Вибір режиму") модуля формуванмодуля формування квадратів або абсолютних ня сигналів синхронізації та управління, виходи значень напруг для виявлення сигналів, тактові контролера передачі даних на інтерфейсну шину входи прийомо-передавачів інтерфейсів Rocket I/O підключені до інтерфейсної шини пристрою, тактоі контролера передачі даних на інтерфейсну шину ві входи модуля перетворення послідовного коду у підключені до другого виходу модуля формування паралельний, а також модуля цифрового діаграсигналів синхронізації та управління (входить до моутворення, перші входи управління модуля складу ПЛІС), до якого також підключені об'єднані управління пам'яттю підключені до другого ви ходу тактові входи модуля вилучення відгуків активних модуля формування сигналів синхронізації та завад, модуля синтезу частотних фільтрів, модуля управління (входить до складу ПЛІС), тактовий формування квадратів або абсолютних значень вхід модуля формування сигналів синхронізації та напруг для виявлення сигналів, тактовий вхід моуправління підключений до виходу комутатора дуля цифрового діаграмоутворення утворений тактових сигналів, входи управління модуля фороб'єднаними тактовими входами модуля завермування сигналів синхронізації та управління підшення цифрового діаграмоутворення за першою з ключені до другої групи виходів контролера перекутови х координат та модуля цифрового діаграмодачі даних на інтерфейсну шину. утворення за другою з кутови х координат, друга Відмінною рисою пристрою, обраного за прогрупа входів модуля вилучення відгуків активних тотип, є паралельна цифрова обробка сигналів з завад підключена до третьої групи виходів модуля багатьох вхідних каналів в одній ПЛІС, викорисформування сигналів синхронізації та управління, тання розподілу функцій між різними модулями у другі входи модуля завершення цифрового діагскладі ПЛІС відповідно до етапів цифрової обробрамоутворення за першою з кутових координат, ки даних. модуля цифрового діаграмоутворення за другою з кутови х координат, модуля синтезу частотних фі 9 38235 10 льтрів та модуля формування квадратів або абсо2.7 - Контролер передачі даних на інтерфейслютних значень напруг для виявлення сигналів ну шину; підключені відповідно до четвертого, п'ятого, шос2.8 - Модуль управління пам'яттю; того та сьомого виходів модуля формування сиг3 - Інтерфейсна шина; налів синхронізації та управління. 4.1 - Модуль оперативної пам'яті RAM1; Перший варіант конкретної реалізації заявле4.2 - Модуль оперативної пам'яті RAM2; ного пристрою відрізняється тим, що в якості ін5 - Постійний запам'я товуючий пристрій; терфейсної шини використовується паралельна 6 - Вхід зовнішньої синхронізації; інтерфейсна шина, наприклад, стандарту 7 - Внутрішній тактовий генератор; CompactPCI або CompactPCI Express, а в якості 8 - Комутатор тактових сигналів. модулів оперативної пам'яті застосовуються зовОб'єднавчий модуль цифрової обробки сигнанішні по відношенню до ПЛІС мікросхеми пам'яті, лів, що наведено на Фіг.1, до складу якого входять наприклад, статичного або динамічного типу. сигнальні входи 1.1.1 - 1.N.К, вхід зовнішньої синДругий варіант конкретної реалізації заявленохронізації 6, внутрішній тактовий генератор 7, кого пристрою відрізняється тим, що в якості інтермутатор тактових сигналів 8 (з внутрішнього тактофейсної шини використовується послідовний інвого генератора 7 та входу зовнішньої терфейс Rocket I/O або мідний чи оптичний синхронізації 6), модулі оперативної пам'яті 4.1, варіанти виконання лінії Ethernet 1(10) Гбіт/с, а в 4.2, постійний запам'я товуючий пристрій 5, Інтерякості модулів оперативної пам'яті застосовуються фейсна шина 3, програмована логічна інтегральна зовнішні по відношенню до ПЛІС мікросхеми пасхема (ПЛІС) 2, в якій містяться модуль перетвом'яті, наприклад, динамічного типу. рення послідовного коду у паралельний 2.2, моПорівняльний аналіз технічного рішення, яке дуль комутації сигналів 2.3, цифровий буфер 2,4, заявляється, із прототипом, дозволяє зробити виконтролер передачі даних на інтерфейсну шину сновок, що заявлений пристрій об'єднавчого мо2.7, модуль управління пам'яттю 2.8, модуль фордуля цифрової обробки сигналів суттєво відрізнямування сигналів синхронізації та управління 2.6, ється тим, що у ньому, на відміну від прототипу, модуль цифрової обробки сигналів 2.5, що містить використано додатково введені модулі для забезмодуль цифрового діаграмоутворення 2.5.1, при печення цифрової обробки сигналів, зокрема: моцьому вхід зовнішньої синхронізації 6 та вихід внудуль завершення цифрового діаграмоутворення трішнього тактового генератора 7 підключені до за першою з кутових координат та модуль цифровідповідних входів комутатора тактових сигналів 8, вого діаграмоутворення за другою з кутови х кооршини даних модулів оперативної пам'яті 4.1, 4.2 динат, модуль вилучення відгуків активних завад, підключені через модуль управління пам'яттю 2.8 модуль синтезу частотних фільтрів та модуль фо(входить до складу ПЛІС 2) до відповідних входів рмування квадратів або абсолютних значень наконтролера передачі даних на інтерфейсну шину пруг для виявлення сигналів. Крім того, вся оброб2.7, а шини адресації та управління модулів опека даних здійснюється в одній мікросхемі ПЛІС. ративної пам'яті 4.1, 4.2 підключені до відповідних Таким чином, об'єднавчий модуль цифрової виходів модуля управління пам'яттю 2.8 (входить обробки сигналів, який заявляється, відповідає до складу ПЛІС 2), постійний запам'ятовуючий критерію "новизна" корисної моделі. пристрій 5 підключений до входів загрузки архітекСуть корисної моделі пояснюється за допомотури ПЛІС 2, виходи модуля перетворення послігою креслень, де на Фіг. представлена структурна довного коду у паралельний 2.2 (входить до скласхема основного варіанту реалізації об'єднавчого ду ПЛІС 2) підключені до першої групи входів модуля цифрової обробки сигналів, який заявлямодуля комутації сигналів 2.3, входи цифрового ється. буфера 2.4 підключені до відповідних ви ходів конЦифрами на Фіг.позначені: тролера передачі даних на інтерфейсну шин у 2.7, 1.1 - 1.N - Сигнальні входи; а виходи - до другої гр упи входів модуля комутації 2 - ПЛІС; сигналів 2.3, третій вхід якого підключений до 2.1.1 - 2.1.N - Прийомо-передавачі інтерфейсів першого виходу (виходу переключення режимів Rocket I/O; "Вибір режиму") модуля формування сигналів син2.2 - Модуль перетворення послідовного коду хронізації та управління 2.6, виходи контролера у паралельний; передачі даних на інтерфейсну шину 2.7 підклю2.3 - Модуль комутації сигналів; чені до інтерфейсної шини 3 пристрою, тактові 2.4 - Цифровий буфер; входи модуля перетворення послідовного коду у 2.5 - Модуль цифрової обробки сигналів; паралельний 2.2, а також модуля цифрового діаг2.5.1 - Модуль цифрового діаграмоутворення; рамоутворення 2.5.1, перші входи управління мо2.5.1.1 - Модуль завершення цифрового діагдуля управління пам'яттю 2.8 підключені до другорамоутворення за першою з кутови х координат; го виходу модуля формування сигналів 2.5.1.2 - Модуль цифрового діаграмоутворення синхронізації та управління 2.6 (входить до складу за другою з кутови х координат; ПЛІС 2), тактовий вхід модуля формування сигна2.5.2 - Модуль вилучення відгуків активних залів синхронізації та управління 2.6 підключений до вад; виходу комутатора тактових сигналів 8, входи 2.5.3 - Модуль синтезу часто тних фільтрів; управління модуля формування сигналів синхроні2.5.4 - Модуль формування квадратів або абзації та управління 2.6 підключені до другої групи солютних значень напруг для виявлення сигналів; виходів контролера передачі даних на інтерфейс2.6 - Модуль формування сигналів синхронізану шину 2.7, який відрізняється тим, що до складу ції та управління; ПЛІС 2 додатково введені прийомо-передавачі 11 38235 12 інтерфейсів Rocket I/O 2.1.1 - 2.1.N, а до складу На етапі ініціювання роботи пристрою одразу модуля цифрової обробки сигналів 2.5 - модуль після вмикання живлення відповідні тактові сигнавилучення відгуків активних завад 2.5.2, модуль ли надходять на вхід модуля формування сигналів синтезу частотних фільтрів 2.5.3, модуль формусинхронізації та управління 2.6, що входить до вання квадратів або абсолютних значень напруг складу ПЛІС 2. Крім того, з постійного запам'ятодля виявлення сигналів 2.5.4, крім того, модуль вуючого пристрою 5 через відповідні входи ПЛІС 2 цифрового діаграмоутворення 2.5.1 виконаний у здійснюють загрузку архітектури ПЛІС 2. Далі чевигляді послідовно з'єднаних модуля завершення рез інтерфейсну шину 3 і контролер передачі дацифрового діаграмоутворення за першою з кутоних на інтерфейсну шин у 2.7 у модуль формуванвих координат 2.5.1.1 та модуля цифрового діагня сигналів синхронізації та управління 2.6 рамоутворення за другою з кутових координат записують параметри управління роботою при2.5.1.2, при цьому сигнальні входи 1.1.1 - 1.N.K строю та параметри управління цифровою обробпідключені до відповідних входів прийомокою сигналів, зокрема: коди управління, що визнапередавачів інтерфейсів Rocket I/O 2.1.1 - 2.1.N чають розмірність швидкого перетворення Фур'є (входять до складу ПЛІС 2), виходи яких підключе(ШПФ) для операцій цифрового діаграмоутворенні до відповідних входів модуля перетворення поня за двома кутовими координатами та для опеслідовного коду у паралельний 2.2 (входить до рації синтезу частотних фільтрів, вагові множники складу ПЛІС 2), виходи якого підключені до першої для вилучення відгуків активних завад (або кільгрупи входів модуля завершення цифрового діагкість та кутові координати постановників активних рам оутворення за першою з кутових координат завад), вибір операцій формування квадратів або 2.5.1.1, виходи якого підключені до першої групи абсолютних значень напруг для виявлення сигнавходів модуля цифрового діаграмоутворення за лів, тощо. другою з кутови х координат 2.5.1.2, ви ходи якого У режимі тестування алгоритмів цифрової обпідключені до першої групи входів модуля вилуробки сигналів на етапі ініціювання роботи причення відгуків активних завад 2.5.2, ви ходи якого строю на додаток до описаних операцій через інпідключені до першої групи входів модуля синтезу терфейсну шин у 3 і контролер передачі даних на частотних фільтрів 2.5.3, ви ходи якого підключені інтерфейсну шину 2.7 у ци фровий буфер 2.4 запидо першої групи входів модуля формування квадсують тестові цифрові коди, а у модуль формуратів або абсолютних значень напруг для вияввання сигналів синхронізації та управління 2.6 залення сигналів 2.5.4, тактові входи прийомописують команду на переключення режимів передавачів інтерфейсів Rocket I/O 2.1.1 - 2.1.N і (одиничний рівень сигналу "Вибір режиму"). Під контролера передачі даних на інтерфейсну шину дією цієї команди модуль комутації сигналів 2.2 2.7 підключені до другого виходу модуля формуперемикають у стан, коли цифрові дані на вхід вання сигналів синхронізації та управління 2.6 модуля цифрової обробки сигналів 2.5 в основно(входить до складу ПЛІС 2), до якого також підму режимі роботи пристрою будуть надходити з ключені об'єднані тактові входи модуля вилучення цифрового буферу 2.4, а не з модуля перетворенвідгуків активних завад 2.5.2, модуля синтезу часня послідовного коду у паралельний 2.2. Далі, за тотних фільтрів 2.5.3, модуля формування квадрадопомогою тестових кодів, записаних у цифровий тів або абсолютних значень напруг для виявлення буфер 2.4, контролюють працездатність модуля сигналів 2.5.4, тактовий вхід модуля цифрового цифрової обробки сигналів 2.5 шляхом зчитування діаграмоутворення 2.5.1 утворений об'єднаними у подальший обчислювальний пристрій результатактовими входами модуля завершення цифровотів обробки у ПЛІС 2 тестової послідовності даних. го діаграмоутворення за першою з кутових коорДля ініціювання роботи пристрою, що заявлядинат 2.5.1.1 та модуля цифрового діаграмоутвоється, у основному режимі через інтерфейсну ширення за другою з кутови х координат 2.5.1.2, друга ну 3 і контролер передачі даних на інтерфейсну група входів модуля вилучення відгуків активних шину 2.7 у модуль формування сигналів синхронізавад 2.5.2 підключена до третьої групи ви ходів зації та управління 2.6 записують команду на відмодуля формування сигналів синхронізації та міну переключення режимів (нульовий рівень сигуправління 2.6, другі входи модуля завершення налу "Вибір режиму"). Під дією цього сигналу цифрового діаграмоутворення за першою з кутомодуль комутації сигналів 2.2 перемикають у стан, вих координат 2.5.1.1, модуля цифрового діаграколи цифрові дані на вхід модуля цифрової обробмоутворення за другою з кутови х координат ки сигналів 2.5 в основному режимі роботи при2.5.1.2, модуля синтезу часто тних фільтрів 2.5.3 та строю будуть надходити з модуля перетворення модуля формування квадратів або абсолютних послідовного коду у паралельний 2.2, а не з цифзначень напруг для виявлення сигналів 2.5.4 підрового буферу 2.4. ключені відповідно до четвертого, п'ятого, шостого У основному режимі роботи пристрою, що зата сьомого виходів модуля формування сигналів являється, цифрові дані з виходів N фізичних касинхронізації та управління 2.6. налів поступають через послідовні диференціальні Принцип роботи основного варіанту заявленоінтерфейси LVDS (по одній диференціальній парі го пристрою полягає в наступному. ліній на кожен з N каналів) на сигнальні входи 1.1 На етапі підготовки пристрою до роботи за до1.N й далі - на відповідні входи прийомопомогою комутатора тактових сигналів 8 вибирапередавачів інтерфейсів Rocket I/O 2.1.1 - 2.1.N у ють режим подальшої роботи пристрою: з тактускладі ПЛІС 2. Тактування прийомо-передавачів ванням сигналами такту, що подають на вхід інтерфейсів Rocket I/O 2.1.1 - 2.1.N здійснюють за зовнішньої синхронізації 6, або ж сигналами такту допомогою сигналів тактування, які надходять на з внутрішнього тактового генератора 7. тактові входи прийомо-передавачів інтерфейсів 13 38235 14 Rocket I/O 2.1.1 - 2.1.N з другого виходу модуля 2.6 надходить сигнал управління, що визначає формування сигналів синхронізації та управління розмірність операції ШПФ. Тактові сигнали надхо2.6. дять на тактовий вхід модуля синтезу частотних З ви ходів прийомо-передавачів інтерфейсів фільтрів 2.5.3 з другого ви ходу модуля формуванRocket I/O 2.1.1 - 2.1.N дані надходять на вхід моня сигналів синхронізації та управління 2.6. дуля перетворення послідовного коду у паралельОтримані у модулі синтезу частотних фільтрів ний 2.2 (входить до складу ПЛІС 2). Далі цифрові 2.5.3 результати обробки сигналів далі поступають відліки напруг сигналів у паралельному коді постуна першу гр упу входів модуля формування квадпають через модуль перетворення послідовного ратів або абсолютних значень напруг для виявкоду у паралельний 2.2 на першу груп у входів молення сигналів 2.5.4. Згідно з назвою цього модудуля завершення цифрового діаграмоутворення ля, у ньому здійснюють формування квадратів за першою з кутових координат 2.5.1.1, які одночамодулів або абсолютних значень напруг сигналів, сно є першою групою входів модуля цифрової общо є необхідною передумовою виконання подаробки сигналів 2.5 та модуля цифрового діаграмольшої операції виявлення сигналів. утворення 2.5.1. У зазначеному модулі Вибір операцій формування квадратів або абзавершення цифрового діаграмоутворення за солютних значень напруг для виявлення сигналів першою з кутових координат 2.5.1.1 реалізовані здійснюють за допомогою сигналу управління, що завершальні етапи процедури цифрового діаграпоступає на другі входи модуля формування квадмоутворення за допомогою операції швидкого ператів або абсолютних значень напруг для виявретворення Фур'є, що має розмірність, наприклад, лення сигналів 2.5.4 з сьомого виходу модуля фо16 або 32 точок. Вибір конкретного алгоритму рмування сигналів синхронізації та управління 2.6. здійснюється за допомогою сигналу управління, Тактові сигнали надходять на тактовий вхід модущо надходить з четвертого виходу модуля формуля формування квадратів або абсолютних значень вання сигналів синхронізації та управління 2.6. напруг для виявлення сигналів 2.5.4 з другого виКрім того, з другого ви ходу модуля формування ходу модуля формування сигналів синхронізації та сигналів синхронізації та управління 2.6 на тактоуправління 2.6. вий вхід модуля цифрового діаграмоутворення Результати обробки сигналів у модулі форму2.5.1 надходять необхідні тактові сигнали. вання квадратів або абсолютних значень напруг Далі у модулі ци фрового діаграмоутворення за для виявлення сигналів 2.5.4 з його виходу постудругою з кутових координат 2.5.1.2 виконують пають через модуль управління пам'яттю 2.8 (вхопроцедуру ци фрового діаграмоутворення для друдить до складу ПЛІС 2) на шину даних модулів гої кутової координати за допомогою операції оперативної пам'яті 4.1, 4.2. Запис даних здійснюшвидкого перетворення Фур'є, що має розмірність, ють в один з банків пам'я ті, тоді як з іншого банку наприклад, 4, 8, 16 або 32 точок. Вибір конкретнозаписані раніше дані зчитують через модуль го алгоритму здійснюється за допомогою сигналу управління пам'яттю 2.8, контролер передачі дауправління, що надходить з п'ятого виходу модуля них на інтерфейсну шину 2.7 та саму інтерфейсну формування сигналів синхронізації та управління шину 3 у подальший обчислювальний пристрій. 2.6. Пристрій-корисна модель, що заявляється Результати обробки даних у модулі цифрового (далі по тексту - пристрій) у конкретному варіанті діаграмоутворення 2.5.1 надходять на перші входи виконання відповідає наведеним нижче вимогам модуля вилучення відгуків активних завад 2.5.2, в до апаратної й програмної частини й здійснює обякому для кожного з променів діаграми спрямоваробку вхідних сигналів відповідно до функціональності, синтезованих у модулі цифрового діаграмоної схеми, наведеної на Фіг. утворення 2.5.1, виконується операція по вилученУ випадку застосування контролера шини ню відгуків активних завад. На другі входи модуля CompactPCI у складі ПЛІС пристрою він забезпевилучення відгуків активних завад 2.5.2 поступачує передачу даних по шині 32 (64) біт/33МГц як у ють з третьої групи виходів модуля формування режимі SLAVE, так і в режимі MASTER. Плата присигналів синхронізації та управління 2.6 параметри строю сумісна за рівнями сигналів шини управління цифровою обробкою сигналів, зокреCompactPCI як із шиною 3,3В, так і з шиною 5В. ма, вагові множники для вилучення відгуків активКонтролер CompactPCI забезпечує можливість них завад (або кількість та кутові координати позчитування й запису параметрів управління в 32 становників активних завад). Крім того, з другого регістра користувача. Кожний з таких регістрів має виходу модуля формування сигналів синхронізації розрядність 32 біт. Ємність модулів оперативної та управління 2.6 на тактовий вхід модуля вилупам'яті становить 4х1Мх72 бит (32 Мбайт). чення відгуків активних завад 2.5.2 надходять неПоказники надійності пристрою відповідають обхідні тактові сигнали. вимогам, наведеним у наступній таблиці: З виходів модуля вилучення відгуків активних завад 2.5.2 очищені від завадових напруг відліки Таблиця 1 сигналів надходять на перші входи модуля синтезу частотних фільтрів 2.5.3. В ньому за допомогою Параметр Значення паоперації ШПФ виконується синтез частотних фільраметра трів для кожного з променів діаграми спрямованоНаробіток на відмову, не менш 20000 годин сті, синтезованих у модулі цифрового діаграмоутТехнічний ресурс протягом 10 роворення 2.5.1. На другі входи модуля синтезу 100 тис. годин ків, не менш частотних фільтрів 2.5.3 з шостого ви ходу модуля формування сигналів синхронізації та управління 15 38235 16 Пристрій за стійкістю до зовнішніх впливів відповідає вимогам, наведеним у таблиці: Таблиця 2 Фактори, що впливають Характеристики факторів, що впливають Амплітуда прискорення, g Діапазон частот, Гц Ме ханічний удар: багаторазової Пікове ударне прискорення, g дії Тривалість дії ударного прискорення, мс Робочий, Па (мм рт ст) Атмосферний знижений тиск Граничний (при транспортуванні в неробочому стані), Па (мм рт ст) Підвищена температура середо- робоча, °С вища: гранична в неробочому стані. °С Знижена температура середови- робоча, °С ща: гранична в неробочому стані. °С Зміна температури середовища в Діапазон зміни температури, °С неробочому стані: Підвищена вологість Відносна вологість %, при температурі, °С Синусоїдальна вібрація Пристрій може бути виконаний у вигляді плати стандарту CompactPCI 6U. Конструкція плати (трасування провідників, кількість шарів) забезпечує: 1) ізоляцію між каналами - не менш 60дБ, 2) рівень взаємних перешкод по сигнальних цифрових ланцюгах - не більше 100мВ, 3) рівень перешкод по ланцюгах живлення, землі між будь-якою точкою плати - не більше 100мВ, 4) проходження цифрових сигналів (у межах друкованої плати) з наростанням/спадом фронтів 3-5 не без перекручувань. 5) Один із провідних шарів друкованої плати є суцільним (за винятком перехідних отворів) і з'єднується з ланцюгом "Корпус". Конструкція плати забезпечує можливість використання мікросхем ПЛІС FPGA фірми Xilinx різних типів. На друкованій платі пристрою від мікросхеми FPGA до кожної із мікросхем пам'яті розведені окремо шина адреси, шина даних й керуючі сигнали. Пристрій працює як від внутрішнього, так і від зовнішнього джерела тактового сигналу. Частота зовнішнього джерела тактового сигналу fтакт=5070МГц. Перемикання джерела тактового сигналу здійснюється за допомогою запаяної у плату перемички. Контакти JTG_TMS, JTG_TDI, JTG_TDO, JTG_TCK, призначені для програмування мікросхем FPGA і FL ASH ROM за допомогою інтерфейсу JTAG і підключаються до відповідних ланцюгів пристрою. Контакт JTG_GND з'єднується з ланцюгом "Корпус" пристрою, а на контакт JTG_VCC33 від ланцюгів живлення плати подається напруга 3,3В. Передбачена можливість розміщення додаткового рознімання JTAG на др укованій платі пристрою. Друкована плата пристрою разом із установленими на неї компонентами покрита двома шарами вологостійкого лаку. Значення фактору, що впливає 2 1-200 10 5-10 6×104(450) 1,2×104(90) +65 +85 -40 -40 Від -40 до +85 98+25 Модуль формування сигналів синхронізації та управління забезпечує видачу службових сигналів із тактовою частотою 50МГц. Крім того, модуль формування сигналів синхронізації та управління забезпечує формування управляючих сигналів для модуля управління пам'яттю. Ці сигнали забезпечують запис даних до пам'яті з необхідним коефіцієнтом проріджування, перемикання між банками оперативної пам'яті та поточне управління мікросхемами для забезпечення потрібного алгоритму роботи. Модуль комутації сигналів забезпечує формування інформаційних потоків для обробки сигналів і запису їх у пам'ять. Модуль управління пам'яттю забезпечує буферизацію даних для обміну між модулями ПЛІС і складається з двох незалежних модулів керування мікросхемами динамічної пам'я ті. Кожен модуль керування мікросхемою забезпечує темп обміну даними при запису або зчитуванні - не менш 50 Мслівх32 у секунду і може знаходитися або в стані запису, або в стані зчитування незалежно один від одного. Модуль цифрової обробки, модуль управління пам'яттю, контролер передачі даних на інтерфейсну шину, модуль формування сигналів синхронізації та управління формуються усередині ПЛІС у вигляді скомпільованих ядер. Джерела інформації: 1. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного.// Электроника: наука, технология, бизнес. - Москва. - 2004, № 8, С. 34 40. http://www.electronics.ru/pdf78_2004/07.pdf. - аналог. 2. Заявка на видачу патенту України на корисну модель. МІЖ 7 G 01 S 13/08-13/44, G 01 S 7/027/46, H 02 К 15/00-15/16. Пристрій аналогоцифрового перетворення. // Слюсар B.I., Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М.- прототип 17 Комп’ютерна в ерстка А. Крижанівський 38235 Підписне 18 Тираж 28 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюCombining module of digital signal processing

Автори англійськоюSliusar Vadym Ivanovych, Voloschuk Ihor Viktorovych, Hrytsenko Viktor Mykolaiovych, Bondarenko Maksym Vasyliovych, Malaschuk Volodymyr Petrovych, Shatsman Leonid Heorhiiovych, Nikitin Mykola Mykhailovych

Назва патенту російськоюОбъединительный модуль цифровой обработки сигналов

Автори російськоюСлюсар Вадим Иванович, Волощук Игорь Викторович, Гриценко Виктор Николаевич, Бондаренко Максим Васильевич, Малащук Владимир Петрович, Шацман Леонид Георгиевич, Никитин Николай Михайлович

МПК / Мітки

МПК: G01S 7/00, G01S 13/00

Мітки: об'єднавчий, цифрової, модуль, обробки, сигналів

Код посилання

<a href="https://ua.patents.su/9-38235-obehdnavchijj-modul-cifrovo-obrobki-signaliv.html" target="_blank" rel="follow" title="База патентів України">Об’єднавчий модуль цифрової обробки сигналів</a>

Попередній патент: Спосіб оцінки рівня адаптаційних можливостей організму осіб, що займаються фізичною культурою та спортом, “паспорт здоров`я”

Наступний патент: Спосіб знешкодження збудників інвазійних хвороб овочів, фруктів, ягід та їстівної зелені

Випадковий патент: Спосіб лікування вагінального дисбіозу у дівчаток-підлітків