Перетворювач двійково-k-значного коду в двійковий код

Номер патенту: 119896

Опубліковано: 10.10.2017

Автори: Вареца Віталій Вікторович, Литвинова Євгенія Іванівна, Какурін Микола Яковлевич, Макаренко Ганна Миколаївна, Хаханов Володимир Іванович

Формула / Реферат

Перетворювач двійково-K-значного коду у двійковий код, що містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що має прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, третю групу CD-тригерів, третій регістр стану, для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, виходи якого є виходами перетворювача коду, першу і другу групи з n елементів І, першу і другу групи з n елементів І-НІ, першу і другу групи з n елементів НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку a, в кожному розряді дешифратор рівняння або перевищення кроку b, в кожному розряді кодовий шифратор, що на виході формує значення коду зменшене на значення третього кроку b, у разі рівняння або перевищення кроку b, формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником і одночасно маючим значення менше кроку b, у разі, коли значення стану відповідного лічильника менше кроку а, кодовий шифратор передає код зі входу на вихід без зміни, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, причому другі входи кожної з n груп елементів АБО є інформаційними входами для запису значень відповідних розрядів, а перші входи кожної з n груп елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному розряді з'єднані з відповідними виходами лічильника цього розряду, а також з відповідними входами дешифратора нуля, дешифратора рівняння або перевищення кроку а, дешифратора рівняння або перевищення кроку b, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами тригерів першої групи, першого регістра стану, виходи дешифраторів рівняння або перевищення кроку а з'єднані з відповідними інформаційними D-входами тригерів другої групи, виходи дешифраторів рівняння або перевищення кроку b з'єднані з відповідними інформаційними D-входами тригерів третьої групи, входи синхронізації тригерів усіх трьох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першого регістра стану з'єднані з відповідними першими входами елементів І першої групи, другі відповідні входи елементів І першої групи з'єднані з відповідними виходами елементів НІ першої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригерів стану другої групи, перші входи елементів І-НІ першої і другої груп з'єднані з прямим виходом тригера стану відповідно другої і третьої групи, другі входи елементів І-НІ першої групи з'єднані з відповідними виходами елементів НІ другої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригера стану третього регістра, треті входи елементів І першої групи, треті входи елементів І-НІ першої групи, а також другі входи елементів І-НІ другої групи з'єднані з виходом першого затриманого імпульсу генератора імпульсів, інверсні виходи елементів І-НІ першої і другої групи у кожному розряді з'єднані відповідно з першим і другим входом елемента І другої групи цього розряду, виходи елементів І другої групи з'єднані з інверсним входом V у лічильнику відповідного розряду, виходи елементів І першої групи з'єднані з входом віднімання -1 у лічильнику відповідного розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані зі входом +1 лічильника наступного розряду, вхід +1 лічильника молодшого розряду є входом запису числа для перетворення у число-імпульсному коді, формувач еквівалентів ФЕ, що складається з першого, другого та третього дешифраторів, першого, другого та третього шифраторів, першого та другого комбінаційних суматорів та двох груп елементів І з двома входами на входах першого і другого дешифраторів у ФЕ, перші входи елементів І першої і другої груп з'єднані з відповідними прямими інформаційними виходами D-тригерів першого і відповідно другого регістра стану, другі входи яких з'єднані з інверсними виходами D-тригерів другого і відповідно третього регістра стану у відповідному розряді, інверсні входи синхронізації усіх дешифраторів у формувачі еквівалентів з'єднані з землею, інверсні виходи першого, другого і третього дешифраторів з'єднані з відповідними входами першого, другого і третього шифраторів, виходи другого і третього шифраторів з'єднані з відповідними входами першої і другої групи входів першого комбінаційного суматора, виходи першого шифратора з'єднані з відповідними входами першої групи входів у другому комбінаційному суматорі, виходи першого комбінаційного суматора з'єднані з відповідними входами другої групи входів другого комбінаційного суматора у формувачі еквівалентів, виходи формувача еквівалентів з'єднані з відповідними входами накопичувального суматора, управляючий вхід накопичувального суматора з'єднаний з виходом другого затриманого імпульсу генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, який відрізняється тим, що в перетворювач коду додатково введена четверта і п'ята групи CD-тригерів стану, третя і четверта групи елементів НІ, третя і четверта групи елементів І-НІ, по два додаткових входи (третьому і четвертому) в кожний елемент І другої групи, в кожний розряд введено по додатковому дешифратору рівняння або перевищеннячетвертого кроку с і по додатковому дешифратору рівняння або перевищення п'ятого кроку d, а в формувач еквівалентів додатково введені четвертий і п'ятий дешифратори, четвертий і п'ятий шифратори, дві групи із n елементів І на входах третього і четвертого дешифраторів та два додаткових комбінаційних суматори, інверсні входи синхронізації четвертого і п'ятого дешифраторів у формувачі еквівалентів з'єднані з землею, інверсні виходи четвертого і п'ятого дешифраторів з'єднані з відповідними входами четвертого і п'ятого шифраторів, інверсні виходи яких з'єднані з відповідними входами першої і другої групи входів першого додаткового комбінаційного суматора у формувачі еквівалентів, виходи першого додаткового комбінаційного суматора з'єднані з відповідними входами другої групи входів другого додаткового комбінаційного суматора, перші входи якого з'єднані з відповідними виходами першого основного суматора у формувачі еквівалентів, виходи другого додаткового комбінаційного суматора з'єднані з відповідними входами другої групи входів другого основного комбінаційного суматора, виходи четвертого дешифратора рівняння і перевищення кроку с з'єднані з відповідними інформаційними D-входами четвертої групи тригерів стану, виходи п'ятого дешифратора рівняння або перевищення кроку d з'єднані з відповідними інформаційними D-входами п'ятої групи тригерів стану, входи синхронізації тригерів стану четвертої і п'ятої груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів стану четвертої і п'ятої групи з'єднані з відповідними першими входами елементів І-НІ відповідно третьої і четвертої групи, другі входи яких у четвертій групі і треті входи у третій групі з'єднані з виходом першого затриманого імпульсу генератора імпульсів, інверсні виходи елементів І-НІ третьої і четвертої групи з'єднані відповідно з третім та четвертим входами елементів І другої групи, прямі виходи тригерів стану четвертої групи з'єднані з відповідними входами елементів НІ третьої групи, інверсні виходи яких з'єднані з відповідними другими входами елементів I-НІ другої групи, прямі виходи тригерів стану п'ятої групи з'єднані з першими входами елементів І-НІ четвертої групи у відповідному розряді і з відповідними входами елементів НІ четвертої групи, інверсні виходи яких з'єднані з відповідними другими входами елементів І-НІ третьої групи, інверсні виходи яких з'єднані з відповідними третіми входами елементів І другої групи, інверсні виходи елементів І-НІ четвертої групи з'єднані з відповідними четвертими входами елементів І другої групи, треті входи усіх елементів І-НІ третьої групи і другі входи усіх елементів І-НІ четвертої групи з’єднані з виходом першого прямого затриманого імпульсу генератора імпульсів, перші входи елементів І на входах третього дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера третього регістра стану, другі входи елементів І на входах третього дешифратора з'єднані з відповідним інверсним виходом D-тригера цього розряду, але четвертого регістра стану, виходи елементів І на входах третього дешифратора з'єднано з відповідними входами цього дешифратора, перші входи елементів І на входах четвертого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом D-тригера четвертого регістра стану, другі входи елементів І на входах четвертого дешифратора з'єднані з відповідним інверсним виходом D-тригера цього розряду, але п'ятого регістра стану, виходи елементів І на входах четвертого дешифратора з'єднано з відповідними входами цього дешифратора, інформаційні входи п'ятого дешифратора у формувачі еквівалентів з'єднані з відповідними прямими виходами D-тригера п'ятого регістра стану.

Текст

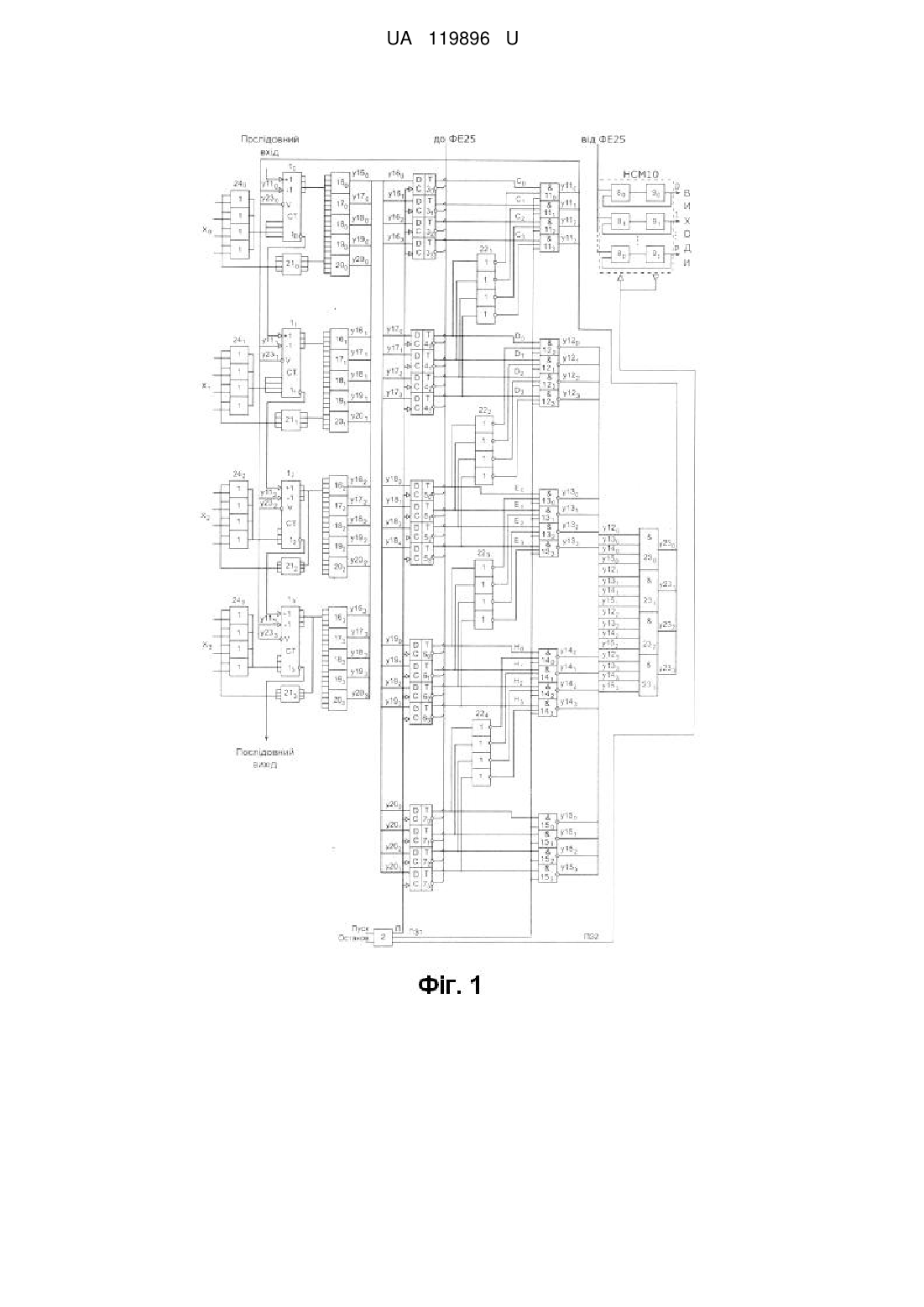

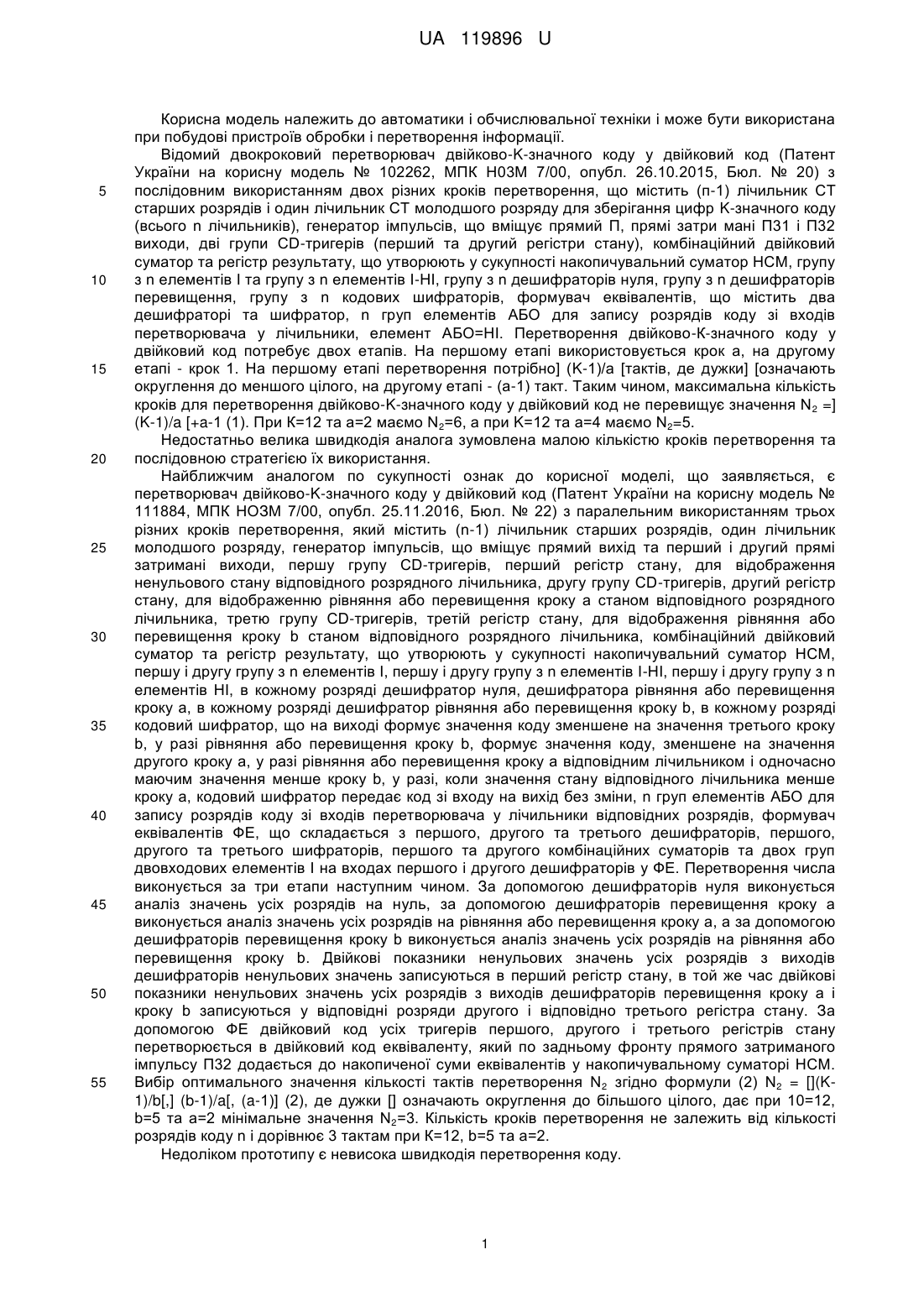

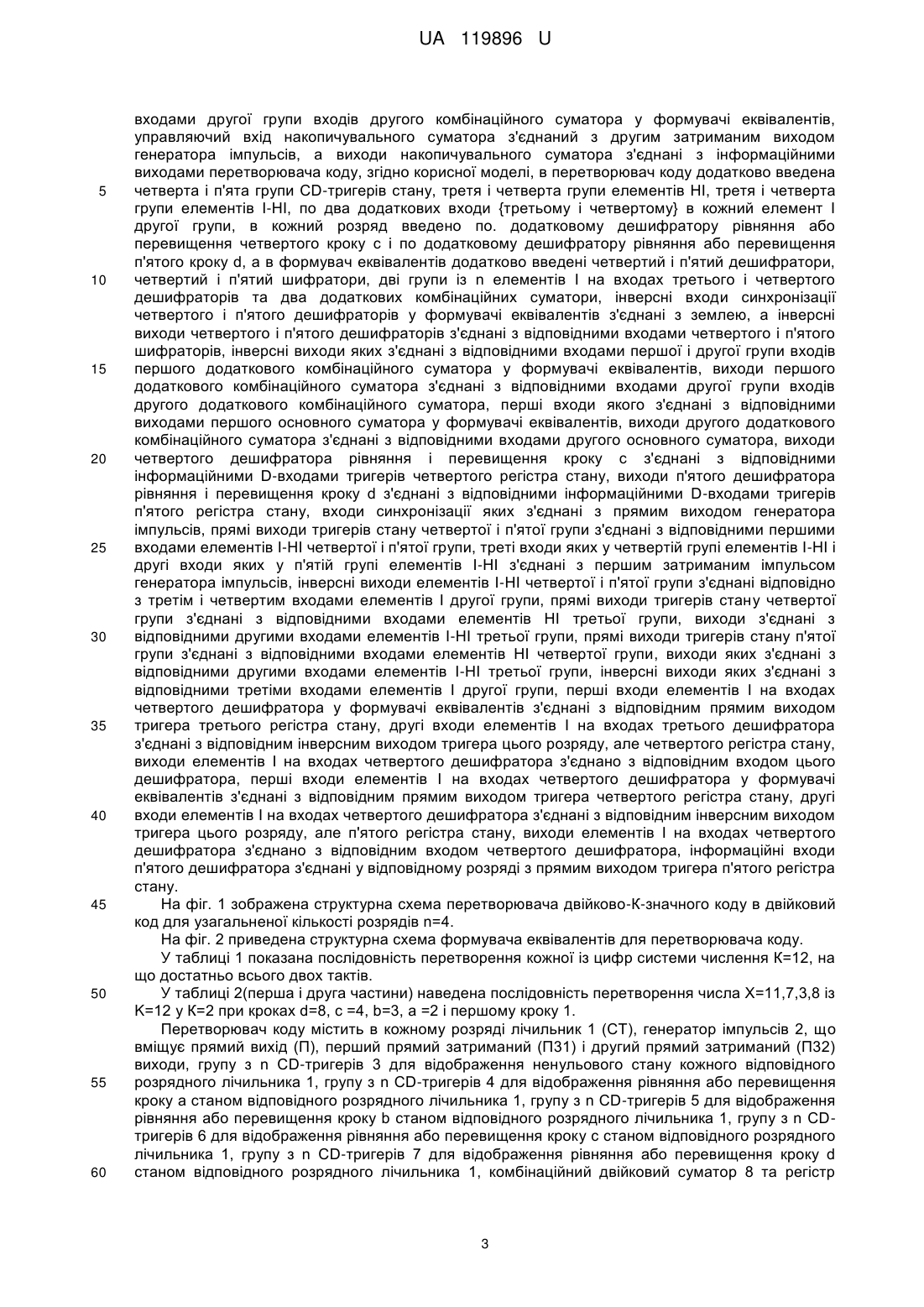

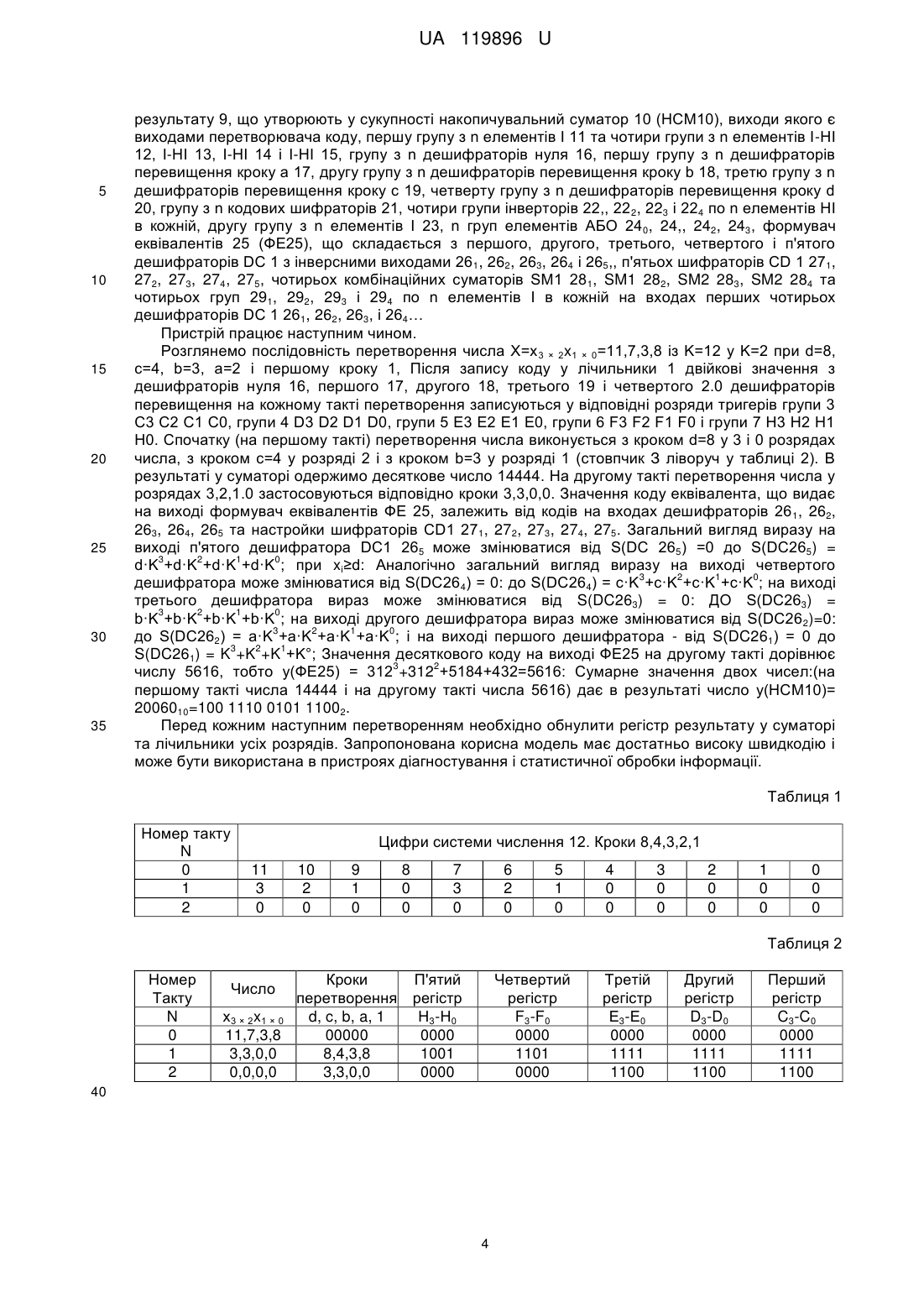

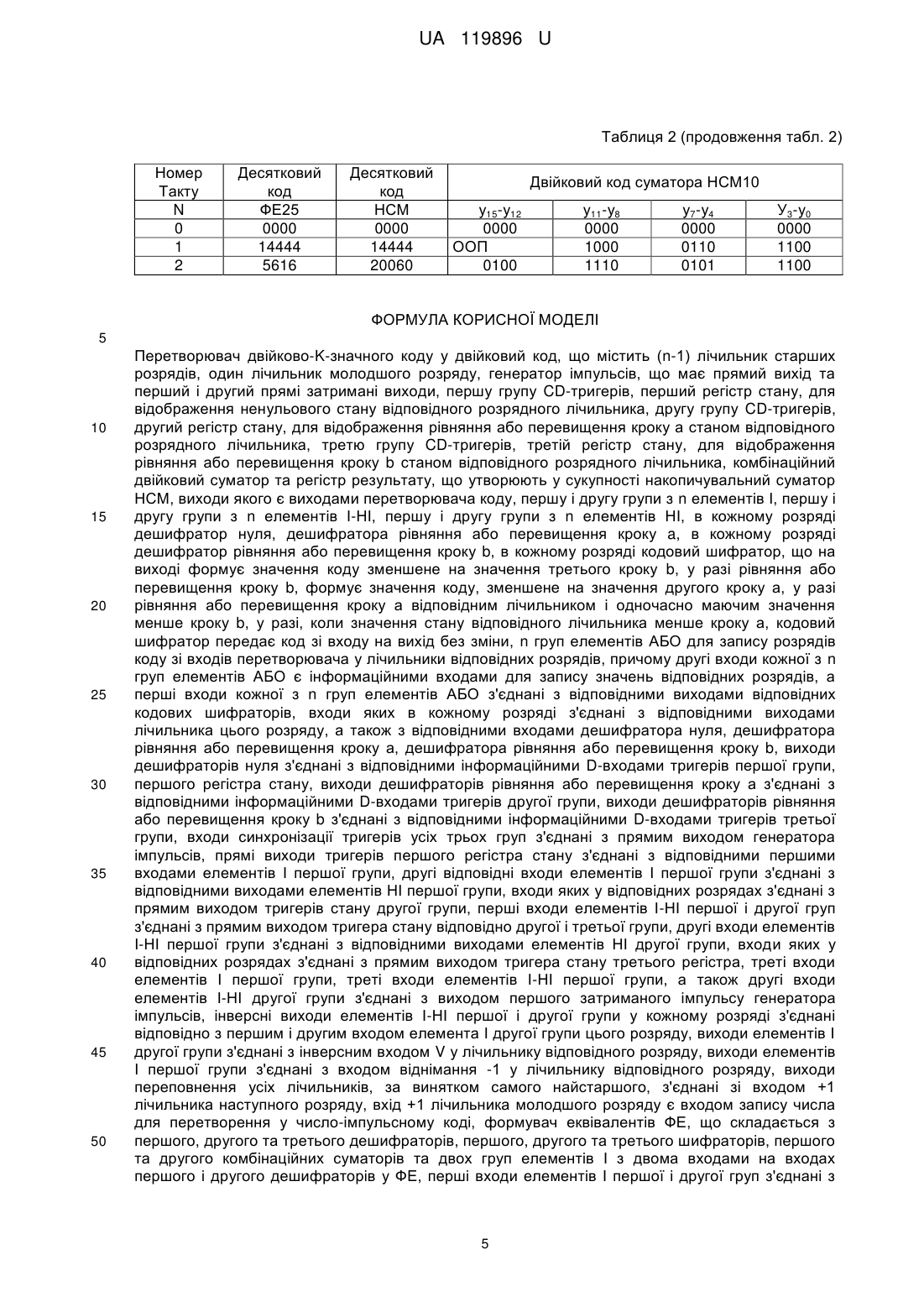

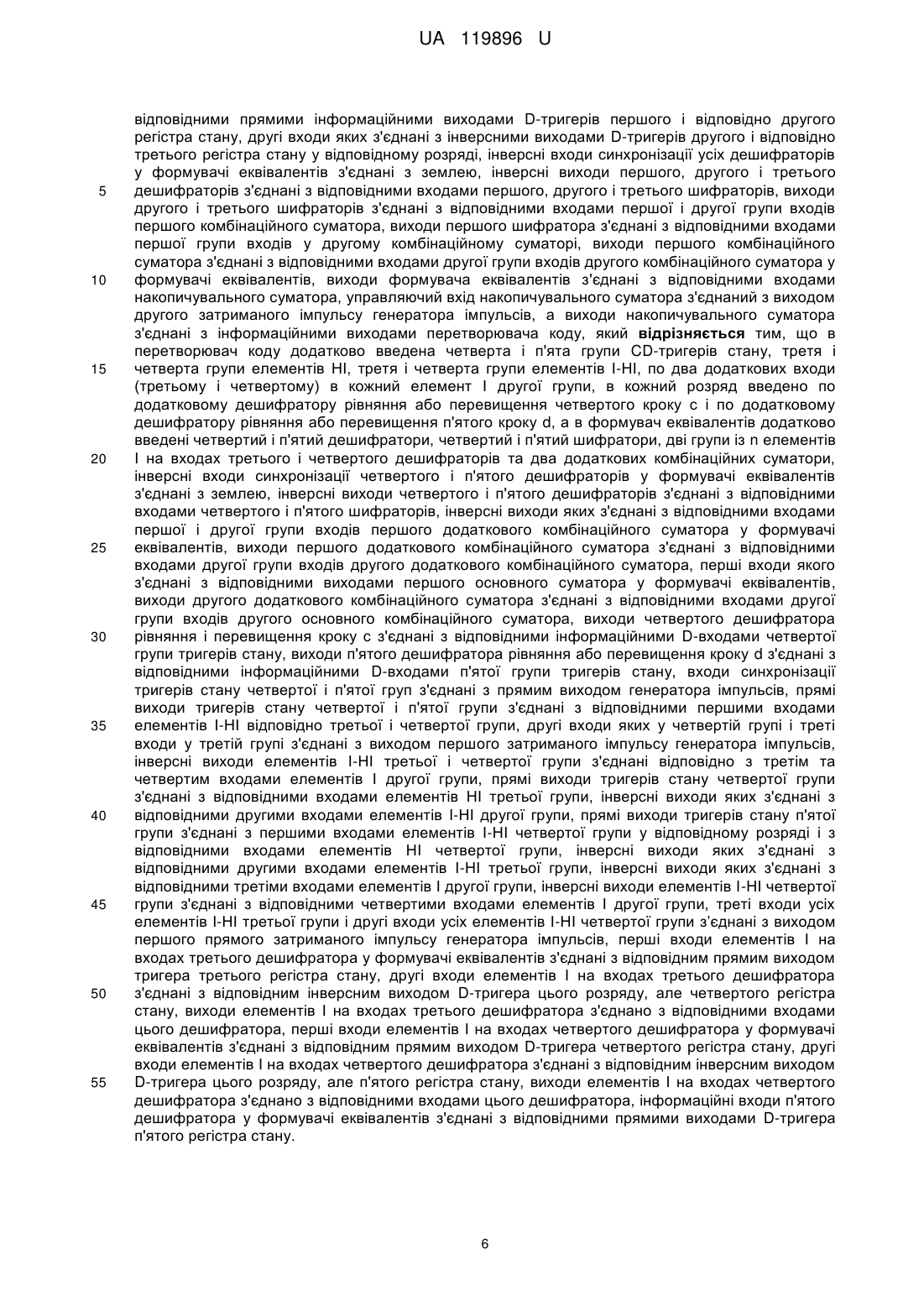

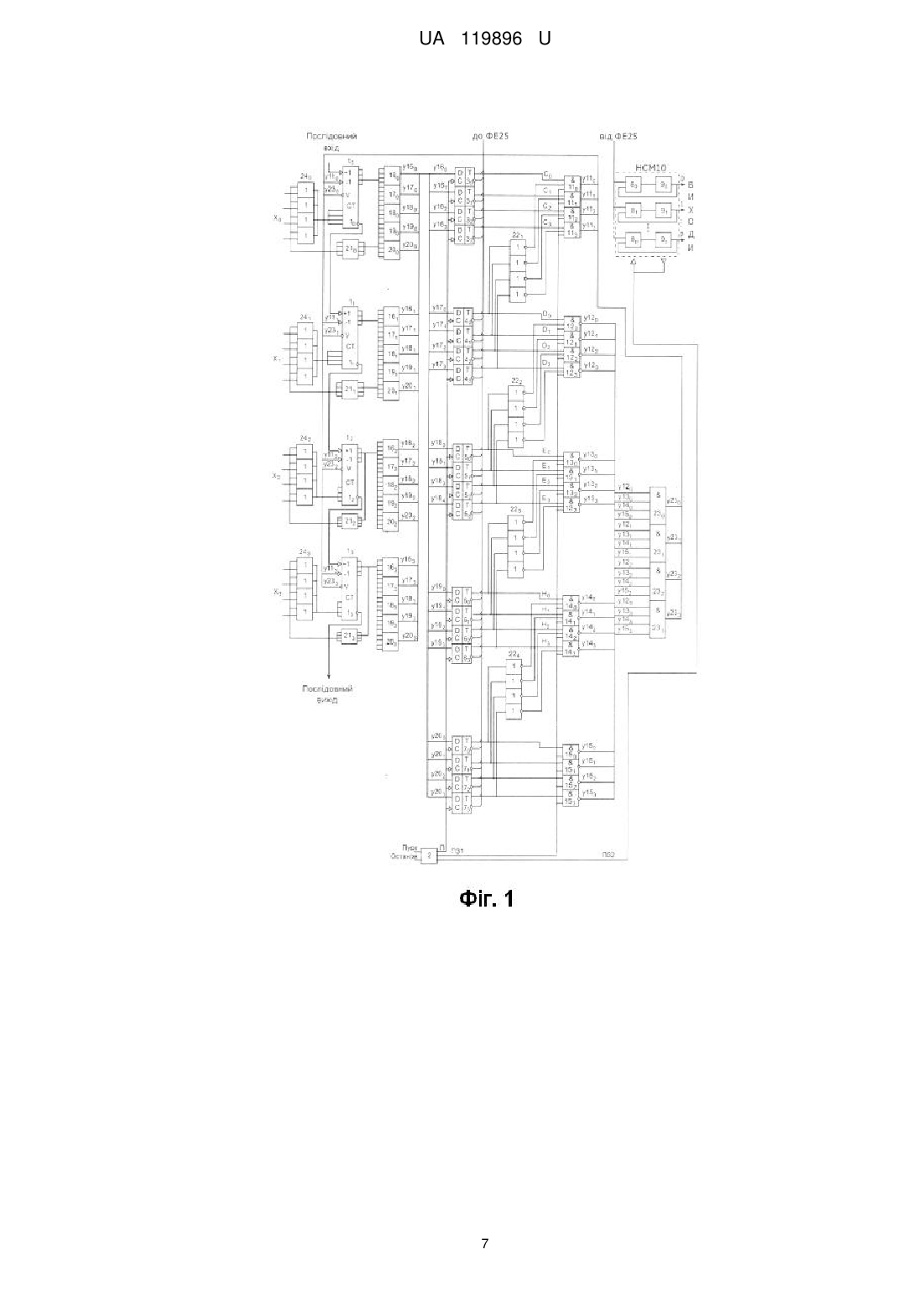

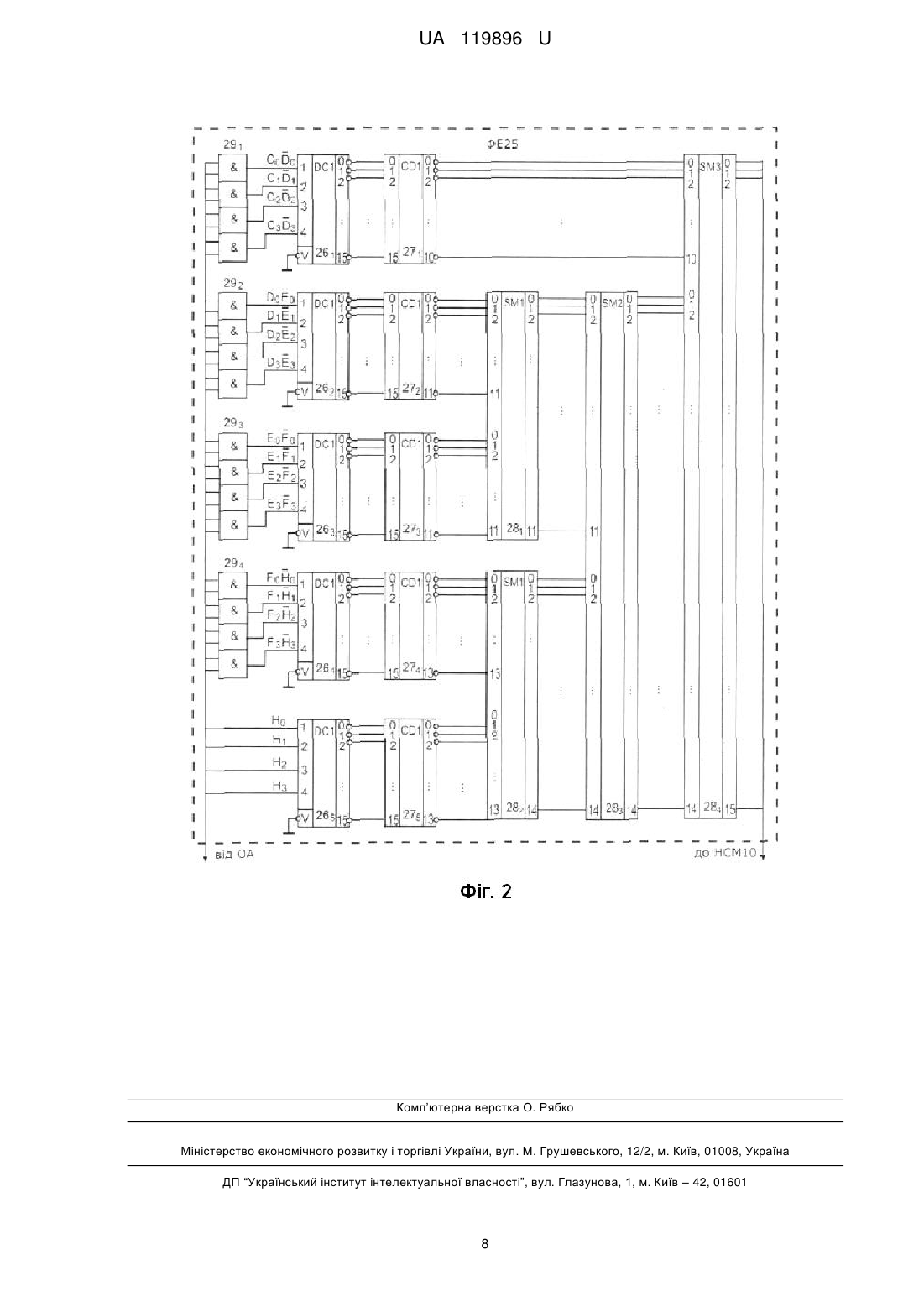

Реферат: Перетворювач двійково-K-значного коду у двійковий код містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що має прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, другу групу CD-тригерів, другий регістр стану, третю групу CD-тригерів, третій регістр стану, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, виходи якого є виходами перетворювача коду, першу і другу групи з n елементів І, першу і другу групи з n елементів І-НІ, першу і другу групи з n елементів НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, В перетворювач коду додатково введена четверта і п'ята групи CD-тригерів стану, третя і четверта групи елементів НІ, третя і четверта групи елементів І-НІ, по два додаткових входи (третьому і четвертому) в кожний елемент І другої групи, в кожний розряд введено по додатковому дешифратору рівняння або перевищення четвертого кроку с і по додатковому дешифратору рівняння або перевищення п'ятого кроку d. В формувач еквівалентів додатково введені четвертий і п'ятий дешифратори, четвертий і п'ятий шифратори, дві групи із n елементів І на входах третього і четвертого дешифраторів та два додаткових комбінаційних суматори. UA 119896 U (54) ПЕРЕТВОРЮВАЧ ДВІЙКОВО-K-ЗНАЧНОГО КОДУ В ДВІЙКОВИЙ КОД UA 119896 U UA 119896 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до автоматики і обчислювальної техніки і може бути використана при побудові пристроїв обробки і перетворення інформації. Відомий двокроковий перетворювач двійково-K-значного коду у двійковий код (Патент України на корисну модель № 102262, МПК Н03М 7/00, опубл. 26.10.2015, Бюл. № 20) з послідовним використанням двох різних кроків перетворення, що містить (п-1) лічильник СТ старших розрядів і один лічильник СТ молодшого розряду для зберігання цифр K-значного коду (всього n лічильників), генератор імпульсів, що вміщує прямий П, прямі затри мані П31 і П32 виходи, дві групи CD-тригерів (перший та другий регістри стану), комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з n елементів І та групу з n елементів І-НІ, групу з n дешифраторів нуля, групу з n дешифраторів перевищення, групу з n кодових шифраторів, формувач еквівалентів, що містить два дешифраторі та шифратор, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники, елемент АБО=НІ. Перетворення двійково-К-значного коду у двійковий код потребує двох етапів. На першому етапі використовується крок а, на другому етапі - крок 1. На першому етапі перетворення потрібно] (K-1)/а [тактів, де дужки] [означають округлення до меншого цілого, на другому етапі - (а-1) такт. Таким чином, максимальна кількість кроків для перетворення двійково-K-значного коду у двійковий код не перевищує значення N 2 =] (K-1)/a [+a-1 (1). При К=12 та а=2 маємо N2=6, а при K=12 та а=4 маємо N2=5. Недостатньо велика швидкодія аналога зумовлена малою кількістю кроків перетворення та послідовною стратегією їх використання. Найближчим аналогом по сукупності ознак до корисної моделі, що заявляється, є перетворювач двійково-K-значного коду у двійковий код (Патент України на корисну модель № 111884, МПК НОЗМ 7/00, опубл. 25.11.2016, Бюл. № 22) з паралельним використанням трьох різних кроків перетворення, який містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображенню рівняння або перевищення кроку а станом відповідного розрядного лічильника, третю групу CD-тригерів, третій регістр стану, для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, першу і другу групу з n елементів І, першу і другу групу з n елементів І-НІ, першу і другу групу з n елементів НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, в кожному розряді дешифратор рівняння або перевищення кроку b, в кожному розряді кодовий шифратор, що на виході формує значення коду зменшене на значення третього кроку b, у разі рівняння або перевищення кроку b, формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником і одночасно маючим значення менше кроку b, у разі, коли значення стану відповідного лічильника менше кроку а, кодовий шифратор передає код зі входу на вихід без зміни, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, формувач еквівалентів ФЕ, що складається з першого, другого та третього дешифраторів, першого, другого та третього шифраторів, першого та другого комбінаційних суматорів та двох груп двовходових елементів І на входах першого і другого дешифраторів у ФЕ. Перетворення числа виконується за три етапи наступним чином. За допомогою дешифраторів нуля виконується аналіз значень усіх розрядів на нуль, за допомогою дешифраторів перевищення кроку а виконується аналіз значень усіх розрядів на рівняння або перевищення кроку а, а за допомогою дешифраторів перевищення кроку b виконується аналіз значень усіх розрядів на рівняння або перевищення кроку b. Двійкові показники ненульових значень усіх розрядів з виходів дешифраторів ненульових значень записуються в перший регістр стану, в той же час двійкові показники ненульових значень усіх розрядів з виходів дешифраторів перевищення кроку а і кроку b записуються у відповідні розряди другого і відповідно третього регістра стану. За допомогою ФЕ двійковий код усіх тригерів першого, другого і третього регістрів стану перетворюється в двійковий код еквіваленту, який по задньому фронту прямого затриманого імпульсу П32 додається до накопиченої суми еквівалентів у накопичувальному суматорі НСМ. Вибір оптимального значення кількості тактів перетворення N2 згідно формули (2) N2 = [](K1)/b[,] (b-1)/a[, (a-1)] (2), де дужки [] означають округлення до більшого цілого, дає при 10=12, b=5 та а=2 мінімальне значення N2=3. Кількість кроків перетворення не залежить від кількості розрядів коду n і дорівнює 3 тактам при К=12, b=5 та а=2. Недоліком прототипу є невисока швидкодія перетворення коду. 1 UA 119896 U 5 10 15 20 25 30 35 40 45 50 55 60 В основу корисної моделі поставлена задача підвищення швидкодії трикрокового перетворювача двійково-K-значного коду у двійковий код за рахунок використання паралельної стратегії п'ятьох різних кроків перетворення та нового схемного рішення. Поставлена задача вирішується тим, що в перетворювач двійково-К-значного коду у двійковий код, що містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, третю групу CDтригерів, третій регістр стану, для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, виходи якого є виходами перетворювача коду, першу і другу групи з n елементів І, першу і другу групи з n елементів І-НІ, першу і другу групи з n елементів НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, в кожному розряді дешифратор рівняння або перевищення кроку b, в кожному розряді кодовий шифратор, що на виході формує значення коду зменшене на значення третього кроку b, у разі рівняння або перевищення кроку b, формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником і одночасно маючим значення менше кроку b, у разі, коли значення стану відповідного лічильника менше кроку а, кодовий шифратор передає код зі входу на вихід без зміни, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, причому другі входи кожної з n груп елементів АБО є інформаційними входами для запису значень відповідних розрядів, а перші входи кожної з n груп елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному розряді з'єднані з відповідними виходами лічильника цього розряду, а також з відповідними входами дешифратора нуля, дешифратора рівняння або перевищення кроку а, дешифратора рівняння або перевищення кроку b, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами тригерів першої групи, першого регістра стану, виходи дешифраторів рівняння або перевищення кроку а з'єднані з відповідними інформаційними Dвходами тригерів другої групи, виходи дешифраторів рівняння або перевищення кроку b з'єднані з відповідними інформаційними D-входами тригерів третьої групи, входи синхронізації тригерів усіх трьох груп з'єднані, з прямим виходом генератора імпульсів, прямі виходи тригерів першого регістра стану з'єднані з відповідними першими входами елементів І першої групи, другі відповідні входи елементів І першої групи з'єднані з відповідними виходами елементів НІ першої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригерів стану другої групи, перші входи елементів І-НІ першої і другої груп з'єднані з прямим виходом тригера стану відповідно другої і третьої групи, другі входи елементів І-НІ першої групи з'єднані з відповідними виходами елементів НІ другої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригера стану третього регістра, входи синхронізації тригерів стану усіх трьох груп з'єднані з прямим виходом генератора імпульсів, треті входи елементів І першої групи, треті входи елементів І-НІ першої групи, а також другі входи елементів І-НІ другої групи з'єднані з першим затриманим імпульсом генератора імпульсів, інверсні виходи елементів І-НІ першої і другої групи у кожному розряді з'єднані відповідно з першим і другим входом елемента І другої групи цього розряду, виходи елементів І другої групи з'єднані з інверсним входом V у лічильнику відповідного розряду, виходи елементів І першої групи з'єднані з входом віднімання -1 у лічильнику відповідного розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані зі входом +1 лічильника наступного розряду, вхід +1 лічильника молодшого розряду є входом запису числа для перетворення у число-імпульсному коді, формувач еквівалентів ФЕ, що складається з першого, другого та третього дешифраторів, першого, другого та третього шифраторів, першого та другого комбінаційних суматорів та двох груп двовходових елементів І на входах першого і другого дешифраторів у ФЕ, перші входи елементів І першої і другої груп з'єднані з відповідними прямими інформаційними виходами Dтригерів першого і відповідно другого регістра стану, другі входи яких з'єднані з інверсними виходами D-тригерів другого і відповідно третього регістра стану у відповідному розряді, інверсні входи синхронізації усіх дешифраторів у формувачі еквівалентів з'єднані з землею, інверсні виходи першого, другого і третього дешифраторів з'єднані з відповідними входами першого, другого і третього шифраторів, виходи другого і третього шифраторів з'єднані з відповідними входами першої і другої групи входів першого комбінаційного суматора, виходи першого шифратора з'єднані з відповідними входами першої групи входів у другому комбінаційному суматорі, виходи першого комбінаційного суматора з'єднані з відповідними 2 UA 119896 U 5 10 15 20 25 30 35 40 45 50 55 60 входами другої групи входів другого комбінаційного суматора у формувачі еквівалентів, управляючий вхід накопичувального суматора з'єднаний з другим затриманим виходом генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, згідно корисної моделі, в перетворювач коду додатково введена четверта і п'ята групи CD-тригерів стану, третя і четверта групи елементів НІ, третя і четверта групи елементів І-НІ, по два додаткових входи {третьому і четвертому} в кожний елемент І другої групи, в кожний розряд введено по. додатковому дешифратору рівняння або перевищення четвертого кроку с і по додатковому дешифратору рівняння або перевищення п'ятого кроку d, а в формувач еквівалентів додатково введені четвертий і п'ятий дешифратори, четвертий і п'ятий шифратори, дві групи із n елементів І на входах третього і четвертого дешифраторів та два додаткових комбінаційних суматори, інверсні входи синхронізації четвертого і п'ятого дешифраторів у формувачі еквівалентів з'єднані з землею, а інверсні виходи четвертого і п'ятого дешифраторів з'єднані з відповідними входами четвертого і п'ятого шифраторів, інверсні виходи яких з'єднані з відповідними входами першої і другої групи входів першого додаткового комбінаційного суматора у формувачі еквівалентів, виходи першого додаткового комбінаційного суматора з'єднані з відповідними входами другої групи входів другого додаткового комбінаційного суматора, перші входи якого з'єднані з відповідними виходами першого основного суматора у формувачі еквівалентів, виходи другого додаткового комбінаційного суматора з'єднані з відповідними входами другого основного суматора, виходи четвертого дешифратора рівняння і перевищення кроку с з'єднані з відповідними інформаційними D-входами тригерів четвертого регістра стану, виходи п'ятого дешифратора рівняння і перевищення кроку d з'єднані з відповідними інформаційними D-входами тригерів п'ятого регістра стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів стану четвертої і п'ятої групи з'єднані з відповідними першими входами елементів І-НІ четвертої і п'ятої групи, треті входи яких у четвертій групі елементів І-НІ і другі входи яких у п'ятій групі елементів I-НІ з'єднані з першим затриманим імпульсом генератора імпульсів, інверсні виходи елементів І-НІ четвертої і п'ятої групи з'єднані відповідно з третім і четвертим входами елементів І другої групи, прямі виходи тригерів стану четвертої групи з'єднані з відповідними входами елементів НІ третьої групи, виходи з'єднані з відповідними другими входами елементів І-НІ третьої групи, прямі виходи тригерів стану п'ятої групи з'єднані з відповідними входами елементів НІ четвертої групи, виходи яких з'єднані з відповідними другими входами елементів І-НІ третьої групи, інверсні виходи яких з'єднані з відповідними третіми входами елементів І другої групи, перші входи елементів І на входах четвертого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера третього регістра стану, другі входи елементів І на входах третього дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але четвертого регістра стану, виходи елементів І на входах четвертого дешифратора з'єднано з відповідним входом цього дешифратора, перші входи елементів І на входах четвертого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера четвертого регістра стану, другі входи елементів І на входах четвертого дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але п'ятого регістра стану, виходи елементів І на входах четвертого дешифратора з'єднано з відповідним входом четвертого дешифратора, інформаційні входи п'ятого дешифратора з'єднані у відповідному розряді з прямим виходом тригера п'ятого регістра стану. На фіг. 1 зображена структурна схема перетворювача двійково-К-значного коду в двійковий код для узагальненої кількості розрядів n=4. На фіг. 2 приведена структурна схема формувача еквівалентів для перетворювача коду. У таблиці 1 показана послідовність перетворення кожної із цифр системи числення К=12, на що достатньо всього двох тактів. У таблиці 2(перша і друга частини) наведена послідовність перетворення числа Х=11,7,3,8 із K=12 у К=2 при кроках d=8, с =4, b=3, а =2 і першому кроку 1. Перетворювач коду містить в кожному розряді лічильник 1 (СТ), генератор імпульсів 2, що вміщує прямий вихід (П), перший прямий затриманий (П31) і другий прямий затриманий (П32) виходи, групу з n CD-тригерів 3 для відображення ненульового стану кожного відповідного розрядного лічильника 1, групу з n CD-тригерів 4 для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника 1, групу з n CD-тригерів 5 для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника 1, групу з n CDтригерів 6 для відображення рівняння або перевищення кроку с станом відповідного розрядного лічильника 1, групу з n CD-тригерів 7 для відображення рівняння або перевищення кроку d станом відповідного розрядного лічильника 1, комбінаційний двійковий суматор 8 та регістр 3 UA 119896 U 5 10 15 20 25 30 35 результату 9, що утворюють у сукупності накопичувальний суматор 10 (НСМ10), виходи якого є виходами перетворювача коду, першу групу з n елементів І 11 та чотири групи з n елементів І-НІ 12, І-НІ 13, І-НІ 14 і І-НІ 15, групу з n дешифраторів нуля 16, першу групу з n дешифраторів перевищення кроку а 17, другу групу з n дешифраторів перевищення кроку b 18, третю групу з n дешифраторів перевищення кроку с 19, четверту групу з n дешифраторів перевищення кроку d 20, групу з n кодових шифраторів 21, чотири групи інверторів 22,, 22 2, 223 і 224 по n елементів НІ в кожній, другу групу з n елементів І 23, n груп елементів АБО 24 0, 24,, 242, 243, формувач еквівалентів 25 (ФЕ25), що складається з першого, другого, третього, четвертого і п'ятого дешифраторів DC 1 з інверсними виходами 261, 262, 263, 264 і 265,, п'ятьох шифраторів CD 1 271, 272, 273, 274, 275, чотирьох комбінаційних суматорів SM1 281, SM1 282, SM2 283, SM2 284 та чотирьох груп 291, 292, 293 і 294 по n елементів І в кожній на входах перших чотирьох дешифраторів DC 1 261, 262, 263, і 264… Пристрій працює наступним чином. Розглянемо послідовність перетворення числа Х=х 3 × 2x1 × 0=11,7,3,8 із K=12 у K=2 при d=8, c=4, b=3, а=2 і першому кроку 1, Після запису коду у лічильники 1 двійкові значення з дешифраторів нуля 16, першого 17, другого 18, третього 19 і четвертого 2.0 дешифраторів перевищення на кожному такті перетворення записуються у відповідні розряди тригерів групи 3 С3 С2 С1 C0, групи 4 D3 D2 D1 D0, групи 5 Е3 Е2 Е1 Е0, групи 6 F3 F2 F1 F0 і групи 7 Н3 Н2 Н1 Н0. Спочатку (на першому такті) перетворення числа виконується з кроком d=8 у 3 і 0 розрядах числа, з кроком с=4 у розряді 2 і з кроком b=3 у розряді 1 (стовпчик З ліворуч у таблиці 2). В результаті у суматорі одержимо десяткове число 14444. На другому такті перетворення числа у розрядах 3,2,1.0 застосовуються відповідно кроки 3,3,0,0. Значення коду еквівалента, що видає на виході формувач еквівалентів ФЕ 25, залежить від кодів на входах дешифраторів 26 1, 262, 263, 264, 265 та настройки шифраторів CD1 271, 272, 273, 274, 275. Загальний вигляд виразу на виході п'ятого дешифратора DC1 265 може змінюватися від S(DC 265) =0 до S(DC265) = 3 2 1 0 d·K +d·K +d·K +d·K ; при xi≥d: Аналогічно загальний вигляд виразу на виході четвертого 3 2 1 0 дешифратора може змінюватися від S(DC264) = 0: до S(DC264) = c·K +с·K +с·K +с·K ; на виході третього дешифратора вираз може змінюватися від S(DC263) = 0: ДО S(DC263) = 3 2 1 0 b·K +b·K +b·K +b·K ; на виході другого дешифратора вираз може змінюватися від S(DС26 2)=0: 3 2 1 0 до S(DC262) = a·K +a·K +a·K +a·K ; і на виході першого дешифратора - від S(DC261) = 0 до 3 2 1 S(DC261) = K +K +K +K°; Значення десяткового коду на виході ФЕ25 на другому такті дорівнює 3 2 числу 5616, тобто у(ФЕ25) = 312 +312 +5184+432=5616: Сумарне значення двох чисел:(на першому такті числа 14444 і на другому такті числа 5616) дає в результаті число у(НСМ10)= 2006010=100 1110 0101 11002. Перед кожним наступним перетворенням необхідно обнулити регістр результату у суматорі та лічильники усіх розрядів. Запропонована корисна модель має достатньо високу швидкодію і може бути використана в пристроях діагностування і статистичної обробки інформації. Таблиця 1 Номер такту N 0 1 2 Цифри системи числення 12. Кроки 8,4,3,2,1 11 3 0 10 2 0 9 1 0 8 0 0 7 3 0 6 2 0 5 1 0 4 0 0 3 0 0 2 0 0 1 0 0 0 0 0 Таблиця 2 Номер Такту N 0 1 2 Кроки П'ятий перетворення регістр х 3 × 2x 1 × 0 d, c, b, a, 1 Н3-Н0 11,7,3,8 00000 0000 3,3,0,0 8,4,3,8 1001 0,0,0,0 3,3,0,0 0000 Четвертий регістр F3-F0 0000 1101 0000 Число 40 4 Третій регістр Е3-Е0 0000 1111 1100 Другий регістр D3-D0 0000 1111 1100 Перший регістр C3-C0 0000 1111 1100 UA 119896 U Таблиця 2 (продовження табл. 2) Номер Такту N 0 1 2 Десятковий код ФЕ25 0000 14444 5616 Десятковий код НCМ 0000 14444 20060 Двійковий код суматора НСМ10 у15-у12 0000 ООП 0100 у11-у8 0000 1000 1110 у7-у4 0000 0110 0101 У3-у0 0000 1100 1100 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 30 35 40 45 50 Перетворювач двійково-K-значного коду у двійковий код, що містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що має прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, третю групу CD-тригерів, третій регістр стану, для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, виходи якого є виходами перетворювача коду, першу і другу групи з n елементів І, першу і другу групи з n елементів І-НІ, першу і другу групи з n елементів НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку a, в кожному розряді дешифратор рівняння або перевищення кроку b, в кожному розряді кодовий шифратор, що на виході формує значення коду зменшене на значення третього кроку b, у разі рівняння або перевищення кроку b, формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником і одночасно маючим значення менше кроку b, у разі, коли значення стану відповідного лічильника менше кроку а, кодовий шифратор передає код зі входу на вихід без зміни, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, причому другі входи кожної з n груп елементів АБО є інформаційними входами для запису значень відповідних розрядів, а перші входи кожної з n груп елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному розряді з'єднані з відповідними виходами лічильника цього розряду, а також з відповідними входами дешифратора нуля, дешифратора рівняння або перевищення кроку а, дешифратора рівняння або перевищення кроку b, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами тригерів першої групи, першого регістра стану, виходи дешифраторів рівняння або перевищення кроку а з'єднані з відповідними інформаційними D-входами тригерів другої групи, виходи дешифраторів рівняння або перевищення кроку b з'єднані з відповідними інформаційними D-входами тригерів третьої групи, входи синхронізації тригерів усіх трьох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першого регістра стану з'єднані з відповідними першими входами елементів І першої групи, другі відповідні входи елементів І першої групи з'єднані з відповідними виходами елементів НІ першої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригерів стану другої групи, перші входи елементів І-НІ першої і другої груп з'єднані з прямим виходом тригера стану відповідно другої і третьої групи, другі входи елементів І-НІ першої групи з'єднані з відповідними виходами елементів НІ другої групи, входи яких у відповідних розрядах з'єднані з прямим виходом тригера стану третього регістра, треті входи елементів І першої групи, треті входи елементів І-НІ першої групи, а також другі входи елементів І-НІ другої групи з'єднані з виходом першого затриманого імпульсу генератора імпульсів, інверсні виходи елементів І-НІ першої і другої групи у кожному розряді з'єднані відповідно з першим і другим входом елемента І другої групи цього розряду, виходи елементів І другої групи з'єднані з інверсним входом V у лічильнику відповідного розряду, виходи елементів І першої групи з'єднані з входом віднімання -1 у лічильнику відповідного розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані зі входом +1 лічильника наступного розряду, вхід +1 лічильника молодшого розряду є входом запису числа для перетворення у число-імпульсному коді, формувач еквівалентів ФЕ, що складається з першого, другого та третього дешифраторів, першого, другого та третього шифраторів, першого та другого комбінаційних суматорів та двох груп елементів І з двома входами на входах першого і другого дешифраторів у ФЕ, перші входи елементів І першої і другої груп з'єднані з 5 UA 119896 U 5 10 15 20 25 30 35 40 45 50 55 відповідними прямими інформаційними виходами D-тригерів першого і відповідно другого регістра стану, другі входи яких з'єднані з інверсними виходами D-тригерів другого і відповідно третього регістра стану у відповідному розряді, інверсні входи синхронізації усіх дешифраторів у формувачі еквівалентів з'єднані з землею, інверсні виходи першого, другого і третього дешифраторів з'єднані з відповідними входами першого, другого і третього шифраторів, виходи другого і третього шифраторів з'єднані з відповідними входами першої і другої групи входів першого комбінаційного суматора, виходи першого шифратора з'єднані з відповідними входами першої групи входів у другому комбінаційному суматорі, виходи першого комбінаційного суматора з'єднані з відповідними входами другої групи входів другого комбінаційного суматора у формувачі еквівалентів, виходи формувача еквівалентів з'єднані з відповідними входами накопичувального суматора, управляючий вхід накопичувального суматора з'єднаний з виходом другого затриманого імпульсу генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, який відрізняється тим, що в перетворювач коду додатково введена четверта і п'ята групи CD-тригерів стану, третя і четверта групи елементів НІ, третя і четверта групи елементів І-НІ, по два додаткових входи (третьому і четвертому) в кожний елемент І другої групи, в кожний розряд введено по додатковому дешифратору рівняння або перевищення четвертого кроку с і по додатковому дешифратору рівняння або перевищення п'ятого кроку d, а в формувач еквівалентів додатково введені четвертий і п'ятий дешифратори, четвертий і п'ятий шифратори, дві групи із n елементів І на входах третього і четвертого дешифраторів та два додаткових комбінаційних суматори, інверсні входи синхронізації четвертого і п'ятого дешифраторів у формувачі еквівалентів з'єднані з землею, інверсні виходи четвертого і п'ятого дешифраторів з'єднані з відповідними входами четвертого і п'ятого шифраторів, інверсні виходи яких з'єднані з відповідними входами першої і другої групи входів першого додаткового комбінаційного суматора у формувачі еквівалентів,виходи першого додаткового комбінаційного суматора з'єднані з відповідними входами другої групи входів другого додаткового комбінаційного суматора, перші входи якого з'єднані з відповідними виходами першого основного суматора у формувачі еквівалентів, виходи другого додаткового комбінаційного суматора з'єднані з відповідними входами другої групи входів другого основного комбінаційного суматора, виходи четвертого дешифратора рівняння і перевищення кроку с з'єднані з відповідними інформаційними D-входами четвертої групи тригерів стану, виходи п'ятого дешифратора рівняння або перевищення кроку d з'єднані з відповідними інформаційними D-входами п'ятої групи тригерів стану, входи синхронізації тригерів стану четвертої і п'ятої груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів стану четвертої і п'ятої групи з'єднані з відповідними першими входами елементів І-НІ відповідно третьої і четвертої групи, другі входи яких у четвертій групі і треті входи у третій групі з'єднані з виходом першого затриманого імпульсу генератора імпульсів, інверсні виходи елементів І-НІ третьої і четвертої групи з'єднані відповідно з третім та четвертим входами елементів І другої групи, прямі виходи тригерів стану четвертої групи з'єднані з відповідними входами елементів НІ третьої групи, інверсні виходи яких з'єднані з відповідними другими входами елементів I-НІ другої групи, прямі виходи тригерів стану п'ятої групи з'єднані з першими входами елементів І-НІ четвертої групи у відповідному розряді і з відповідними входами елементів НІ четвертої групи, інверсні виходи яких з'єднані з відповідними другими входами елементів І-НІ третьої групи, інверсні виходи яких з'єднані з відповідними третіми входами елементів І другої групи, інверсні виходи елементів І-НІ четвертої групи з'єднані з відповідними четвертими входами елементів І другої групи, треті входи усіх елементів І-НІ третьої групи і другі входи усіх елементів І-НІ четвертої групи з’єднані з виходом першого прямого затриманого імпульсу генератора імпульсів, перші входи елементів І на входах третього дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера третього регістра стану, другі входи елементів І на входах третього дешифратора з'єднані з відповідним інверсним виходом D-тригера цього розряду, але четвертого регістра стану, виходи елементів І на входах третього дешифратора з'єднано з відповідними входами цього дешифратора, перші входи елементів І на входах четвертого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом D-тригера четвертого регістра стану, другі входи елементів І на входах четвертого дешифратора з'єднані з відповідним інверсним виходом D-тригера цього розряду, але п'ятого регістра стану, виходи елементів І на входах четвертого дешифратора з'єднано з відповідними входами цього дешифратора, інформаційні входи п'ятого дешифратора у формувачі еквівалентів з'єднані з відповідними прямими виходами D-тригера п'ятого регістра стану. 6 UA 119896 U 7 UA 119896 U Комп’ютерна верстка О. Рябко Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 7/00

Мітки: двійковий, коду, перетворювач, двійково-к-значного, код

Код посилання

<a href="https://ua.patents.su/10-119896-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-k-значного коду в двійковий код</a>

Попередній патент: Спосіб оцінки кінцево-діастоличного об’єму лівого шлуночка у пацієнтів після стентування коронарних артерій

Наступний патент: Одночерв’ячний екструдер

Випадковий патент: Надчистий нанокарбоксилат