Перетворювач двійково-к-значного коду в двійковий код

Номер патенту: 102262

Опубліковано: 26.10.2015

Автори: Литвинова Євгенія Іванівна, Макаренко Ганна Миколаївна, Хаханов Володимир Іванович, Вареца Віталій Вікторович, Какурін Микола Яковлевич

Формула / Реферат

Перетворювач двійково-К-значного коду в двійковий код, який містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного старшого розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного старшого розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з (n-1)-го елемента І та групу з (n-1)-го елемента І-НІ, групу з (n-1)-го дешифратора нуля, групу з (n-1)-го дешифратора перевищення, групу з (n-1)-го кодових шифраторів, що на виході формують значення коду зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником, формувач еквівалентів ФЕ, що складається з першого і другого дешифраторів, шифратора, групи елементів І та групи елементів АБО для трансляції молодшого розряду, елемент АБО-НІ та (n-1)-у групу елементів АБО для запису розрядів коду з входів перетворювача у лічильники старших розрядів, причому бітові входи лічильника молодшого розряду є інформаційними входами для запису значення молодшого розряду, перші входи кожної з (n-1)-ї групи елементів АБО є інформаційними входами для запису значень відповідних старших розрядів, а другі входи кожної з (n-1) -ї групи елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному старшому розряді з'єднані з відповідними виходами лічильника цього старшого розряду, а також з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами першої групи тригерів, а виходи дешифраторів перевищення з'єднані з відповідними інформаційними D-входами другої групи тригерів, входи синхронізації тригерів обох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першої групи з'єднані з відповідними першими входами елементів групи І і з відповідними входами першого дешифратора у формувачі еквівалентів, прямі виходи тригерів другої групи з'єднані з входами елемента АБО-НІ, з відповідними першими входами елементів групи І-НІ і з відповідними входами другого дешифратора у формувачі еквівалентів, другі входи елементів групи І з'єднані з виходом елемента АБО-НІ, треті входи елементів групи І і другі входи елементів групи І-НІ з'єднані з першим затриманим виходом генератора імпульсів, інверсні виходи елементів групи І-НІ з'єднані з інверсними входами V у відповідному лічильнику старшого розряду, виходи елементів групи І з'єднані з входом віднімання -1 у відповідному лічильнику старшого розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані з входом +1 лічильника наступного розряду, входи +1 та -1 лічильника молодшого розряду є входами запису числа для перетворення у число-імпульсному коді, бітові виходи лічильника молодшого розряду з'єднані у формувачі еквівалентів з відповідними входами групи елементів І, виходи яких з'єднані з відповідними входами шифратора у формувачі еквівалентів, виходи першого дешифратора у формувачі еквівалентів з'єднані з відповідними входами групи елементів АБО, виходи яких з'єднані з відповідними входами шифратора у формувачі еквівалентів, виходи другого дешифратора у формувачі еквівалентів безпосередньо з'єднані з відповідними входами шифратора, виходи шифратора у формувачі еквівалентів з'єднані з відповідними входами накопичувального суматора, управляючий вхід накопичувального суматора з'єднаний з другим затриманим виходом генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, який відрізняється тим, що в перетворювач коду додатково введено по одному тригеру в першу і другу групи CD-тригерів, один додатковий елемент І в групу елементів І, один додатковий елемент I-НІ в групу елементів I-НІ, по одному додатковому входу в перший і другий дешифратори з інверсними виходами у формувачі еквівалентів, в молодший розряд введено один дешифратор нуля, один дешифратор перевищення, один кодовий шифратор, одна група елементів АБО, перші входи додаткової групи елементів АБО є інформаційними входами для запису в перетворювач коду значення молодшого розряду, другі входи кожного з елементів цієї групи елементів АБО з'єднані з відповідними виходами додаткового кодового шифратора, входи якого в молодшому розряді з'єднані з відповідними виходами лічильника цього розряду і з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, вихід дешифратора нуля молодшого розряду з'єднаний з інформаційним D-входом додаткового тригера в першій групі тригерів, вихід додаткового дешифратора перевищення з'єднаний з інформаційним D-входом додаткового тригера в другій групі тригерів, входи синхронізації додаткових тригерів обох груп з'єднані з прямим виходом генератора імпульсів, виходи додаткового елемента І і додаткового елемента І-НІ з'єднані відповідно з входом -1 та входом V лічильника молодшого розряду, прямі виходи додаткових тригерів стану першої і другої груп з'єднані з молодшими додатковими входами відповідно першого і другого дешифраторів у формувачі еквівалентів, інверсний нульовий вихід другого дешифратора з'єднаний з інверсним входом V першого дешифратора у формувачі еквівалентів, а інверсні виходи першого і другого дешифраторів з'єднані з відповідними входами шифратора у формувачі еквівалентів безпосередньо.

Текст

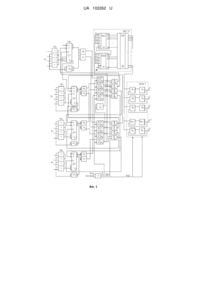

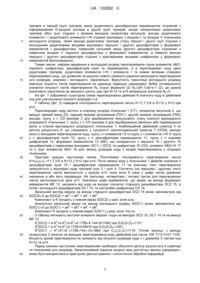

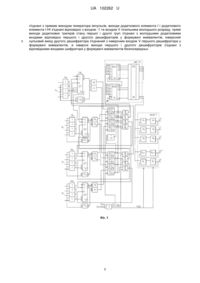

Реферат: Перетворювач двійково-К-значного коду в двійковий код містить (n-1) лічильник старших розрядів, лічильник молодшого розряду, генератор імпульсів, групи CD-тригерів, перший та другий регістр стану, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з (n-1)-го елемента І та групу з (n-1)-го елемента І-НІ, групу з (n-1)-го дешифратора нуля, групу з (n-1)-го дешифратора перевищення, групу з (n-1)-го кодових шифраторів, формувач еквівалентів, групи елементів І та групи елементів АБО для трансляції молодшого розряду, елемент АБО-НІ, лічильник, інформаційні Dвходи першої та другої групи тригерів, генератор імпульсів, накопичувальний суматор, кодовий шифратор, дешифратор нуля, дешифратор перевищення. UA 102262 U (54) ПЕРЕТВОРЮВАЧ ДВІЙКОВО-К-ЗНАЧНОГО КОДУ В ДВІЙКОВИЙ КОД UA 102262 U UA 102262 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до автоматики і обчислювальної техніки і може бути використана при побудові пристроїв обробки і перетворення інформації. Відомий однокроковий перетворювач двійково-К-значного коду у двійковий код з послідовним використанням кроку перетворення, що дорівнює одиниці, (А. с. СССР 1126946, МКИ G06F 5/02 Преобразователь двоично-К-ичного кода в двоичный код /А.И. Слобожанин //Открытия. Изобретения. 1983. № 44. С. 250.), що вміщує групу з n розрядних лічильників СТ для зберігання цифр К-значного коду, генератор імпульсів, що вміщує прямий П, прямі затримані П31 і П32 виходи, групу CD-тригерів для відображення ненульового стану розрядних лічильників, формувач еквівалентів ФЕ, комбінаційний двійковий суматор та регістр результату, що утворюють в сукупності накопичувальний суматор НСМ, групу елементів І та групу дешифраторів нуля. Формувач еквівалентів ФЕ виконують звичайно у вигляді послідовного з'єднання дешифратора DC, групи елементів І, шифратора CD та групи елементів АБО. Функціонування перетворювача коду виконується наступним чином. За допомогою дешифраторів нуля виконується аналіз значень старших розрядів на нуль. Двійкові показники ненульових значень старших розрядів записуються в регістр стану з CD-тригерів і за допомогою ФЕ перетворюються в двійковий код еквівалента, який по задньому фронту прямого затриманого імпульсу ПЗ 2 додається до накопиченої суми еквівалентів у двійковому суматорі НСМ. По задньому фронту прямого затриманого імпульсу ПЗ 1 виконується відрахування одиниць із значень тих старших розрядних лічильників, значення яких не дорівнюють нулю. Після обнуління старших розрядів виконується трансляція (додавання) молодшого розряду до накопиченої суми еквівалентів. Перетворення коду числа виконується за два етапи. На першому етапі перетворення старших розрядів потребує К-1 тактів тому, що найбільш можливе значення старшого розряду дорівнює К-1, на другому етапі трансляція молодшого розряду додає ще один такт. Таким чином, загальна кількість тактів перетворення числа в однокроковому перетворювачі кодів становить К тактів, де К- модуль (основа)системи числення. Більш швидкодіючим є перетворювач двійково-К-значного коду в двійковий код з послідовним використанням двох різних кроків перетворення (на першому етапі кроку перетворення а, на другому - кроку перетворення 1). Найбільш близьким по сукупності ознак до патенту, що заявляється, є перетворювач двійково-К-значного коду в двійковий код з послідовним використанням двох різних кроків перетворення (А. с. СССР № 1647908, МПК Н03М 7/12. Пребразователь двоично-К-ичного кода в двоичный код /Н.Я. Какурин, Ю.К. Кирьяков, Макаренко А.Н. //Открытия. Изобретения. 1991. № 17. С. 262-263.), що містить групу з n розрядних лічильників СТ для зберігання цифр Кзначного коду, генератор імпульсів, що вміщує прямий П, прямі затримані ПЗ1 і ПЗ2 виходи, першу групу CD-тригерів (перший регістр стану) для відображення ненульового стану кожного старшого розрядного лічильника, другу групу CD-тригерів (другий регістр стану) для відображення рівняння або перевищення кроку а станом відповідного старшого розрядного лічильника, комбінаційний двійковий суматор та регістр результат, що утворюють у сукупності накопичувальний суматор НСМ, групу елементів І та групу елементів І-НІ, групу дешифраторів нуля, групу дешифраторів перевищення, групу кодових шифраторів CD, що на виході формують значення коду зменшене на значення другого кроку а (у разі рівняння або перевищення кроку а відповідним лічильником), формувач еквівалентів ФЕ, що складається з двох дешифраторів DC 1 і DC 2, шифратора CD, групи елементів І та групи елементів АБО для трансляції молодшого розряду, елемента АБО-НІ та груп елементів АБО для запису розрядів коду з входів перетворювача у старші розрядні лічильники СТ. Старші розряди двійково-К-значного коду числа для перетворення записуються через перші бітові входи груп елементів АБО старших розрядів у старші лічильники, молодший же розряд коду записується безпосередньо у молодший лічильник. Перетворення числа виконується за три етапи наступним чином. За допомогою дешифраторів нуля виконується аналіз значень старших розрядів на нуль, а за допомогою дешифраторів перевищення виконується аналіз значень старших розрядів на рівняння або перевищення значення кроку а. Двійкові показники ненульових значень старших розрядів записуються в перший регістр стану, а ненульові значення дешифраторів перевищення старших розрядів записуються в другий регістр стану. На першому етапі перетворення числа використовується крок а, використання кроку 1 забороняється нульовим сигналом з виходу елемента АБО-НІ, що подається на всі перші входи групи елементів І. За допомогою ФЕ двійковий код другої групи тригерів перетворюється в двійковий код еквівалента, який по задньому фронту прямого затриманого імпульсу ПЗ 2 додається до накопиченої суми еквівалентів у накопичувальному суматорі НСМ. На першому етапі перетворення потрібно] (К-1)/а [тактів, де дужки] [означають округлення до меншого цілого, на другому етапі - (а -1) такт, та на третьому етапі потрібен ще один такт для трансляції 1 UA 102262 U 5 10 15 20 25 30 35 40 45 50 55 60 молодшого розряду. Таким чином, максимальна кількість кроків для перетворення двійково-Кзначного коду у двійковий код не перевищує значення N2=](К-1)/а[+а (1). При К=12 та а=2 маємо N2=7. В основу корисної моделі поставлена задача підвищення швидкодії двокрокового перетворювача двійково-К-значного коду у двійковий код за рахунок нового схемного рішення. Поставлена задача вирішується наступним чином. В перетворювач двійково-К-значного коду у двійковий код, який містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного старшого розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного старшого розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з (n-1)-го елемента І та групу з (n-1)-го елемента І-НІ, групу з (n-1)-го дешифратора нуля, групу з (n-1)-го дешифратора перевищення, групу з (n-1)-го кодових шифраторів, що на виході формують значення коду зменшене на значення другого кроку а (у разі рівняння або перевищення кроку а відповідним лічильником), формувач еквівалентів ФЕ, що складається з першого і другого дешифраторів, шифратора, групи елементів І та групи елементів АБО для трансляції молодшого розряду, елемент АБО-НІ та (n1)-у групу елементів АБО для запису розрядів коду з входів перетворювача у лічильники старших розрядів, причому бітові входи лічильника молодшого розряду є інформаційними входами для запису значення молодшого розряду, перші входи кожної з (n-1)-ї групи елементів АБО є інформаційними входами для запису значень відповідних старших розрядів, а другі входи кожної з (n-1)-ї групи елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному старшому розряді з'єднані з відповідними виходами лічильника цього старшого розряду, а також з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами першої групи тригерів, а виходи дешифраторів перевищення з'єднані з відповідними інформаційними D-входами другої групи тригерів, входи синхронізації тригерів обох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першої групи з'єднані з відповідними першими входами елементів групи І і з відповідними входами першого дешифратора у формувачі еквівалентів, прямі виходи тригерів другої групи з'єднані з входами елемента АБО-НІ, з відповідними першими входами елементів групи І-НІ і з відповідними входами другого дешифратора у формувачі еквівалентів, другі входи елементів групи І з'єднані з виходом елемента АБО-НІ, треті входи елементів групи І і другі входи елементів групи І-НІ з'єднані з першим затриманим виходом генератора імпульсів, інверсні виходи елементів групи І-НІ з'єднані з інверсними входами V у відповідному лічильнику старшого розряду, виходи елементів групи І з'єднані з входом віднімання -1 у відповідному лічильнику старшого розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані з входом +1 лічильника наступного розряду, входи +1 та -1 лічильника молодшого розряду є входами запису числа для перетворення у число-імпульсному коді, бітові виходи лічильника молодшого розряду з'єднані у формувачі еквівалентів з відповідними входами групи елементів І, виходи яких з'єднані з відповідними входами шифратора у формувачі еквівалентів, виходи першого дешифратора у формувачі еквівалентів з'єднані з відповідними входами групи елементів АБО, виходи яких з'єднані з відповідними входами шифратора у формувачі еквівалентів, виходи другого дешифратора у формувачі еквівалентів безпосередньо з'єднані з відповідними входами шифратора, виходи шифратора у формувачі еквівалентів з'єднані з відповідними входами накопичувального суматора, управляючий вхід накопичувального суматора з'єднаний з другим затриманим виходом генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, згідно з корисною моделлю, в перетворювач коду додатково введені по одному тригеру в першу і другу групи CD-тригерів, один додатковий елемент І в групу елементів І, один додатковий елемент I-III в групу елементів І-НІ, по одному додатковому входу в перший і другий дешифратори з інверсними виходами у формувачі еквівалентів, в молодший розряд введено один дешифратор нуля, один дешифратор перевищення, один кодовий шифратор, одна група елементів АБО, перші входи додаткової групи елементів АБО є інформаційними входами для запису в перетворювач коду значення молодшого розряду, другі входи кожного з елементів цієї групи елементів АБО з'єднані з відповідними виходами додаткового кодового шифратора, входи якого в молодшому розряді з'єднані з відповідними виходами лічильника цього розряду і з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, вихід дешифратора нуля молодшого розряду з'єднаний з інформаційним D-входом додаткового 2 UA 102262 U 5 10 15 20 25 30 35 40 45 50 55 60 тригера в першій групі тригерів, вихід додаткового дешифратора перевищення з'єднаний з інформаційним D-входом тригера в другій групі тригерів, входи синхронізації додаткових тригерів обох груп з'єднані з прямим виходом генератора імпульсів, виходи додаткового елемента І і додаткового елемента І-НІ з'єднані відповідно з входом-1 та входом V лічильника молодшого розряду, прямі виходи додаткових тригерів стану першої і другої груп з'єднані з молодшими додатковими входами відповідно першого і другого дешифраторів у формувачі еквівалентів і дешифратора, інверсний нульовий вихід другого дешифратора з'єднаний з інверсним входом V першого дешифратора у формувачі еквівалентів, а інверсні виходи першого і другого дешифраторів з'єднані з відповідними входами шифратора у формувачі еквівалентів безпосередньо. Таким чином, завдяки введенню в молодший розряд перетворювача групи елементів АБО, кодового шифратора, дешифраторів нуля та перевищення, а в перетворювач коду двох додаткових тригерів, додаткових елементів І-НІ і елемента І та новим зв'язкам створено перетворювач коду, що дозволяє за рахунок нового схемного рішення виконувати перетворення усіх розрядів, зокрема і молодшого, паралельно. Відсутність трансляції молодшого розряду зменшує кількість тактів перетворення на одиницю підвищує швидкодію). Вибір оптимального значення кількості тактів перетворення N2 згідно формули (2) N2=](K-1)/a[+а-1 (2), де дужки] [означають округлення до меншого цілого, дає при К=12 та а=4 мінімальне значення N2=5. На фіг. 1 зображена структурна схема перетворювача двійково-К-значного коду в двійковий код для узагальненої кількості розрядів n=4. У таблиці (фіг. 2) наведена послідовність перетворення числа Х=11,7,3,8 із K=12 у K=2 при а=4. Перетворювач коду містить в кожному розряді лічильник 1 (СТ), генератор імпульсів 2, що вміщує прямий вихід (П), перший прямий затриманий (ПЗ1) і другий прямий затриманий (ПЗ2) виходи, групу з n CD-тригерів 3 для відображення ненульового стану кожного відповідного розрядного лічильника 1, групу з n CD-тригерів 4 для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника 1, комбінаційний двійковий суматор 5 та регістр результату 6, що утворюють у сукупності накопичувальний суматор 7 (НСМ), виходи якого є виходами перетворювача коду, групу з n елементів І 8 та групу з n елементів І-НІ 9, групу з n дешифраторів нуля 10, групу з n дешифраторів перевищення 11, групу з n кодових шифраторів 12, формувач еквівалентів 13 (ФЕ), що складається з першого 14 і другого 15 дешифраторів з інверсними виходами (DC1) і (DC2) та шифратора 16 (CD), елемент АБО-НІ 17 та n груп елементів АБО 18 для запису розрядів коду з входів перетворювача у розрядні лічильники. Пристрій працює наступним чином. Розглянемо послідовність перетворення числа Х=х3x2х1x0 =11,7,3,8 із K=12 у K=2 при а=4. Після запису коду у лічильники 1 двійкові значення з дешифраторів нуля 10 і дешифраторів перевищення 11 на кожному такті перетворення записуються у відповідні коди тригерів груп 3 і груп 4. Спочатку (на першому і другому такті) перетворення числа виконується з кроком а=4, коли хоча б одна з цифр числа дорівнює значенню а або його перевищує. На третьому, четвертому і пятому тактах для перетворення числа застосовується крок а=1. Значення кодів еквівалентів, що видає на виході формувач еквівалентів ФЕ 13, залежить від коду на входах спочатку старшого дешифратора DC2 15, а потім і молодшого дешифратора DC1 14, та настройки шифратора CD 16. Загальний вигляд виразу на виході старшого дешифратора DC2 15 може змінюватися від 3 2 1 0 S(DC2)=0 до S(DC2) = аK + аK + аK + аK . i Компонент а·K входить у повний вираз S(DC2) у разі, коли хi≥а. Аналогічно загальний вираз на виході молодшого кодеру S(DC1) може змінюватися від 3 2 1 0 S(DC1)=0 до S(DC1) = аK + аK + аK + аK . i Компонент K входить у повний вираз S(DC1) у разі, коли 1≤хi

ДивитисяДодаткова інформація

Назва патенту англійськоюBinary-k-digit code converter into a binary code

Автори англійськоюKakurin Mykola Yakovlevych, Khakhanov Volodymyr Ivanovych, Lytvynenko Evheniia Ivanivna, Varetsa Vitalii Viktorovych, Makarenko Hanna Mykolaivna

Назва патенту російськоюПреобразователь двоично-к-значного кода в двоичный код

Автори російськоюКакурин Николай Яковлевич, Хаханов Владимир Иванович, Литвинова Евгения Ивановна, Вареца Виталий Викторович, Макаренко Анна Николаевна

МПК / Мітки

МПК: H03M 7/00

Мітки: коду, двійковий, перетворювач, код, двійково-к-значного

Код посилання

<a href="https://ua.patents.su/8-102262-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-v-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду в двійковий код</a>

Попередній патент: Спосіб безконтактного вимірювання температури заряду артилерійських боєприпасів

Наступний патент: Спосіб корекції гематологічних показників свиней за умов лікування респіраторних захворювань запального характеру

Випадковий патент: Спосіб спеціалізованого пошуку інформації в масиві текстів