Пристрій для цифрової передачі та прийому неперервного сигналу

Формула / Реферат

Устройство для цифровой передачи и приема непрерывного сигнала, содержащее на передающей стороне первый источник опорного напряжения, выход которого подключен к первому информационному входу первого компаратора, второй информационный вход которого объединен с информационным входом аналого-цифрового преобразователя и является входом устройства, генератор импульсов, выход которого подключен к тактовому входу первого компаратора и аналого-цифрового преобразователя, выход первого компаратора подключен к первому управляющему входу смесителя импульсов, информационный вход которого подключен к выходу аналого-цифрового преобразователя, выход смесителя импульсов подключен к каналу связи, на приемной стороне - селектор импульсов, вход которого подключен к каналу связи, первый и второй выходы селектора импульсов подключены к одноименным информационным входам реверсивного счетчика, выходы которого являются информационными выходами устройства, отличающееся тем, что, с целью повышения достоверности передаваемой информации путем уменьшения динамической погрешности, в устройство на передающей стороне введены n-1 компараторов и источников опорного напряжения n буферных регистров, блок элементов ИЛИ, элемент ИЛИ, выходы n-1 источников опорного напряжения подключены к первым информационным входам одноименных компараторов, вторые информационные входы которых объединены с информационным входом аналого-цифрового преобразователя, тактовые входы n-1 компараторов объединены с тактовым входом аналого-цифрового преобразователя, выход первого компаратора подключен к первому управляющему входу блока элементов ИЛИ и к первому входу элемента ИЛИ, выход которого подключен к управляющему входу аналого-цифрового преобразователя, выходы n-1 компараторов подключены к одноименным управляющим входам смесителя импульсов и блока элементов ИЛИ и к одноименным входам элемента ИЛИ, выходы n буферных регистров подключены к одноименным информационным входам блока элементов ИЛИ, выходы которого подключены к информационным входам группы аналого-цифрового преобразователя, на приемной стороне введены элемент ИЛИ, блок элементов ИЛИ и n буферных регистров, n управляющих выходов селектора импульсов подключены к одноименным управляющим входам блока элементов ИЛИ и через элемент ИЛИ - к управляющему входу реверсивного счетчика, выходы n буферных регистров подключены к одноименным информационным входам блока элементов ИЛИ, выходы которого подключены к информационным входам группы реверсивного счетчика.

Текст

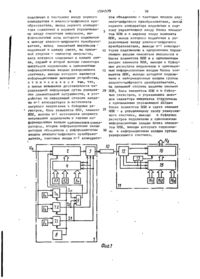

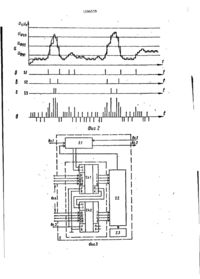

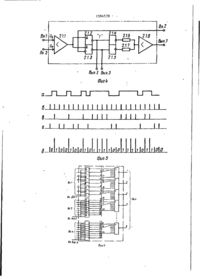

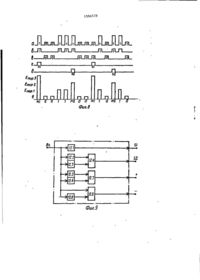

Изобретение относится к телеиз-* мерению и может быть использовано при цифровой передаче, регистрации обработке и восстановлении непрерывных сигналов. Цель изобретения - повышение достоверности передаваемой информации путем уменьшения динамической погрешности. Устройство содержит на передающей стороне 1 анало Я*. го-цифровой преобразователь 2 следящего уравновешивания, смеситель 3 импульсных последовательностей, блок элементов ИЛИ 4 с клапанами на входе, буферные регистры 5.1,,..,5.п, источники опорного напряжения 6.1,,.,,6.п. компараторы 7.1,...,7tn, генератор тактовых импульсов 8, элемент ИЛИ 9, канал связи 10, на приемной стороне 11 селектор 12 импульсных последовательностей, элемент ИЛИ 13, буферные регистры 14,1,...,14.п, блок элементов ИЛИ J5 с клапанами яа входе, реверсивный счетчик 16. Устройство позволяет за счет введения нескольких фиксированных порогов опорного напряжения уменьшить динамическую погрешность как от перегрузки по крутизне входного сигнала» как и от накоплений ошибок в канале связи. 10 ил. аг "о" С СП СО чин^- 5.6 ЗМ СО 3.5 3.6 sr Фиг.7 ^ • i ... MS I J——^ 1594579 Изобретение относится к телеизмерению и может быть использовано при цифровой передаче"( регистрации, обработке И восстановлении непрерывных сигналов. Цель изобретения - повышение дос-' товарности передаваемой информации путем уменьшения динамической ПОГреШНОСТИ. На фиг.I приведена функциональная схема устройства; на фиг о 2 ~ временные диаграммы, поясняющие работу устройства; на фиг.З - схема аналогоцифрового преобразователя следящего-~ уравновешивания; на фиг.4 - схема компаратора; на фиг,5 - временные диаграммы, поясняющие работу компаратора; на фиг,6 - схема блоков элементов ИЛИ с клапанами на входе; на фиг.7 - схема смесителя импульсных последовательностей; на фиг.8 временные диаграммы, поясняющие р а боту смесителя импульсных последовательностей; на фиг„9 - схема селектора импульсов; на фиг.10 - временные диаграммы, поясняющие работу селектора импульсов. J0 J5 20 25 Устройство содержит на передаю30 щей стороне 1 аналого-цифровой п р е образователь 2 следящего уравновешивания, смеситель 3 импульсных п о с л е довательностей, блок элементов ИЛИ 4 с клапанами на входе, буферные р е гистры 5.1 - 5 , п , источники 6 . 1 - б . п 35 опорного напряжения, коішараторьі 7 . 1 7.п, генератор 8 импульсов, элемент ИЛИ 9, канал 10 с в я з и , на приемной стороне И - селектор 12 импульсных последовательностей, элемент ИЛИ 13, 40 буферные регистры 14.1—34,п, блок элементов ИЛИ 15 с клапанами на входе и реверсивный счетчик 16. Аналого-цифровой преобразователь 2 следящего уравновешивания (фиг,. 3) "состоит из компаратора 2,1,цифроанаї лотового преобразователя 2 . 2 , источи ника 2 С 3 эталонного напряжения, р е версивного счетчика 2.4 состоящего из двух реверсивных счетчиков 2 , 4 . 1 и 2.4.2. Компаратор 2,1 (фиг.4) состоит из операционного усилителя 2 , 1 . 1 , двух клапанов 2.1,2 и 2 . 1 , 3 , двух инверторов 2 , 1 , 4 и 2 . 1 . 5 , двух р е зисторов 2 . 1 . 6 и 2 . 1 . 7 с весами 1:3 соответственно,и усилителя 2 . 1 , 8 . 45 50 55 Сигнал (фиг.5а) с выхода операционного усилителя 2.1.1 формируется при сравнении входного измерительного сигнала U^, поступающего по шине Вх,1, с компенсирующим напряжением U , формируемым с выхода цифроаналогового преобразователя по шине Вх.З. Тактовые импульсы (фиг.5б) поступают по шине Бх.2. Последовательности импульсов (фиг.5в,г) соответствуют приращениям " і " и " 0 " . Выходной сигнал (фиг.5д) соответствует суммарному потоку двоичных символов инкрементного кода или последовательного кода приращений и поступает на выходную шину Вых.Ї. Смеситель 3 (фиг.7) состоит из амплитудного селектора 3.1 (iJftv,>E_ *) It VI ^* WA III) у элемента Запрет 3.2 с одним запрещающим входом, 3.3 и 3.4 - элементов "Запрет" 3.3 и 3.4 с двумя запрещающими входами повторителей 3.5 и 3,6, резисторов 3.7-3.10 с соответствующими весами и усилителя 3.11. ^ _ Смеситель 3 импульсных последовательностей функционирует следующим образом. На вход поступает последовательность двоичных символов (приращений), причем нуль представлен как импульс положительной полярноети с амплитудой сигнала, равной U, а единица - с амплитудой 3U, Импульсы с амплитудой 3U поступают на вход амплитудного селектора 3.1, с выхода которого формируется сигнал логической "і" (фиг.86), и этот сигнал поступает на запрещающий вход элемента "Запрет" 3,2, с выхода которого сигнал в этот момент времени не выдается. Таким образом, импуль•сы логического " 0 " (фиг.8в) поступают на вход элемента "Запрет" 3.3, а импульсы логической " 1 " (Лиг.8б) поступают на вход элемента "Запрет" 3 С 4. При поступлении управляющих сигналов S1 (сигнал первого фиксированного уровня) и S2 (сигнал второго фиксированного на соответствующие входы элементов 3.3, 3.4, фиг о 8г,д) выдача информации с соот-, ветствуюших выходов этих элементов осуществляется только в моменты отсутствия запрещающих сигналов S1 и S2« Таким образом, при поступлении сигнала S1 на управляющие входы элементов "Запрет" 3,3 и 3.4 происходит запрет выдачи информации через эти 1594579 сов осуществляет тактирование аналоэлементы, а сигнал SI проходит через го-цифрового преобразователя 2 еле- повторитель 3,6 и поступает на редящего уравновешивания и коммутатозистор 3.J0, вес которого меньше веров 7.1-7.п. Измеряемое напряжение са резисторов 3.7-3,9 как 1:7:5:3. U поступает на вторые входы компаПри поступлении сигнала S2 на управраторов 7.1-7.П и на информационный ляющие входы элементов "Запрет" 3.3 вход аналого-цифрового преобразоваи 3,4 происходит запрет выдачи интеля 2, с выхода которого формируетформации через эти элементы, а сиг*Q ся последовательный код приращений, нал S2 проходит через повторитель который поступает на информационный 3.5 и поступает на резистор 3.9, вход смесителя 3. Первый вход каждовес которого меньше веса резисторов к а к го из компараторов 7.1-7.П соответст3.8 и 3.7'» 3:5:7. Таким образом, венно соединен с источниками 6.1-б.п в точке соединения резисторов форми15 опорных напряжений, настроенных на руется смешанная кодовая последовасоответствующие уровни фиксированнотельность двоичных символов (приращего напряжения U^y , . . о ,U ф,уп. ний) и маркерных сигналов, которая проходит через усилитель и поступаПри пересечении входным измериет на выходную шину смесителя 3 имтельным сигналом и„ фиксированного пульсных последовательностей (фиг.8(0 20 уровня U ^ t в момент тактового импульПри этом логический "О" выдается имса срабатывает первый компаратор 7.1, пульсом с амплитудой U, логическая с выхода которого формируется сигнал " 1 " - 3U, маркерный сигнал М2 - 5U, S1 (фиг.1,2а,б). Этот сигнал постумаркерный сигнал Ml - 7U. пает на первый управляющий вход сме25 сителя 3, запрещая в этот момент вреСелектор 12 импульсных последовамени выдачу очередного приращения и тельностей (фиг.9) состоит из ампразрешая выдачу маркерного сигнала литудного селектора 12.1 ( И х ~* ^щ^>) "б Ml с селектирующим признаком, отличамплитудного селектора 1/.5 ным от того, который принят для пе( и б х > Е п о р 2 ) , амплитудного селектора ЗО редачи приращений других маркерных 12.3 ( U b x ? Е п о р 3), элемента "Запрет" сигналов. В этот же момент времени 12.4, амплитудного селектора 12.5 сигнал SJ поступает на первый управ(UfrJ(. >Е ПОр 1 ) , амплитудного селектоляющий вход блока элементов ИЛИ 4, ра 12.6 (Uй х 7 Е П 6 р 2 ) , элемента "Запразрешая выдачу с выхода блока 4 парет" I2.7|- амплитудного селектора раллельного кода, соответствующего бу35 12.8 (U 6 х >Е п 6 р 1 ) , элемента "Запрет" ферному регистру 5.1. В этот же мо12.9 и элемента ИЛИ 12.10. мент времени сигнал S1 поступает чеСелектор 12 импульсных^последоварез элемент ИЛИ 9 на управляющий тельностей осуществляет процедуру, вход аналого-цифрового преобразовапротивоположную смесителю 3 импульс40 теля 2, разрешая занесение в его ных последовательностей, и используреверсивный счетчик параллельный ет аналогичный принцип амплитудной код с выхода блока элементов ИЛИ 4, селекции. На вход селектора 12 имкоторый соответствует значению копульсных последовательностей поступада в буферном регистре 5„1, При пеет смешанная последовательность дво45 ресечении входным сигналом Uх напряичных символов приращений и маркержения Фиксированного уровня U J , ^ ных сигналов Ml и М2 (фиг.10а), а с в момент тактового импульса формируего выходов формируется сигнал S1 ется с выхода второго компаратора (фиг.Юб), соответствующий моменту 7,2 сигнал S2, который (по аналогии времени П О Я Р Л Є Н И Я маркерного сигна50 с сигналом S1 ) поступает на второй уп~ : ла Ml (фиг. 10а), сигнал С2 (фиг. Ю в ) , равляющий вход смесителя 3, запрещая высоответствующий моменту времени появдачу очередного кода приращения и разления маркерного сигнала М2 (фиг. Ю а ) . решая выдачу маркерного сигнала М2 с сигнал логической " 1 " (фиг. Ю г ) , сигселектирующим признаком, отличным нал логического " 0 " (фиг.IОд) 55 от того, который принят для передаУстройство работает следующим чи приращений и других маркерных образом. сигналов. Этот же сигнал S2 поступаВ исходном состоянии, после вклюет на блок элементов ИЛИ 4, разрешая чения, генератор 8 тактовых импульвыдачу параллельного кода, соответ 1594579 ствугощего буферному регистру 5 , 2 , код которого соответствует второму уровню фиксированного напряжения В этот же момент времени сигнал S2 поступает через элемент ИЛИ 9 на управляющий вход .аналого-цифрового преобразователя 2 следящего уравновешивания, разрешая занесение параллельного кода в реверсивный счетчик преобразователя 2 с выхода блока элементов ИЛИ 4, причем этот код равен с о держимому буферного регистра 5,2 И соответствует второму уровню фиксированного напряжения U ,Аналогичным образом происходит функционирование передающей стороны устройства и при пересечении входным сигналом U других уровней фиксирован20 ного напряжения. На фиг.2а,.6 показаны эпюры формирования сигнала SI при пересечении входным сигналом напряжения фиксированного уровня' ^fy,- На ф и г . 2 а , в показаны эпюры формирования сигнала 25 S2 при пересении входным сигналом н а п * ряжения фиксированного уровня U ^ ^ , На ф и г . 2 а , г показаны эпюры формирования сигнала S3 гри пересечении входным сигналом напряжения фиксиро- 30 ванного уровня Uf-уз. На ф и г . 2 а , д п о — казаны эпюры, поясняющие процесс формирования смешанной кодовой последовательности приращений и маркерных •г э сигналов. Таким образом, на выходе смесителя 3 формируется смешанная последовательность символов приращений (0 и 1) и маркерных сигналов (например, Ml, M2, МЗ). Описанная ко40 довая последовательность информационных символов ( 0 , 1 , Ml, М2, МЗ) поступает в канал 10 связи (фнг.1 и 2д) 7 из которого поступает па селектор 1 12, где осуществляется выделение 45 и формирование маркерных сигналов M l , . . . , M n и сигналов S I , S 2 , . . . , S n , а также выделение импульсов сложения и вычитания, соответствующим импульсам кода приращений (1 или 0) и поступающим из к а н а л а " с в я з и . Б ис- 50 ходном состоянии, при включении, на реверсивном счетчике 16 происходит преобразование последовательного инкрементного кода в параллель55 ный код, соответствующий значению полномерной выборки. С приемом и .селекцией первого маркерного сигнала МІ (фиг,2д) и с формированием с и г нала S1 происходит разрешение выда 8 чи с выхода блока элементов ИЛИ 15 информации, соответствующей первому буферному регистру 1 4 , 1 , значение кода в котором соответствует первому уровню фиксированного напряжения U^ В этот же момент времени сигнал S1 поступает на вход элемента ИЛИ 13 ; с выхода которого формируется с и г нал разрешения занесения параллельного кода в реверсивный счетчик 16 с параллельного выхода блока элементов ИЛИ 15. Аналогичным образом происходит функционирование приемной стороны устройства при приеме и селек~ ции других маркерных сигналов (М2, М З , . , . , М п ) . При этом в реверсивный счетчик 16 заносится параллельный код соответствующий выбранным фиксированным уровням напряжения е Значению к фиксированного уровня U^ соответствуют маркерный сигнал Ml, сигнал S1 и код буферного регистра 1 4 . 1 . Значению фиксированного уровня U ф у ^ с о о т в е т с т вуют маркерный сигнал М2, сигнал S2 и код буферного регистра 1 4 . 2 . Аналогичное соответствие имеет место и для других значений напряжений фиксированного уровня U$.y,- , маркерных сигналов К , , сигналов S и кода буферного регистра 1 4 . І , Таким образом ( на приемной стороне происходит формирование отсчетов на реверсивном счетчике 16, При этом отсчет на р е версивном счетчике формируется с приемом каждого двоичного символа приращений, а также с приемом каждого маркерного сигнала, причем каждому типу маркерного сигнала соответствует свой уровень фиксированного напряжения и кода в буферном р е г и с т р е . Таким образом, предлагаемое у с т ройство позволяет уменьшить динамическую погрешность как от перегрузки по крутизне входного сигнала, так и от накоплений ошибок в канале с в я з и . Ф о р м у л а и з о б р е т е н и я Устройство для цифровой передачи и приема непрерывного сигнала, содержащее на передающей стороне п е р вый источник опорного напряжения, выход которого подключен к первому ' информационному входу первого компаратора, второй информационный вход которого объединен с информационным входом аналого-цифрового преобразователя и является входом устройства, генератор импульсов, выход которого 1594579 подключен к тактовому входу первого компаратора и аналоїо-цифрового преобразователя, выход первого компаратора подключен к первому управляющему входу смесителя импульсов, информационный вход которого подключен к выходу аналого-цифрового преобразователя, выход смесителя импульсов * подключен к каналу связи, на прием10 ной стороне - селектор импульсов, вход которого подключен к каналу связи, первый и второй выходы селектора импульсов подключены к одноименным информационным входам реверсивного 15 счетчика, выходы которого являются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности передаваемой информации путем уменьше- 20 ния динамической погрешности, в устройство на передающей стороне введены п-1 компараторов и источников опорного напряя ения п буферных регистров, блок элементов ИЛИ, элемент 25 ИЛИ, выходы п-1 источников опорного напряжения подключены к первым информационным входам одноименных компараторов, вторые информационные входы которых объединены с информационным 30 входом аналого-цифрового преобразователя, тактовые входы п-1 комларато 10 ров объединены с тактовым входом аналого-цифрового преобразователя, выход первого компаратора подключен к первому управляющему входу блока элементов ИЛИ и к первому входу элемента ИЛИ, выход которого подключен к управляющему входу аналого-цифрового преобразователя, выхор}>1 п-1 компараторов подключены к одноименным управляющим входам смесителя импульсов и блока элементов ИЛИ и к одноименным входам элемента ИЛИ, выходы п буферных регистров подключены к одноименным" информационным входам блока элементов ИЛИ, выходы которого подключены к информационным входам группы аналого-цифрового преобразователя, на приемной стороне введены элемент ИЛИ, блок элементов ИЛИ и п буферных регистров, п управляющих выходов селектора импульсов подключены к одноименным управляющим входам блока элементов ИЛИ и через элемент ИЛИ - к управляющему входу реверсивного счетчика, выходы п буферных регистров подключены к одноименным информационным входам блока элементов ИЛИ, выходы которого подключены к информационным входам группы реверсивного счетчика. 11 " • • • 13 *~ • 11 ФигЛ " І 1 • " W > Ф •* «» 15 1594579 • м.ЛТі І|І п И Г • * - * • ' ' j I fc • " Д . .ч ЦІ • і і . ь - ll'ij И Д І І Т ї ї Д і і Д її IT їїII I тгт Ш U і 1 ІЛ U Фиг. 2 г Лг-J П і! гмі •І* І І J Ч U -і 2Л2 я? Б r. З 2.3 L Фиг.3 1594579 Вых. 7 8хд о о Выхг Вых.З Фиг ^ л 6-і І и 11 і і і и і 11 і і і і 11 I I 1111 1111 11 II II ікк 11 іМа. Фиг 5 Bxl < Bx ynp } Фиг 6 І И і\о\о І ік Ma. 159*579 J i LfoUoui U і LJi LOUOUOLJI LraJi Lh Lm_ iff о о і мг о о мі і Q M Z J Фиг в Вк SI 121 122 12.6 12В 12M 12.7 12.9 Фиг.9 SZ 594579 Фиг, Ю Редактор 0. Головач Составитель В. Струков Техред Л.Олийнык Корректор т. Палий Заказ 2832 — Т и р а ж 44Ї . Подписное ВНИИПИ Государствешшго комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital-data transmitter and device to receive continuous signal

Автори англійськоюSevastianov Anatolii Kostiantynovych

Назва патенту російськоюУстройство для цифровой предачи и приема непрерывного сигнала

Автори російськоюСевастьянов Анатолий Константинович

МПК / Мітки

МПК: G08C 19/28

Мітки: сигналу, передачі, прийому, пристрій, неперервного, цифрової

Код посилання

<a href="https://ua.patents.su/10-14070-pristrijj-dlya-cifrovo-peredachi-ta-prijjomu-neperervnogo-signalu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для цифрової передачі та прийому неперервного сигналу</a>

Попередній патент: Речовина для кріоконсервування тканинних лімфоцитів

Наступний патент: Спосіб визначення проникності еритроцитів для осмотично активних органічних речовин

Випадковий патент: Спосіб виготовлення гнучкого електролюмінесцентного індикатора