Локальний комутатор

Номер патенту: 54292

Опубліковано: 10.11.2010

Автори: Горбулін Володимир Павлович, Колесник Костянтин Іванович, Яковлев Віталій Васильович, Свириденко Анатолій Олексійович, Немчин Олександр Федорович, Конюхов Станіслав Миколайович, Курячий Євген Віталійович

Формула / Реферат

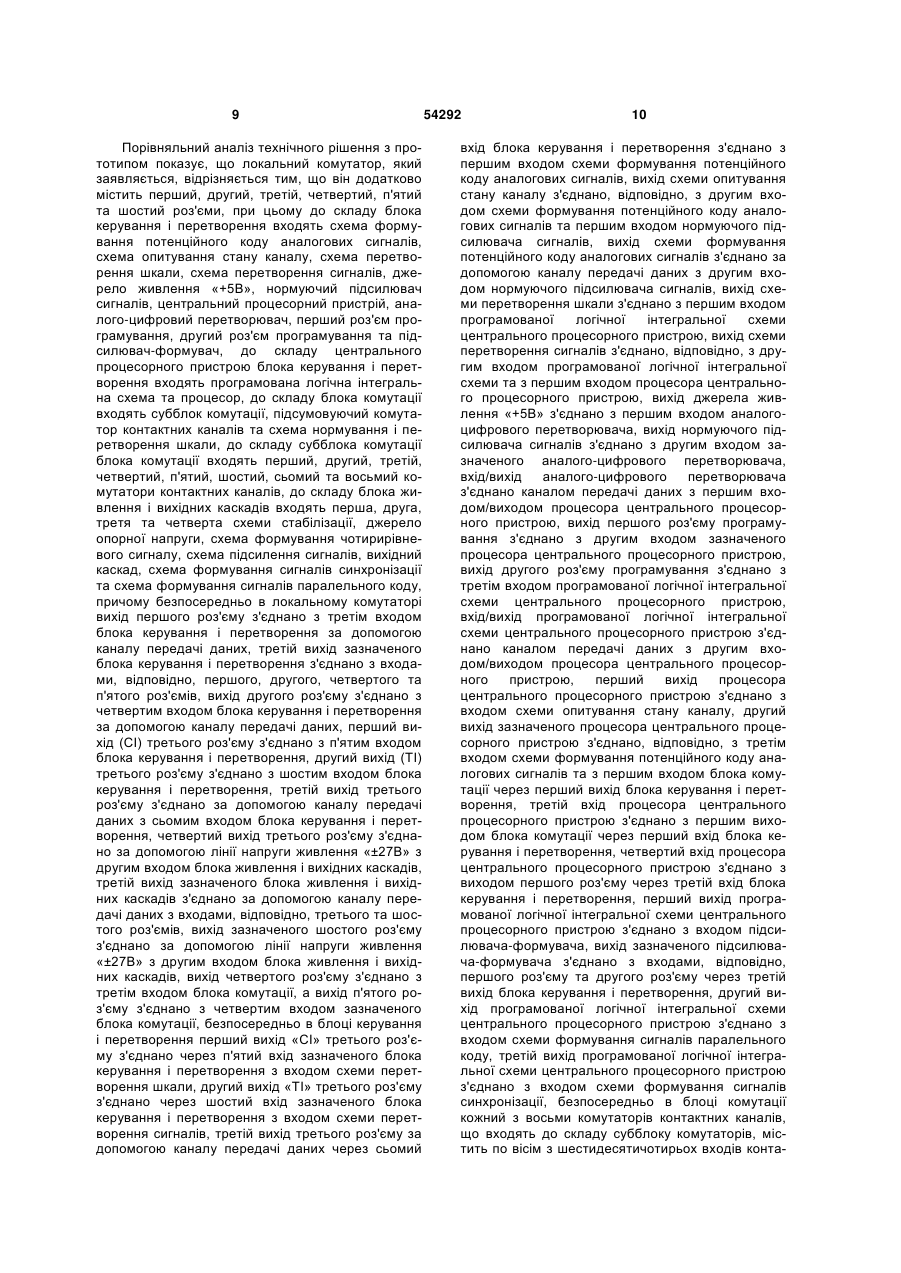

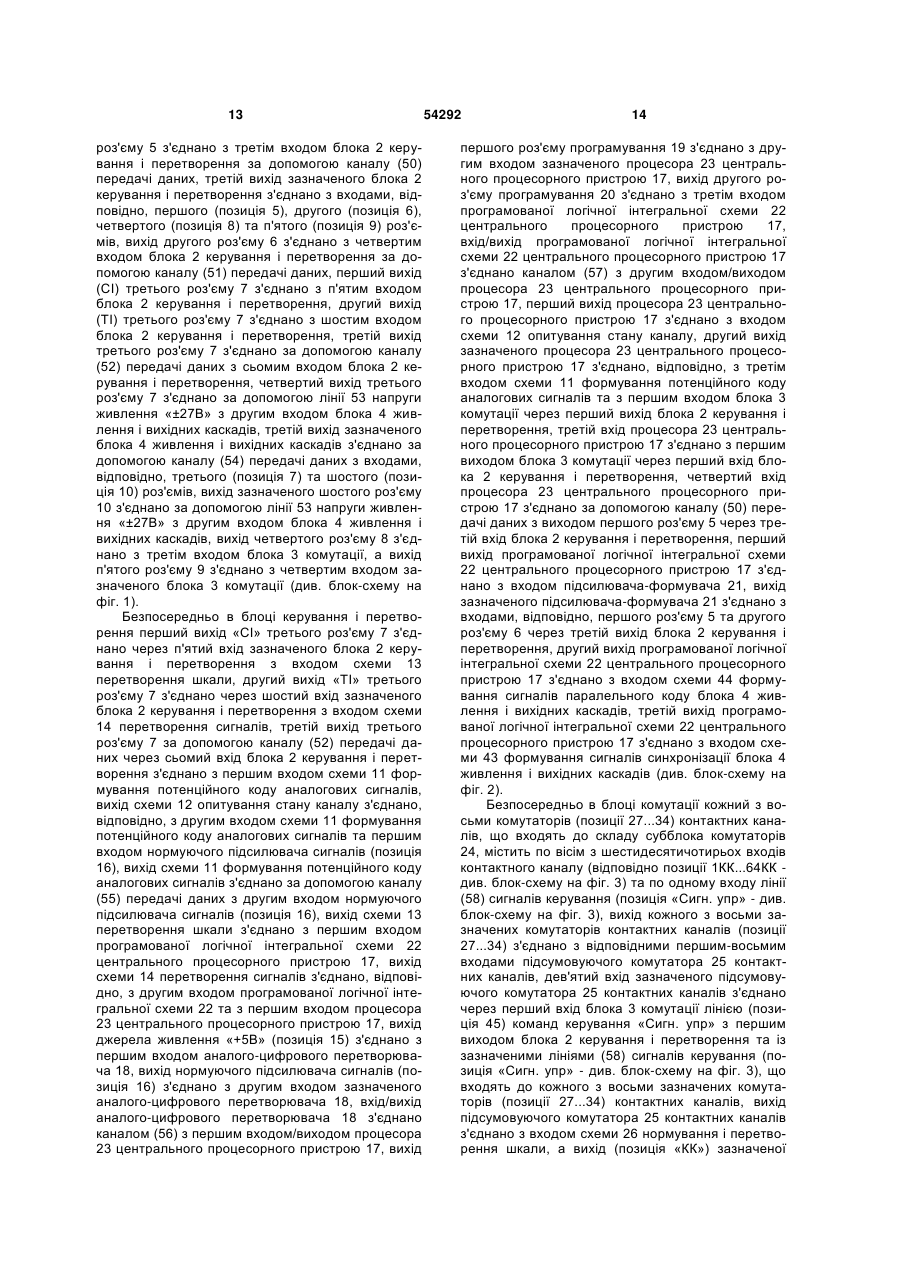

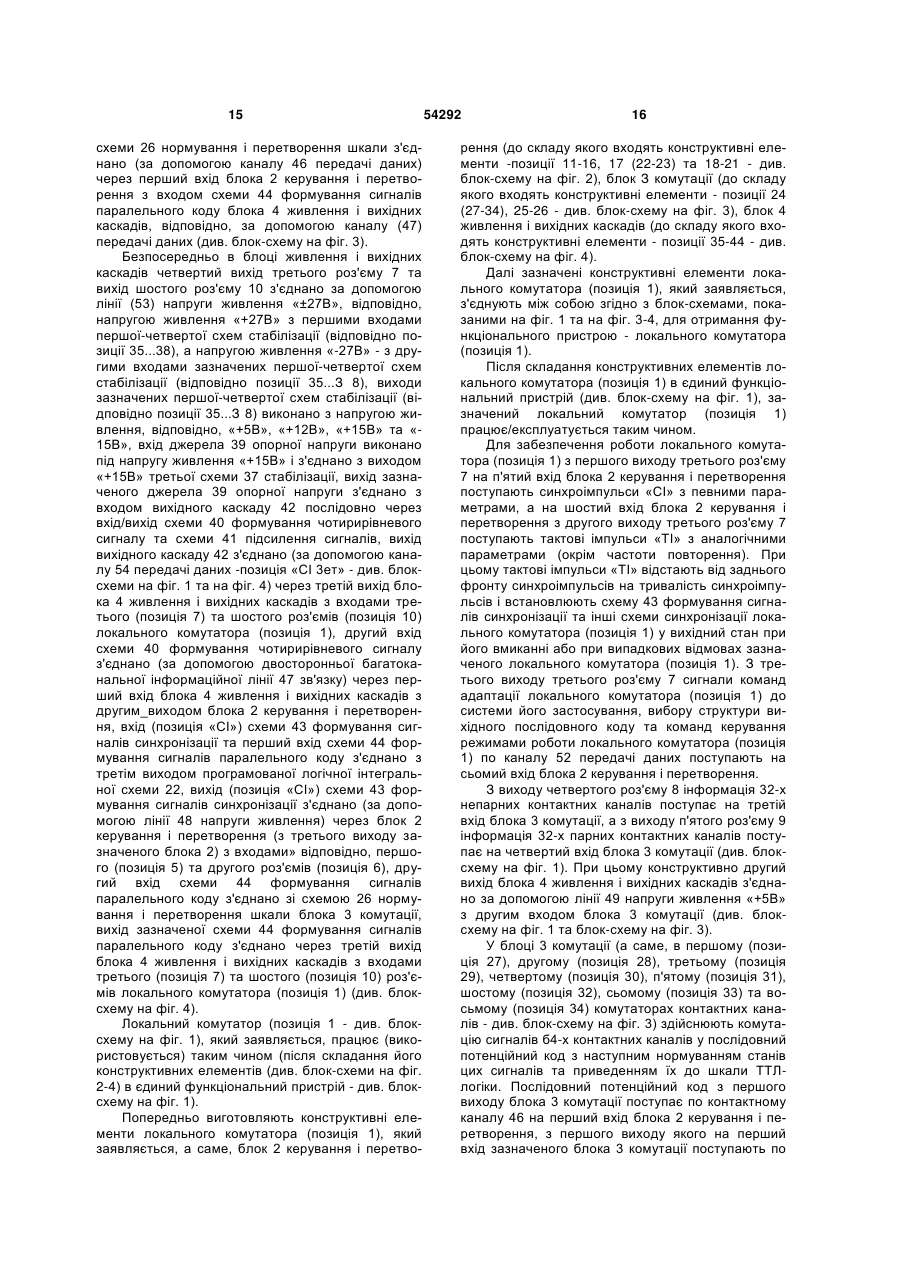

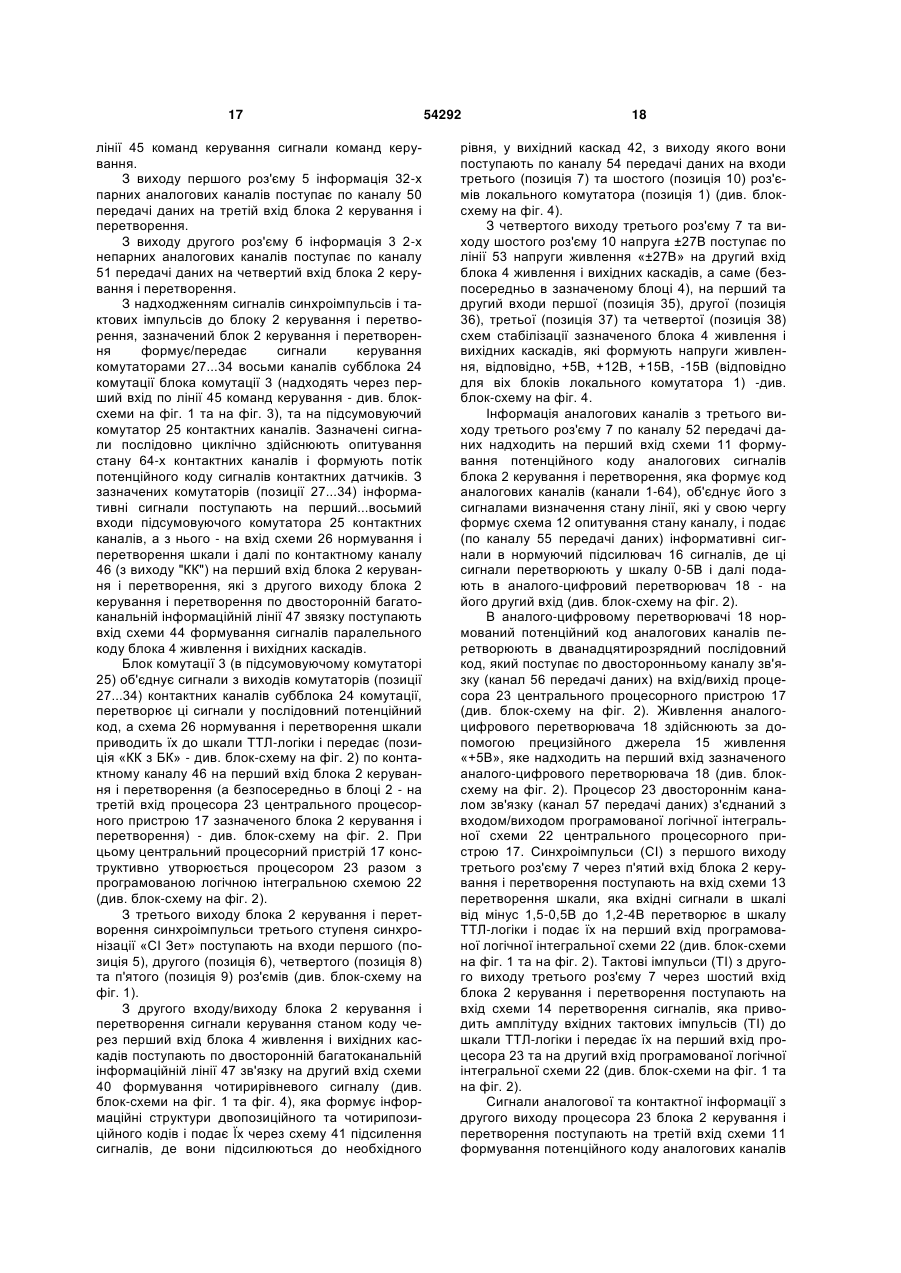

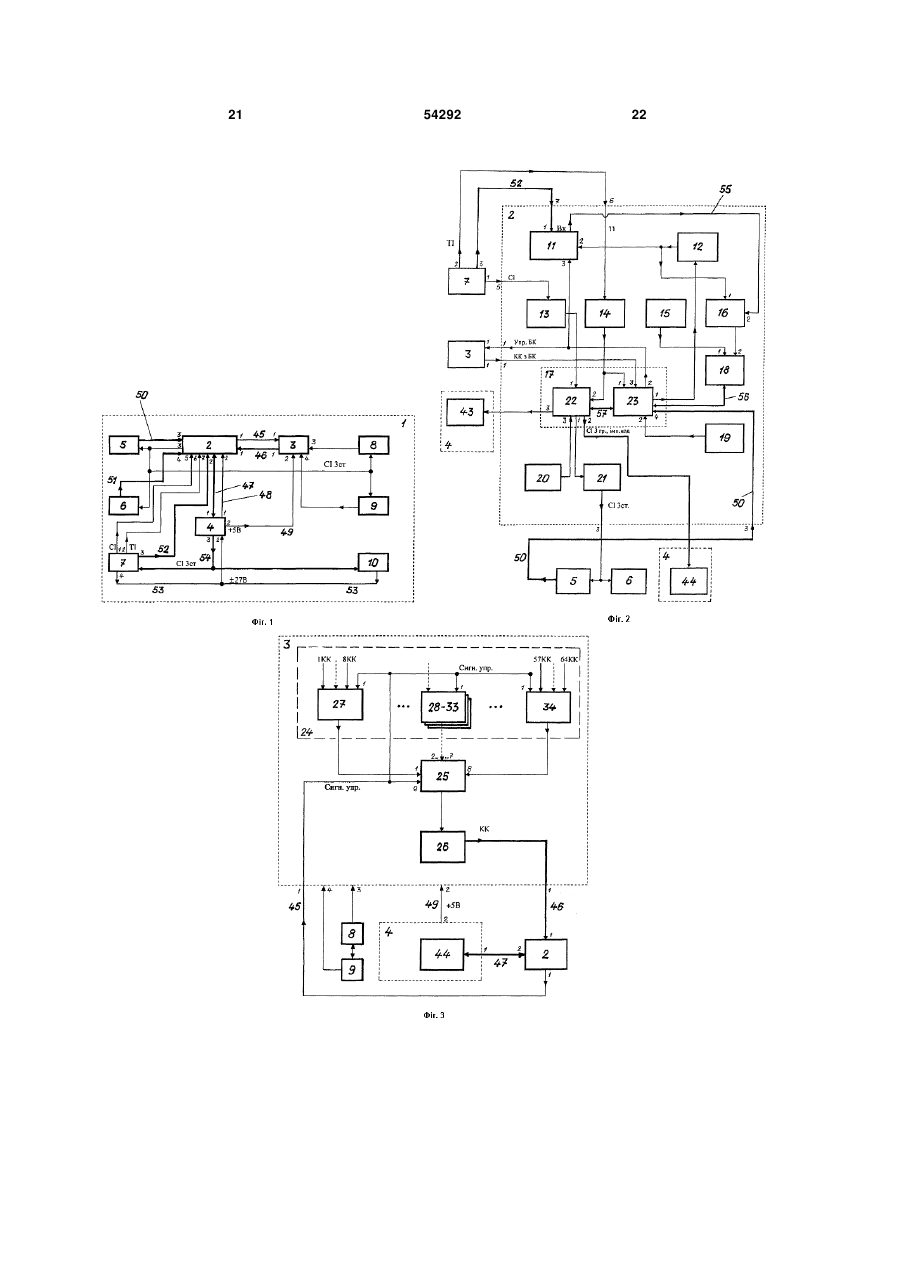

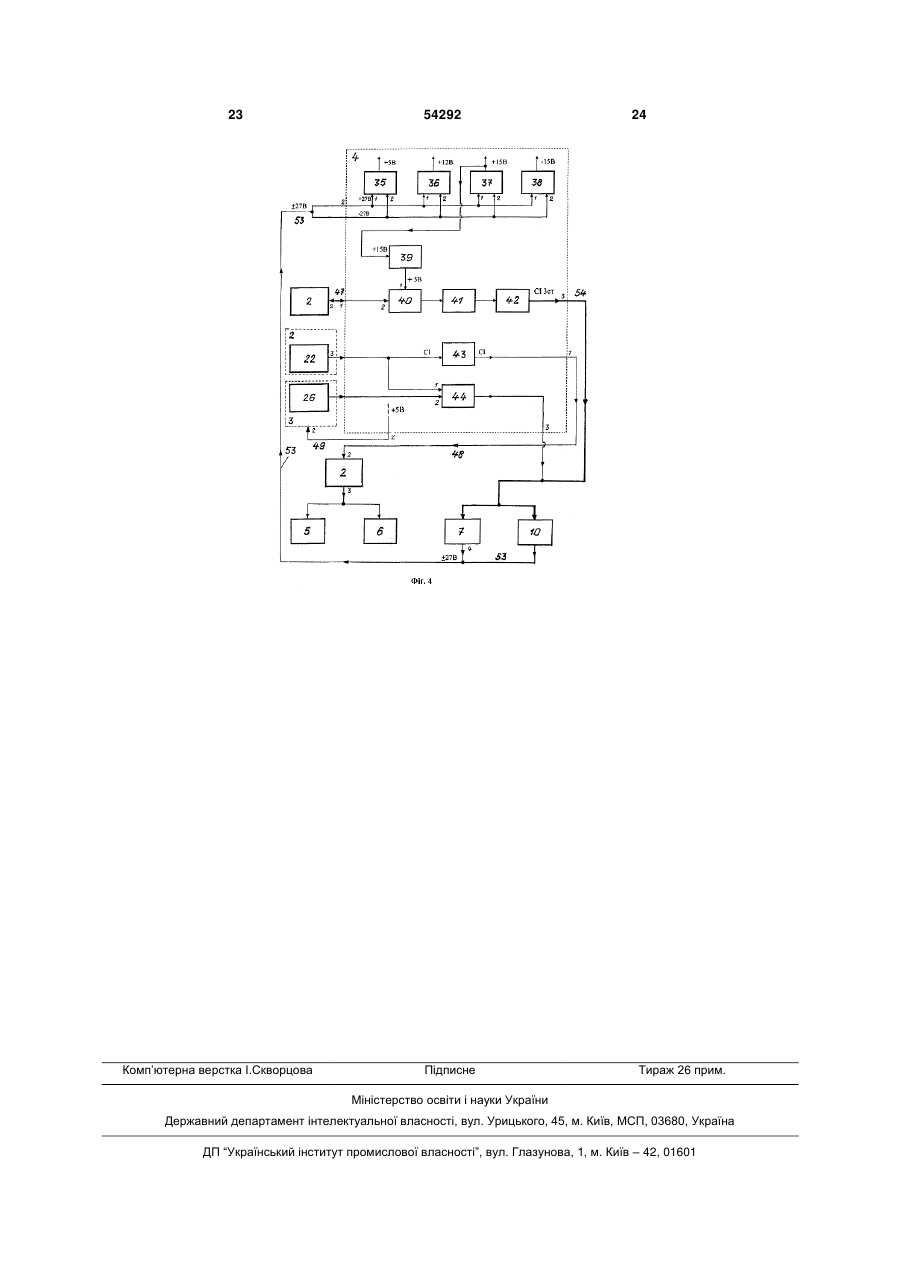

Локальний комутатор, що містить блок керування і перетворення, блок комутації та блок живлення і вихідних каскадів, при цьому перший вихід блока керування і перетворення з'єднаний за допомогою лінії команд керування з першим входом блока комутації, перший вихід зазначеного блока комутації з'єднаний за допомогою контактного каналу з першим входом блока керування і перетворення, другий вхід/вихід блока керування і перетворення з'єднаний за допомогою двосторонньої багатоканальної інформаційної лінії зв'язку з першим входом блока живлення І вихідних каскадів, перший вихід зазначеного блока живлення і вихідних каскадів з'єднаний за допомогою лінії напруги живлення з другим входом блока керування і перетворення, другий вихід блока живлення і вихідних каскадів з'єднаний за допомогою лінії напруги живлення "+5В" з другим входом блока комутації, який відрізняється тим, що він додатково містить перше, друге, третє, четверте, п'яте та шосте рознімання, при цьому до складу блока керування і перетворення входять схема формування потенційного коду аналогових сигналів, схема опитування стану каналу, схема перетворення шкали, схема перетворення сигналів, джерело живлення "+5В", нормуючий підсилювач сигналів, центральний процесорний пристрій, аналого-цифровий перетворювач, перше рознімання програмування, друге рознімання програмування та підсилювач-формувач, до складу центрального процесорного пристрою блока керування і перетворення входять програмована логічна інтегральна схема та процесор, до складу блока комутації входять субблок комутації, підсумовуючий комутатор контактних каналів та схема нормування і перетворення шкали, до складу субблока комутації блока комутації входять перший, другий, третій, четвертий, п'ятий, шостий, сьомий та восьмий комутатори контактних каналів, до складу блока живлення і вихідних каскадів входять перша, друга, третя та четверта схеми стабілізації, джерело опорної напруги, схема формування чотирирівневого сигналу, схема підсилення сигналів, вихідний каскад, схема формування сигналів синхронізації та схема формування сигналів паралельного коду, причому безпосередньо в локальному комутаторі вихід першого рознімання з'єднаний з третім входом блока керування і перетворення за допомогою каналу передачі даних, третій вихід зазначеного блока керування і перетворення з'єднаний з входами відповідно першого, другого, четвертого та п'ятого рознімань, вихід другого рознімання з'єднаний з четвертим входом блока і перетворення за допомогою каналу передачі даних, перший вихід (СІ) третього рознімання з'єднаний з п'ятим входом блока керування і перетворення, другий вихід (ТІ) третього рознімання з'єднаний з шостим входом блока керування і перетворення, третій вихід третього рознімання з'єднаний за допомогою каналу передачі даних з сьомим входом блока керування і перетворення, четвертий вихід третього рознімання з'єднаний за допомогою лінії напруги живлення "±27В" з другим входом блока живлення і вихідних каскадів, третій вихід зазначеного блока живлення і вихідних каскадів з'єднаний за допомогою каналу передачі даних з входами відповідно третього та шостого рознімань, вихід зазначеного шостого рознімання з'днаний за допомогою лінії напруги живлення "±27В"з другим входом блока живлення і вихідних каскадів, вихід четвертого рознімання з'єднаний з третім входом блока комутації, а вихід п'ятого рознімання з'єднаний з четвертим входом зазначеного блока комутації, при цьому безпосередньо в блоці керування і перетворення перший вихід "СІ" третього рознімання з'єднаний через п'ятий вхід зазначеного блока керування і перетворення з входом схеми перетворення шкали, другий вихід «ТІ» третього рознімання з'єднаний через шостий вхід зазначеного блока керування і перетворення з входом схеми перетворення сигналів, третій вихід третього рознімання за допомогою каналу передачі даних через сьомий вхід блока керування і перетворення з'єднаний з першим входом схеми формування потенційного коду аналогових сигналів, вихід схеми опитування стану каналу з'єднаний відповідно з другим входом схеми формування потенційного коду аналогових сигналів та першим входом нормуючого підсилювача сигналів, вихід схеми формування потенційного коду аналогових сигналів з'єднаний за допомогою каналу передачі даних з другим входом нормуючого підсилювача сигналів, вихід схеми перетворення шкали з'єднаний з першим входом програмованої логічної інтегральної схеми центрального процесорного пристрою, вихід схеми перетворення сигналів з'єднаний відповідно з другим входом програмованої логічної інтегральної схеми та з першим входом процесора центрального процесорного пристрою, вихід джерела живлення "+5В" з'єднаний з першим входом аналого-цифрового перетворювача, вихід нормуючого підсилювача сигналів з'єднаний з другим входом зазначеного аналого-цифрового перетворювача, вхід/вихід аналого-цифрового перетворювача з'єднаний каналом передачі даних з першим входом/виходом процесора центрального процесорного пристрою, вихід першого рознімання програмування з'єднаний з другим входом зазначеного процесора центрального процесорного пристрою, вихід другого рознімання програмування з'єднаний з третім входом програмованої логічної інтегральної схеми центрального процесорного пристрою, вхід/вихід програмованої логічної інтегральної схеми центрального процесорного пристрою з'єднаний каналом передачі даних з другим входом/виходом процесора центрального процесорного пристрою, перший вихід процесора центрального процесорного пристрою з'єднаний з входом схеми опитування стану каналу, другий вихід зазначеного процесора центрального процесорного пристрою з'єднаний відповідно з третім входом схеми формування потенційного коду аналогових сигналів та з першим входом блока комутації через перший вихід блока керування і перетворення, третій вхід процесора центрального процесорного пристрою з'єднаний з першим виходом блока комутації через перший вхід блока керування і перетворення, четвертий вхід процесора центрального процесорного пристрою з'єднаний з виходом першого рознімання через третій вхід блока керування і перетворення, перший вихід програмованої логічної інтегральної схеми центрального процесорного пристрою з'єднаний з входом підсилювача-формувача, вихід зазначеного підсилювача-формувача з'єднаний з входами, відповідно, першого рознімання та другого рознімання через третій вихід блока керування і перетворення, другий вихід програмованої логічної інтегральної схеми центрального процесорного пристрою з'єднаний з входом схеми формування сигналів паралельного коду, третій вихід програмованої логічної інтегральної схеми центрального процесорного пристрою з'єднаний з входом схеми формування сигналів синхронізації, безпосередньо в блоці комутації кожний з восьми комутаторів контактних каналів, що входять до складу субблока комутаторів, містить по вісім з шестидесяти чотирьох входів контактного каналу та по одному входу лінії сигналів керування, вихід кожного з восьми зазначених комутаторів контактних каналів з'єднаний з відповідними першим-восьмим входами підсумовуючого комутатора контактних каналів, дев'ятий вхід зазначеного підсумовуючого комутатора контактних каналів з'єднаний через перший вхід блока комутації лінією команд керування з першим виходом блока керування і перетворення та із зазначеними лініями сигналів керування, що входять до кожного з восьми зазначених комутаторів контактних каналів, вихід підсумовуючого комутатора контактних каналів з'єднаний з входом схеми нормування і перетворення шкали, а вихід зазначеної схеми нормування і перетворення шкали з'єднаний через перший вхід блока керування і перетворення з входом схеми формування сигналів паралельного коду блока живлення і вихідних каскадів, безпосередньо в блоці живлення і вихідних каскадів четвертий вихід третього рознімання та вихід шостого рознімання з'єднані за допомогою лінії напруги живлення "±27В" відповідно напругою живлення "+27В" з першими входами першої-четвертої схем стабілізації, а напругою живлення "-27В" - з другими входами зазначених першої-четвертої схем стабілізації, виходи зазначених першої-четвертої схем стабілізації виконані з напругою живлення відповідно "+5В", "+12В", "+15В" та "-15В", вхід джерела опорної напруги виконаний під напругу живлення "+15В" і з'єднаний з виходом "+15В" третьої схеми стабілізації, вихід зазначеного джерела опорної напруги з'єднаний з входом вихідного каскаду послідовно через вхід/вихід схеми формування чотирирівневого сигналу та схеми підсилення сигналів, вихід вихідного каскаду з'єднаний через третій вихід блока живлення і вихідних каскадів з входами третього та шостого рознімань локального комутатора, другий вхід схеми формування чотирирівневого сигналу з'єднаний за допомогою двосторонньої багатоканальної інформаційної лінії зв'язку через перший вхід блока живлення і вихідних каскадів з другим виходом блока керування і перетворення, вхід схеми формування сигналів синхронізації та перший вхід схеми формування сигналів паралельного коду з'єднані з третім виходом програмованої логічної інтегральної схеми, вихід схеми формування сигналів синхронізації з'єднаний за допомогою лінії напруги живлення через блок керування і перетворення з входами, відповідно, першого та другого рознімань, другий вхід схеми формування сигналів паралельного коду з'єднаний зі схемою нормування і перетворення шкали блока комутації, вихід зазначеної схеми формування сигналів паралельного коду з'єднаний через третій вихід блока живлення і вихідних каскадів з входами третього та шостого рознімань локального комутатора.

Текст

з другим входом/виходом процесора 23 центрального процесорного пристрою 17, перший вихід процесора 23 центрального процесорного пристрою 17 з'єднано з входом схеми 12 опитування стану каналу, другий вихід зазначеного процесора 23 центрального процесорного пристрою 17 з'єднано, відповідно, з третім входом схеми 11 формування потенційного коду аналогових сигналів та з першим входом блока 3 комутації через перший вихід блока 2 керування і перетворення, третій вхід процесора 23 центрального процесорного пристрою 17 з'єднано з першим виходом блока 3 комутації через перший вхід блока 2 керування і перетворення, четвертий вхід процесора 23 центрального процесорного пристрою 17 з'єднано за допомогою каналу (50) передачі даних з виходом першого роз'єму 5 через третій вхід блока 2 керування і перетворення, перший вихід програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17 з'єднано з входом підсилювача-формувача 21, вихід зазначеного підсилювача-формувача 21 з'єднано з входами, відповідно, першого роз'єму 5 та другого роз'єму 6 через третій вихід блока 2 керування і перетворення, другий вихід програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17 з'єднано з входом схеми 44 формування сигналів паралельного коду блока 4 живлення і вихідних каскадів, третій вихід програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17 з'єднано з входом схеми 43 формування сигналів синхронізації блока 4 живлення і вихідних каскадів (див. блок-схему на фіг. 2). Безпосередньо в блоці комутації кожний з восьми комутаторів (позиції 27...34) контактних каналів, що входять до складу субблока комутаторів 24, містить по вісім з шестидесятичотирьох входів контактного каналу (відповідно позиції 1КК...64КК див. блок-схему на фіг. 3) та по одному входу лінії (58) сигналів керування (позиція «Сигн. упр» - див. блок-схему на фіг. 3), вихід кожного з восьми зазначених комутаторів контактних каналів (позиції 27...34) з'єднано з відповідними першим-восьмим входами підсумовуючого комутатора 25 контактних каналів, дев'ятий вхід зазначеного підсумовуючого комутатора 25 контактних каналів з'єднано через перший вхід блока 3 комутації лінією (позиція 45) команд керування «Сигн. упр» з першим виходом блока 2 керування і перетворення та із зазначеними лініями (58) сигналів керування (позиція «Сигн. упр» - див. блок-схему на фіг. 3), що входять до кожного з восьми зазначених комутаторів (позиції 27...34) контактних каналів, вихід підсумовуючого комутатора 25 контактних каналів з'єднано з входом схеми 26 нормування і перетворення шкали, а вихід (позиція «КК») зазначеної 15 схеми 26 нормування і перетворення шкали з'єднано (за допомогою каналу 46 передачі даних) через перший вхід блока 2 керування і перетворення з входом схеми 44 формування сигналів паралельного коду блока 4 живлення і вихідних каскадів, відповідно, за допомогою каналу (47) передачі даних (див. блок-схему на фіг. 3). Безпосередньо в блоці живлення і вихідних каскадів четвертий вихід третього роз'єму 7 та вихід шостого роз'єму 10 з'єднано за допомогою лінії (53) напруги живлення «±27В», відповідно, напругою живлення «+27В» з першими входами першої-четвертої схем стабілізації (відповідно позиції 35...38), а напругою живлення «-27В» - з другими входами зазначених першої-четвертої схем стабілізації (відповідно позиції 35...З 8), виходи зазначених першої-четвертої схем стабілізації (відповідно позиції 35...З 8) виконано з напругою живлення, відповідно, «+5В», «+12В», «+15В» та «15В», вхід джерела 39 опорної напруги виконано під напругу живлення «+15В» і з'єднано з виходом «+15В» третьої схеми 37 стабілізації, вихід зазначеного джерела 39 опорної напруги з'єднано з входом вихідного каскаду 42 послідовно через вхід/вихід схеми 40 формування чотирирівневого сигналу та схеми 41 підсилення сигналів, вихід вихідного каскаду 42 з'єднано (за допомогою каналу 54 передачі даних -позиція «СІ 3ет» - див. блоксхеми на фіг. 1 та на фіг. 4) через третій вихід блока 4 живлення і вихідних каскадів з входами третього (позиція 7) та шостого роз'ємів (позиція 10) локального комутатора (позиція 1), другий вхід схеми 40 формування чотирирівневого сигналу з'єднано (за допомогою двосторонньої багатоканальної інформаційної лінії 47 зв'язку) через перший вхід блока 4 живлення і вихідних каскадів з другим_виходом блока 2 керування і перетворення, вхід (позиція «СІ») схеми 43 формування сигналів синхронізації та перший вхід схеми 44 формування сигналів паралельного коду з'єднано з третім виходом програмованої логічної інтегральної схеми 22, вихід (позиція «СІ») схеми 43 формування сигналів синхронізації з'єднано (за допомогою лінії 48 напруги живлення) через блок 2 керування і перетворення (з третього виходу зазначеного блока 2) з входами» відповідно, першого (позиція 5) та другого роз'ємів (позиція 6), другий вхід схеми 44 формування сигналів паралельного коду з'єднано зі схемою 26 нормування і перетворення шкали блока 3 комутації, вихід зазначеної схеми 44 формування сигналів паралельного коду з'єднано через третій вихід блока 4 живлення і вихідних каскадів з входами третього (позиція 7) та шостого (позиція 10) роз'ємів локального комутатора (позиція 1) (див. блоксхему на фіг. 4). Локальний комутатор (позиція 1 - див. блоксхему на фіг. 1), який заявляється, працює (використовується) таким чином (після складання його конструктивних елементів (див. блок-схеми на фіг. 2-4) в єдиний функціональний пристрій - див. блоксхему на фіг. 1). Попередньо виготовляють конструктивні елементи локального комутатора (позиція 1), який заявляється, а саме, блок 2 керування і перетво 54292 16 рення (до складу якого входять конструктивні елементи -позиції 11-16, 17 (22-23) та 18-21 - див. блок-схему на фіг. 2), блок З комутації (до складу якого входять конструктивні елементи - позиції 24 (27-34), 25-26 - див. блок-схему на фіг. 3), блок 4 живлення і вихідних каскадів (до складу якого входять конструктивні елементи - позиції 35-44 - див. блок-схему на фіг. 4). Далі зазначені конструктивні елементи локального комутатора (позиція 1), який заявляється, з'єднують між собою згідно з блок-схемами, показаними на фіг. 1 та на фіг. 3-4, для отримання функціонального пристрою - локального комутатора (позиція 1). Після складання конструктивних елементів локального комутатора (позиція 1) в єдиний функціональний пристрій (див. блок-схему на фіг. 1), зазначений локальний комутатор (позиція 1) працює/експлуатується таким чином. Для забезпечення роботи локального комутатора (позиція 1) з першого виходу третього роз'єму 7 на п'ятий вхід блока 2 керування і перетворення поступають синхроімпульси «СІ» з певними параметрами, а на шостий вхід блока 2 керування і перетворення з другого виходу третього роз'єму 7 поступають тактові імпульси «ТІ» з аналогічними параметрами (окрім частоти повторення). При цьому тактові імпульси «ТІ» відстають від заднього фронту синхроімпульсів на тривалість синхроімпульсів і встановлюють схему 43 формування сигналів синхронізації та інші схеми синхронізації локального комутатора (позиція 1) у вихідний стан при його вмиканні або при випадкових відмовах зазначеного локального комутатора (позиція 1). З третього виходу третього роз'єму 7 сигнали команд адаптації локального комутатора (позиція 1) до системи його застосування, вибору структури вихідного послідовного коду та команд керування режимами роботи локального комутатора (позиція 1) по каналу 52 передачі даних поступають на сьомий вхід блока 2 керування і перетворення. З виходу четвертого роз'єму 8 інформація 32-х непарних контактних каналів поступає на третій вхід блока 3 комутації, а з виходу п'ятого роз'єму 9 інформація 32-х парних контактних каналів поступає на четвертий вхід блока 3 комутації (див. блоксхему на фіг. 1). При цьому конструктивно другий вихід блока 4 живлення і вихідних каскадів з'єднано за допомогою лінії 49 напруги живлення «+5В» з другим входом блока 3 комутації (див. блоксхему на фіг. 1 та блок-схему на фіг. 3). У блоці 3 комутації (а саме, в першому (позиція 27), другому (позиція 28), третьому (позиція 29), четвертому (позиція 30), п'ятому (позиція 31), шостому (позиція 32), сьомому (позиція 33) та восьмому (позиція 34) комутаторах контактних каналів - див. блок-схему на фіг. 3) здійснюють комутацію сигналів б4-х контактних каналів у послідовний потенційний код з наступним нормуванням станів цих сигналів та приведенням їх до шкали ТТЛлогіки. Послідовний потенційний код з першого виходу блока 3 комутації поступає по контактному каналу 46 на перший вхід блока 2 керування і перетворення, з першого виходу якого на перший вхід зазначеного блока 3 комутації поступають по 17 лінії 45 команд керування сигнали команд керування. З виходу першого роз'єму 5 інформація 32-х парних аналогових каналів поступає по каналу 50 передачі даних на третій вхід блока 2 керування і перетворення. З виходу другого роз'єму б інформація 3 2-х непарних аналогових каналів поступає по каналу 51 передачі даних на четвертий вхід блока 2 керування і перетворення. З надходженням сигналів синхроімпульсів і тактових імпульсів до блоку 2 керування і перетворення, зазначений блок 2 керування і перетворення формує/передає сигнали керування комутаторами 27...34 восьми каналів субблока 24 комутації блока комутації 3 (надходять через перший вхід по лінії 45 команд керування - див. блоксхеми на фіг. 1 та на фіг. 3), та на підсумовуючий комутатор 25 контактних каналів. Зазначені сигнали послідовно циклічно здійснюють опитування стану 64-х контактних каналів і формують потік потенційного коду сигналів контактних датчиків. З зазначених комутаторів (позиції 27...34) інформативні сигнали поступають на перший...восьмий входи підсумовуючого комутатора 25 контактних каналів, а з нього - на вхід схеми 26 нормування і перетворення шкали і далі по контактному каналу 46 (з виходу "КК") на перший вхід блока 2 керування і перетворення, які з другого виходу блока 2 керування і перетворення по двосторонній багатоканальній інформаційній лінії 47 звязку поступають вхід схеми 44 формування сигналів паралельного коду блока 4 живлення і вихідних каскадів. Блок комутації 3 (в підсумовуючому комутаторі 25) об'єднує сигнали з виходів комутаторів (позиції 27...34) контактних каналів субблока 24 комутації, перетворює ці сигнали у послідовний потенційний код, а схема 26 нормування і перетворення шкали приводить їх до шкали ТТЛ-логіки і передає (позиція «КК з БК» - див. блок-схему на фіг. 2) по контактному каналу 46 на перший вхід блока 2 керування і перетворення (а безпосередньо в блоці 2 - на третій вхід процесора 23 центрального процесорного пристрою 17 зазначеного блока 2 керування і перетворення) - див. блок-схему на фіг. 2. При цьому центральний процесорний пристрій 17 конструктивно утворюється процесором 23 разом з програмованою логічною інтегральною схемою 22 (див. блок-схему на фіг. 2). З третього виходу блока 2 керування і перетворення синхроімпульси третього ступеня синхронізації «СІ Зет» поступають на входи першого (позиція 5), другого (позиція 6), четвертого (позиція 8) та п'ятого (позиція 9) роз'ємів (див. блок-схему на фіг. 1). З другого входу/виходу блока 2 керування і перетворення сигнали керування станом коду через перший вхід блока 4 живлення і вихідних каскадів поступають по двосторонній багатоканальній інформаційній лінії 47 зв'язку на другий вхід схеми 40 формування чотирирівневого сигналу (див. блок-схеми на фіг. 1 та фіг. 4), яка формує інформаційні структури двопозиційного та чотирипозиційного кодів і подає Їх через схему 41 підсилення сигналів, де вони підсилюються до необхідного 54292 18 рівня, у вихідний каскад 42, з виходу якого вони поступають по каналу 54 передачі даних на входи третього (позиція 7) та шостого (позиція 10) роз'ємів локального комутатора (позиція 1) (див. блоксхему на фіг. 4). З четвертого виходу третього роз'єму 7 та виходу шостого роз'єму 10 напруга ±27В поступає по лінії 53 напруги живлення «±27В» на другий вхід блока 4 живлення і вихідних каскадів, а саме (безпосередньо в зазначеному блоці 4), на перший та другий входи першої (позиція 35), другої (позиція 36), третьої (позиція 37) та четвертої (позиція 38) схем стабілізації зазначеного блока 4 живлення і вихідних каскадів, які формують напруги живлення, відповідно, +5В, +12В, +15В, -15В (відповідно для віх блоків локального комутатора 1) -див. блок-схему на фіг. 4. Інформація аналогових каналів з третього виходу третього роз'єму 7 по каналу 52 передачі даних надходить на перший вхід схеми 11 формування потенційного коду аналогових сигналів блока 2 керування і перетворення, яка формує код аналогових каналів (канали 1-64), об'єднує його з сигналами визначення стану лінії, які у свою чергу формує схема 12 опитування стану каналу, і подає (по каналу 55 передачі даних) інформативні сигнали в нормуючий підсилювач 16 сигналів, де ці сигнали перетворюють у шкалу 0-5В і далі подають в аналого-цифровий перетворювач 18 - на його другий вхід (див. блок-схему на фіг. 2). В аналого-цифровому перетворювачі 18 нормований потенційний код аналогових каналів перетворюють в дванадцятирозрядний послідовний код, який поступає по двосторонньому каналу зв'язку (канал 56 передачі даних) на вхід/вихід процесора 23 центрального процесорного пристрою 17 (див. блок-схему на фіг. 2). Живлення аналогоцифрового перетворювача 18 здійснюють за допомогою прецизійного джерела 15 живлення «+5В», яке надходить на перший вхід зазначеного аналого-цифрового перетворювача 18 (див. блоксхему на фіг. 2). Процесор 23 двостороннім каналом зв'язку (канал 57 передачі даних) з'єднаний з входом/виходом програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17. Синхроімпульси (СІ) з першого виходу третього роз'єму 7 через п'ятий вхід блока 2 керування і перетворення поступають на вхід схеми 13 перетворення шкали, яка вхідні сигнали в шкалі від мінус 1,5-0,5В до 1,2-4В перетворює в шкалу ТТЛ-логіки і подає їх на перший вхід програмованої логічної інтегральної схеми 22 (див. блок-схеми на фіг. 1 та на фіг. 2). Тактові імпульси (ТІ) з другого виходу третього роз'єму 7 через шостий вхід блока 2 керування і перетворення поступають на вхід схеми 14 перетворення сигналів, яка приводить амплітуду вхідних тактових імпульсів (ТІ) до шкали ТТЛ-логіки і передає їх на перший вхід процесора 23 та на другий вхід програмованої логічної інтегральної схеми 22 (див. блок-схеми на фіг. 1 та на фіг. 2). Сигнали аналогової та контактної інформації з другого виходу процесора 23 блока 2 керування і перетворення поступають на третій вхід схеми 11 формування потенційного коду аналогових каналів 19 та з першого виходу зазначеного блока 2 по лінії 45 команд керування поступають водночас як на дев'ятий вхід підсумовуючого комутатора 25 контактних каналів, так і на перші входи кожного з восьми (першого (позиція 27), другого (позиція 28), третього (позиція 29), четвертого (позиція 30), п'ятого (позиція 31), шостого (позиція 32), сьомого (позиція 33) та восьмого (позиція 34) див. блоксхему на фіг. 3) комутаторів контактних каналів. З першого виходу процесора 23 сигнали керування поступають на вхід схеми 12 опитування стану каналу. З третього виходу схеми 44 формування сигналів паралельного коду блока 4 живлення і вихідних каскадів синхроімпульси таксування розрядних імпульсів (позиція «СІ Зет») по каналу 54 передачі даних поступають на входи третього (позиція 7) та шостого (позиція 10) роз'ємів локального комутатора 1. З першого виходу програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17 блока 2 керування і перетворення синхроімпульси третього ступеня комутації та синхроімпульси таксування розрядних імпульсів через схему 44 формування сигналів паралельного коду блока 4 живлення і вихідних каскадів в шкалі ТТЛлогіки поступають (по двосторонній багатоканальній інформаційній лінії 47 зв'язку) також на входи третього (позиція 7) та шостого (позиція 10) роз'ємів аналогового комутатора 1, а саме, з третього виходу блока 4 живлення і вихідних каскадів по каналу 54 передачі даних на входи зазначених третього (позиція 7) та шостого (позиція 10) роз'ємів аналогового комутатора 1 - див. блок-схеми на фіг. 1 та на фіг. 4. З першого виходу програмованої логічної інтегральної схеми 22 центрального процесорного пристрою 17 (з третього виходу блока 2 керування і перетворення) синхроімпульси третього ступеня комутації (позиція «С1 3ет») поступають у підсилювач-формувач 21, де їх формують по амплітуді у вихідну шкалу від 0,2 - мінус 1В до 1,5 - 2,5В і 54292 20 подають на входи, відповідно, першого (позиція 5) та другого (позиція 6) роз'ємів аналогового комутатора 1 з третього виходу блока 2 керування і перетворення (див. блок-схеми на фіг. 1 та на фіг. 2). Сигнали керування з виходу другого роз'єму програмування 20 подаються на третій вхід прграмованої логічної інтегральної схеми 22, а з першого роз'єму програмування 19 сигнали керування подаються на другий вхід процесора 23 (що входять до складу центрального процесорного пристрою 17 (див. блок-схему на фіг. 2). У той же час підсилювач-формувач отримує синхроімпульси з прграмованої логічної інтегральної схеми 22 і подає їх на входи першого (позиція 5), другого (позиція 6), четвертого (позиція 8) та п'ятого (позиція 9) роз'ємів локального комутатора 1 (див. блок-схеми на фіг, 1 та на фіг. 2). Підвищення ефективності застосування локального комутатора, який заявляється, у порівнянні з прототипом, досягається шляхом введення до складу базових виконавчих елементів локального комутатора нових складових частин, що дозволить розширити функціональні можливості локального комутатора, збільшити бистродію, збільшити кількість каналів, що обслуговуються, а також підвищити його надійність та ефективність при зменшенні габаритно-масових характеристик та обмеженнях. Джерела інформації 1. Назаров А.В., Козырев Г.И., Шитов И.В., Обрученков В.П., Древин А.В., Краскин В.Б. и др.. «Современная телеметрия в теории и на практике». Учебный курс. Издательство «Наука и техника». Санкт-Петербург, 2007, стор. 251-253 -аналог. 2. Назаров А.В., Козырев Г.И., Шитов И.В., Обрученков В.П., Древин А.В., Краскин В.Б. и др.. «Современная телеметрия в теории и на практике». Учебный курс. Издательство «Наука и техника». Санкт-Петербург, 2007, стор. 244-253, мал. 3.54 -прототип. 21 54292 22 23 Комп’ютерна верстка І.Скворцова 54292 Підписне 24 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюLocal commutator

Автори англійськоюKoniukhov Stanislav Mykolaiovych, Kuriachyi Yevhen Vitaliiovych, Svyrydenko Anatolii Oleksiiovych, Kolesnyk Kostiantyn Ivanovych, Nemchyn Oleksandr Fedorovych, Yakovlev Vitalii Vasyliovych, Horbulin Volodymyr Pavlovych

Назва патенту російськоюЛокальный коммутатор

Автори російськоюКонюхов Станислав Николаевич, Курячий Евгений Витальевич, Свириденко Анатолий Алексеевич, Колесник Константин Иванович, Немчин Александр Федорович, Яковлев Виталий Васильевич, Горбулин Владимир Павлович

МПК / Мітки

МПК: H04Q 1/00

Код посилання

<a href="https://ua.patents.su/12-54292-lokalnijj-komutator.html" target="_blank" rel="follow" title="База патентів України">Локальний комутатор</a>

Попередній патент: Ресорна передня стійка шасі для безпілотного літального апарата

Наступний патент: Спосіб виробництва спечених підшипників ковзання з контрольованим розміром пор

Випадковий патент: Спосіб фіксування рівня шуму та керування подрібненням залізорудної сировини в барабанному млині на основі поточного сигналу