Пристрій для ділення послідовних кодів золотої пропорції

Номер патенту: 5494

Опубліковано: 15.03.2005

Формула / Реферат

Пристрій для ділення послідовних кодів золотої пропорції, що містить тактовий вхід, вхід діленого, вхід дільника та n блоків визначення розряду частки (де n - розрядність операндів), кожен з яких містить тактовий вхід, вхід діленого, вхід дільника, вихід діленого, вихід дільника, вихід частки, перший, другий і третій вузли затримки, віднімач, перший елемент АБО, перший D-тригер та комутатор, причому тактовий вхід пристрою з'єднаний з тактовими входами всіх блоків визначення розряду частки, вихід діленого кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом діленого наступного блока визначення розряду частки, вихід дільника кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом дільника наступного блока визначення розряду частки, а в кожному блоці визначення розряду частки тактовий вхід блока з'єднаний з тактовими входами першого, другого і третього вузлів затримки та віднімача, вхід встановлення в нульовий стан віднімача з'єднаний зі входом встановлення в нульовий стан першого D-тригера, вхід діленого блока з'єднаний з інформаційним входом першого вузла затримки та входом зменшуваного віднімача, вхід дільника з'єднаний з інформаційним входом другого вузла затримки та входом від'ємника віднімача, інформаційний вихід віднімача з'єднаний з першим інформаційним входом комутатора, вихід першого вузла затримки з'єднаний з другим інформаційним входом комутатора, знаковий вихід віднімача з'єднаний з інформаційним входом D першого D-тригера, прямий вихід якого з'єднаний з керуючим входом комутатора, вихід якого є виходом діленого блока, який відрізняється тим, що в нього введено вхід синхронізації початку числа, вихід синхронізації початку числа та вихід частки, а в кожному блоці визначення розряду частки введено вхід частки, вхід синхронізації початку числа, вихід синхронізації початку числа, четвертий вузол затримки, другий, третій, четвертий і п'ятий D-тригери, другий і третій елементи АБО та елемент І, причому, вхід діленого пристрою з'єднаний зі входом діленого першого блока визначення розряду частки, вхід дільника пристрою з'єднаний зі входом дільника першого блока визначення розряду частки, вхід частки першого блока визначення розряду частки з'єднаний з шиною логічного нуля, вихід частки кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом частки наступного блока, вихід частки n-го блока визначення розряду частки з'єднаний з виходом частки пристрою, вхід синхронізації початку числа пристрою з'єднаний зі входом синхронізації початку числа першого блока визначення розряду частки, вихід синхронізації початку числа кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом синхронізації початку числа наступного блока визначення розряду частки, вихід синхронізації початку числа n-го блока визначення розряду частки з'єднаний з виходом синхронізації початку числа пристрою, а в кожному блоці визначення розряду частки тактовий вхід блока з'єднаний з тактовими входами четвертого вузла затримки і четвертого та п'ятого D-тригерів, вхід частки блока з'єднаний з інформаційним входом третього вузла затримки, вхід синхронізації початку числа з'єднаний з інформаційним входом четвертого вузла затримки і входами встановлення в нульовий стан першого, другого, третього і четвертого D-тригерів та першим входом другого елемента АБО, інформаційний вихід першого вузла затримки з'єднаний з першим входом першого елемента АБО, інформаційний вихід другого вузла затримки з'єднаний з тактовим входом третього D-тригера, інформаційним входом п'ятого D-тригера та другим входом першого елемента АБО, вихід якого з'єднаний з тактовим входом другого D-тригера, інформаційний вхід якого з'єднаний з шиною логічної одиниці, а вихід з'єднаний з тактовим входом першого D-тригера, інверсний вихід якого з'єднаний з першим входом елемента І, прямий вихід п'ятого D-тригера є виходом дільника блока, інформаційний вхід третього D-тригера з'єднаний з шиною логічної одиниці, а вихід з'єднаний з другим входом елемента І та інформаційними входом четвертого D-тригера, інверсний вихід якого з'єднаний з третім входом елемента І, вихід якого з'єднаний з першим входом третього елемента АБО, вихід третього вузла затримки з'єднаний з другим входом третього елемента АБО, вихід якого є виходом частки блока, вихід четвертого вузла затримки є виходом синхронізації початку числа блока та з'єднаний з другим входом другого елемента АБО, вихід якого з'єднаний зі входом встановлення в нульовий стан п'ятого D-тригера.

Текст

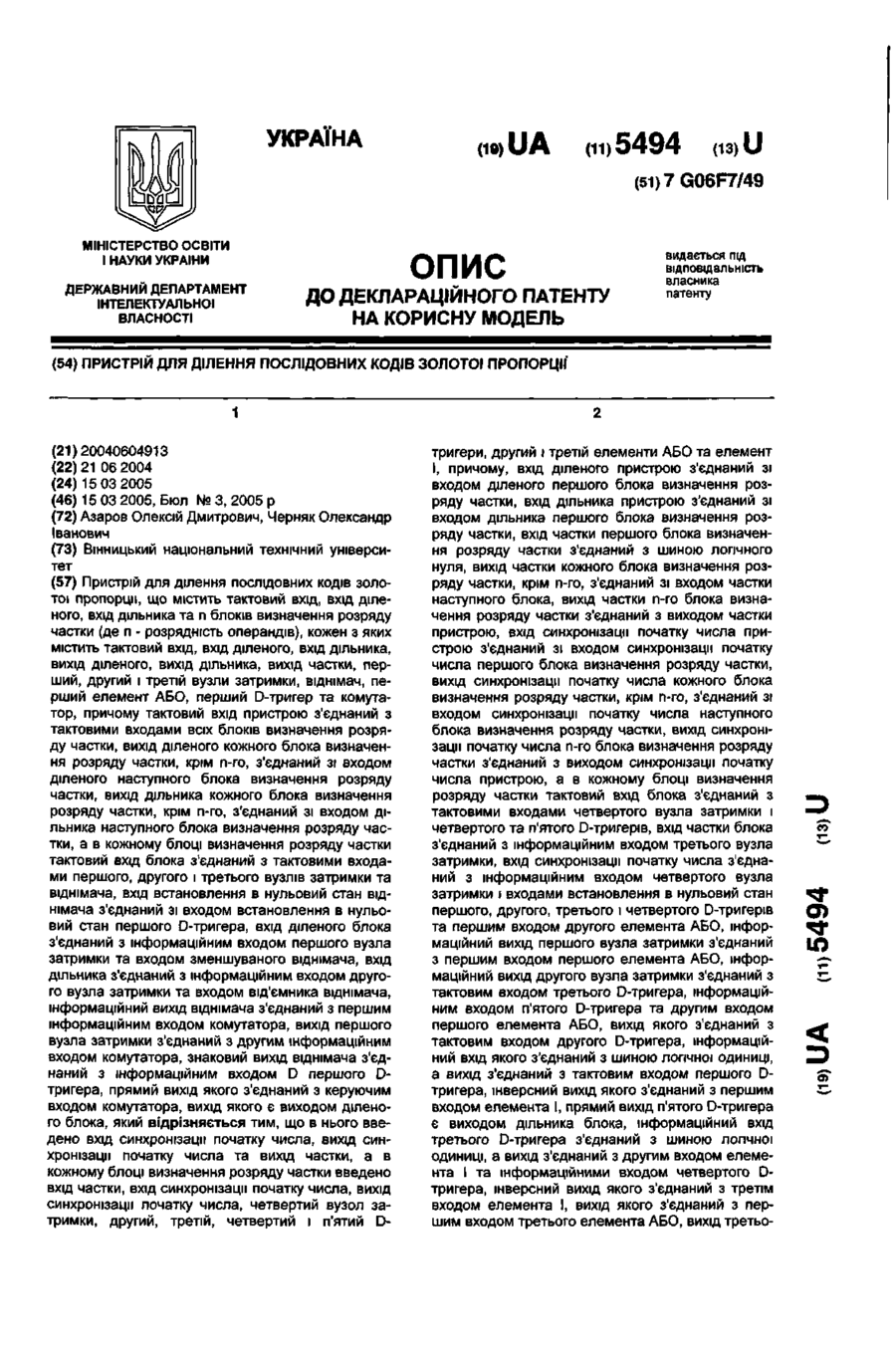

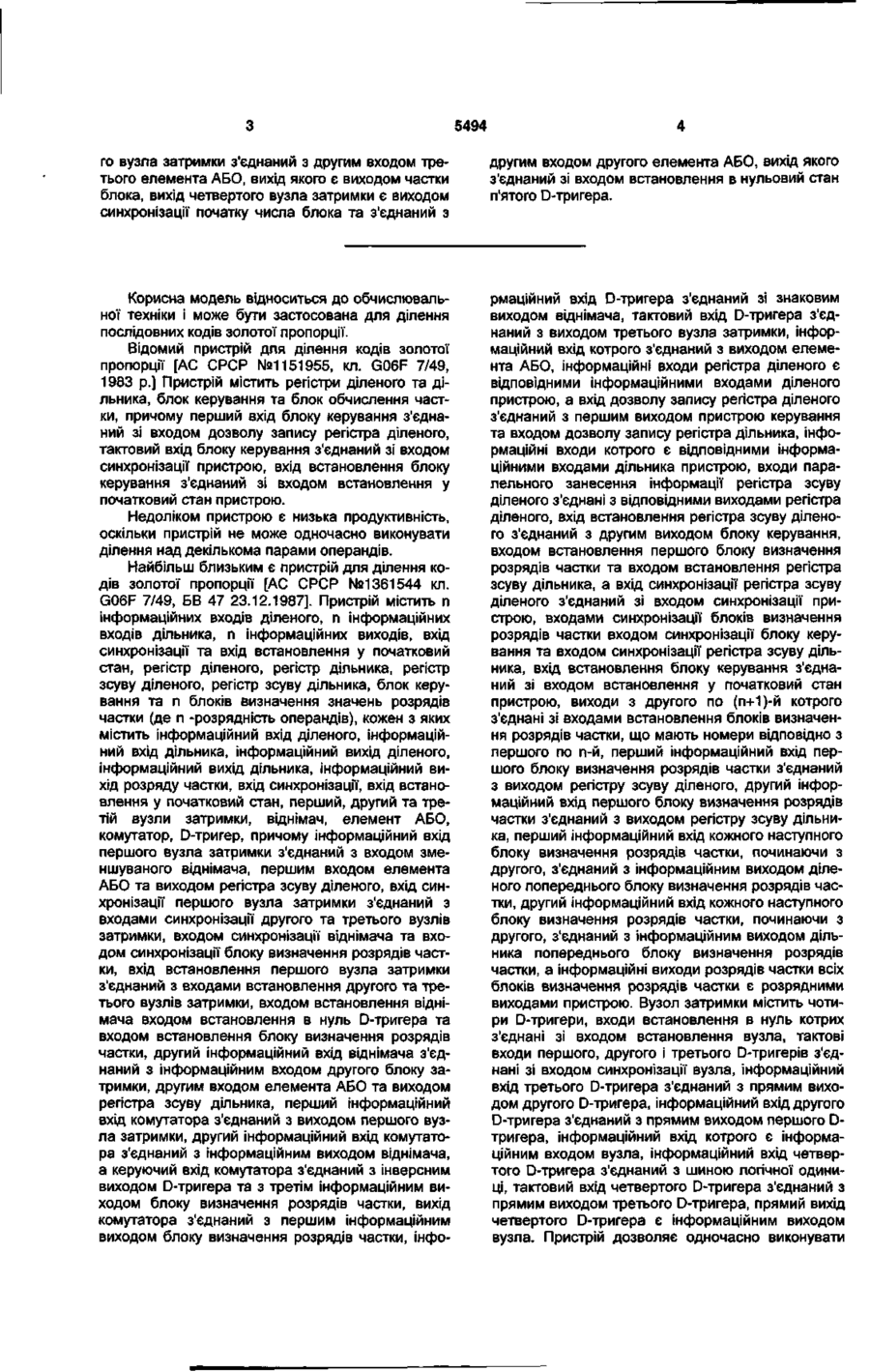

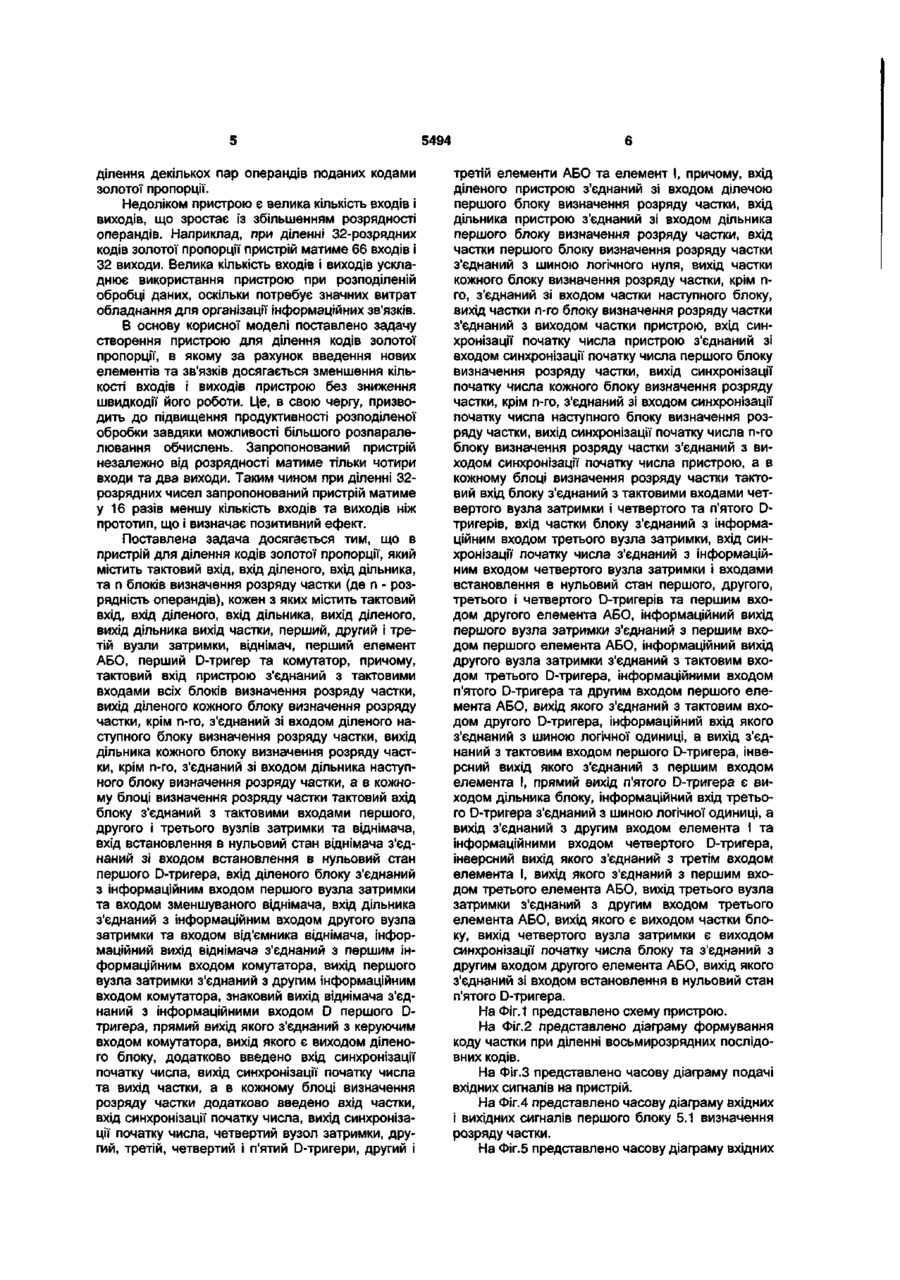

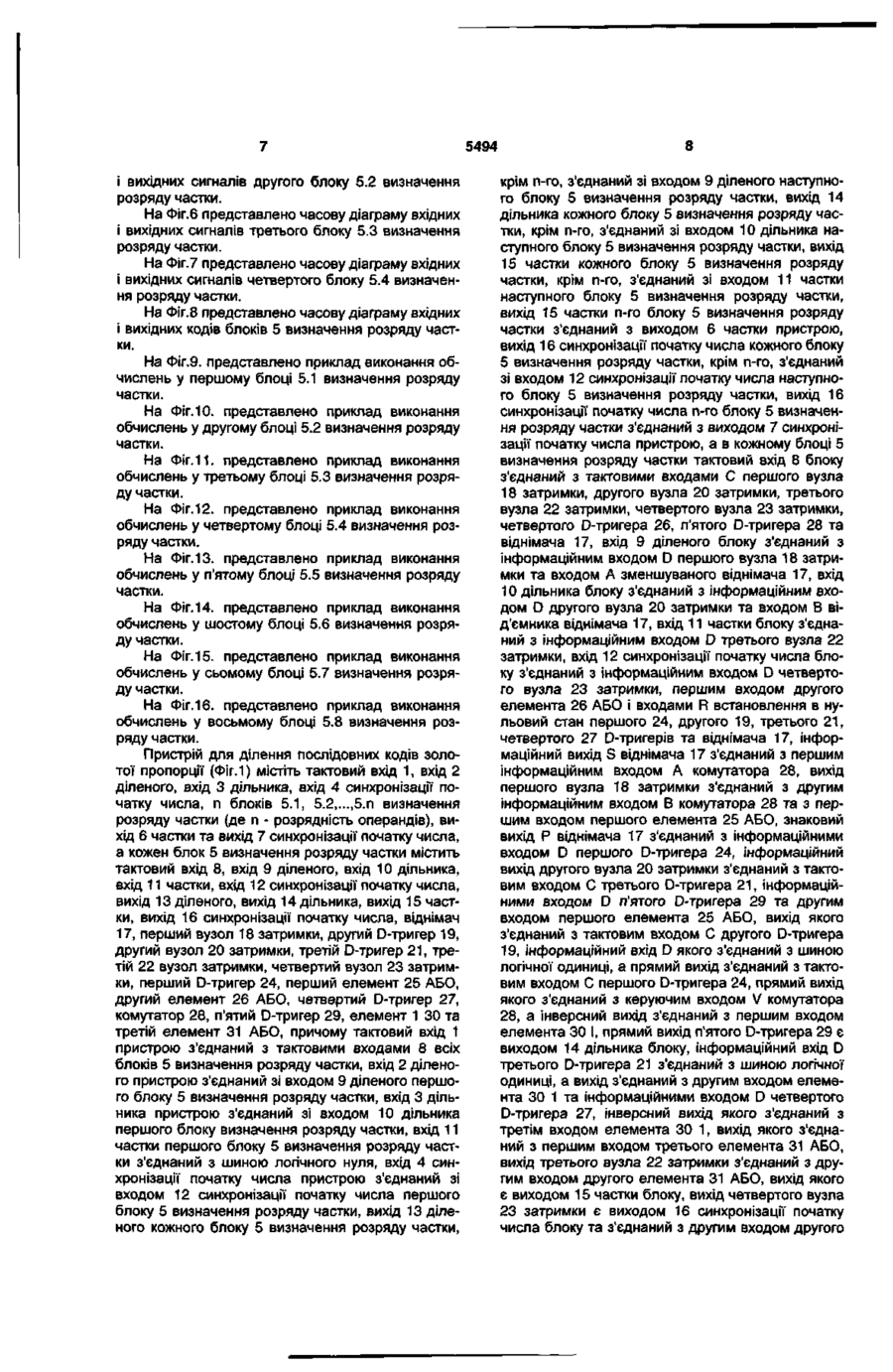

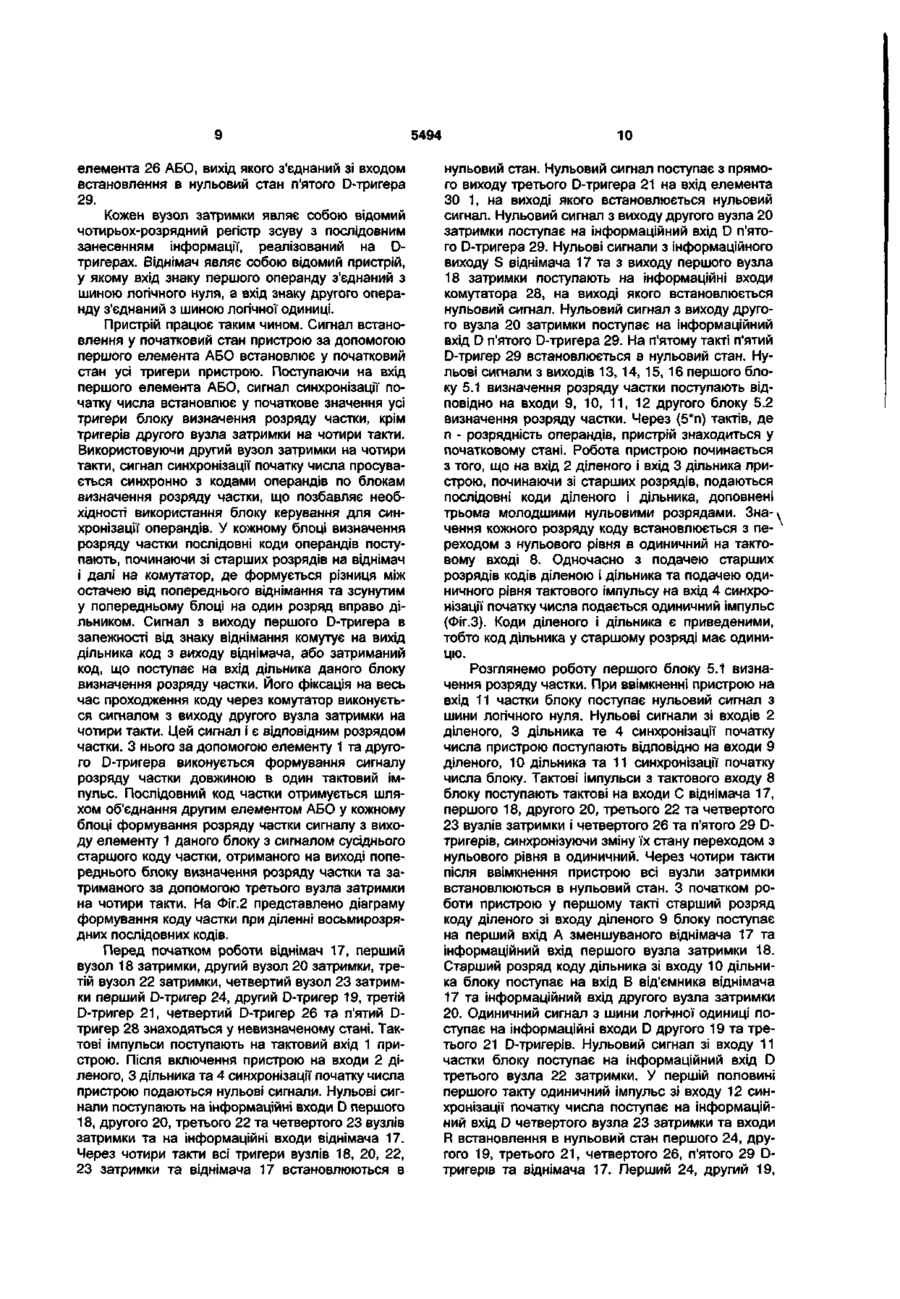

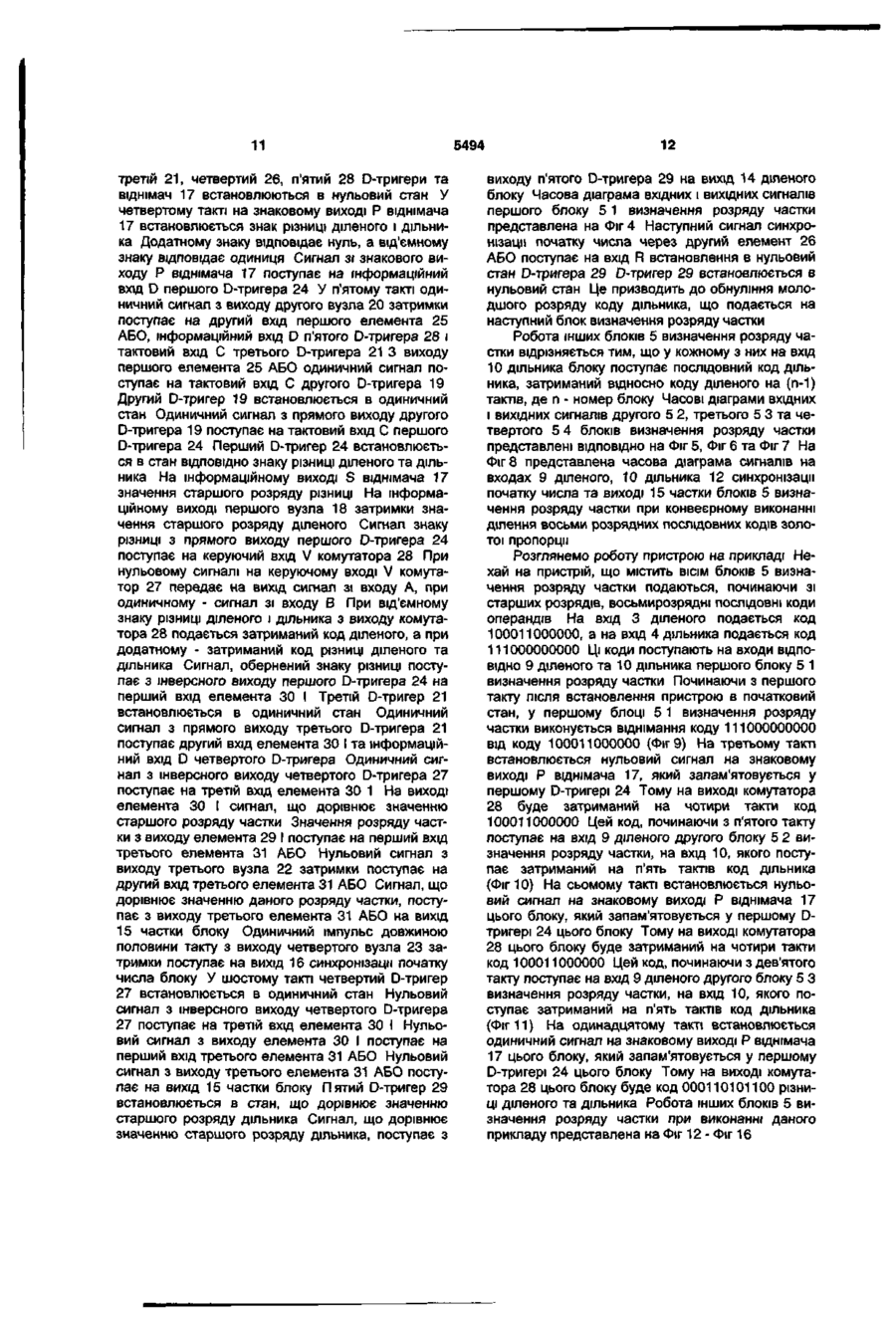

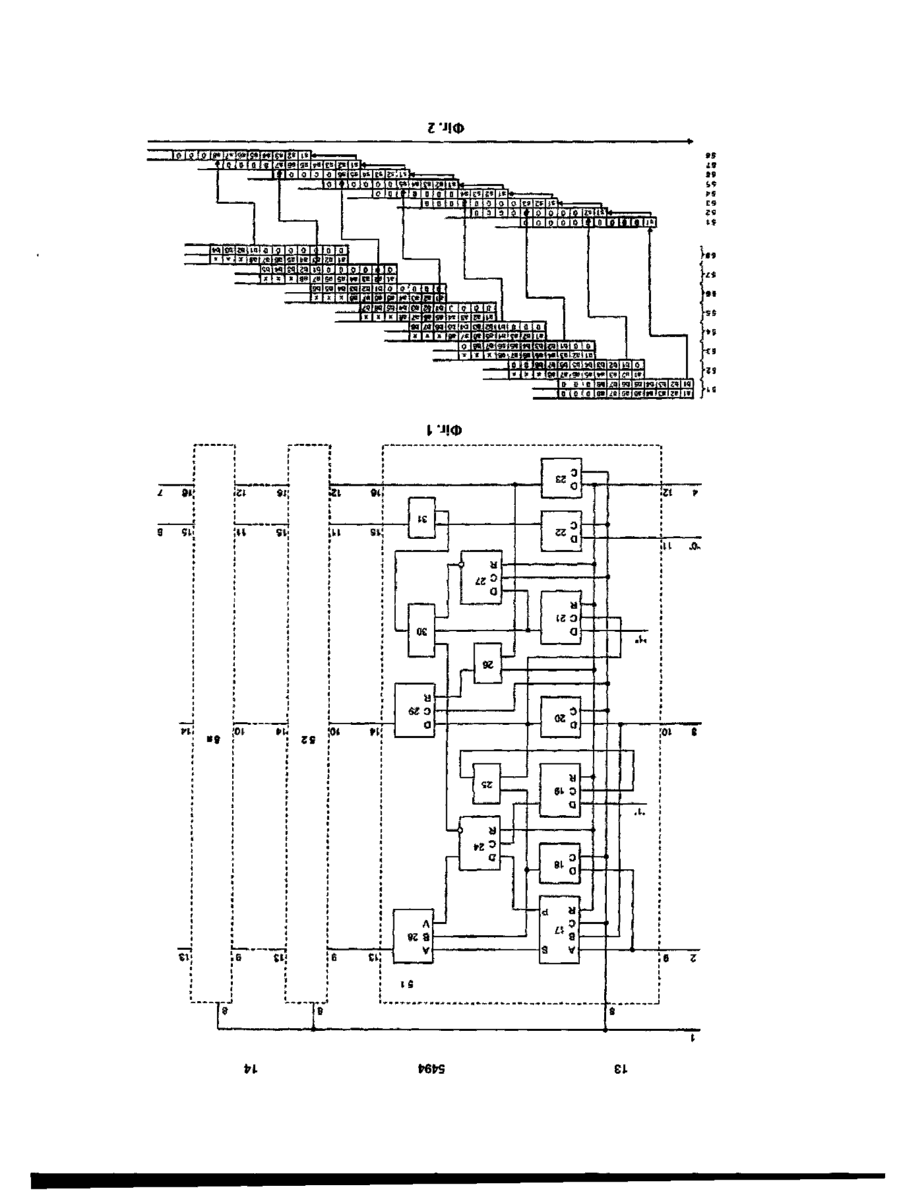

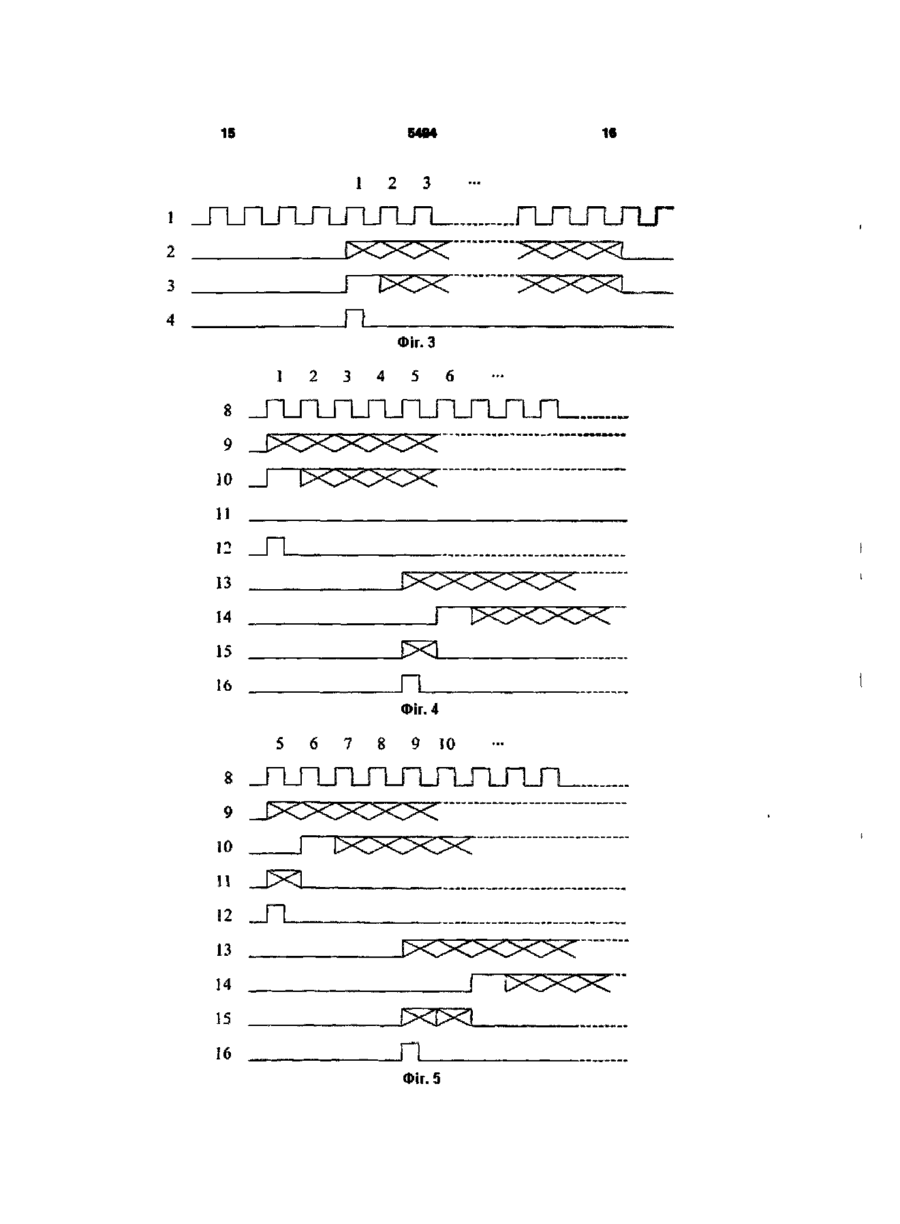

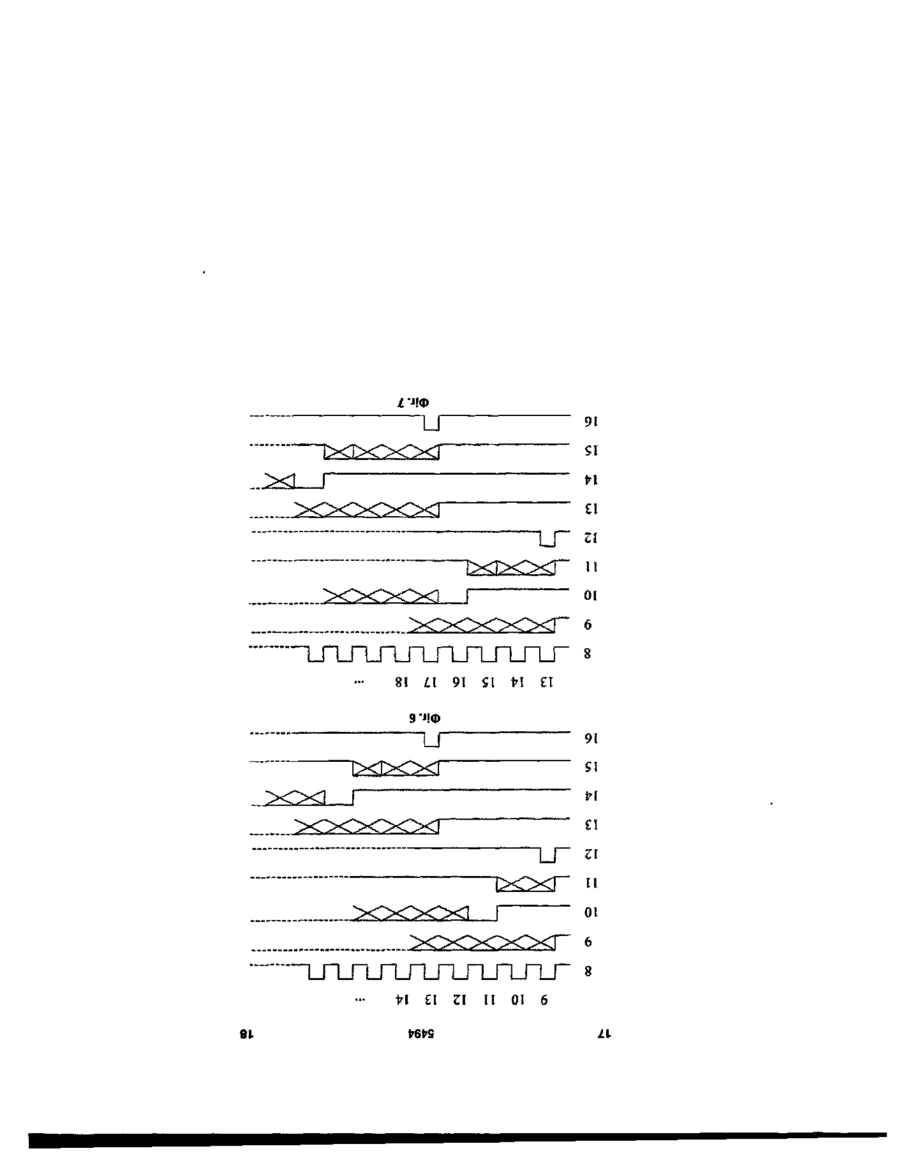

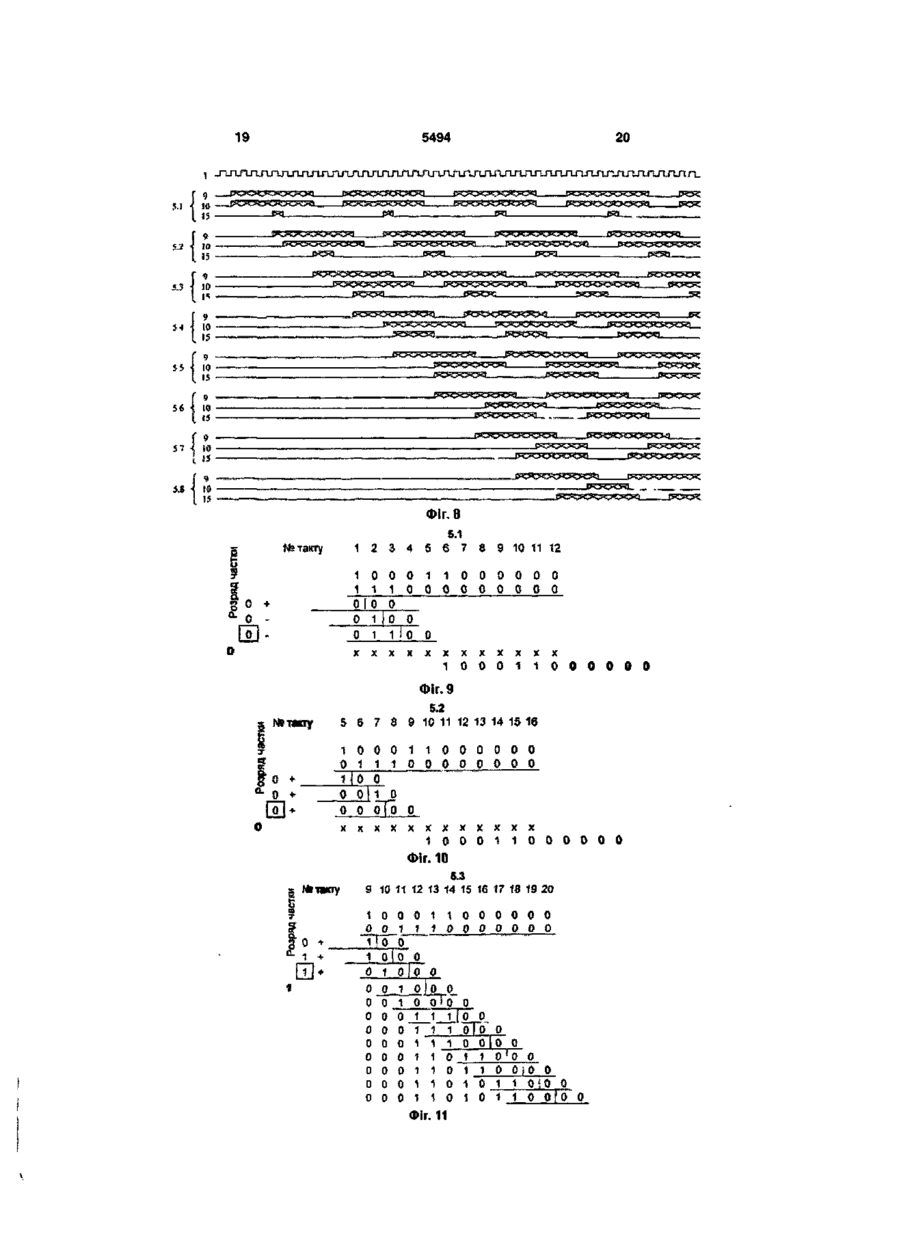

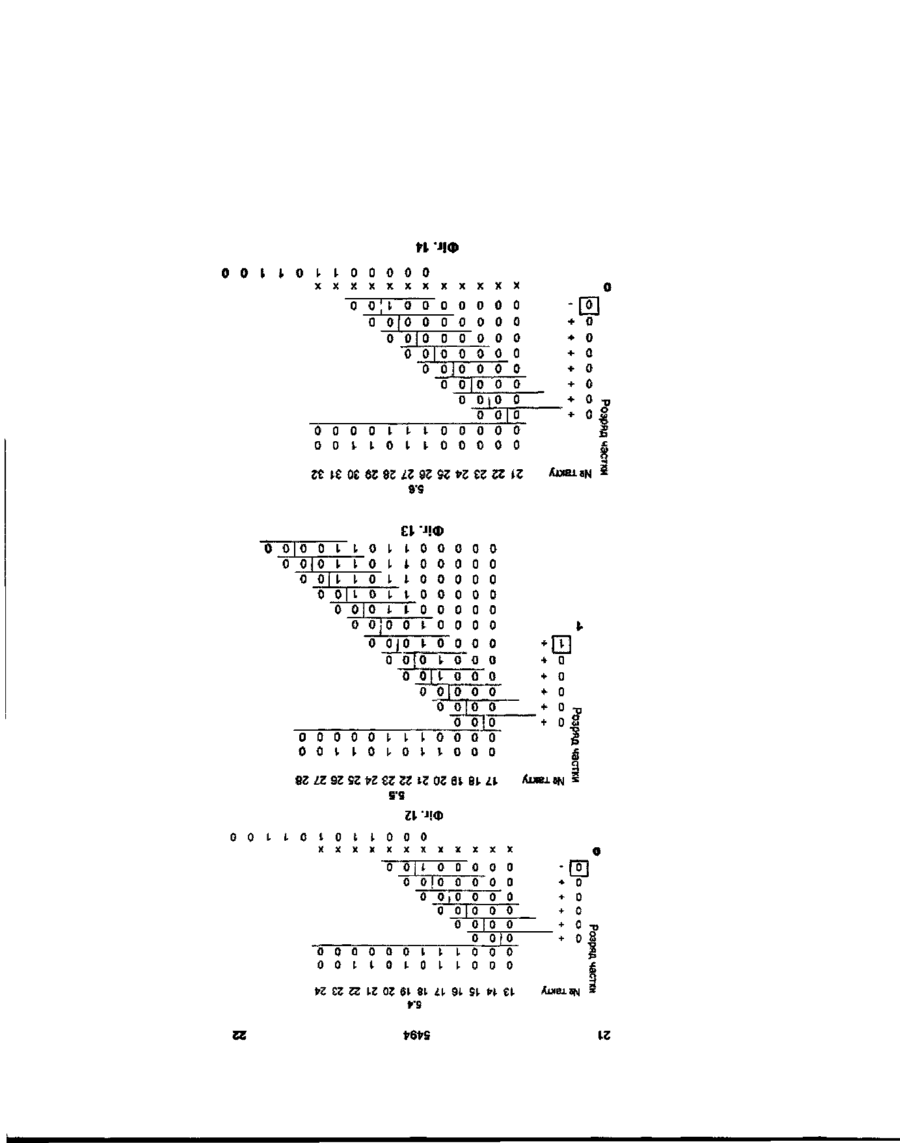

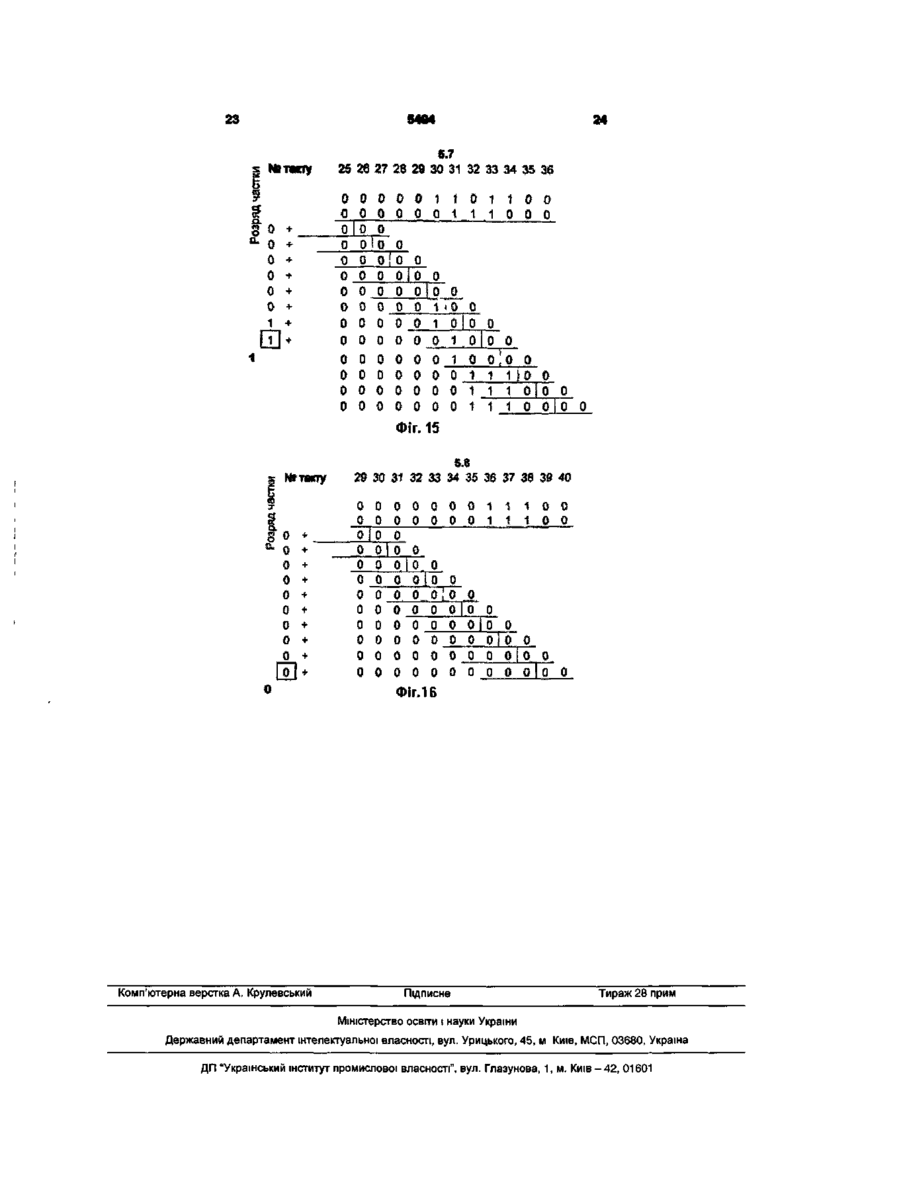

Пристрій для ділення послідовних кодів золотої пропорції, що містить тактовий вхід, вхід діленого, вхід дільника та п блоків визначення розряду частки (де п - розрядність операндів), кожен з яких містить тактовий вхід, вхід діленого, вхід дільника, вихід діленого, вихід дільника, вихід частки, перший, другий і третій вузли затримки, віднімач, перший елемент АБО, перший D-тригер та комутатор, причому тактовий вхід пристрою з'єднаний з тактовими входами всіх блоків визначення розряду частки, вихід діленого кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом діленого наступного блока визначення розряду частки, вихід дільника кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом дільника наступного блока визначення розряду частки, а в кожному блоці визначення розряду частки тактовий вхід блока з'єднаний з тактовими входами першого, другого і третього вузлів затримки та віднімача, вхід встановлення в нульовий стан віднімача з'єднаний зі входом встановлення в нульовий стан першого D-тригера, вхід діленого блока з'єднаний з інформаційним входом першого вузла затримки та входом зменшуваного віднімача, вхід дільника з'єднаний з інформаційним входом другого вузла затримки та входом від'ємника віднімача, інформаційний вихід віднімача з'єднаний з першим інформаційним входом комутатора, вихід першого вузла затримки з'єднаний з другим інформаційним входом комутатора, знаковий вихід віднімача з'єднаний з інформаційним входом D першого Dтригера, прямий вихід якого з'єднаний з керуючим входом комутатора, вихід якого є виходом діленого блока, який відрізняється тим, що в нього введено вхід синхронізації початку числа, вихід синхронізації початку числа та вихід частки, а в кожному блоці визначення розряду частки введено вхід частки, вхід синхронізації початку числа, вихід синхронізації початку числа, четвертий вузол затримки, другий, третій, четвертий і п'ятий D тригери, другий і третій елементи АБО та елемент І, причому, вхід діленого пристрою з'єднаний зі входом діленого першого блока визначення розряду частки, вхід дільника пристрою з'єднаний зі входом дільника першого блока визначення розряду частки, вхід частки першого блока визначення розряду частки з'єднаний з шиною логічного нуля, вихід частки кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом частки наступного блока, вихід частки n-го блока визначення розряду частки з'єднаний з виходом частки пристрою, вхід синхронізації початку числа пристрою з'єднаний зі входом синхронізації початку числа першого блока визначення розряду частки, вихід синхронізації початку числа кожного блока визначення розряду частки, крім n-го, з'єднаний зі входом синхронізації початку числа наступного блока визначення розряду частки, вихід синхронізації початку числа n-го блока визначення розряду частки з'єднаний з виходом синхронізації початку числа пристрою, а в кожному блоці визначення розряду частки тактовий вхід блока з'єднаний з тактовими входами четвертого вузла затримки і четвертого та п'ятого D-тригерів, вхід частки блока з'єднаний з інформаційним входом третього вузла затримки, вхід синхронізації початку числа з'єднаний з інформаційним входом четвертого вузла затримки і входами встановлення в нульовий стан першого, другого, третього і четвертого D-тригерів та першим входом другого елемента АБО, інформаційний вихід першого вузла затримки з'єднаний з першим входом першого елемента АБО, інформаційний вихід другого вузла затримки з'єднаний з тактовим входом третього D-тригера, інформаційним входом п'ятого D-тригера та другим входом першого елемента АБО, вихід якого з'єднаний з тактовим входом другого D-тригера, інформаційний вхід якого з'єднаний з шиною логічної одиниці, а вихід з'єднаний з тактовим входом першого Dтригера, інверсний вихід якого з'єднаний з першим входом елемента І, прямий вихід п'ятого D-тригера є виходом дільника блока, інформаційний вхід третього D-тригера з'єднаний з шиною логічної одиниці, а вихід з'єднаний з другим входом елемента І та інформаційними входом четвертого Dтригера, інверсний вихід якого з'єднаний з третім входом елемента І, вихід якого з'єднаний з першим входом третього елемента АБО, вихід третьо О) ю О) 5494 го вузла затримки з'єднаний з другим входом третього елемента АБО, вихід якого є виходом частки блока, вихід четвертого вузла затримки є виходом синхронізації початку числа блока та з'єднаний з другим входом другого елемента АБО, вихід якого з'єднаний зі входом встановлення в нульовий стан п'ятого D-тригера. Корисна модель відноситься до обчислювальної техніки і може бути застосована для ділення послідовних кодів золотої пропорції. Відомий пристрій для ділення кодів золотої пропорції [АС СРСР №1151955, кл. G06F 7/49, 1983 p.] Пристрій містить регістри діленого та дільника, блок керування та блок обчислення частки, причому перший вхід блоку керування з'єднаний зі входом дозволу запису регістра діленого, тактовий вхід блоку керування з'єднаний зі входом синхронізації пристрою, вхід встановлення блоку керування з'єднаний зі входом встановлення у початковий стан пристрою. Недоліком пристрою є низька продуктивність, оскільки пристрій не може одночасно виконувати ділення над декількома парами операндів. Найбільш близьким є пристрій для ділення кодів золотої пропорції [АС СРСР №1361544 кл. G06F 7/49, БВ 47 23.12.1987]. Пристрій містить п інформаційних входів діленого, п інформаційних входів дільника, п інформаційних виходів, вхід синхронізації та вхід встановлення у початковий стан, регістр діленого, регістр дільника, регістр зсуву діленого, регістр зсуву дільника, блок керування та п блоків визначення значень розрядів частки (де п -розрядність операндів), кожен з яких містить інформаційний вхід діленого, інформаційний вхід дільника, інформаційний вихід діленого, інформаційний вихід дільника, інформаційний вихід розряду частки, вхід синхронізації, вхід встановлення у початковий стан, перший, другий та третій вузли затримки, віднімач, елемент АБО, комутатор, D-тригер, причому інформаційний вхід першого вузла затримки з'єднаний з входом зменшуваного віднімача, першим входом елемента АБО та виходом регістра зсуву діленого, вхід синхронізації першого вузла затримки з'єднаний з входами синхронізації другого та третього вузлів затримки, входом синхронізації віднімача та входом синхронізації блоку визначення розрядів частки, вхід встановлення першого вузла затримки з'єднаний з входами встановлення другого та третього вузлів затримки, входом встановлення віднімача входом встановлення в нуль D-тригера та входом встановлення блоку визначення розрядів частки, другий інформаційний вхід віднімача з'єднаний з інформаційним входом другого блоку затримки, другим входом елемента АБО та виходом регістра зсуву дільника, перший інформаційний вхід комутатора з'єднаний з виходом першого вузла затримки, другий інформаційний вхід комутатора з'єднаний з інформаційним виходом віднімача, а керуючий вхід комутатора з'єднаний з інверсним виходом D-тригера та з третім інформаційним виходом блоку визначення розрядів частки, вихід комутатора з'єднаний з першим інформаційним виходом блоку визначення розрядів частки, інфо рмаційний вхід D-тригера з'єднаний зі знаковим виходом віднімача, тактовий вхід D-тригера з'єднаний з виходом третього вузла затримки, інформаційний вхід котрого з'єднаний з виходом елемента АБО, інформаційні входи регістра діленого є відповідними інформаційними входами діленого пристрою, а вхід дозволу запису регістра діленого з'єднаний з першим виходом пристрою керування та входом дозволу запису регістра дільника, інформаційні входи котрого є відповідними інформаційними входами дільника пристрою, входи паралельного занесення інформації регістра зсуву діленого з'єднані з відповідними виходами регістра діленого, вхід встановлення регістра зсуву діленого з'єднаний з другим виходом блоку керування, входом встановлення першого блоку визначення розрядів частки та входом встановлення регістра зсуву дільника, а вхід синхронізації регістра зсуву діленого з'єднаний зі входом синхронізації пристрою, входами синхронізації блоків визначення розрядів частки входом синхронізації блоку керування та входом синхронізації регістра зсуву дільника, вхід встановлення блоку керування з'єднаний зі входом встановлення у початковий стан пристрою, виходи з другого по (п+1)-й котрого з'єднані зі входами встановлення блоків визначення розрядів частки, що мають номери відповідно з першого по п-й, перший інформаційний вхід першого блоку визначення розрядів частки з'єднаний з виходом регістру зсуву діленого, другий інформаційний вхід першого блоку визначення розрядів частки з'єднаний з виходом регістру зсуву дільника, перший інформаційний вхід кожного наступного блоку визначення розрядів частки, починаючи з другого, з'єднаний з інформаційним виходом діленого попереднього блоку визначення розрядів частки, другий інформаційний вхід кожного наступного блоку визначення розрядів частки, починаючи з другого, з'єднаний з інформаційним виходом дільника попереднього блоку визначення розрядів частки, а інформаційні виходи розрядів частки всіх блоків визначення розрядів частки є розрядними виходами пристрою. Вузол затримки містить чотири D-тригери, входи встановлення в нуль котрих з'єднані зі входом встановлення вузла, тактові входи першого, другого і третього D-тригерів з'єднані зі входом синхронізації вузла, інформаційний вхід третього D-тригера з'єднаний з прямим виходом другого D-тригера, інформаційний вхід другого D-тригера з'єднаний з прямим виходом першого Dтригера, інформаційний вхід котрого є інформаційним входом вузла, інформаційний вхід четвертого D-тригера з'єднаний з шиною логічної одиниці, тактовий вхід четвертого D-тригера з'єднаний з прямим виходом третього D-тригера, прямий вихід четвертого D-тригера є інформаційним виходом вузла. Пристрій дозволяє одночасно виконувати 5494 ділення декількох пар операндів поданих кодами золотої пропорції. Недоліком пристрою є велика кількість входів і виходів, що зростає із збільшенням розрядності операндів. Наприклад, при діленні 32-розрядних кодів золотої пропорції пристрій матиме 66 входів і 32 виходи. Велика кількість входів і виходів ускладнює використання пристрою при розподіленій обробці даних, оскільки потребує значних витрат обладнання для організації інформаційних зв'язків. В основу корисної моделі поставлено задачу створення пристрою для ділення кодів золотої пропорції, в якому за рахунок введення нових елементів та зв'язків досягається зменшення кількості входів і виходів пристрою без зниження швидкодії його роботи. Це, в свою чергу, призводить до підвищення продуктивності розподіленої обробки завдяки можливості більшого розпаралелювання обчислень. Запропонований пристрій незалежно від розрядності матиме тільки чотири входи та два виходи. Таким чином при діленні 32розрядних чисел запропонований пристрій матиме у 16 разів меншу кількість входів та виходів ніж прототип, що і визначає позитивний ефект. Поставлена задача досягається тим, що в пристрій для ділення кодів золотої пропорції, який містить тактовий вхід, вхід діленого, вхід дільника, та п блоків визначення розряду частки (де п - розрядність операндів), кожен з яких містить тактовий вхід, вхід діленого, вхід дільника, вихід діленого, вихід дільника вихід частки, перший, другий і третій вузли затримки, віднімач, перший елемент АБО, перший D-тригер та комутатор, причому, тактовий вхід пристрою з'єднаний з тактовими входами всіх блоків визначення розряду частки, вихід діленого кожного блоку визначення розряду частки, крім п-го, з'єднаний зі входом діленого наступного блоку визначення розряду частки, вихід дільника кожного блоку визначення розряду частки, крім п-го, з'єднаний зі входом дільника наступного блоку визначення розряду частки, а в кожному блоці визначення розряду частки тактовий вхід блоку з'єднаний з тактовими входами першого, другого і третього вузлів затримки та віднімача, вхід встановлення в нульовий стан віднімача з'єднаний зі входом встановлення в нульовий стан першого D-тригера, вхід діленого блоку з'єднаний з інформаційним входом першого вузла затримки та входом зменшуваного віднімача, вхід дільника з'єднаний з інформаційним входом другого вузла затримки та входом від'ємника віднімача, інформаційний вихід віднімача з'єднаний з першим інформаційним входом комутатора, вихід першого вузла затримки з'єднаний з другим інформаційним входом комутатора, знаковий вихід віднімача з'єднаний з інформаційними входом D першого Dтригера, прямий вихід якого з'єднаний з керуючим входом комутатора, вихід якого є виходом діленого блоку, додатково введено вхід синхронізації початку числа, вихід синхронізації початку числа та вихід частки, а в кожному блоці визначення розряду частки додатково введено вхід частки, вхід синхронізації початку числа, вихід синхронізації початку числа, четвертий вузол затримки, другий, третій, четвертий і п'ятий D-тригери, другий і третій елементи АБО та елемент І, причому, вхід діленого пристрою з'єднаний зі входом ділечою першого блоку визначення розряду частки, вхід дільника пристрою з'єднаний зі входом дільника першого блоку визначення розряду частки, вхід частки першого блоку визначення розряду частки з'єднаний з шиною логічного нуля, вихід частки кожного блоку визначення розряду частки, крім пго, з'єднаний зі входом частки наступного блоку, вихід частки п-го блоку визначення розряду частки з'єднаний з виходом частки пристрою, вхід синхронізації початку числа пристрою з'єднаний зі входом синхронізації початку числа першого блоку визначення розряду частки, вихід синхронізації початку числа кожного блоку визначення розряду частки, крім п-го, з'єднаний зі входом синхронізації початку числа наступного блоку визначення розряду частки, вихід синхронізації початку числа п-го блоку визначення розряду частки з'єднаний з виходом синхронізації початку числа пристрою, а в кожному блоці визначення розряду частки тактовий вхід блоку з'єднаний з тактовими входами четвертого вузла затримки і четвертого та п'ятого Dтригерів, вхід частки блоку з'єднаний з інформаційним входом третього вузла затримки, вхід синхронізації початку числа з'єднаний з інформаційним входом четвертого вузла затримки і входами встановлення в нульовий стан першого, другого, третього і четвертого D-тригерів та першим входом другого елемента АБО, інформаційний вихід першого вузла затримки з'єднаний з першим входом першого елемента АБО, інформаційний вихід другого вузла затримки з'єднаний з тактовим входом третього D-тригера, інформаційними входом п'ятого D-тригера та другим входом першого елемента АБО, вихід якого з'єднаний з тактовим входом другого D-тригера, інформаційний вхід якого з'єднаний з шиною логічної одиниці, а вихід з'єднаний з тактовим входом першого D-тригера, інверсний вихід якого з'єднаний з першим входом елемента І, прямий вихід п'ятого D-тригера є виходом дільника блоку, інформаційний вхід третього D-тригера з'єднаний з шиною логічної одиниці, а вихід з'єднаний з другим входом елемента І та інформаційними входом четвертого D-тригера, інверсний вихід якого з'єднаний з третім входом елемента І, вихід якого з'єднаний з першим входом третього елемента АБО, вихід третього вузла затримки з'єднаний з другим входом третього елемента АБО, вихід якого є виходом частки блоку, вихід четвертого вузла затримки є виходом синхронізації початку числа блоку та з'єднаний з другим входом другого елемента АБО, вихід якого з'єднаний зі входом встановлення в нульовий стан п'ятого D-тригера. На Фіг.1 представлено схему пристрою. На Фіг.2 представлено діаграму формування коду частки при діленні восьмирозрядних послідовних кодів. На Фіг.З представлено часову діаграму подачі вхідних сигналів на пристрій. На Фіг.4 представлено часову діаграму вхідних і вихідних сигналів першого блоку 5.1 визначення розряду частки. На Фіг.5 представлено часову діаграму вхідних 5494 і вихідних сигналів другого блоку 5.2 визначення розряду частки. На Фіг.6 представлено часову діаграму вхідних і вихідних сигналів третього блоку 5.3 визначення розряду частки. На Фіг.7 представлено часову діаграму вхідних і вихідних сигналів четвертого блоку 5.4 визначення розряду частки. На Фіг.8 представлено часову діаграму вхідних і вихідних кодів блоків 5 визначення розряду частки. На Фіг.9. представлено приклад виконання обчислень у першому блоці 5.1 визначення розряду частки. На Фіг. 10. представлено приклад виконання обчислень у другому блоці 5.2 визначення розряду частки. На Фіг. 11. представлено приклад виконання обчислень у третьому блоці 5.3 визначення розряду частки. На Фіг. 12. представлено приклад виконання обчислень у четвертому блоці 5.4 визначення розряду частки. На Фіг. 13. представлено приклад виконання обчислень у п'ятому блоці 5.5 визначення розряду частки. На Фіг. 14. представлено приклад виконання обчислень у шостому блоці 5.6 визначення розряду частки. На Фіг. 15. представлено приклад виконання обчислень у сьомому блоці 5.7 визначення розряду частки. На Фіг. 16. представлено приклад виконання обчислень у восьмому блоці 5.8 визначення розряду частки. Пристрій для ділення послідовних кодів золотої пропорції (Фіг. 1) містіть тактовий вхід 1, вхід 2 діленого, вхід 3 дільника, вхід 4 синхронізації початку числа, п блоків 5.1, 5.2,...,5.п визначення розряду частки (де п - розрядність операндів), вихід 6 частки та вихід 7 синхронізації початку числа, а кожен блок 5 визначення розряду частки містить тактовий вхід 8, вхід 9 діленого, вхід 10 дільника, вхід 11 частки, вхід 12 синхронізації початку числа, вихід 13 діленого, вихід 14 дільника, вихід 15 частки, вихід 16 синхронізації початку числа, віднімач 17, перший вузол 18 затримки, другий D-тригер 19, другий вузол 20 затримки, третій D-тригер 21, третій 22 вузол затримки, четвертий вузол 23 затримки, перший D-тригер 24, перший елемент 25 АБО, другий елемент 26 АБО, четвертий D-тригер 27, комутатор 28, п'ятий D-тригер 29, елемент 1 ЗО та третій елемент 31 АБО, причому тактовий вхід 1 пристрою з'єднаний з тактовими входами 8 всіх блоків 5 визначення розряду частки, вхід 2 діленого пристрою з'єднаний зі входом 9 діленого першого блоку 5 визначення розряду частки, вхід 3 дільника пристрою з'єднаний зі входом 10 дільника першого блоку визначення розряду частки, вхід 11 частки першого блоку 5 визначення розряду частки з'єднаний з шиною логічного нуля, вхід 4 синхронізації початку числа пристрою з'єднаний зі входом 12 синхронізації початку числа першого блоку 5 визначення розряду частки, вихід 13 діленого кожного блоку 5 визначення розряду частки, 8 крім п-го, з'єднаний зі входом 9 діленого наступного блоку 5 визначення розряду частки, вихід 14 дільника кожного блоку 5 визначення розряду частки, крім п-го, з'єднаний зі входом 10 дільника наступного блоку 5 визначення розряду частки, вихід 15 частки кожного блоку 5 визначення розряду частки, крім п-го, з'єднаний зі входом 11 частки наступного блоку 5 визначення розряду частки, вихід 15 частки п-го блоку 5 визначення розряду частки з'єднаний з виходом 6 частки пристрою, вихід 16 синхронізації початку числа кожного блоку 5 визначення розряду частки, крім п-го, з'єднаний зі входом 12 синхронізації початку числа наступного блоку 5 визначення розряду частки, вихід 16 синхронізації початку числа п-го блоку 5 визначення розряду частки з'єднаний з виходом 7 синхронізації початку числа пристрою, а в кожному блоці 5 визначення розряду частки тактовий вхід 8 блоку з'єднаний з тактовими входами С першого вузла 18 затримки, другого вузла 20 затримки, третього вузла 22 затримки, четвертого вузла 23 затримки, четвертого D-тригера 26, п'ятого D-тригера 28 та віднімача 17, вхід 9 діленого блоку з'єднаний з інформаційним входом D першого вузла 18 затримки та входом А зменшуваного віднімача 17, вхід 10 дільника блоку з'єднаний з інформаційним входом D другого вузла 20 затримки та входом В від'ємника віднімача 17, вхід 11 частки блоку з'єднаний з інформаційним входом D третього вузла 22 затримки, вхід 12 синхронізації початку числа блоку з'єднаний з інформаційним входом D четвертого вузла 23 затримки, першим входом другого елемента 26 АБО і входами R встановлення в нульовий стан першого 24, другого 19, третього 21, четвертого 27 D-тригерів та віднімача 17, інформаційний вихід S віднімача 17 з'єднаний з першим інформаційним входом А комутатора 28, вихід першого вузла 18 затримки з'єднаний з другим інформаційним входом В комутатора 28 та з першим входом першого елемента 25 АБО, знаковий вихід Р віднімача 17 з'єднаний з інформаційними входом D першого D-тригера 24, інформаційний вихід другого вузла 20 затримки з'єднаний з тактовим входом С третього D-тригера 21, інформаційними входом D п'ятого D-тригера 29 та другим входом першого елемента 25 АБО, вихід якого з'єднаний з тактовим входом С другого D-тригера 19, інформаційний вхід D якого з'єднаний з шиною логічної одиниці, а прямий вихід з'єднаний з тактовим входом С першого D-тригера 24, прямий вихід якого з'єднаний з керуючим входом V комутатора 28, а інверсний вихід з'єднаний з першим входом елемента ЗО І, прямий вихід п'ятого D-тригера 29 є виходом 14 дільника блоку, інформаційний вхід D третього D-тригера 21 з'єднаний з шиною логічної одиниці, а вихід з'єднаний з другим входом елемента ЗО 1 та інформаційними входом D четвертого D-тригера 27, інверсний вихід якого з'єднаний з третім входом елемента ЗО 1, вихід якого з'єднаний з першим входом третього елемента 31 АБО, вихід третього вузла 22 затримки з'єднаний з другим входом другого елемента 31 АБО, вихід якого є виходом 15 частки блоку, вихід четвертого вузла 23 затримки є виходом 16 синхронізації початку числа блоку та з'єднаний з другим входом другого 5494 елемента 26 АБО, вихід якого з'єднаний зі входом встановлення в нульовий стан п'ятого D-тригера 29. Кожен вузол затримки являє собою відомий чотирьох-розрядний регістр зсуву з послідовним занесенням інформації, реалізований на Dтригерах. Віднімач являє собою відомий пристрій, у якому вхід знаку першого операнду з'єднаний з шиною логічного нуля, а вхід знаку другого операнду з'єднаний з шиною логічної одиниці. Пристрій працює таким чином. Сигнал встановлення у початковий стан пристрою за допомогою першого елемента АБО встановлює у початковий стан усі тригери пристрою. Поступаючи на вхід першого елемента АБО, сигнал синхронізації початку числа встановлює у початкове значення усі тригери блоку визначення розряду частки, крім тригерів другого вузла затримки на чотири такти. Використовуючи другий вузол затримки на чотири такти, сигнал синхронізації початку числа просувається синхронно з кодами операндів по блокам визначення розряду частки, що позбавляє необхідності використання блоку керування для синхронізації операндів. У кожному блоці визначення розряду частки послідовні коди операндів поступають, починаючи зі старших розрядів на віднімач і далі на комутатор, де формується різниця між остачею від попереднього віднімання та зсунутим у попередньому блоці на один розряд вправо дільником. Сигнал з виходу першого D-тригера в залежності від знаку віднімання комутує на вихід дільника код з виходу віднімача, або затриманий код, що поступає на вхід дільника даного блоку визначення розряду частки. Його фіксація на весь час проходження коду через комутатор виконується сигналом з виходу другого вузла затримки на чотири такти. Цей сигнал і є відповідним розрядом частки. З нього за допомогою елементу 1 та другого D-тригера виконується формування сигналу розряду частки довжиною в один тактовий імпульс. Послідовний код частки отримується шляхом об'єднання другим елементом АБО у кожному блоці формування розряду частки сигналу з виходу елементу 1 даного блоку з сигналом сусіднього старшого коду частки, отриманого на виході попереднього блоку визначення розряду частки та затриманого за допомогою третього вузла затримки на чотири такти. На Фіг.2 представлено діаграму формування коду частки при діленні восьмирозрядних послідовних кодів. Перед початком роботи віднімач 17, перший вузол 18 затримки, другий вузол 20 затримки, третій вузол 22 затримки, четвертий вузол 23 затримки перший D-тригер 24, другий D-тригер 19, третій D-тригер 21, четвертий D-тригер 26 та п'ятий Dтригер 28 знаходяться у невизначеному стані. Тактові імпульси поступають на тактовий вхід 1 пристрою. Після включення пристрою на входи 2 діленого, 3 дільника та 4 синхронізації початку числа пристрою подаються нульові сигнали. Нульові сигнали поступають на інформаційні входи D першого 18, другого 20, третього 22 та четвертого 23 вузлів затримки та на інформаційні входи віднімача 17. Через чотири такти всі тригери вузлів 18, 20, 22, 23 затримки та віднімача 17 встановлюються в 10 нульовий стан. Нульовий сигнал поступає з прямого виходу третього D-тригера 21 на вхід елемента ЗО 1, на виході якого встановлюється нульовий сигнал. Нульовий сигнал з виходу другого вузла 20 затримки поступає на інформаційний вхід D п'ятого Ь-тригера 29. Нульові сигнали з інформаційного виходу S віднімача 17 та з виходу першого вузла 18 затримки поступають на інформаційні входи комутатора 28, на виході якого встановлюється нульовий сигнал. Нульовий сигнал з виходу другого вузла 20 затримки поступає на інформаційний вхід D п'ятого D-тригера 29. На п'ятому такті п'ятий D-тригер 29 встановлюється в нульовий стан. Нульові сигнали з виходів 13, 14, 15, 16 першого блоку 5.1 визначення розряду частки поступають відповідно на входи 9, 10, 11, 12 другого блоку 5.2 визначення розряду частки. Через (5*п) тактів, де п - розрядність операндів, пристрій знаходиться у початковому стані. Робота пристрою починається з того, що на вхід 2 діленого і вхід 3 дільника пристрою, починаючи зі старших розрядів, подаються послідовні коди діленого і дільника, доповнені трьома молодшими нульовими розрядами. Зна-у чення кожного розряду коду встановлюється з переходом з нульового рівня в одиничний на тактовому вході 8. Одночасно з подачею старших розрядів кодів діленою і дільника та подачею одиничного рівня тактового імпульсу на вхід 4 синхронізації початку числа подається одиничний імпульс (Фіг.З). Коди діленого і дільника є приведеними, тобто код дільника у старшому розряді має одиницю. Розглянемо роботу першого блоку 5.1 визначення розряду частки. При ввімкненні пристрою на вхід 11 частки блоку поступає нульовий сигнал з шини логічного нуля. Нульові сигнали зі входів 2 діленого, 3 дільника те 4 синхронізації початку числа пристрою поступають відповідно на входи 9 діленого, 10 дільника та 11 синхронізації початку числа блоку. Тактові імпульси з тактового входу 8 блоку поступають тактові на входи С віднімача 17, першого 18, другого 20, третього 22 та четвертого 23 вузлів затримки і четвертого 26 та п'ятого 29 Dтригерів, синхронізуючи зміну їх стану переходом з нульового рівня в одиничний. Через чотири такти після ввімкнення пристрою всі вузли затримки встановлюються в нульовий стан. З початком роботи пристрою у першому такті старший розряд коду діленого зі входу діленого 9 блоку поступає на перший вхід А зменшуваного віднімача 17 та інформаційний вхід першого вузла затримки 18. Старший розряд коду дільника зі входу 10 дільника блоку поступає на вхід В від'ємника віднімача 17 та інформаційний вхід другого вузла затримки 20. Одиничний сигнал з шини логічної одиниці поступає на інформаційні входи D другого 19 та третього 21 D-тригерів. Нульовий сигнал зі входу 11 частки блоку поступає на інформаційний вхід D третього вузла 22 затримки. У першій половині першого такту одиничний імпульс зі входу 12 синхронізації початку числа поступає на інформаційний вхід D четвертого вузла 23 затримки та входи R встановлення в нульовий стан першого 24, другого 19, третього 21, четвертого 26, п'ятого 29 Dтригерів та віднімача 17. Перший 24, другий 19, 11 третій 21, четвертий 26, п'ятий 28 D-тригери та віднімач 17 встановлюються в нульовий стан У четвертому такті на знаковому виході Р віднімача 17 встановлюється знак різниці діленого і дільника Додатному знаку відповідає нуль, а від'ємному знаку відповідає одиниця Сигнал зі знакового виходу Р віднімача 17 поступає на інформаційний вхід D першого D-тригера 24 У п'ятому такті одиничний сигнал з виходу другого вузла 20 затримки поступає на другий вхід першого елемента 25 АБО, інформаційний вхід D п'ятого D-тригера 28 і тактовий вхід С третього D-тригера 21 3 виходу першого елемента 25 АБО одиничний сигнал поступає на тактовий вхід С другого D-тригера 19 Другий D-тригер 19 встановлюється в одиничний стан Одиничний сигнал з прямого виходу другого D-тригера 19 поступає на тактовий вхід С першого D-тригера 24 Перший D-тригер 24 встановлюється в стан ВІДПОВІДНО знаку різниці діленого та дільника На інформаційному виході S віднімача 17 значення старшого розряду різниці На інформаційному виході першого вузла 18 затримки значення старшого розряду діленого Сигнал знаку різниці з прямого виходу першого D-тригера 24 поступає на керуючий вхід V комутатора 28 При нульовому сигналі на керуючому вході V комутатор 27 передає на вихід сигнал зі входу А, при одиничному - сигнал зі входу В При від'ємному знаку різниці діленого і дільника з виходу комутатора 28 подається затриманий код діленого, а при додатному - затриманий код різниці діленого та дільника Сигнал, обернений знаку різниці поступає з інверсного виходу першого D-тригера 24 на перший вхід елемента ЗО І Третій D-тригер 21 встановлюється в одиничний стан Одиничний сигнал з прямого виходу третього D-тригера 21 поступає другий вхід елемента ЗО І та інформаційний вхід D четвертого D-тригера Одиничний сигнал з інверсного виходу четвертого D-тригера 27 поступає на третій вхід елемента ЗО 1 На виході елемента ЗО І сигнал, що дорівнює значенню старшого розряду частки Значення розряду частки з виходу елемента 29 І поступає на перший вхід третього елемента 31 АБО Нульовий сигнал з виходу третього вузла 22 затримки поступає на другий вхід третього елемента 31 АБО Сигнал, що дорівнює значенню даного розряду частки, поступає з виходу третього елемента 31 АБО на вихід 15 частки блоку Одиничний імпульс довжиною половини такту з виходу четвертого вузла 23 затримки поступає на вихід 16 синхронізації початку числа блоку У шостому такті четвертий D-тригер 27 встановлюється в одиничний стан Нульовий сигнал з інверсного виходу четвертого D-тригера 27 поступає на третій вхід елемента ЗО І Нульовий сигнал з виходу елемента ЗО І поступає на перший вхід третього елемента 31 АБО Нульовий сигнал з виходу третього елемента 31 АБО поступає на вихід 15 частки блоку Пятий D-тригер 29 встановлюється в стан, що дорівнює значенню старшого розряду дільника Сигнал, що дорівнює значенню старшого розряду дільника, поступає з 5494 12 виходу п'ятого D-тригера 29 на вихід 14 діленого блоку Часова діаграма вхідних і вихідних сигналів першого блоку 5 1 визначення розряду частки представлена на Фіг 4 Наступний сигнал синхронізації початку числа через другий елемент 26 АБО поступає на вхід R встановлення в нульовий стан D-тригера 29 D-тригер 29 встановлюється в нульовий стан Це призводить до обнуління молодшого розряду коду дільника, що подається на наступний блок визначення розряду частки Робота інших блоків 5 визначення розряду частки відрізняється тим, що у кожному з них на вхід 10 дільника блоку поступає послідовний код дільника, затриманий відносно коду діленого на (п-1) тактів, де п - номер блоку Часові діаграми вхідних і вихідних сигналів другого 5 2, третього 5 3 та четвертого 5 4 блоків визначення розряду частки представлені ВІДПОВІДНО на Фіг 5, Фіг 6 та Фіг 7 На Фіг 8 представлена часова діаграма сигналів на входах 9 діленого, 10 дільника 12 синхронізації початку числа та виході 15 частки блоків 5 визначення розряду частки при конвеєрному виконанні ділення восьми розрядних послідовних кодів золотої пропорції Розглянемо роботу пристрою на прикладі Нехайна пристрій, що містить ВІСІМ блоків 5 визначення розряду частки подаються, починаючи зі старших розрядів, восьмирозрядні ПОСЛІДОВНІ КОДИ операндів На вхід 3 діленого подається код 100011000000, а на вхід 4 дільника подається код 111000000000 Ці КОДИ поступають на входи ВІДПОВІДНО 9 діленого та 10 дільника першого блоку 5 1 визначення розряду частки Починаючи з першого такту після встановлення пристрою в початковий стан, у першому блоці 5 1 визначення розряду частки виконується віднімання коду 111000000000 від коду 100011000000 (Фіг 9) На третьому такті встановлюється нульовий сигнал на знаковому виході Р віднімача 17, який запам'ятовується у першому D-тригері 24 Тому на виході комутатора 28 буде затриманий на чотири такти код 100011000000 Цей код, починаючи з п'ятого такту поступає на вхід 9 діленого другого блоку 5 2 визначення розряду частки, на вхід 10, якого поступає затриманий на п'ять тактів код дільника (Фіг 10) На сьомому такті встановлюється нульовий сигнал на знаковому виході Р віднімача 17 цього блоку, який запам'ятовується у першому Dтригері 24 цього блоку Тому на виході комутатора 28 цього блоку буде затриманий на чотири такти код 100011000000 Цей код, починаючи з дев'ятого такту поступає на вхід 9 діленого другого блоку 5 З визначення розряду частки, на вхід 10, якого поступає затриманий на п'ять тактів код дільника (Фіг 11) На одинадцятому такті встановлюється одиничний сигнал на знаковому виході Р віднімача 17 цього блоку, який запам'ятовується у першому D-тригері 24 цього блоку Тому на виході комутатора 28 цього блоку буде код 000110101100 різниці діленого та дільника Робота інших блоків 5 визначення розряду частки при виконанні даного прикладу представлена на Фіг 12 - Фіг 16 Z'-ЧФ н 15 5484 1 2 16 З ^О< 15 п 16 л із 14 ^хххх ^ ^ ^ 15 16 л Фіг. 5 п SI П П £1 91 и z\ it oi б 5494 19 20 JTUXJ\JXTiriJTJTJTSXSlJXriT\Tiririr\JXr^ 56 5? 3.8 Фіг. 8 № такту S.1 6 ? 1 2 8 9 10 11 12 1 0 0 0 1 1 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 OlIO 0 1 1 0 0 (о 0 1; Io 0 x x x x x x x x x x s c x 1 0 0 0 1 1 0 0 0 0 0 0 Фіг. 9 5.2 5 & 7 8 9 10 11 12 13 14 15 16 1 0 0 0 1 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 10 0 0 GO» о о oTo о x x x x x x x x x x x x 1 0 0 0 1 1 0 O O 0 0 O Фіг. 10 53 . S 10 11 12 13 14 15 16 17 16 10 20 0 + 1 + 1 0 0 0 1 1 0 0 0 0 0 0 0 0 f JL JL 0 0 0 0 0 0 0 л 'o "o JLLi 0 0 і 0 0 0 0 0 0 0 0 0 0 0 0 JLJ JL 0 JL 0 1 JL 9» 0 0 0 0 JL о 0 0 0 0 0 0 0 0 0 0 0 0 'і 1 1 1 1 1 0 T oTcT 0 і 0 0 0 і 0 1 1 0 1 0 1 I 0 1 0 1 0 1 1 0 1 0 1 Фіг. 11 0 0 0 1 1 0 0 0 0 |0 0 0 oh о И МІ V I О О О О О х х х х х х х х х х х х 1° 0 ©Зо 0 0 0 0 0 0 °р 0 0 0 0 0 0 0 0 0 0 0 ; і. о 0 0 0 0 0 [0 0 0 0 0 0 0 0| 0 о! о О О 0 0 |0 0 0 0| 0 + |о 0 0 + OOOOI- I * 0 0 0 0 0 . O O t L O t ^ t - 0 0 0 0 0 OS Ж Ш LZ 93 9Z PZ £Z ZZ iZ £1 ' 0 0 0 0 0 0 0 0 0 0 0 V 0 0 0 V і Q 0 1 0 0 і 0 0 і. і- і і і і І 0 0 0 0 0 0 0 0 0 І % 0 0 0 0 0 jo 0 І- 0 0 0 0 0 0 1 0 0 Q 0 0 0 0 0 0 0 п 0 0 0 0 0 0 0 і і 0 0 1 1 і 0 0 0 ^ 0 1 те ZZ іг V 1! 0 + 0 0 й 0 0 £} 0 D п 1 0 0 8Z ZZ9Z 0 0 0 0 0 0 0 0 0 0 0 0 0 Q 0 + 0 • + 0 0 0 0 61 8І- IV ss і і G I 0 t і О ОО X X X X X X X X 0 0 0 о! 0 K 0 0 0 0 0 0 0 0 0 II vz zz zz iz Г2 iv и X X 0 й 0 0 0 X 0 0 0 0 0 0 0 0 0 0 0 0 0 1 . 0 0 0 1 - 0 0 0 n т 1 % ш І 5494 23 Мйтжоу 0 0 0 0 0 0 1 24 5.7 26 26 27 26 29 ЗО 31 32 33 34 35 36 0 0 0 0 0 1 1 01 1 0 0 О О О О О О 1 1 1 0 0 0 + + + + + + + 0 0 0 0 0 0 0 0 0 0 0 0 Т] + о 0 0 0 0 0 0 0 0 0 0 0 0 І0 0 0 0 0 0 0 0 0 0 0 jo 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 %* 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 !о 0 0 1 1 1 0 0 1 1 1 0 0 1 1 1 0 0 0 0 0 0 0 0 |0 0 Фіг. 15 5.8 29 ЗО 31 32 33 34 35 36 37 38 33 40 0 0 0 й 0 0 0 + + + + + + + о + о + + я Комп'ютерна верстка А. Крулевський 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 1 1 1 0 0 0 о 0 0 0 0 0 JL JL 0 о]JL 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 oi 0 0 0 0 0 0 0 0 0 0 0I0 0 Фіг. 16 Підписне Тираж 28 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м Київ, МСП, 03680, Україна ДП "Український інститут промислової власності", вул. Глазунова, 1, м. Київ-42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for dividing serial code numbers according to the golden section

Автори англійськоюAzarov Oleksii Dmytrovych

Назва патенту російськоюУстройство для деления чисел в последовательном коде в соответствии с золотым сечением

Автори російськоюАзаров Алексей Дмитриевич

МПК / Мітки

МПК: G06F 7/535, G06F 7/49

Мітки: послідовних, кодів, пристрій, ділення, золотої, пропорції

Код посилання

<a href="https://ua.patents.su/12-5494-pristrijj-dlya-dilennya-poslidovnikh-kodiv-zoloto-proporci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для ділення послідовних кодів золотої пропорції</a>

Попередній патент: Спосіб відновлення працездатності циліндричних охоплюваних деталей зі зношеними зовнішніми посадковими поверхнями

Наступний патент: Спосіб паралельного алгебраїчного додавання тривалостей групи часових інтервалів

Випадковий патент: Спосіб фазової диференціальної діагностики патології шлунка