Пристрій для моделювання нейрона

Номер патенту: 95067

Опубліковано: 10.12.2014

Автори: Мартинюк Тетяна Борисівна, Колісник Петро Федорович, Кожем'яко Андрій Вікторович, Васильківа Олена Сергіївна

Формула / Реферат

Пристрій для моделювання нейрона, який містить n блоківзміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, комутатор, причому установний вхід пристрою з'єднаний з відповідним входом n блоків зміни синаптичних ваг, вхід порога, адресний і перший керуючий входи пристрою з'єднані з відповідними входами суматора, перший і другий виходи суматора з'єднані з інформаційними входами комутатора, вихід комутатора є інформаційним виходом результату пристрою, вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою, який відрізняється тим, що в нього введено логічний блок, перший і другий входи якого з'єднані з другим і третім керуючими входами пристрою, вихід результуючого сигналу суматора підключений до третього інформаційного входу комутатора і третього входу логічного блока, вихід якого з'єднаний з керуючим входом комутатора.

Текст

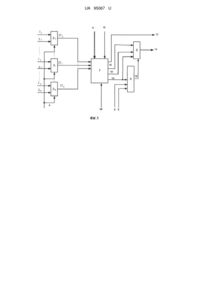

Реферат: Пристрій для моделювання нейрона містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, комутатор. Установний вхід пристрою з'єднаний з відповідним входом n блоків зміни синаптичних ваг, вхід порога, адресний і перший керуючий входи пристрою з'єднані з відповідними входами суматора. Перший і другий виходи суматора з'єднані з інформаційними входами комутатора. Вихід комутатора є інформаційним виходом результату пристрою. Вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою. Пристрій містить логічний блок, перший і другий входи якого з'єднані з другим і третім керуючими входами пристрою. Вихід результуючого сигналу суматора підключений до третього інформаційного входу комутатора і третього входу логічного блока, вихід якого з'єднаний з керуючим входом комутатора. UA 95067 U (12) UA 95067 U UA 95067 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до області біоніки та обчислювальної техніки і може бути використана як елемент нейроподібних мереж для моделювання біологічних процесів у пристроях оброблення, аналізу і розпізнавання образів, а також як елемент паралельних обчислювальних структур для вирішення задач цифрового оброблення сигналів, систем алгебраїчних рівнянь, крайових задач теорії поля. Відомий пристрій для моделювання нейрона (а.с. СРСР № 1479944, кл. G06G7/60, 1989 р., Бюл. 18), який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, а треті є установними, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, перший і другий регістри, перший і другий елементи 1 та логічний блок, при цьому вихід першого регістра з'єднаний з (n+1) входом суматора, а вхід - через перший вхід першого елемента І підключений до виходу суматора, який зв'язаний через перший вхід другого елемента І з входом другого регістра і першим входом логічного блока, до другого входу якого підключений вихід другого регістра. Недоліком даного пристрою є його обмежені функціональні можливості через відсутність моделювання формального нейрона у режимі з лінійною з насиченням функцією активації. За прототип вибраний пристрій для моделювання нейрона (патент України 38491, кл. G 06 G7/00, 2009р., Бюл. № 1), який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, комутатор і елемент НЕРІВНОЗНАЧНОСТІ, причому установний вхід пристрою з'єднаний з відповідним входом n блоків зміни синаптичних ваг, вхід порога, адресний і перший керуючий входи пристрою з'єднані з відповідними входами суматора, перший і другий виходи суматора з'єднані з інформаційними входами комутатора, другий вихід суматора з'єднаний також з першим входом елемента НЕРІВНОЗНАЧНОСТІ, вихід якого з'єднаний з керуючим входом комутатора, вихід якого є інформаційним виходом результату пристрою, вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою, другий і третій керуючі входи пристрою з'єднані з відповідними входами елемента НЕРІВНОЗНАЧНОСТІ. Недоліком прототипу є його обмежені функціональні можливості через відсутність моделювання формального нейрона у режимі з лінійною з насиченням функцією активації. В основу корисної моделі поставлено задачу створення пристрою для моделювання нейрона, в якому введення нових вузлів та зв'язків дозволяє розширити його функціональні можливості за рахунок реалізації режиму формального нейрона з лінійною з насиченням функцією активації. Поставлена задача вирішується тим, що у пристрій для моделювання нейрона, який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, комутатор, причому установний вхід пристрою з'єднаний з відповідним входом n блоків зміни синаптичних ваг, вхід порога, адресний і перший керуючий входи пристрою з'єднані з відповідними входами суматора, перший і другий виходи суматора з'єднані з інформаційними входами комутатора, вихід комутатора є інформаційним виходом результату пристрою, вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою, введено логічний блок, перший і другий входи якого з'єднані з другим і третім керуючими входами пристрою, вихід результуючого сигналу суматора підключений до третього інформаційного входу комутатора і третього входу логічного блока, вихід якого з'єднаний з керуючим входом комутатора. На Фіг. 1 приведено структурну схему пристрою для моделювання нейрона; на Фіг. 2 структурну схему суматора. Пристрій для моделювання нейрона (Фіг. 1) містить дві групи інформаційних входів 1 1,…,1n і 21….,2n пристрою, n блоків 31,…,3n зміни синаптичних ваг, установний вхід 4 і керуючі входи 5, 6 пристрою, суматор 7, логічний блок 8, комутатор 9, інформаційний вихід 10 суматора 7, вхід 11 порога, керуючий вхід 12, вихід 13 сигналу "Кінець", вихід 14 результату і вихід 15 результуючого сигналу суматора 7, адресний вхід 16 пристрою. Групи інформаційних входів 11,…,1n і 21,…,2n, пристрою підключені відповідно до першого і другого входів блоків 3 1,…,3n зміни синаптичних ваг, третій вхід яких з'єднаний відповідно з установним входом 4 пристрою. Група виходів 171,…,17n блоків 31,…,3n зміни синаптичних ваг підключена до n входів суматора 7, вихід ознаки нуля якого з'єднаний з виходом 13 сигналу "Кінець" пристрою. Перший інформаційний вхід комутатора 9 з'єднаний з виходом 10 суматора 7, три входи логічного блока 8 з'єднані відповідно з виходом 15 результуючого сигналу суматора 7 і керуючими входами 5 і 6 пристрою. Адресний вхід 16 пристрою з'єднаний з відповідним входом суматора 7, вихід 15 результуючого сигналу якого з'єднаний з третім інформаційним входом комутатора 9. Вхід 11 порога і керуючий вхід 12 пристрою з'єднані з відповідними входами суматора 7, інформаційний вихід комутатора 9 є виходом 14 результату пристрою. Вихід 18 суматора 7 з'єднаний з другим 1 UA 95067 U 5 10 15 20 25 30 35 40 45 інформаційним входом комутатора 9, керуючий вхід якого з'єднаний з виходом 19 логічного блока 8. Суматор 7 (Фіг. 2) містить комірку 20 і n комірок 21, причому і-та комірка 21 містить мультиплексор 22, регістр 23, суматор-віднімач 24, суматор 25, D-тригер 26, мініматор 27, два регістри 28, 29, комутатор 30. Перший інформаційний вхід мультиплексора 22 з'єднаний з входом 17 і-ої комірки 21, керуючий вхід з'єднаний з адресним входом 16 пристрою, а його вихід підключено до входу 31 регістра 23, в якого вихід з'єднаний з прямим входом 32 суматоравіднімача 24 та інформаційним входом 33 мініматора 27. Вихід регістра 29 з'єднаний з інформаційним входом комутатора 30 та інверсним входом 34 суматора-віднімача 24, вихід 35 якого з'єднаний з другим інформаційним входом мультиплексора 22, а вихід 36 знака суматоравіднімача 24 з'єднаний зі знаковим входом 37 мініматора 27 і D-входом D-тригера 26, інверсний вихід якого з'єднаний з керуючим входом комутатора 30. Вихід комутатора 30 підключено до виходу 38 і-ої комірки 21, крім того, інформаційний вхід 39 мініматора 27 і-ої комірки 21 з'єднаний з виходом 40 (і-1)-ої комірки 21, вхід 41 суматора 25 i-ої комірки 21 з'єднаний з виходом 42 (і-1)-ої комірки 21, а вхід 43 підключено до виходу 38 (і+1)-ої комірки 21. В і-й комірці 21 вхід регістра 29 підключено до входу 44 цієї комірки 21, вихід 45 мініматора 27 з'єднаний з входом регістра 28 цієї комірки, інформаційний вихід якого є виходом 40 і-ої комірки 21, а його вихід знака є виходом 46 і-ої комірки 21, який з'єднаний зі знаковим входом 47 мініматора 27 (і+1)-ої комірки 21, вихід 45 мініматора 27 n-ої комірки 21 підключений до входів 44 всіх (n-1) молодших комірок 21. Перша комірка 21 не містить мiнiматор 27 та регістр 28, вихід її регістра 23 є виходом 40 першої комірки 21, вихід 36 знака суматора-віднімача 24 є її виходом 46, а вхід 41 суматора 25 з'єднаний з виходом комутатора 30 цієї ж комірки 21. Остання n-a комірка 21 містить регістр 48, вхід якого з'єднаний з виходом суматора 25 цієї комірки 21, а його вихід є інформаційним виходом 10 суматора 7 i з'єднаний також з входом 43 суматора 25 цієї ж комірки 21. Вихід 45 мініматора 27 n-ої комірки 21 з'єднаний з входом регістра 29 цієї комірки, а його вихід ознаки нуля з'єднаний з виходом 13 ознаки нуля суматора 7. Комірка 20 містить мультиплексор 22, регістр 23, суматор-віднімач 24, D-тригер 26, комутатор 30, елемент АБО 49, елемент І 50, комутатор 51 і регістр 52. Перший інформаційний вхід мультиплексора 22 комірки 20 з'єднаний з входом 11 порога пристрою, його керуючий вхід з'єднаний з адресним входом 16 пристрою. Вихід 42 (n-і)-ої комірки 21 з'єднаний з інформаційним входом комутатора 30, вихід регістра 48 n-ої комірки 21 з'єднаний з інформаційним входом комутатора 51 комірки 20, а керуючий вхід комутатора 30 з'єднаний з виходом елемента І 50, перший вхід якого з'єднаний з керуючим входом 12 пристрою, а другий вхід - з iнверсним виходом D-тригера 26 цієї комірки. Вихід комутатора 30 комірки 20 з'єднаний з інверсним входом 34 суматора-віднімача 24 цієї комірки, вихід 36 знака якого з'єднаний з першим входом елемента АБО 49, а вихід 54 ознаки нуля - з другим входом елемента АБО 49, вихід якого з'єднаний з D-входом D-тригера 26 комірки 20, прямий вихід якого є виходом 15 результуючого сигналу суматора 7. Вихід мультиплексора 22 комірки 20 підключено до входу 31 регістра 23 цієї комірки, в якого вихід з'єднаний з прямим входом 32 суматора-віднімача 24 цієї комірки, вихід 35 якого з'єднаний з другим інформаційним входом мультиплексора 22 цієї комірки. Інверсний вихід D-тригера 26 з'єднаний також з керуючим входом комутатора 51, інформаційний вихід якого підключений до входу 53 регістра 52, вихід якого є інформаційним виходом 18 суматора 7. Пристрій для моделювання нейрона (Фіг. 1) працює таким чином. У n блоках 31,…,3n зміни синаптичних ваг виконується формування зважених вхідних сигналів вигляду: ai x i i , i 1 n , , 50 (1) де xi , i - відповідно і-й вхідний сигнал та i-та синаптична вага. Зважені вхідні сигнали ai,…,аn з групи виходів 171,…,17n подаються на відповідні входи суматора 7 паралельно, де відбувається їх підсумовування з формуванням часткових сум Sj з подальшим їх накопиченням у вигляді: Sk k Sj . j 1 (2) 2 UA 95067 U Одночасно у суматорі 7 часткові суми S j порівнюються з порогом , що надходить зі входу 11, і формується значення поточного порога j на j-му етапі оброблення вигляду: j j 1 S j , j 1 N , , 5 10 (3) де 0 ; N - кількість етапів оброблення. При цьому, якщо j 0 , το на виході 15 результуючого сигналу суматора 7 буде незмінним нульовий сигнал ( Y1 0) . Якщо j 0 , то на виході 15 результуючого сигналу суматора 7 сформується одиничний сигнал ( Y1 1) і порогове оброблення припиняється. При пороговій функції активації на входи логічного блока 8 подаються такі сигнали: з входів 5 і 6 подаються відповідно одиничний і нульовий сигнали (табл. 1), результуючий сигнал Y1 з виходу 15 суматора 7, на установний вхід 4 - нульовий сигнал, на керуючий вхід 12 пристрою одиничний сигнал, на вхід 11 порога початкове значення порога . В результаті на виході 19 логічного блока 8 формується відповідний сигнал. Таким чином, при цьому режимі роботи на кожному j-му етапі пристрій реалізує функцію: 15 k 1 якщо Sk , , (4) Y1 sign x i i i 1 0, якщо Sk , що відповідає роботі формального нейрона з пороговою функцією активації. Отже, комутатор 9 на виході 14 буде видавати результуючий сигнал Y1 вигляду (4) з виходу 15 суматора 7. 20 Таблиця 1 Режими Формальний нейрон з пороговою функцією активації Формальний нейрон з лінійною функцією активації Формальний нейрон з лінійною з насиченням функцією активації Формувач скалярного добутку векторів Цифровий інтегратор 4 0 0 Керуючі входи 5 6 1 0 1 1 12 1 1 0 0 0 1 0 1 0 0 0 0 0 0 Для налаштування на режим формального нейрона з лінійною функцією активації вигляду: S , якщо 0 Sk , , Y2 k 0, якщо Sk 0 , 25 30 (5) на керуючі входи 5, 6, 12 пристрою необхідно подати одиничні сигнали, на установний вхід 4 - нульовий сигнал, а на вхід 11 порога - початкове значення порога . Іншими словами, на керуючі входи 4, 5, 6 і 12 подається код операції 0111 (табл.1). В результаті на два відповідні входи логічного блока 8 подаються одиничні сигнали, при цьому, якщо на виході 15 суматора 7 формується нульовий результуючий сигнал, який подається на вхід логічного блока 8, то на вихід 14 комутатора 9 проходить сигнал Y2 0 , в іншому випадку величина накопиченої суми Y2 Sk . У цих випадках на виході 19 логічного блока 8 формуються відповідні сигнали дозволу, які подаються на керуючий вхід комутатора 9. Для налаштування на режим формального нейрона з лінійною з насиченням функцією активації вигляду: 35 S, якщо Sk , Y3 Sk , якщо 0 Sk , 0, якщо Sk 0, (6) 3 UA 95067 U на керуючі входи 5 і 6 пристрою необхідно подати нульові сигнали, на керуючий вхід 12 одиничний сигнал, на установний вхід 4 - нульовий сигнал, а на вхід 11 порога - початкове значення порога . Іншими словами, на установний вхід 4 і на керуючі входи 5, 6, 12 подається код 0001 (табл. 1). В результаті в суматорі 7 формування і підсумовування часткових сум S j 5 10 продовжується доти, доки не сформується одиничний сигнал на виході ознаки нуля суматора 7, що спричинить появу одиничного сигналу на виході 13 сигналу "Кінець" пристрою. У цьому випадку на керуючому вході комутатора 9 вже сформовано відповідні сигнали дозволу з виходу 19 логічного блока 8 і через комутатор 9 на інформаційний вихід 14 результату пристрою подається або результуючий сигнал Y3 0 з виходу 15 суматора 7, або Y3 Sk з виходу 18 суматора 1, або результат Y3 S підсумовування вигляду: 15 20 25 30 N n j 1 S i 1 S j xi i , (7) з виходу 10 суматора 7. У режимі формувача скалярного добутку векторів операцію (7) можна реалізувати окремо, якщо як компоненти одного вектора взяти вхідні сигнали x 1,…,хn, які надходять на групу інформаційних входів 11,…,1n пристрою, а як компоненти другого вектора - значення синаптичних ваг 1,…, n, які надходять на групу інформаційних входів 21,…,2n пристрою. При цьому на установний вхід 4 і керуючі входи 5, 6 і 12 пристрою подаються нульові потенціали, тобто код даної операції 0000 (табл. 1), а на вхід 11 порога також подається нульовий потенціал. В блоках 31,…,3n зміни синаптичних ваг формуються добутки вигляду (1), які з групи виходів 171,…,17n n блоків 3i,…,3n зміни синаптичних ваг подаються на відповідні входи суматора 7 паралельно. Після цього в суматорі 7 виконується формування і підсумовування часткових сум S j цих добутків за формулою (2), поки не з'явиться одиничний сигнал на виході ознаки нуля суматора 7, а отже, на виході 13 сигналу "Кінець" пристрою. Тоді сформована остаточна сума S (7), яка є скалярним добутком компонент xi і i вхідних векторів, подається з виходу 10 суматора 7 через комутатор 9 на інформаційний вихід 14 результату пристрою, оскільки на всі входи логічного блока 8 з керуючих входів 5, 6 пристрою надходять нульові сигнали і відповідно нульовий сигнал з виходу 15 суматора 7. А це свідчить про те, що на виході 19 логічного блока 8 буде сформований відповідний сигнал дозволу для комутатора 9. При налаштуванні на роботу у режимі цифрового інтегратора пристрій працює як суматор вхідних сигналів х1,…,хn, які подаються на групу інформаційних входів 1 1,…,1n пристрою, у вигляді: S' n xi . (8) i 1 35 У цьому випадку на установний вхід 4 пристрою подається одиничний сигнал, який задає значення синаптичних ваг i,…, n рівними одиниці, на керуючі входи 5, 6 і 12 пристрою подаються нульові потенціали відповідно, тобто код даної операції 1000 (табл.1), а на вхід 11 порога подається нульовий потенціал. В суматорі 7 формується за N етапів оброблення сума S' часткових сум S' j вигляду: 40 S' N S' j , j 1 45 (9) яка після появи одиничного сигналу на виході ознаки нуля суматора 7, а отже, на виході 13 сигналу "Кінець" пристрою, подається з виходу 10 суматора 7 через комутатор 9 на інформаційний вихід 14 результату пристрою. В цьому режимі відповідний сигнал дозволу на виході 19 логічного блока 8 формується аналогічно, як у режимі скалярного добутку векторів. Суть роботи суматора 7 (Фіг. 2) полягає в тому, що порогове оброблення n чисел зводиться до обчислення і підсумовування N часткових сум S j , де N - кількість різноманітних вхідних величин ai , порівняння цих сум з порогом і формування підсумкового сигналу вигляду: 4 UA 95067 U n N N , 1 якщо S a i S j q j d j , (10) Y1 i1 j1 j1 0 у протилежно му випадку, де Y1 - результуючий сигнал суматора 7; q j - загальна значуща частина доданків 5 (мінімальний елемент) j-гo етапу; d j - кратність загальної частини q j на j-му етапі; - значення порога оброблення; j - етап оброблення. Процес підсумовування у суматорі 7 має такий вигляд. Спочатку визначається загальна значуща частина q j всіх доданків на j-му етапі, тобто: q j min ai, j 1 n , j 1 N , , i 1 (11) де ai,0 -i-й доданок на вході суматора 7, і перевіряється умова: 10 qj 0 . (12) Якщо умова (12) виконується, то процес підсумовування припиняється. У протилежному випадку виділяється різницевий зріз A j , тобто сукупність величин різниці всіх доданків j-гo етапу з їхньою загальною частиною q j , тобто: 15 i1 i1 A j ai, j n ai, j 1 q j n . (13) В подальшому отриманий різницевий зріз A j є вхідною множиною доданків для наступного (j+1)-ro етапу. Далі формується часткова сума S j як кратне загальної частини q j , де кратність d j 20 визначається кількістю додатних доданків j-гo етапу: S j a j dj . (14) Після цього відбувається підсумовування часткових сум S j за формулою (2). 25 Після сформування часткової суми S i за формулою (14) на першому етапі формується різниця між заданим порогом та частковою сумою Si, отриманою на цьому етапі, тобто: 1 S1 , (15) і перевіряється умова: 1 0 , (16) 30 а в разі її виконання формується одиничний результуючий сигнал Υ суматора 7 і порогове оброблення припиняється. В протилежному випадку процес порогового оброблення продовжується і в подальшому поточна різниця j1 є поточним значенням порогу на 35 наступному j-му етапі оброблення згідно з формулою (3). На j-му етапі перевіряється умова j 0 . (17) Процес порогового оброблення повторюється до виконання умови (17) або до визначення нульової величини q j (II). Виконання умови (11) свідчить про закінчення підсумовування і про 40 формування остаточного результату S підсумовування вигляду (7). 5 UA 95067 U Отже, суматор 7 (Фіг. 2) працює таким чином. На вхід 17і і-ої комірки 21 надходить і-й операнд ai,0 з групи операндів, кількість яких n. Запис операндів в n комірок 21 виконується паралельно за наявності одиничного сигналу на адресному вході 16 пристрою. Через мультиплексор 22 і-й операнд ai,0 надходить на вхід 31 5 10 15 20 25 30 35 40 45 50 55 регістра 23 і-ої комірки 21. Одночасно на вхід 11 порогу подають зовнішній поріг , який через мультиплексор 22 комірки 20 надходить по входу 31 в регістр 23 цієї комірки. Після цього виконується послідовне виділення загальної (мінімальної значущої) частини двох операндів - (і1)-го та і-го - мініматором 27 і запис результату в регістр 28 і-ої комірки 21. Згідно з виразом (11) ця операція виконується послідовно, починаючи з другої комірки 21. Кінцевий результат q1 виділення загальної частини всіх n операндів на першому етапі формується в n-iй комірці 21 і з виходу 45 мінiматора 27 цієї комірки 21 записується в регістри 29 всіх n комірок 21 паралельно по входу 44. Після цього в і-й комірці відбувається порівняння в суматорі-віднімачi 24 і-го операнда ai,0 , що надходить з регістра 23 на його прямий вхід 32, та загальної частини q1 всіх операндів, що надходить з регістра 29 на його інверсний вхід 34. Порівняння відбувається в процесі віднімання від величини операнда загальної частини всіх величин операндів згідно з виразом (13) і ця різниця записується з виходу 35 суматора-віднімача 24 через мультиплексор 22 в регістр 23 по його входу 31 за наявності нульового сигналу на адресному вході 16 пристрою. При цьому на виході 36 знака суматора-віднімача 24 формується знак різниці. Перед початком роботи регістри 23, 28, 29, 48 і тригер 26 всіх комірок 21 і комірки 20 занулені. При відсутності одиничного сигналу знака від'ємного результату одиничний сигнал з інверсного виходу D-тригера 26 подається на керуючий вхід комутатора 30 і дозволяє проходження в і-й комірці через комутатор 30 загальної частини q1 операндів з регістра 29 в суматор 25 (і-1)-ої комірки 21, де відбувається накопичення загальної частини операндів. У випадку, якщо на виході 36 знака суматора-віднімача 24 і-ої комірки 21 з'явиться одиничний сигнал знака від'ємного результату, то наявність нульового сигналу на інверсному виході Dтригера 26, а отже, на керуючому вході комутатора 30 заборонить надходження загальної частини q1 операндів на даному етапі оброблення через комутатор 30 на відповідний вхід суматора 25 (і-1)-ої комірки 21. В суматорі 25 кожної комірки 21 відбувається послідовне підсумовування загальних частин q1 групи з n операндів, а в результаті на виході суматора (n1)-ої комірки 21, тобто на виході 42 цієї комірки формується часткова сума S1 операндів згідно з виразом (14). Після цього відбувається порівняння в суматорі-віднімачі 24 комірки 20 зовнішнього порогу , що надходить по його прямому входу 32 з регістра 23, та часткової суми S1 , що надходить по його інверсному входу 34 з виходу комутатора 30. На першому етапі оброблення з інверсного виходу D-тригера 26 комірки 20 на керуючий вхід комутатора 30 подається одиничний сигнал дозволу, оскільки на початку роботи пристрою D-тригер 26 всіх n комірок 21 і комірки 20 суматора 7 встановлено у нульовий стан одиничним сигналом на вході скидання пристрою, а на керуючому вході 12 пристрою, а також на одному з входів елемента І 50 присутній одиничний сигнал (табл. 1). Порівняння відбувається в процесі віднімання у першому циклі від зовнішнього порогу часткової суми S1 згідно з виразом (15). Різниця 1 записується з виходу 35 суматора-віднімача 24 комірки 20 через мультиплексор 22 у регістр 23 по його входу 31. Сигнали з виходу 36 знака і виходу 54 ознаки нуля суматора-віднімача 24 комірки 20 подаються через елемент АБО 49 на D-вхід D-тригера 26 комірки 20. При цьому при наявності одиничного сигналу на одному з виходів: виході 36 знака або виході 54 ознаки нуля суматоравіднімача 24 нульовий сигнал з інверсного виходу D-тригера 26, проходячи через елемент І 50, заборонить подачу величини S j в наступному циклі оброблення через комутатор 30 на інверсний вхід 34 суматора-віднімача 24 комірки 20, що свідчить про закінчення порогового оброблення пристрою. На прямому виході D-тригера 26 комірки 21 у цьому випадку присутній одиничний сигнал, який формує одиничний сигнал Y1 на виході 15 результуючого сигналу суматора 7. І навпаки, при відсутності одиничного сигналу на обох виходах: виході 36 знака і виході 54 ознаки нуля суматора-віднімача 24 комірки 20 нульовий сигнал подається з виходу елемента АБО 49 на D-вхід D-тригера 26 цієї комірки, з інверсного виходу якого одиничний сигнал, проходячи через елемент І 50, дозволяє подачу через комутатор 30 часткової суми S j з 6 UA 95067 U 5 10 виходу 42 (n-і)-ої комірки 21 на інверсний вхід 34 суматора-віднімача 24 комірки 20. Одночасно одиничний сигнал з інверсного виходу D-тригера 26 комірки 20, поданий на керуючий вхід комутатора 51, дозволяє проходження через нього на вхід 53 регістра 52 накопиченої суми Sk вигляду (2) з виходу регістра 48 n-ої комірки 21 з її фіксацією на інформаційному виході 18 суматора 7. В n-й комірці 21 в суматорі 7 наприкінці кожного етапу оброблення виконується накопичення часткових сум S j за виразом (2) та їх запам'ятовування у регістрі 48 цієї комірки. Так виконується перший етап підсумовування i порогового оброблення. В подальшому процес підсумовування виконується аналогічно першому етапу оброблення згідно з формулами (11)-(14). Процес підсумовування припиняється тоді, коли загальна значуща частина q j всіх поточних доданків на j-му етапі дорівнює нулю за виразом (12), тобто присутній 20 одиничний сигнал на виході ознаки нуля мініматора 27 n-ої комірки 21, а отже на виході 13 суматора 7. При виконанні умови (12) після виконання N етапів оброблення на виході регістра 48 n-ої комірки 21, тобто на інформаційному виході 10 суматора 7 формується остаточна сума S вигляду (7). Процес порогового оброблення буде продовжуватись, доки не буде виконуватись умова (17), а при її невиконанні - доки не буде виконуватись умова (12). При виконанні умови (17) на виході 15 результуючого сигналу суматора 7 формується одиничний сигнал. У табл. 2 наведено приклад формування у суматорі 7 суми чисел масиву {13, 8, 3, 11}, що подаються на входи 171,…,17n, часткових сум S j на виході 18, поточного порогу j у комірці 20, 25 результуючого сигналу Y1 на виході 15 та накопиченої суми S на виході 10. Особливістю порогового оброблення масиву чисел за методом різницевих зрізів є природний паралелізм і нефiксоване (нестале) значення часу оброблення. Це значення залежить від кількості елементів на вході і кількості однакових елементів у масиві. Тому кількість етапів формування остаточної суми S можна визначити за формулою: 15 Nn R (mr 1) , (18) r 1 де n - розмірність вхідного масиву чисел; R - кількість груп з кількістю mr однакових чисел; 30 mr , R - випадкові величини. Разом з тим, з аналізу даних, наведених у табл. 2, видно, що за певних умов результат порогового оброблення, а саме, одиничний результуючий сигнал Y1 , формується раніше, ніж накопичується остаточна сума S чисел, які являють собою зважені вхідні сигнали. Таблиця 2 Різницеві зрізи Aj Елементи a ij зрізів А0 А1 А2 А3 А4 А5 a1j 13 10 5 2 0 0 a2j 8 5 0 a3 j 3 0 a4 j Етапи оброблення Найменше число qii 11 0 0 8 1 3 3 2 5 0 3 3 4 2 5 0 Часткова сума S j 0 3×4=12 5×3=15 3×2=6 2×1=2 0 Поточний поріг j Результуючий сигнал Y1 Накопичення часткових сум S j Ознака закінчення Ζ 30 30-12=18 18-15=3 3-6=-3 -3 -3 0 0 0 1 1 1 0 0 12 0 12+15=27 0 27+6=33 0 33+2=35 0 35 1 7 UA 95067 U 5 Отже, принцип роботи пристрою для моделювання нейрона наближається до роботи біологічного нейрона, час спрацювання якого залежить від порога оброблення, кількості вхідних сигналів і закону їх розподілу у вхідному масиві. Крім того, пристрій за рахунок моделювання формального нейрона як з пороговою, так і з лінійною і лінійною з насиченням функціями активації значно розширює свої функціональні можливості. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 Пристрій для моделювання нейрона, який містить n блоків зміни синаптичних ваг, перші і другі входи яких є інформаційними входами пристрою, суматор, перші n входів якого з'єднані відповідно з виходами n блоків зміни синаптичних ваг, комутатор, причому установний вхід пристрою з'єднаний з відповідним входом n блоків зміни синаптичних ваг, вхід порога, адресний і перший керуючий входи пристрою з'єднані з відповідними входами суматора, перший і другий виходи суматора з'єднані з інформаційними входами комутатора, вихід комутатора є інформаційним виходом результату пристрою, вихід ознаки нуля суматора є виходом сигналу "Кінець" пристрою, який відрізняється тим, що в нього введено логічний блок, перший і другий входи якого з'єднані з другим і третім керуючими входами пристрою, вихід результуючого сигналу суматора підключений до третього інформаційного входу комутатора і третього входу логічного блока, вихід якого з'єднаний з керуючим входом комутатора. 8 UA 95067 U 9 UA 95067 U Комп’ютерна верстка М. Шамоніна Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 10

ДивитисяДодаткова інформація

Автори англійськоюMartyniuk Tetiana Borysivna, Kolisnyk Petro Fedorovych, Kozhemiako Andrii Viktorovych

Автори російськоюМартынюк Татьяна Борисовна, Колиснык Петр Федорович, Кожемьяко Андрей Викторович

МПК / Мітки

МПК: G06G 7/00

Мітки: моделювання, нейрона, пристрій

Код посилання

<a href="https://ua.patents.su/12-95067-pristrijj-dlya-modelyuvannya-nejjrona.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання нейрона</a>

Попередній патент: Модуль активної фазованої антенної решітки з покращеними функціями керування діаграмою направленості

Наступний патент: Біогазова установка з сонячною батареєю

Випадковий патент: Гідропресова установка