Пристрій аналого-цифрового перетворення

Номер патенту: 115691

Опубліковано: 25.04.2017

Автори: Слюсар Вадим Іванович, Волощук Ігор Вікторович, Нікітін Микола Михайлович, Шацман Леонід Георгієвич

Формула / Реферат

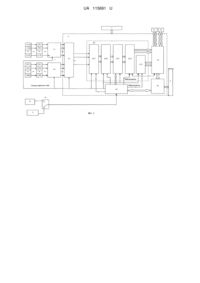

1. Пристрій аналого-цифрового перетворення, до складу якого входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів у складі послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрового діаграмоутворення та до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину, який відрізняється тим, що до складу модуля цифрової обробки сигналів додатково введено модуль цифрової I/Q (квадратурної)-демодуляції та модуль синтезу цифрових частотних фільтрів, при цьому перша група входів модуля цифрової I/Q (квадратурної)-демодуляції є першою групою входів модуля цифрової обробки сигналів, виходи модуля цифрової I/Q (квадратурної)-демодуляції підключені до першої групи входів модуля цифрової фільтрації сигналів, шини даних модуля синтезу цифрових частотних фільтрів через модуль управління пам'яттю (входить до складу ПЛІС) підключені до шини даних модулів оперативної пам'яті, тактові входи модуля цифрової I/Q (квадратурної)-демодуляції та модуля синтезу цифрових частотних фільтрів підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової I/Q (квадратурної)-демодуляції підключені до п'ятого виходу модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля синтезу цифрових частотних фільтрів підключений до шостого виходу модуля формування сигналів синхронізації та управління.

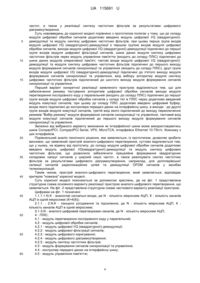

2. Пристрій аналого-цифрового перетворення за п. 1, який відрізняється тим, що для забезпечення режиму тестування алгоритмів цифрової обробки сигналів виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля цифрової обробки сигналів у складі тієї ж ПЛІС через додатково введений до складу ПЛІС модуль комутації сигналів, при цьому до складу ПЛІС додатково введено цифровий буфер, входи якого підключені до контролера передачі даних на інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління, тактовий вхід модуля комутації сигналів підключений до першого виходу модуля формування сигналів синхронізації та управління.

3. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовується шина CompactPCI.

4. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовується шина CompactPCI Serial.

5. Пристрій аналого-цифрового перетворення за будь-яким з пп.1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси VPX.

6. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси МісrоТСА.

7. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси Ethernet 10 Гбіт/с.

Текст

Реферат: Пристрій аналого-цифрового перетворення, до складу якого входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів у складі послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів. UA 115691 U (12) UA 115691 U UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до галузі радіотехніки, зокрема до пристроїв аналого-цифрового перетворення, і може бути використана для цифрової обробки сигналів в системах радіолокації, зв'язку тощо. Відомий пристрій аналого-цифрового перетворення (АЦП) МХ.3132 для шини CompactPCI (СРСІ) та РХІ у форматі 6U німецької фірми Spectrum Systementwicklung Microelectronic Gmbh [1]. До складу цього пристрою входять вісім аналогових сигнальних входів, ланцюги узгодження та підсилення, вісім 12-бітних мікросхем АЦП, модуль управління пам'яттю й суміщений з ним модуль управління АЦП, модулі оперативної пам'яті, контролер передачі даних на інтерфейсну шину, вхід зовнішньої синхронізації, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), внутрішній тактовий генератор, модуль формування сигналів синхронізації, цифрові входи, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до аналогових входів 12-бітних мікросхем АЦП, цифрові виходи АЦП підключені через модуль управління пам'яттю й суміщений з ним модуль управління АЦП до шини даних модулів оперативної пам'яті та до відповідних входів контролера передачі даних на інтерфейсну шину, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації). Зазначений пристрій АЦП дозволяє здійснювати аналого-цифрове перетворення сигналів синхронно у часі по восьми паралельних каналах, записувати отримані відліки АЦП у модулі оперативної пам'яті та передавати їх через інтерфейсну шину СРСІ на подальші пристрої цифрової обробки сигналів. До недоліків відомих пристроїв АЦП МХ.3132 [1] слід віднести відсутність у їхньому складі модуля програмованої логічної інтегральної схеми (ПЛІС), в якому можна було б здійснювати цифрову обробку сигналів, зокрема їх децимацію (проріджування у часі), цифрову фільтрацію, цифрову корекцію характеристик приймальних каналів, цифрове формування квадратурних складових сигналів тощо. Крім того, виконання АЦП у вигляді окремої мікросхеми на кожен канал перетворення призводить до надмірного теплового розсіювання ними потужності та додаткового споживання електричної енергії пристроєм. Застосування в АЦП паралельної 12бітної шини для видачі результатів аналого-цифрового перетворення надто ускладнює розведення електричних сигнальних ліній на друкованій платі, спонукає виготовляти її з великою кількістю друкованих шарів. Крім того, паралельна вихідна шина АЦП породжує додатковий джитер тактових сигналів за рахунок погіршення електромагнітної сумісності модулів, що застосовуються у пристрої, через випромінювання завад 12-бітними паралельними шинами з виходів АЦП, що виконують роль своєрідних антен та погіршують імпеданс ліній розповсюдження сигналів. Останні з недоліків, зокрема, обмежують частоту дискретизації сигналів у зазначених пристроях величиною 25 МГц [1]. Відомий пристрій аналого-цифрового перетворення (АЦП) VHS-ADC16 High Performance Multi-Channel A/D для шини CompactPCI (CPCI) у форматі 6U канадської фірми Lyrtech [2]. До складу цього пристрою у основному варіанті конфігурації входять вісім аналогових сигнальних входів (можливо збільшення їхньої кількості до шістнадцяти входів шляхом встановлення додаткової мезонінної плати), ланцюги узгодження та підсилення, вісім (або шістнадцять) 14-бітних мікросхем АЦП, вхід зовнішньої синхронізації, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), внутрішній тактовий генератор, модуль формування сигналів синхронізації, цифрові входи, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), до складу якої входять модуль управління пам'яттю й суміщений з ним модуль управління АЦП, контролер передачі даних на інтерфейсну шину, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до аналогових входів 14бітних мікросхем АЦП, цифрові виходи АЦП підключені через модуль управління пам'яттю й суміщений з ним модуль управління АЦП до шини даних модулів оперативної пам'яті та до відповідних входів контролера передачі даних на інтерфейсну шину, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації). Перевагою пристрою аналого-цифрового перетворення (АЦП) VHS-ADC16, порівняно з [1], є наявність ПЛІС, в якій здійснюється паралельна обробка даних з кількох каналів АЦП. Недоліком є низька швидкість передачі даних через інтерфейс 32-бітної шини CompactPCI з тактовою частотою 33 МГц, використання окремих мікросхем АЦП на кожен з каналів, 1 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 60 паралельні вихідні шини АЦП, що потребує використання надмірно дорогих ПЛІС, щоб забезпечити одночасне підключення паралельних виходів 8 чи 16 мікросхем АЦП. Відомий пристрій аналого-цифрового перетворення (АЦП) для шини CompactPCI (CPCI) у форматі 6U, запропонований у [3], до складу якого входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрової обробки сигналів та до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою. Відмінною рисою відомого пристрою [3] є аналого-цифрове перетворення сигналів синхронно у часі по значній кількості паралельних каналів, обробка сигналів з виходів чотирьох і більше каналів АЦП в одному чипі ПЛІС, використання ешелонованого розташування ПЛІС на платі, що дозволяє розділити функції між різними ПЛІС відповідно до етапів цифрової обробки даних. Наприклад, у ПЛІС першого ешелону, що безпосередньо контактують з АЦП, можуть бути реалізовані первинна або узгоджена цифрова фільтрація сигналів із проріджуванням інформаційного потоку у часі (децимацією) й формуванням квадратурних складових сигналів, корекція квадратичних погрішностей, неідентичностей амплітудно-частотних характеристик (АЧХ) аналогових приймальних каналів і діаграм спрямованості антенних елементів, а також модуль менеджменту алгоритмів обробки, що забезпечує їхню адаптацію під необхідний режим функціонування. У другому ешелоні ПЛІС реалізовані модулі міжканальної обробки даних, наприклад, початкові етапи цифрового діаграмоутворення, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, контролер передачі даних на інтерфейсну шину, що забезпечує передачу результатів цифрової обробки сигналів через шину CompactPCI на подальший обчислювальний пристрій. Для передачі даних між ешелонами ПЛІС використовується послідовний інтерфейс Rocket I/O, що істотно спрощує розведення друкованої плати. Для проведення контролю функціонування МЦПМ можуть використовуватися нарівні з основними також спеціальні тестові архітектури ПЛІС, записані у постійний запам'ятовуючий пристрій, що дозволяють діагностувати правильність функціонування ПЛІС на конкретних фазах обробки сигналів. До недоліків відомого пристрою [3] слід віднести використання ешелонованого розташування модулів обробки даних у різних ПЛІС, що призводить до надмірного теплового розсіювання ними потужності та додаткового споживання електричної енергії пристроєм, надто ускладнює розведення електричних сигнальних ліній на друкованій платі, спонукає виготовляти її з великою кількістю друкованих шарів. Це призводить до збільшення собівартості пристрою. Крім того, наявність надмірної кількості ПЛІС погіршує електромагнітну сумісність модулів, що застосовуються у пристрої, через випромінювання додаткових завад послідовними інтерфейсними шинами, що з'єднують мікросхеми ПЛІС і виконують роль своєрідних антен та погіршують імпеданс ліній розповсюдження сигналів. Застосування як оперативної пам'яті мікросхем статичної пам'яті ZBT SRAM обмежує максимальний об'єм записуваної інформації через відсутність відповідних мікросхем з ємністю 1 Гігабайт та більше і призводить до подорожчання пристрою. Найбільш близьким технічним рішенням до заявленої корисної моделі є пристрій аналогоцифрового перетворення, запропонований у [4], до складу якого входять аналогові сигнальні 2 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів у складі послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрового діаграмоутворення та до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину. Відмінною рисою відомого пристрою АЦП, вибраного за прототип, є забезпечення можливості багаторозрядного (12-біт і більше) оцифровування паралельно до 32 і більше каналів надходження аналогових сигналів (застосована одна багатоканальна мікросхема АЦП на всі 4 і більше каналів надходження аналогових сигналів замість окремих мікросхем на кожен з каналів), здійснення попередньої цифрової обробки сигналів, що формуються одночасно по всіх паралельних каналах АЦП, зменшення джитеру за рахунок поліпшення електромагнітної сумісності модулів, що застосовуються у пристрої (паралельні інтерфейси передачі результатів оцифровування з виходів окремих мікросхем АЦП на ПЛІС замінені на послідовні диференціальні інтерфейси (по одній диференціальній парі ліній на канал АЦП), що дозволило поліпшити електромагнітну сумісність елементів пристрою, спростити розведення друкованої плати та зменшити явище джитеру), збільшення об'єму та здешевлення вартості оперативної пам'яті за рахунок застосування розосереджених усередині ПЛІС чарунок пам'яті або окремих мікросхем динамічної пам'яті. Недоліком пристрою-прототипу є те, що в модулі цифрової фільтрації сигналів здійснюють лише попередню узгоджену цифрову фільтрацію сигналів із проріджуванням інформаційного потоку у часі (децимацією) й формуванням квадратурних складових напруг сигналів за результатами децимації [4]. Такий спосіб формування квадратурних складових напруг сигналів є вузькосмуговим і призводить до похибок в обробці сигналів. Крім того, у пристрої-прототипі не передбачено синтез частотних фільтрів за результатами цифрового діаграмоутворення. В основу корисної моделі поставлена задача підвищення основних технічних характеристик пристрою АЦП. Очікуваний технічний результат від заявленої корисної моделі полягає у забезпеченні можливості прецизійного формування квадратурних складових напруг сигналів у широкій смузі 3 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 60 частот, а також у реалізації синтезу частотних фільтрів за результатами цифрового діаграмоутворення. Суть нововведень до корисної моделі порівняно з прототипом полягає у тому, що до складу модуля цифрової обробки сигналів додатково введено модуль цифрової I/Q (квадратурної)демодуляції та модуль синтезу цифрових частотних фільтрів, при цьому перша група входів модуля цифрової I/Q (квадратурної)-демодуляції є першою групою входів модуля цифрової обробки сигналів, виходи модуля цифрової I/Q (квадратурної)-демодуляції підключені до першої групи входів модуля цифрової фільтрації сигналів, шини даних модуля синтезу цифрових частотних фільтрів через модуль управління пам'яттю (входить до складу ПЛІС) підключені до шини даних модулів оперативної пам'яті, тактові входи модуля цифрової I/Q (квадратурної)демодуляції та модуля синтезу цифрових частотних фільтрів підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової I/Q (квадратурної)-демодуляції підключені до п'ятого виходу модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля синтезу цифрових частотних фільтрів підключений до шостого виходу модуля формування сигналів синхронізації та управління. Перший варіант конкретної реалізації заявленого пристрою відрізняється тим, що для забезпечення режиму тестування алгоритмів цифрової обробки сигналів виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля цифрової обробки сигналів у складі тієї ж ПЛІС через додатково введений модуль комутації сигналів, при цьому до складу ПЛІС додатково введено цифровий буфер, входи якого підключені до контролера передачі даних на інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління, тактовий вхід модуля комутації сигналів підключений до першого виходу модуля формування сигналів синхронізації та управління. Залежно від вибраного варіанту виконання як інтерфейсної шини може використовуватись шина CompactPCI, CompactPCI Serial, VPX, MicroTCA, інтерфейси Ethernet 10 Гбіт/с. Кожному з цих інтерфейсів. Порівняльний аналіз технічного рішення, яке заявляється, із прототипом, дозволяє зробити висновок, що заявлений пристрій аналого-цифрового перетворення, суттєво відрізняється тим, що у ньому, на відміну від прототипу, до складу модуля цифрової обробки сигналів додатково введено модуль цифрової І/Q(квадратурної)-демодуляції та модуль синтезу цифрових частотних фільтрів, що дозволило забезпечити прецизійне формування квадратурних складових напруг сигналів у широкій смузі частот, а також реалізувати синтез частотних фільтрів за результатами цифрового діаграмоутворення, наприклад, для допплерівської селекції сигналів радіолокаційних цілей та демодуляції OFDM сигналів у засобах телекомунікацій. Таким чином, пристрій аналого-цифрового перетворення, який заявляється, відповідає критерію "новизна" корисної моделі. Суть корисної моделі пояснюється за допомогою креслень, де на фіг. 1 представлена структурна схема основного варіанту реалізації пристрою аналого-цифрового перетворення, що заявляється. На фіг. 2 представлена структурна схема часткового варіанту реалізації пристрою. Цифрами на фіг. 1 позначені: 1.1.1-1.N.K - аналогові сигнальні входи, де N - кількість мікросхем АЦП, К - кількість каналів АЦП в одній мікросхемі (К=4(8)); 2.1.1. - 2.N.K - ланцюги узгодження та підсилення, де N - кількість мікросхем АЦП, К кількість каналів АЦП в одній мікросхемі; 3.1-3.N - аналого-цифровий перетворювач каналів, де N - кількість мікросхем АЦП; 4 - ПЛІС; 4.1 - модуль перетворення послідовного коду у паралельний; 4.2 - модуль цифрової обробки сигналів; 4.2.1 - модуль цифрової I/Q (квадратурної)-демодуляції; 4.2.2 - модуль цифрової фільтрації сигналів; 4.2.3 - модуль цифрового коригування; 4.2.4 - модуль цифрового діаграмоутворення; 4.2.5 - модуль синтезу частотних фільтрів; 4.3 - модуль формування сигналів синхронізації та управління; 4.4 - контролер передачі даних на інтерфейсну шину; 4.5 - модуль управління пам'яттю; 4 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 60 5 - інтерфейсна шина; 6.1 - модуль оперативної пам'яті RAM1; 6.2 - модуль оперативної пам'яті RAM2; 7 - постійний запам'ятовуючий пристрій; 8 - вхід зовнішньої синхронізації; 9 - внутрішній тактовий генератор; 10 - комутатор тактових сигналів. Пристрій аналого-цифрового перетворення, що наведено на фіг. 1, містить аналогові сигнальні входи 1.1.1-1.N.K, ланцюги узгодження та підсилення 2.1.1. - 2.N.K, вхід зовнішньої синхронізації 8, внутрішній тактовий генератор 9, комутатор тактових сигналів 10 (з внутрішнього тактового генератора 9 та входу зовнішньої синхронізації 8), багатоканальні АЦП 3.1-3.N, модулі оперативної пам'яті 6.1, 6.2, постійний запам'ятовуючий пристрій 7, програмовану логічну інтегральну схему (ПЛІС) 4, в якій містяться модуль перетворення послідовного коду у паралельний 4.1, модуль цифрової обробки сигналів 4.2 у складі послідовно з'єднаних модуля цифрової фільтрації сигналів 4.2.2, модуля цифрового коригування 4.2.3 та модуля цифрового діаграмоутворення 4.2.4, контролер передачі даних на інтерфейсну шину 4.4, модуль управління пам'яттю 4.5, модуль формування сигналів синхронізації та управління 4.3, при цьому аналогові сигнальні входи 1.1.1-1.N.K підключені через ланцюги узгодження та підсилення 2.1.1. - 2.N.K до відповідних аналогових входів багатоканальних АЦП 3.1-3.N, вхід зовнішньої синхронізації 8 та вихід внутрішнього тактового генератора 9 підключені до відповідних входів комутатора тактових сигналів 10, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів 4.2, що входить до складу ПЛІС 4, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП 3.1-3.N), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний 4.1 (входить до складу ПЛІС 4), виходи модуля перетворення послідовного коду у паралельний 4.1 підключені до першої групи входів модуля цифрової обробки сигналів 4.2 (входить до складу ПЛІС 4), шини даних модулів оперативної пам'яті 6.1, 6.2 підключені через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) до виходів модуля цифрового діаграмоутворення 4.2.4 та до відповідних входів контролера передачі даних на інтерфейсну шину 4.4, а шини адресації та управління модулів оперативної пам'яті 6.1, 6.2 підключені до відповідних виходів модуля управління пам'яттю 4.5 (входить до складу ПЛІС 4), постійний запам'ятовуючий пристрій 7 підключений до входів загрузки архітектури ПЛІС 4, виходи контролера передачі даних на інтерфейсну шину 4.4 підключені до інтерфейсної шини 5 пристрою, виходи модуля цифрової фільтрації сигналів 4.2.2 підключені до першої групи входів модуля цифрового коригування 4.2.3, тактові входи модуля цифрової фільтрації сигналів 4.2.2, модуля цифрового коригування 4.2.3, модуля цифрового діаграмоутворення 4.2.4, а також тактові входи АЦП 3.1-3.N, модуля перетворення послідовного коду у паралельний 4.1 і перші входи управління модуля управління пам'яттю 4.5 підключені до першого виходу модуля формування сигналів синхронізації та управління 4.3 (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів 4.2.2 та модуля цифрового коригування 4.2.3 підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління 4.3, вхід вибору алгоритму модуля цифрового діаграмоутворення 4.2.4 підключений до четвертого виходу модуля формування сигналів синхронізації та управління 4.3, тактовий вхід якого підключений до виходу комутатора тактових сигналів 10, входи управління модуля формування сигналів синхронізації та управління 4.3 підключені до другої групи виходів контролера передачі даних на інтерфейсну шину 4.4, який відрізняється тим, що до складу модуля цифрової обробки сигналів 4.2 додатково введено модуль цифрової I/Q (квадратурної)-демодуляції 4.2.1 та модуль синтезу цифрових частотних фільтрів 4.2.5, при цьому перша група входів модуля цифрової І/Q (квадратурної)-демодуляції 4.2.1 є першою групою входів модуля цифрової обробки сигналів 4.2, виходи модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 підключені до першої групи входів модуля цифрової фільтрації сигналів 4.2.2, шини даних модуля синтезу цифрових частотних фільтрів 4.2.5 через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) підключені до шини даних модулів оперативної пам'яті 6.1, 6.2, тактові входи модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 та модуля синтезу цифрових частотних фільтрів 4.2.5 підключені до першого виходу модуля формування сигналів синхронізації та управління 4.3 (входить до складу ПЛІС 4), другі групи входів модуля цифрової I/Q (квадратурної)демодуляції 4.2.1 підключені до п'ятого виходу модуля формування сигналів синхронізації та управління 4.3, вхід вибору алгоритму модуля синтезу цифрових частотних фільтрів 4.2.5 підключений до шостого виходу модуля формування сигналів синхронізації та управління 4.3. 5 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 60 Принцип роботи основного варіанту заявленого пристрою полягає в наступному. На етапі підготовки пристрою до роботи за допомогою комутатора тактових сигналів 10 вибирають режим подальшої роботи пристрою: з тактуванням сигналами такту, що подають на вхід зовнішньої синхронізації 8, або ж сигналами такту з внутрішнього тактового генератора 9. На етапі ініціювання роботи пристрою одразу після вмикання живлення відповідні тактові сигнали надходять на вхід модуля формування сигналів синхронізації та управління 4.3, що входить до складу ПЛІС 4. Крім того, з постійного запам'ятовуючого пристрою 7 через відповідні входи ПЛІС 4 здійснюють загрузку архітектури ПЛІС 4. Далі через інтерфейсну шину 5 і контролер передачі даних на інтерфейсну шину 4.4 у модуль формування сигналів синхронізації та управління 4.3 записують параметри управління роботою пристрою та параметри управління цифровою обробкою сигналів, зокрема: розмірність та коефіцієнти I/Q (квадратурної)демодуляції, коди управління, що визначають кількість відліків сигналів, які мають накопичуватися в алгоритмі узгодженої фільтрації, коефіцієнти коригування міжканальних неідентичностей амплітудно-частотних характеристик (АЧХ) аналогових приймальних каналів і діаграм спрямованості антенних елементів, розмірність ШПФ для операції цифрового діаграмоутворення та синтезу частотних фільтрів. В основному режимі роботи пристрою, що заявляється, аналогові сигнали з K×N радіоканалів надходять на аналогові сигнальні входи 1.1.1-1.N.K й далі через ланцюги узгодження та підсилення 2.1.1. - 2.N.K - на відповідні аналогові входи N багатоканальних АЦП 3.1-3.N. Тактування АЦП 3.1-3.N здійснюють за допомогою сигналів управління АЦП, які надходять на тактові входи АЦП 3.1-3.N з відповідного виходу модуля формування сигналів синхронізації та управління 4.3. Результати аналого-цифрового перетворення напруг сигналів з виходів АЦП 3.1-3.N передають за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з K каналів N АЦП 3.1-3.N) на вхід модуля перетворення послідовного коду у паралельний 4.1 (входить до складу ПЛІС 4). Далі цифрові відліки напруг сигналів у паралельному коді надходять на першу групу входів модуля цифрової I/Q (квадратурної)демодуляції 4.2.1, які одночасно є першою групою входів модуля цифрової обробки сигналів 4.2. В модулі цифрової I/Q (квадратурної)-демодуляції 4.2.1 формують квадратурні складові напруг сигналів, наприклад, згідно з способом, описаним у патенті України на корисну модель № 46666 [5]. При цьому попередньо з модуля формування сигналів синхронізації та управління 4.3 завантажуються розмірність та коефіцієнти I/Q (квадратурної)-демодуляції. В модулі цифрової фільтрації сигналів 4.2.2 здійснюють попередню узгоджену цифрову фільтрацію сигналів із проріджуванням інформаційного потоку у часі (децимацією). По другій групі входів на модуль цифрової фільтрації сигналів 4.2.2 надходять з модуля формування сигналів синхронізації та управління 4.3 коди управління, що визначають кількість відліків сигналів, які мають накопичуватися в алгоритмі узгодженої фільтрації. Крім того, з першого виходу модуля формування сигналів синхронізації та управління 4.3 на відповідні входи модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 та модуля цифрової фільтрації сигналів 4.2.2 надходять необхідні тактові сигнали. Далі у модулі цифрового коригування 4.2.3 здійснюють цифрове коригування неідентичностей амплітудно-частотних характеристик (АЧХ) аналогових приймальних каналів і амплітудно-фазових характеристик діаграм спрямованості антенних елементів. Результати обробки у модулі цифрового коригування 4.2.3 надходять на вхід модуля цифрового діаграмоутворення 4.2.4, в якому реалізована міжканальна обробка даних, наприклад, початкові етапи цифрового діаграмоутворення за допомогою операції швидкого перетворення Фур'є. На другі групи входів модуля цифрового коригування 4.2.3, модуля цифрового діаграмоутворення 4.2.4 та модуля синтезу цифрових частотних фільтрів 4.2.5 надходять параметри управління цифровою обробкою сигналів з відповідних виходів модуля формування сигналів синхронізації та управління 4.3, зокрема: коефіцієнти коригування міжканальних неідентичностей амплітудно-частотних характеристик (АЧХ) аналогових приймальних каналів і діаграм спрямованості антенних елементів, розмірність ШПФ для операції цифрового діаграмоутворення та синтезу частотних фільтрів. Тактові сигнали надходять з першого виходу модуля формування сигналів синхронізації та управління 4.3 на тактові входи модуля цифрового коригування 4.2.3, модуля цифрового діаграмоутворення 4.2.4 та модуля синтезу цифрових частотних фільтрів 4.2.5. Результати обробки сигналів у модулі цифрового діаграмоутворення 4.2.4 з його виходу надходять через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) на шину даних модулів оперативної пам'яті 6.1, 6.2. Запис даних здійснюють в один з банків пам'яті, тоді як з 6 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 60 іншого банку записані раніше дані можуть зчитувати через модуль управління пам'яттю 4.5, контролер передачі даних на інтерфейсну шину 4.4 та саму інтерфейсну шину 5 у подальший обчислювальний пристрій. В іншому режимі відліки сигнальних напруг, записані у модулі оперативної пам'яті 6.1, 6.2 завантажують через модуль управління пам'яттю 4.5 та шину даних до модуля синтезу цифрових частотних фільтрів 4.2.5. Результати формування відгуків частотних фільтрів, наприклад, за допомогою операції швидкого перетворення Фур'є, надходять через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) на шину даних модулів оперативної пам'яті 6.1, 6.2, де вони зберігаються. Надалі через модуль управління пам'яттю 4.5, контролер передачі даних на інтерфейсну шину 4.4 та саму інтерфейсну шину 5 результати синтезу цифрових частотних фільтрів зчитуються у подальший обчислювальний пристрій. Цифрами на фіг. 2 позначені: 1.1.1-1.N.K - аналогові сигнальні входи, де N - кількість мікросхем АЦП, К - кількість каналів АЦП в одній мікросхемі (К= 4(8)); 2.1.1. - 2.N.K - ланцюги узгодження та підсилення, де N - кількість мікросхем АЦП, К кількість каналів АЦП в одній мікросхемі; 3.1-3.N - аналого-цифровий перетворювач каналів, де N - кількість мікросхем АЦП; 4 - ПЛІС; 4.1 - модуль перетворення послідовного коду у паралельний; 4.2 - модуль цифрової обробки сигналів; 4.2.1. - модуль цифрової I/Q (квадратурної)-демодуляції; 4.2.2 - модуль цифрової фільтрації сигналів; 4.2.3 - модуль цифрового коригування; 4.2.4 - модуль цифрового діаграмоутворення; 4.2.5 - модуль синтезатора частотних фільтрів; 4.3 - модуль формування сигналів синхронізації та управління; 4.4 - контролер передачі даних на інтерфейсну шину; 4.5 - модуль управління пам'яттю; 4.6 - цифровий буфер; 4.7 - модуль комутації сигналів; 5 - інтерфейсна шина; 6.1 - модуль оперативної пам'яті RAM1; 6.2 - модуль оперативної пам'яті RAM2; 7 - постійний запам'ятовуючий пристрій; 8 - вхід зовнішньої синхронізації; 9 - внутрішній тактовий генератор; 10 - комутатор тактових сигналів. Пристрій аналого-цифрового перетворення, що наведено на фіг. 2, містить аналогові сигнальні входи 1.1.1-1.N.K, ланцюги узгодження та підсилення 2.1.1. - 2.N.K, вхід зовнішньої синхронізації 8, внутрішній тактовий генератор 9, комутатор тактових сигналів 10 (з внутрішнього тактового генератора 9 та входу зовнішньої синхронізації 8), багатоканальні АЦП 3.1-3.N, модулі оперативної пам'яті 6.1, 6.2, постійний запам'ятовуючий пристрій 7, програмовану логічну інтегральну схему (ПЛІС) 4, в якій містяться модуль перетворення послідовного коду у паралельний 4.1, модуль цифрової обробки сигналів 4.2 у складі послідовно з'єднаних модуля цифрової фільтрації сигналів 4.2.2, модуля цифрового коригування 4.2.3 та модуля цифрового діаграмоутворення 4.2.4, контролер передачі даних на інтерфейсну шину 4.4, модуль управління пам'яттю 4.5, модуль формування сигналів синхронізації та управління 4.3, при цьому аналогові сигнальні входи 1.1.1-1.N.K підключені через ланцюги узгодження та підсилення 2.1.1. - 2.N.K до відповідних аналогових входів багатоканальних АЦП 3.1-3.N, вхід зовнішньої синхронізації 8 та вихід внутрішнього тактового генератора 9 підключені до відповідних входів комутатора тактових сигналів 10, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів 4.2, що входить до складу ПЛІС 4, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП 3.1-3.N), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний 4.1 (входить до складу ПЛІС 4), виходи модуля перетворення послідовного коду у паралельний 4.1 підключені до першої групи входів модуля цифрової обробки сигналів 4.2 (входить до складу ПЛІС 4), шини даних модулів оперативної пам'яті 6.1, 6.2 підключені через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) до виходів модуля цифрового діаграмоутворення 4.2.4 та до відповідних входів контролера передачі даних на інтерфейсну шину 4.4, а шини адресації та управління модулів оперативної пам'яті 6.1, 6.2 підключені до відповідних виходів модуля 7 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 управління пам'яттю 4.5 (входить до складу ПЛІС 4), постійний запам'ятовуючий пристрій 7 підключений до входів загрузки архітектури ПЛІС 4, виходи контролера передачі даних на інтерфейсну шину 4.4 підключені до інтерфейсної шини 5 пристрою, виходи модуля цифрової фільтрації сигналів 4.2.2 підключені до першої групи входів модуля цифрового коригування 4.2.3, тактові входи модуля цифрової фільтрації сигналів 4.2.2, модуля цифрового коригування 4.2.3, модуля цифрового діаграмоутворення 4.2.4, а також тактові входи АЦП 3.1-3.N, модуля перетворення послідовного коду у паралельний 4.1 і перші входи управління модуля управління пам'яттю 4.5 підключені до першого виходу модуля формування сигналів синхронізації та управління 4.3 (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів 4.2.2 та модуля цифрового коригування 4.2.3 підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління 4.3, вхід вибору алгоритму модуля цифрового діаграмоутворення 4.2.4 підключений до четвертого виходу модуля формування сигналів синхронізації та управління 4.3, тактовий вхід якого підключений до виходу комутатора тактових сигналів 10, входи управління модуля формування сигналів синхронізації та управління 4.3 підключені до другої групи виходів контролера передачі даних на інтерфейсну шину 4.4, який відрізняється тим, що до складу модуля цифрової обробки сигналів 4.2 додатково введено модуль цифрової I/Q (квадратурної)-демодуляції 4.2.1 та модуль синтезу цифрових частотних фільтрів 4.2.5, а також для забезпечення режиму тестування алгоритмів цифрової обробки сигналів - модуль комутації сигналів 4.7 та цифровий буфер 4.6, при цьому перша група входів модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 є першою групою входів модуля цифрової обробки сигналів 4.2, виходи модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 підключені до першої групи входів модуля цифрової фільтрації сигналів 4.2.2, шини даних модуля синтезу цифрових частотних фільтрів 4.2.5 через модуль управління пам'яттю 4.5 (входить до складу ПЛІС 4) підключені до шини даних модулів оперативної пам'яті 6.1, 6.2, тактові входи модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 та модуля синтезу цифрових частотних фільтрів 4.2.5 підключені до першого виходу модуля формування сигналів синхронізації та управління 4.3 (входить до складу ПЛІС 4), другі групи входів модуля цифрової I/Q (квадратурної)-демодуляції 4.2.1 підключені до п'ятого виходу модуля формування сигналів синхронізації та управління 4.3, вхід вибору алгоритму модуля синтезу цифрових частотних фільтрів 4.2.5 підключений до шостого виходу модуля формування сигналів синхронізації та управління 4.3, виходи модуля перетворення послідовного коду у паралельний 4.1 (входить до складу ПЛІС 4) підключені до першої групи входів модуля цифрової обробки сигналів 4.2 у складі тієї ж ПЛІС 4 через додатково введений до складу ПЛІС 4 модуль комутації сигналів 4.7, входи цифрового буфера 4.6 підключені до контролера передачі даних на інтерфейсну шину 4.4, а виходи - до другої групи входів модуля комутації сигналів 4.7, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління 4.3, тактовий вхід модуля комутації сигналів 4.7 підключений до першого виходу модуля формування сигналів синхронізації та управління 4.3. Функціонування заявленого пристрою у варіанті виконання, наведеному на фіг. 2, відрізняється від роботи пристрою за фіг. 1, 3 тим, що у режимі тестування алгоритмів цифрової обробки сигналів на етапі ініціювання роботи пристрою на додаток до описаних операцій через інтерфейсну шину 5 і контролер передачі даних на інтерфейсну шину 4.4 у цифровий буфер 4.6 записують тестові цифрові коди, а у модуль формування сигналів синхронізації та управління 4.3 записують команду на переключення режимів "Вибір режиму". Під дією цієї команди модуль комутації сигналів 4.7 перемикають у стан, коли цифрові дані на вхід модуля цифрової обробки сигналів 4.2 в основному режимі роботи пристрою будуть надходити з цифрового буферу 4.6, а не з модуля перетворення послідовного коду у паралельний 4.1. В основному режимі роботи варіанту заявленого пристрою, зображеного на фіг. 2, за допомогою тестових кодів, записаних у цифровий буфер 4.6, контролюють працездатність модуля цифрової обробки сигналів 4.2 шляхом зчитування у подальший обчислювальний пристрій результатів обробки тестової послідовності даних. У випадку застосування контролера шини CompactPCI у складі ПЛІС пристрою він забезпечує передачу даних по шині 32 (64) біт/33 МГц як у режимі SLAVE, так і в режимі MASTER. Плата пристрою сумісна за рівнями сигналів шини CompactPCI як із шиною 3,3 В, так і з шиною 5 В. Контролер CompactPCI забезпечує можливість зчитування й запису параметрів управління в 32 регістра користувача. Кожний з таких регістрів має розрядність 32 біт. 8 UA 115691 U 5 10 15 20 25 30 35 40 45 При застосуванні інших варіантів інтерфейсної шини (CompactPCI Serial, VPX, MicroTCA, інтерфейси Ethernet 10 Гбіт/с) забезпечують дотримання вимог до електричних та конструктивних параметрів інтерфейсу відповідних стандартів. Конструкція плати забезпечує можливість використання мікросхем ПЛІС FPGA, наприклад, фірми Xilinx. На друкованій платі пристрою від мікросхеми FPGA до кожної із мікросхем пам'яті розведені окремо шина адреси, шина даних й керуючі сигнали. Пристрій працює як від внутрішнього, так і від зовнішнього джерела тактового сигналу. Частота зовнішнього джерела тактового сигналу fтaкт=50-70 МГц. Перемикання джерела тактового сигналу здійснюється за допомогою запаяної у плату перемички. Друкована плата пристрою разом із установленими на неї компонентами покрита двома шарами вологостійкого лаку. Як рознімання для аналогових входів пристрою застосовуються рознімання SMA або SMB. Модуль формування сигналів синхронізації та управління забезпечує видачу на АЦП службових сигналів і зчитування відліків АЦП, наприклад, із тактовою частотою 50 МГц. Крім того, модуль формування сигналів синхронізації та управління забезпечує формування управляючих сигналів для модуля управління пам'яттю. Ці сигнали забезпечують запис даних до пам'яті з необхідним коефіцієнтом проріджування і перемикання між модулями управління мікросхемами для забезпечення потрібного алгоритму роботи. Модуль комутації сигналів забезпечує формування інформаційних потоків для обробки сигналів і запису їх у пам'ять. Модуль управління пам'яттю забезпечує буферизацію даних для обміну між модулями ПЛІС і складається з двох або більше незалежних модулів керування мікросхемами динамічної пам'яті. Кожен модуль керування мікросхемою забезпечує темп обміну даними при запису або зчитуванні - не менш 50 Мслів×32 у секунду і може знаходитися або в стані запису, або в стані зчитування незалежно один від одного. Модуль цифрової обробки сигналів, модуль управління пам'яттю, контролер передачі даних на інтерфейсну шину, модуль формування сигналів синхронізації та управління формуються усередині ПЛІС у вигляді скомпільованих ядер. Джерела інформації: 1. МХ.3132-8 Каnаl 12 Bit A/D. - http://www.spectrum-gmbh.com/mc3132+M5d637ble38d.html. аналог. 2. VHS-ADC. High Performance Multi-Channel A/D. http://www.lyrtech.com/publications/VHSADC 16_en.pdf. - аналог. 3. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного. // Электроника: наука, технология, бизнес. - Москва. - 2004, № 8, С. 34-40. http://www.electronics.ru/pdf/82004/07.pdf. - аналог. 4. Патент України на корисну модель № 33256. G01S 13/08-13/44, G01S 7/02-7/46, H02K 15/00-15/16. Пристрій аналого-цифрового перетворення. // Слюсар В.І., Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель № u200802466 від 26.02.2008. - Патент опубліковано 10.06.2008, бюл. № 11. - прототип. 5. Патент України на корисну модель № 46666. МПК (2006) G01S 7/36, H03D 13/00. Спосіб додаткового стробування відліків аналого-цифрового перетворювача. // Слюсар В.І., Малярчук М.В. - Заявка на видачу патенту України на корисну модель № u200909210 від 07.09.2009. Патент опубліковано 25.12.2009, бюл. № 24. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 50 55 60 1. Пристрій аналого-цифрового перетворення, до складу якого входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів у складі послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої 9 UA 115691 U 5 10 15 20 25 30 35 40 45 50 55 синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрового діаграмоутворення та до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів загрузки архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування,модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину, який відрізняється тим, що до складу модуля цифрової обробки сигналів додатково введено модуль цифрової I/Q (квадратурної)-демодуляції та модуль синтезу цифрових частотних фільтрів, при цьому перша група входів модуля цифрової I/Q (квадратурної)-демодуляції є першою групою входів модуля цифрової обробки сигналів, виходи модуля цифрової I/Q (квадратурної)-демодуляції підключені до першої групи входів модуля цифрової фільтрації сигналів, шини даних модуля синтезу цифрових частотних фільтрів через модуль управління пам'яттю (входить до складу ПЛІС) підключені до шини даних модулів оперативної пам'яті, тактові входи модуля цифрової I/Q (квадратурної)-демодуляції та модуля синтезу цифрових частотних фільтрів підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової I/Q (квадратурної)-демодуляції підключені до п'ятого виходу модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля синтезу цифрових частотних фільтрів підключений до шостого виходу модуля формування сигналів синхронізації та управління. 2. Пристрій аналого-цифрового перетворення за п. 1, який відрізняється тим, що для забезпечення режиму тестування алгоритмів цифрової обробки сигналів виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля цифрової обробки сигналів у складі тієї ж ПЛІС через додатково введений до складу ПЛІС модуль комутації сигналів, при цьому до складу ПЛІС додатково введено цифровий буфер, входи якого підключені до контролера передачі даних на інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління, тактовий вхід модуля комутації сигналів підключений до першого виходу модуля формування сигналів синхронізації та управління. 3. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовується шина CompactPCI. 4. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовується шина CompactPCI Serial. 5. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси VPX. 6. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси МісrоТСА. 7. Пристрій аналого-цифрового перетворення за будь-яким з пп. 1, 2, який відрізняєтъся тим, що як інтерфейсна шина використовуються інтерфейси Ethernet 10 Гбіт/с. 10 UA 115691 U Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 11

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H02K 15/16, G01S 13/08, G01S 7/02, H02K 15/00, G01S 13/44

Мітки: перетворення, пристрій, аналого-цифрового

Код посилання

<a href="https://ua.patents.su/13-115691-pristrijj-analogo-cifrovogo-peretvorennya.html" target="_blank" rel="follow" title="База патентів України">Пристрій аналого-цифрового перетворення</a>

Попередній патент: 4-(5,7-диметил-2-оксотіазоло[4,5-b]піридин-3-іл)бутиратна кислота, що проявляє антиексудативну дію

Наступний патент: Система обробки сигналів приймальної цифрової антенної решітки

Випадковий патент: Шліфувальний інструмент