Процесор петрі

Номер патенту: 15213

Опубліковано: 30.06.1997

Автори: Матейченко Віктор Валентинович, Гуца Олег Миколайович, Маркін Олег Михайлович, Калінін Генадій Олександрович, Запорожцев Сергій Юрійович

Формула / Реферат

Процессор Петри, содержащий первый и второй блоки топологии, блок арифметико-логических устройств (АЛУ), блок хранения текущей разметки, блок приоритетного выбора и блок синхронизации, причем выходы первого блока топологии подключены ко второй группе информационных входов блока АЛУ, информационные выходы которого подключены к информационным входам блока хранения текущей разметки, выходы которого подключены к первой группе информационных входов блока АЛУ, выходы блока приоритетного выбора подключены к адресным входам первого и второго блоков топологии, отличающийся тем, что в него дополнительно введены блок ввода, информационные входы которого являются информационными входами устройства, блок вывода, выходы которого являются информационными выходами устройства, третий и четвертый блоки топологии, блок формирования постусловий, блок проверки логических условий и блок программирования, причем информационные выходы блока программирования подключены к входам программирования первого, второго, третьего и четвертого блоков топологии, второй группе входов программирования блока АЛУ, входам программирования блока приоритетного выбора и к входам программирования блока ввода, информационные выходы которого подключены к четвертой группе информационных входов блока АЛУ, третья группа информационных входов которого подключена к информационным выходам блока формирования постусловий, информационные входы которого подключены к выходам второго блока топологии, выходы блока приоритетного выбора подключены к адресным входам третьего и четвертого блоков топологии, причем выходы третьего блока топологии подключены ко второй группе входов блока проверки логических условий, третья группа входов которого подключена к выходам четвертого блока топологии, а первая группа входов блока проверки логических условий подключена к выходам блока хранения текущей разметки, которые одновременно соединены с входами блока вывода, кроме того, выход блока проверки логических условий подключен к первому управляющему входу блока хранения текущей разметки и к первому управляющему входу блока формирования постусловий, второй управляющий вход которого соединен со вторым управляющим выходом блока АЛУ и со вторым управляющим входом блока хранения текущей разметки, входы программирования которого подключены к первой группе выходов программирования блока ввода, вторая группа выходов программирования которого подключена к первой группе входов программирования блока АЛУ, первый управляющий выход которого подключен к первому управляющему входу блока синхронизации, второй управляющий вход которого подключен к управляющему выходу блока формирования постусловий.

Текст

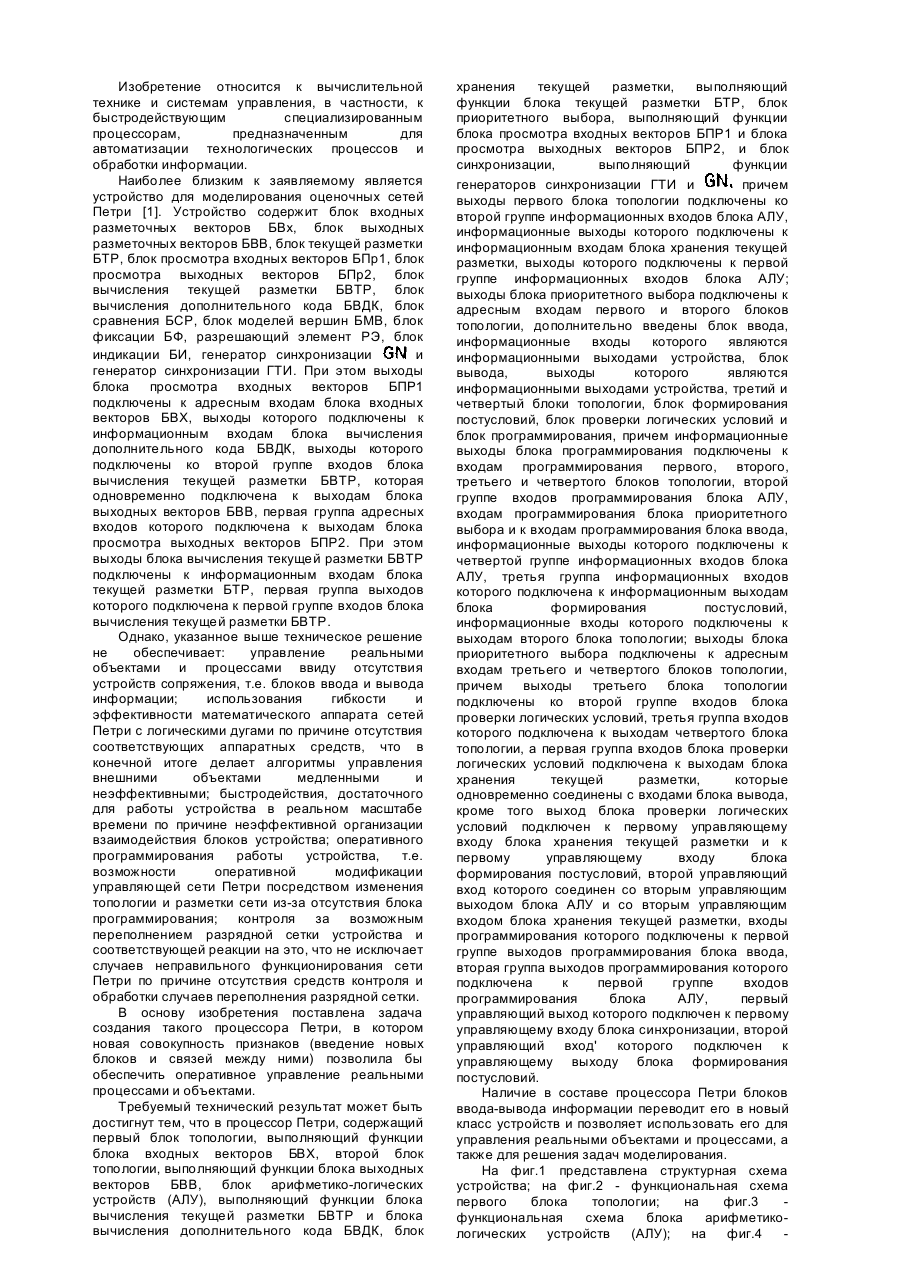

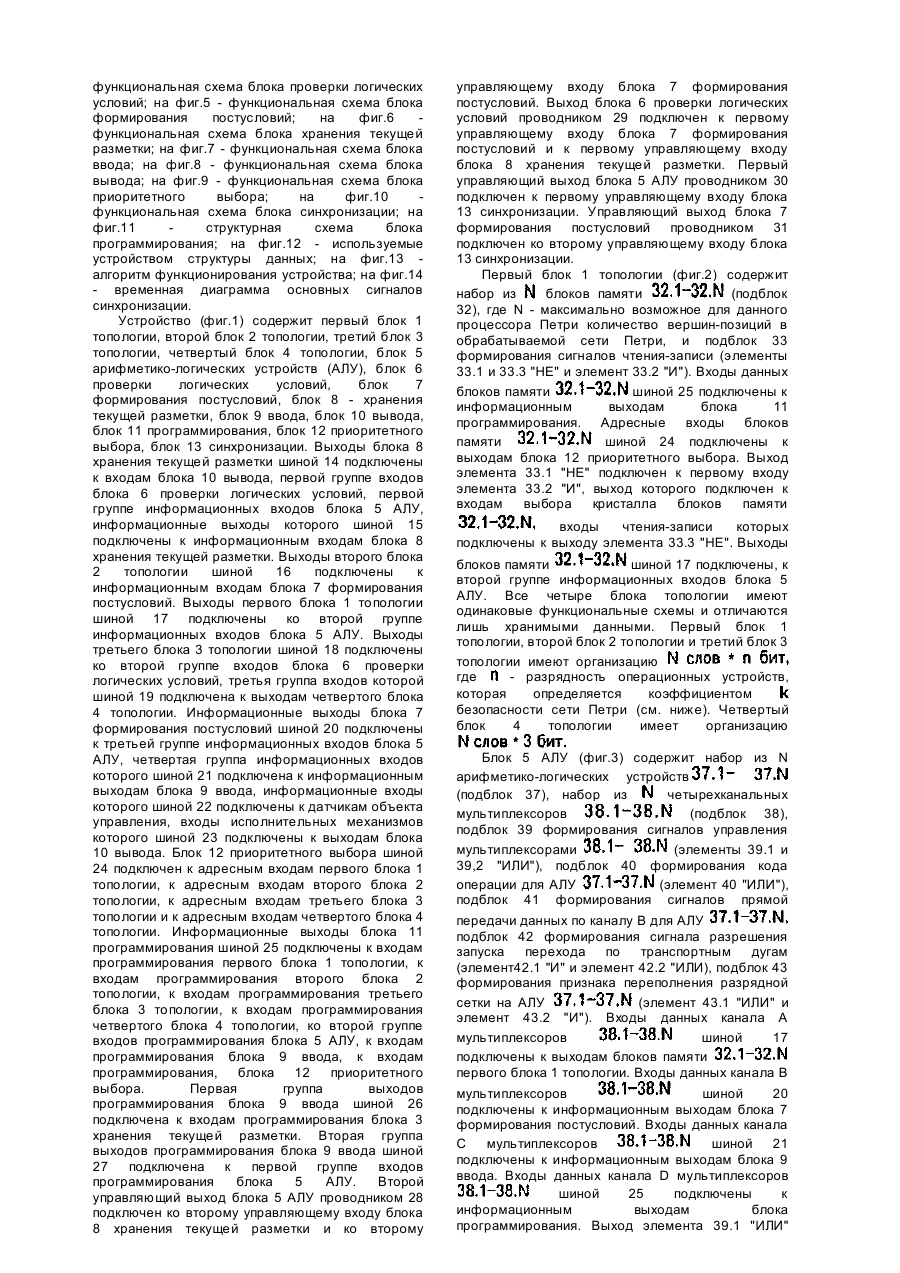

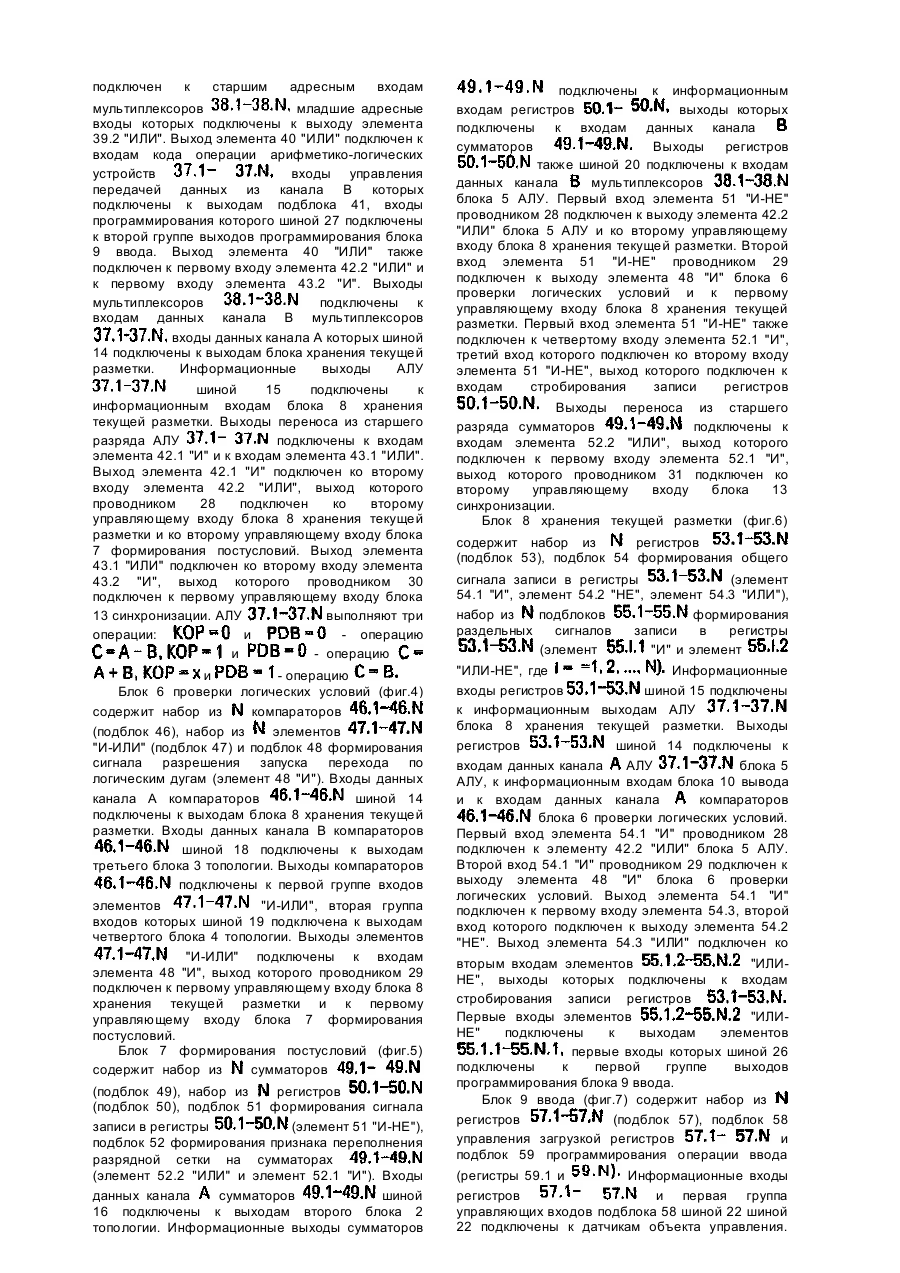

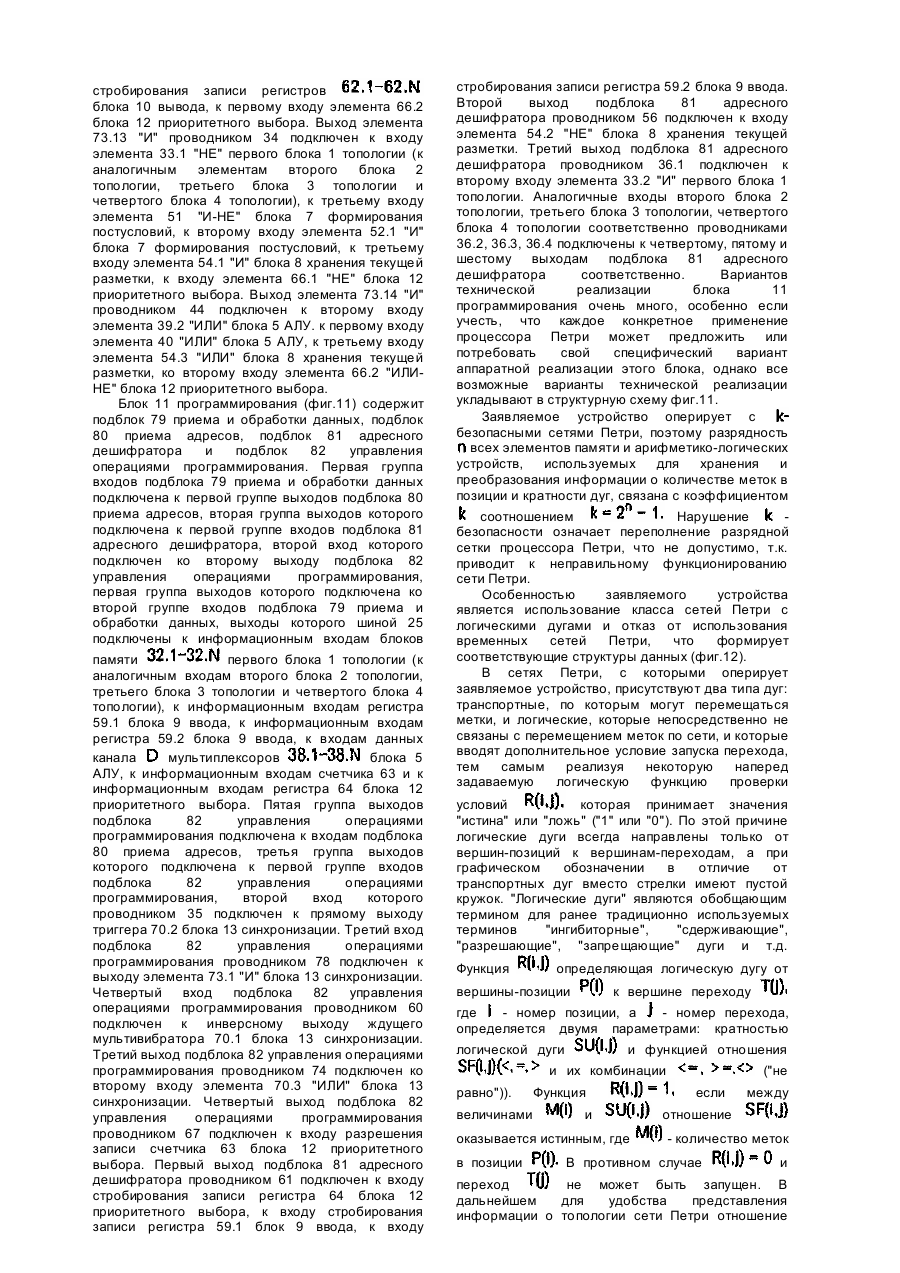

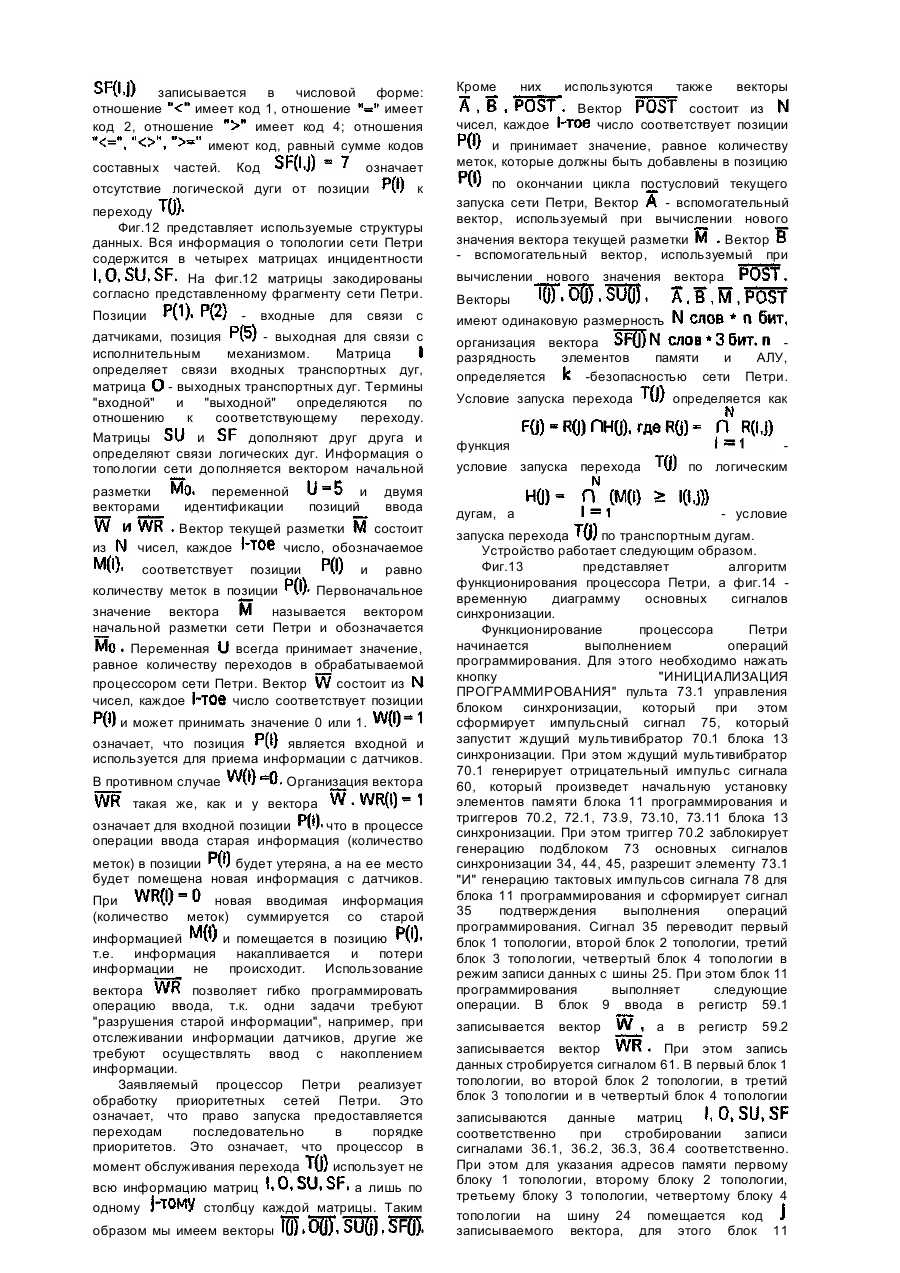

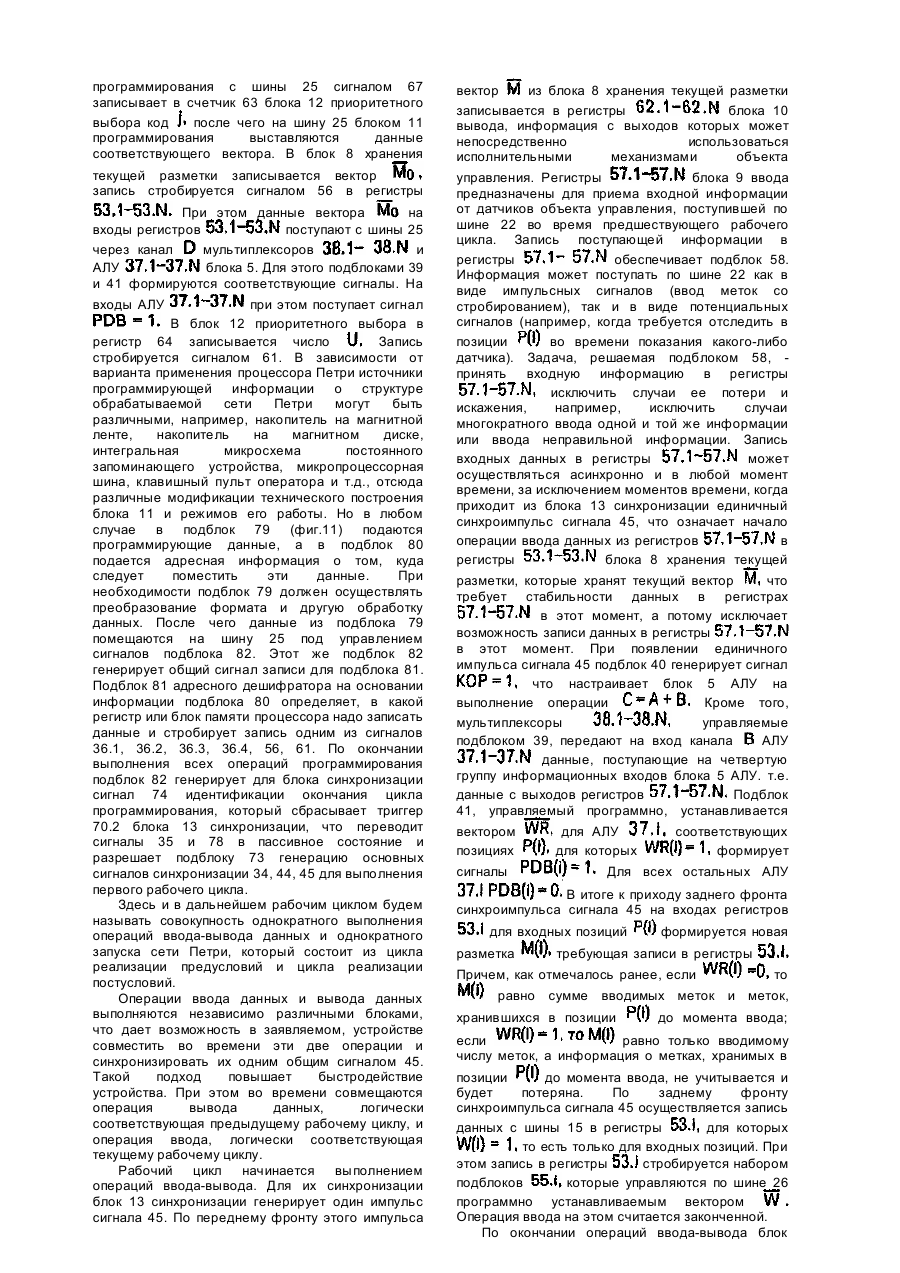

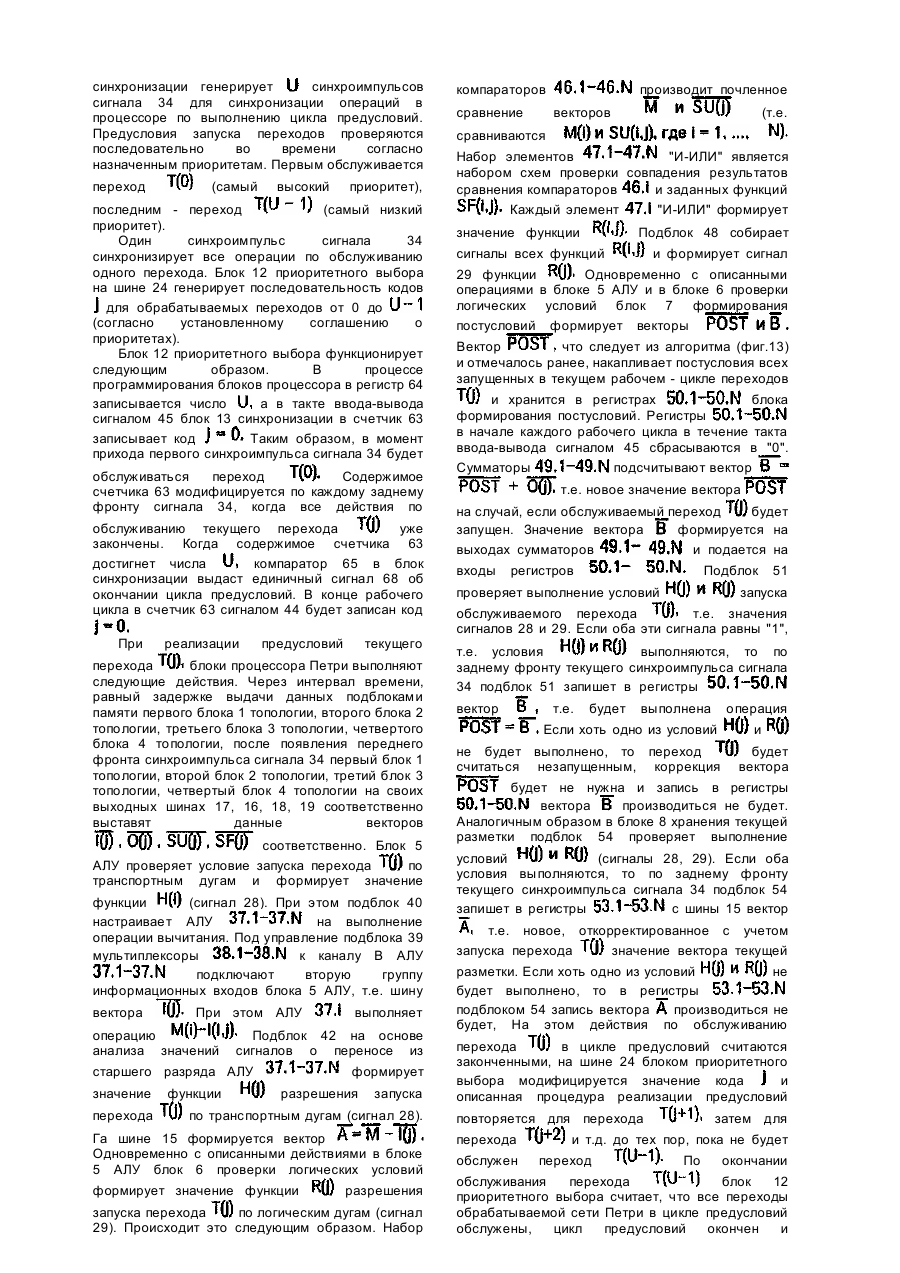

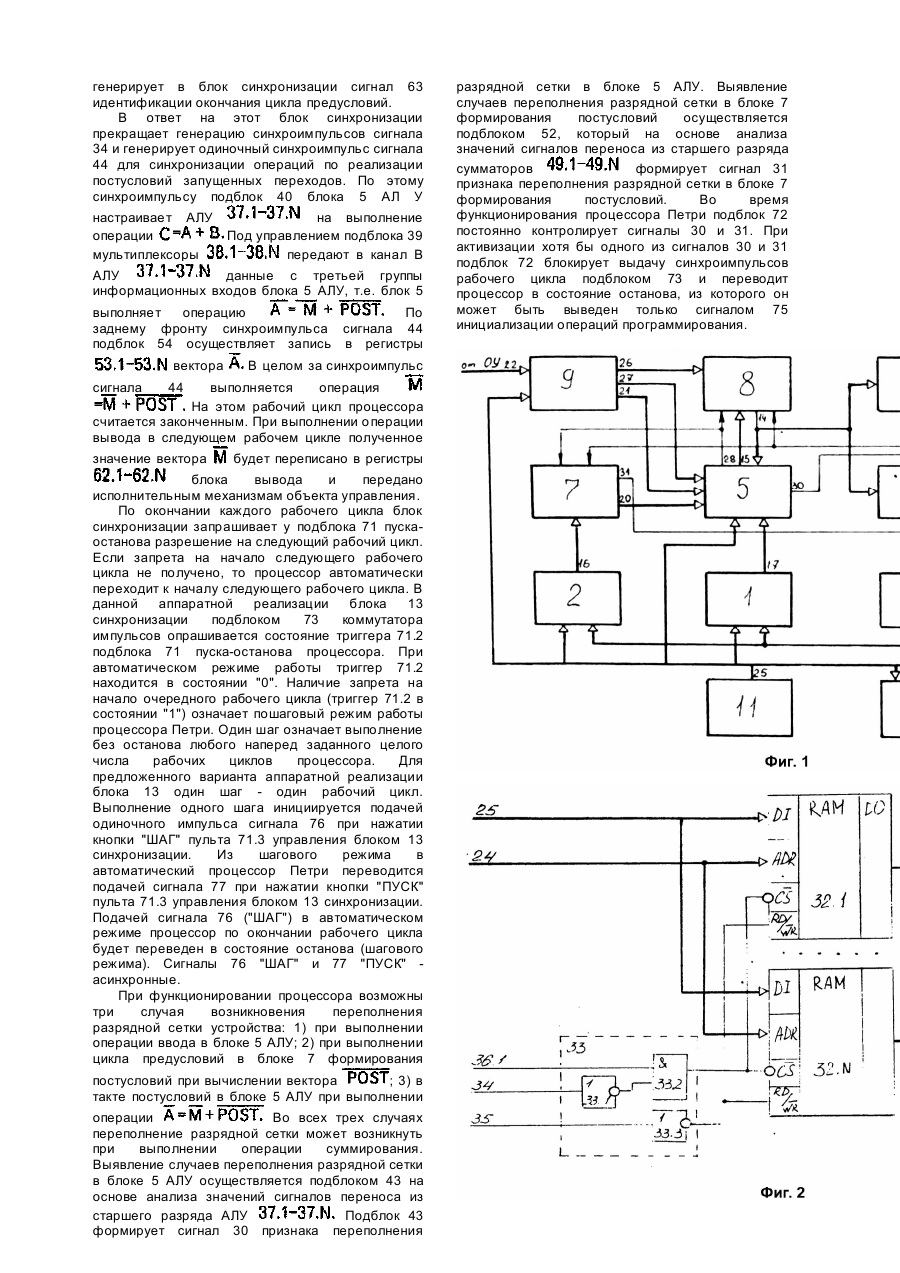

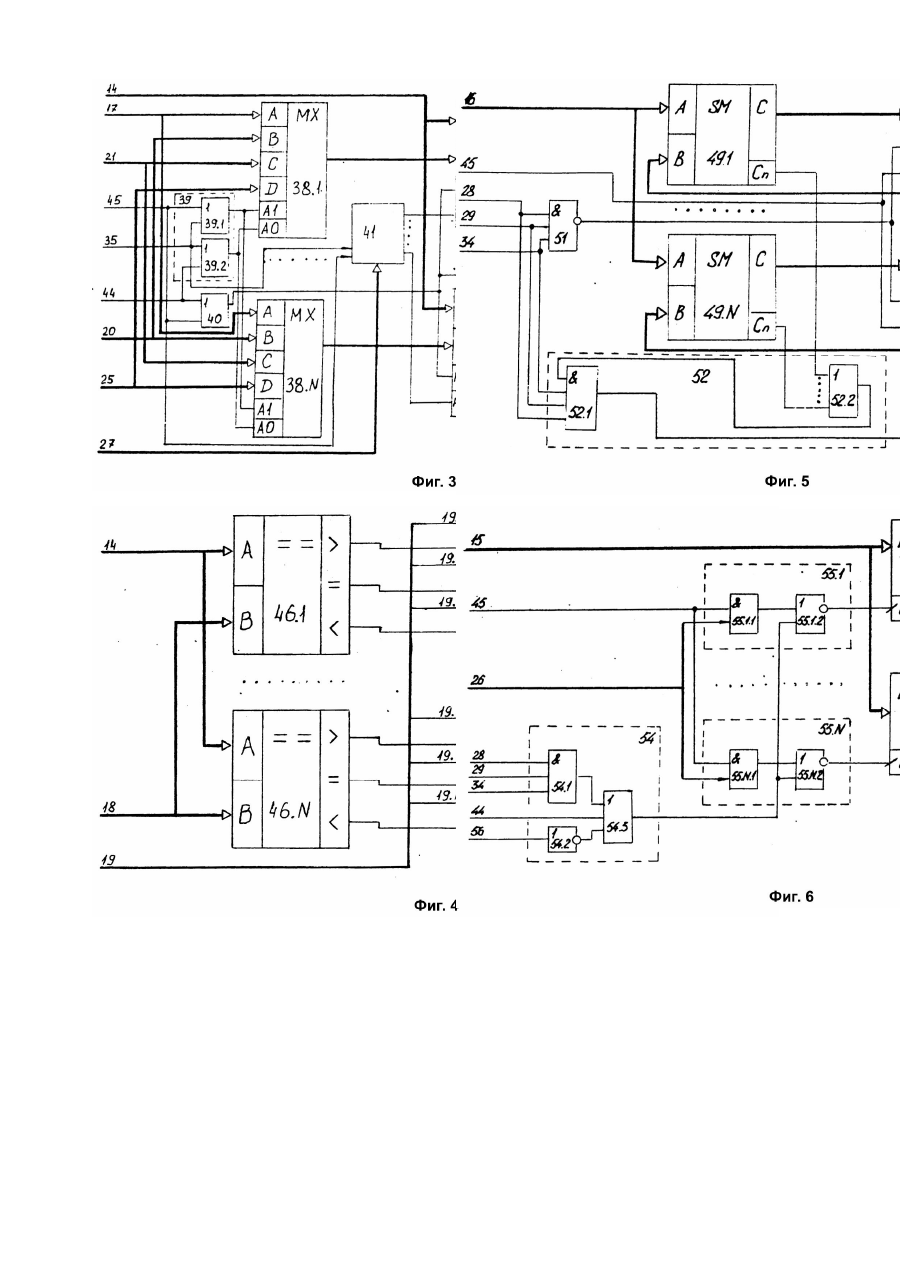

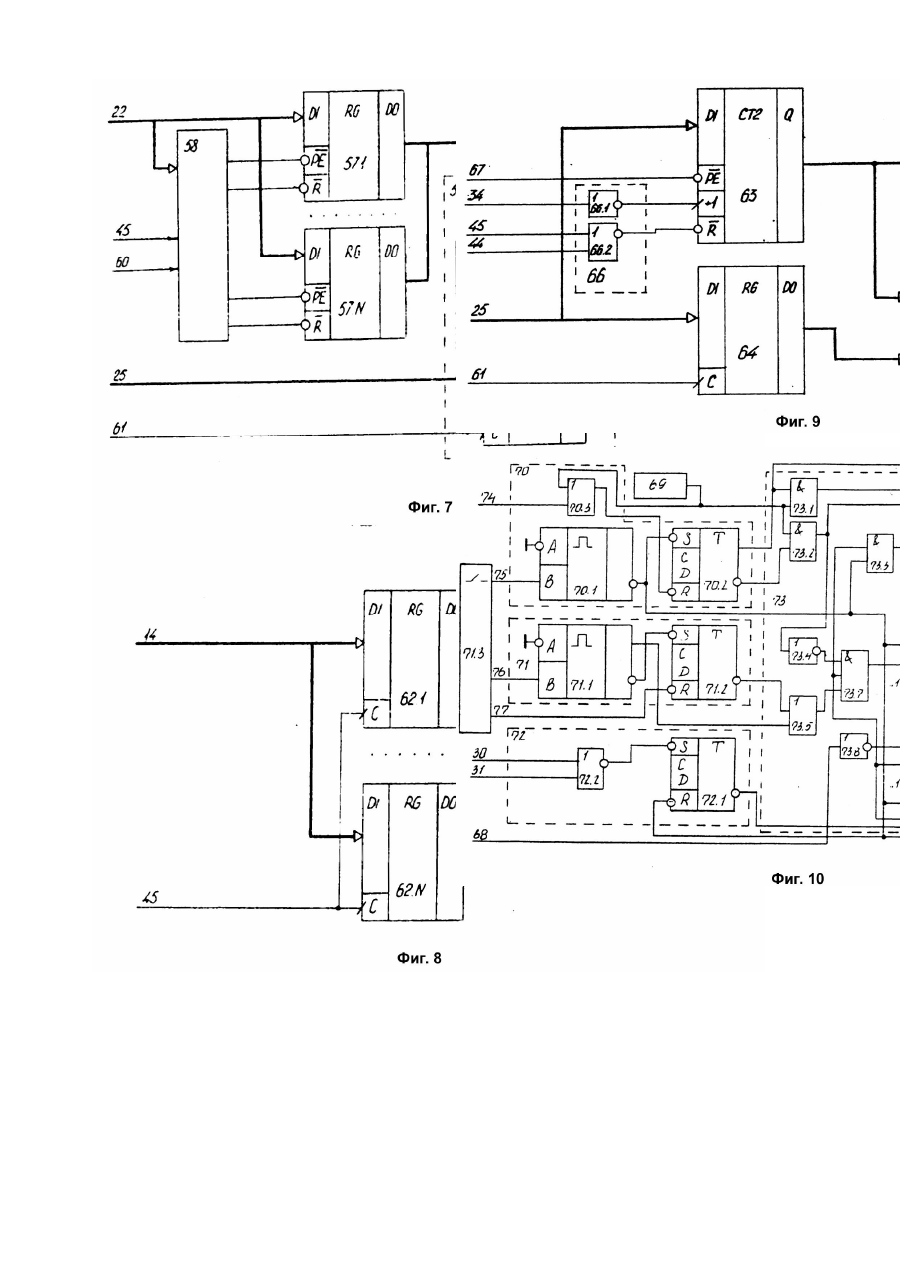

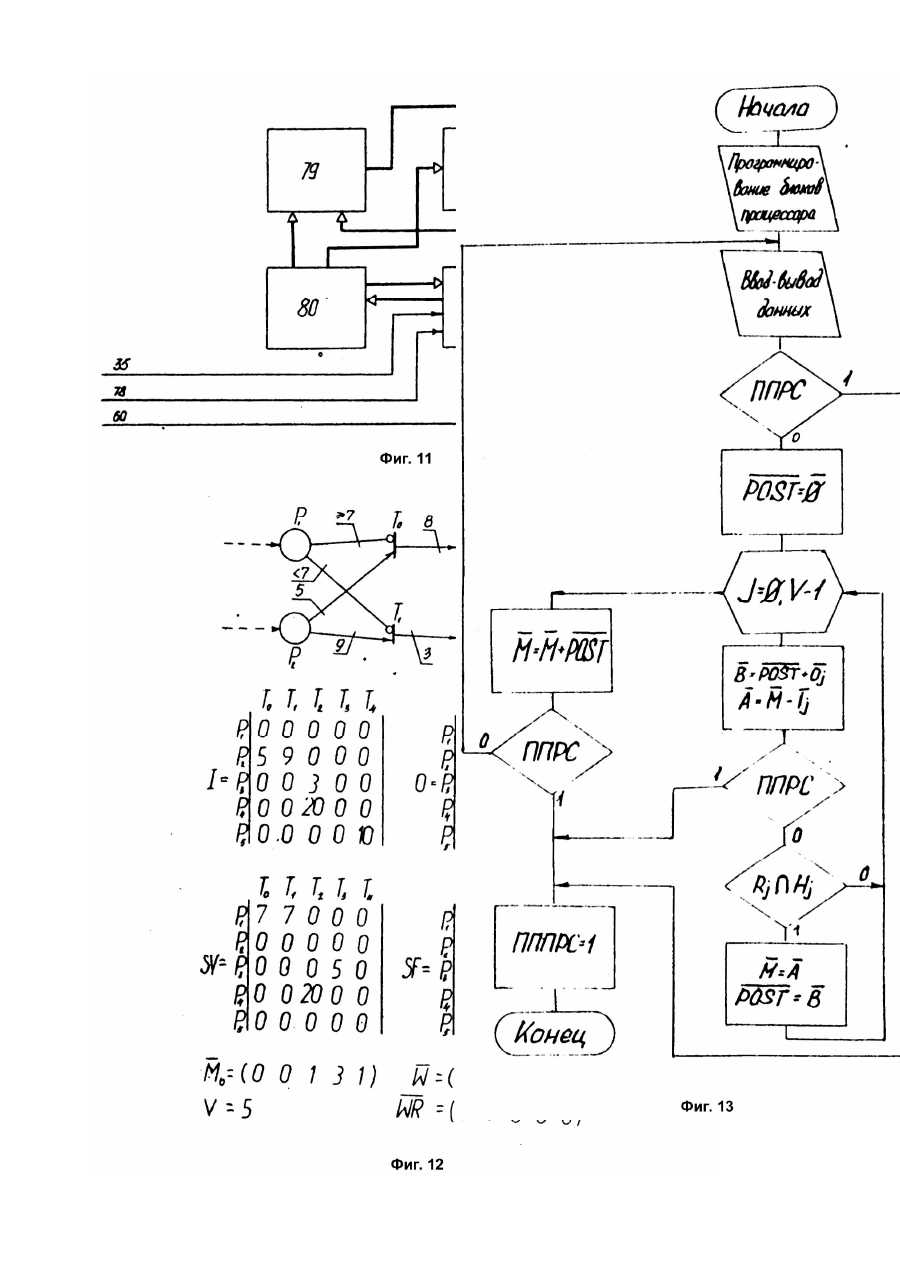

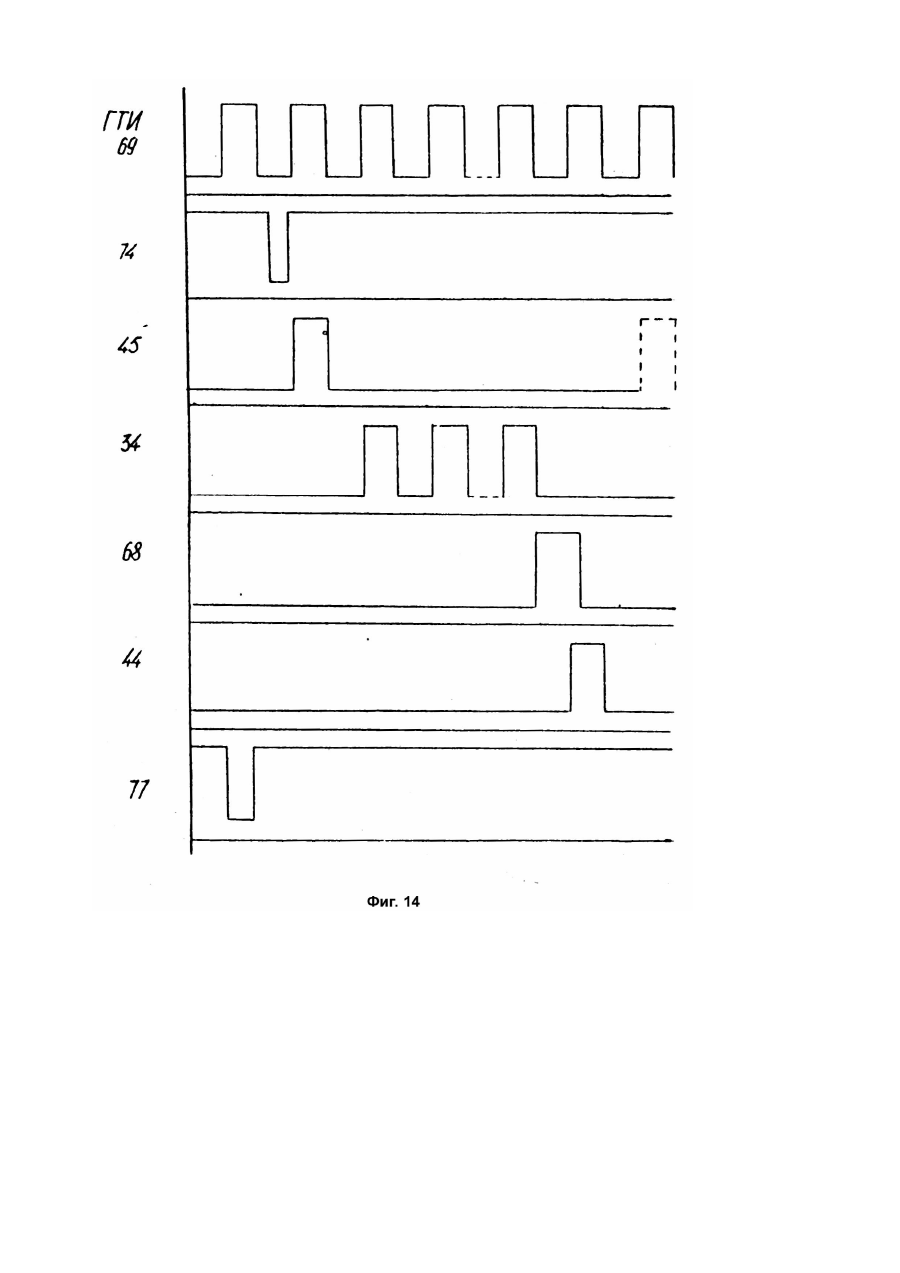

Изобретение относится к вычислительной технике и системам управления, в частности, к быстродействующим специализированным процессорам, предназначенным для автоматизации технологических процессов и обработки информации. Наиболее близким к заявляемому является устройство для моделирования оценочных сетей Петри [1]. Устройство содержит блок входных разметочных векторов БВх, блок выходных разметочных векторов БВВ, блок текущей разметки БТР, блок просмотра входных векторов БПр1, блок просмотра выходных векторов БПр2, блок вычисления текущей разметки БВТР, блок вычисления дополнительного кода БВДК, блок сравнения БСР, блок моделей вершин БМВ, блок фиксации БФ, разрешающий элемент РЭ, блок индикации БИ, генератор синхронизации и генератор синхронизации ГТИ. При этом выходы блока просмотра входных векторов БПР1 подключены к адресным входам блока входных векторов БВХ, выходы которого подключены к информационным входам блока вычисления дополнительного кода БВДК, выходы которого подключены ко второй группе входов блока вычисления текущей разметки БВТР, которая одновременно подключена к выходам блока выходных векторов БВВ, первая группа адресных входов которого подключена к выходам блока просмотра выходных векторов БПР2. При этом выходы блока вычисления текущей разметки БВТР подключены к информационным входам блока текущей разметки БТР, первая группа выходов которого подключена к первой группе входов блока вычисления текущей разметки БВТР. Однако, указанное выше техническое решение не обеспечивает: управление реальными объектами и процессами ввиду отсутствия устройств сопряжения, т.е. блоков ввода и вывода информации; использования гибкости и эффективности математического аппарата сетей Петри с логическими дугами по причине отсутствия соответствующих аппаратных средств, что в конечной итоге делает алгоритмы управления внешними объектами медленными и неэффективными; быстродействия, достаточного для работы устройства в реальном масштабе времени по причине неэффективной организации взаимодействия блоков устройства; оперативного программирования работы устройства, т.е. возможности оперативной модификации управляющей сети Петри посредством изменения топологии и разметки сети из-за отсутствия блока программирования; контроля за возможным переполнением разрядной сетки устройства и соответствующей реакции на это, что не исключает случаев неправильного функционирования сети Петри по причине отсутствия средств контроля и обработки случаев переполнения разрядной сетки. В основу изобретения поставлена задача создания такого процессора Петри, в котором новая совокупность признаков (введение новых блоков и связей между ними) позволила бы обеспечить оперативное управление реальными процессами и объектами. Требуемый технический результат может быть достигнут тем, что в процессор Петри, содержащий первый блок топологии, выполняющий функции блока входных векторов БВХ, второй блок топологии, выполняющий функции блока выходных векторов БВВ, блок арифметико-логических устройств (АЛУ), выполняющий функции блока вычисления текущей разметки БВТР и блока вычисления дополнительного кода БВДК, блок хранения текущей разметки, выполняющий функции блока текущей разметки БТР, блок приоритетного выбора, выполняющий функции блока просмотра входных векторов БПР1 и блока просмотра выходных векторов БПР2, и блок синхронизации, выполняющий функции генераторов синхронизации ГТИ и причем выходы первого блока топологии подключены ко второй группе информационных входов блока АЛУ, информационные выходы которого подключены к информационным входам блока хранения текущей разметки, выходы которого подключены к первой группе информационных входов блока АЛУ; выходы блока приоритетного выбора подключены к адресным входам первого и второго блоков топологии, дополнительно введены блок ввода, информационные входы которого являются информационными выходами устройства, блок вывода, выходы которого являются информационными выходами устройства, третий и четвертый блоки топологии, блок формирования постусловий, блок проверки логических условий и блок программирования, причем информационные выходы блока программирования подключены к входам программирования первого, второго, третьего и четвертого блоков топологии, второй группе входов программирования блока АЛУ, входам программирования блока приоритетного выбора и к входам программирования блока ввода, информационные выходы которого подключены к четвертой группе информационных входов блока АЛУ, третья группа информационных входов которого подключена к информационным выходам блока формирования постусловий, информационные входы которого подключены к выходам второго блока топологии; выходы блока приоритетного выбора подключены к адресным входам третьего и четвертого блоков топологии, причем выходы третьего блока топологии подключены ко второй группе входов блока проверки логических условий, третья группа входов которого подключена к выходам четвертого блока топологии, а первая группа входов блока проверки логических условий подключена к выходам блока хранения текущей разметки, которые одновременно соединены с входами блока вывода, кроме того выход блока проверки логических условий подключен к первому управляющему входу блока хранения текущей разметки и к первому управляющему входу блока формирования постусловий, второй управляющий вход которого соединен со вторым управляющим выходом блока АЛУ и со вторым управляющим входом блока хранения текущей разметки, входы программирования которого подключены к первой группе выходов программирования блока ввода, вторая группа выходов программирования которого подключена к первой группе входов программирования блока АЛУ, первый управляющий выход которого подключен к первому управляющему входу блока синхронизации, второй управляющий вход' которого подключен к управляющему выходу блока формирования постусловий. Наличие в составе процессора Петри блоков ввода-вывода информации переводит его в новый класс устройств и позволяет использовать его для управления реальными объектами и процессами, а также для решения задач моделирования. На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема первого блока топологии; на фиг.3 функциональная схема блока арифметикологических устройств (АЛУ); на фиг.4 функциональная схема блока проверки логических условий; на фиг.5 - функциональная схема блока формирования постусловий; на фиг.6 функциональная схема блока хранения текущей разметки; на фиг.7 - функциональная схема блока ввода; на фиг.8 - функциональная схема блока вывода; на фиг.9 - функциональная схема блока приоритетного выбора; на фиг.10 функциональная схема блока синхронизации; на фиг.11 структурная схема блока программирования; на фиг.12 - используемые устройством структуры данных; на фиг.13 алгоритм функционирования устройства; на фиг.14 - временная диаграмма основных сигналов синхронизации. Устройство (фиг.1) содержит первый блок 1 топологии, второй блок 2 топологии, третий блок 3 топологии, четвертый блок 4 топологии, блок 5 арифметико-логических устройств (АЛУ), блок 6 проверки логических условий, блок 7 формирования постусловий, блок 8 - хранения текущей разметки, блок 9 ввода, блок 10 вывода, блок 11 программирования, блок 12 приоритетного выбора, блок 13 синхронизации. Выходы блока 8 хранения текущей разметки шиной 14 подключены к входам блока 10 вывода, первой группе входов блока 6 проверки логических условий, первой группе информационных входов блока 5 АЛУ, информационные выходы которого шиной 15 подключены к информационным входам блока 8 хранения текущей разметки. Выходы второго блока 2 топологии шиной 16 подключены к информационным входам блока 7 формирования постусловий. Выходы первого блока 1 топологии шиной 17 подключены ко второй группе информационных входов блока 5 АЛУ. Выходы третьего блока 3 топологии шиной 18 подключены ко второй группе входов блока 6 проверки логических условий, третья группа входов которой шиной 19 подключена к выходам четвертого блока 4 топологии. Информационные выходы блока 7 формирования постусловий шиной 20 подключены к третьей группе информационных входов блока 5 АЛУ, четвертая группа информационных входов которого шиной 21 подключена к информационным выходам блока 9 ввода, информационные входы которого шиной 22 подключены к датчикам объекта управления, входы исполнительных механизмов которого шиной 23 подключены к выходам блока 10 вывода. Блок 12 приоритетного выбора шиной 24 подключен к адресным входам первого блока 1 топологии, к адресным входам второго блока 2 топологии, к адресным входам третьего блока 3 топологии и к адресным входам четвертого блока 4 топологии. Информационные выходы блока 11 программирования шиной 25 подключены к входам программирования первого блока 1 топологии, к входам программирования второго блока 2 топологии, к входам программирования третьего блока 3 топологии, к входам программирования четвертого блока 4 топологии, ко второй группе входов программирования блока 5 АЛУ, к входам программирования блока 9 ввода, к входам программирования, блока 12 приоритетного выбора. Первая группа выходов программирования блока 9 ввода шиной 26 подключена к входам программирования блока 3 хранения текущей разметки. Вторая группа выходов программирования блока 9 ввода шиной 27 подключена к первой группе входов программирования блока 5 АЛУ. Второй управляющий выход блока 5 АЛУ проводником 28 подключен ко второму управляющему входу блока 8 хранения текущей разметки и ко второму управляющему входу блока 7 формирования постусловий. Выход блока 6 проверки логических условий проводником 29 подключен к первому управляющему входу блока 7 формирования постусловий и к первому управляющему входу блока 8 хранения текущей разметки. Первый управляющий выход блока 5 АЛУ проводником 30 подключен к первому управляющему входу блока 13 синхронизации. Управляющий выход блока 7 формирования постусловий проводником 31 подключен ко второму управляющему входу блока 13 синхронизации. Первый блок 1 топологии (фиг.2) содержит набор из блоков памяти (подблок 32), где N - максимально возможное для данного процессора Петри количество вершин-позиций в обрабатываемой сети Петри, и подблок 33 формирования сигналов чтения-записи (элементы 33.1 и 33.3 "НЕ" и элемент 33.2 "И"). Входы данных блоков памяти шиной 25 подключены к информационным выходам блока 11 программирования. Адресные входы блоков памяти шиной 24 подключены к выходам блока 12 приоритетного выбора. Выход элемента 33.1 "НЕ" подключен к первому входу элемента 33.2 "И", выход которого подключен к входам выбора кристалла блоков памяти входы чтения-записи которых подключены к выходу элемента 33.3 "НЕ". Выходы блоков памяти шиной 17 подключены, к второй группе информационных входов блока 5 АЛУ. Все четыре блока топологии имеют одинаковые функциональные схемы и отличаются лишь хранимыми данными. Первый блок 1 топологии, второй блок 2 топологии и третий блок 3 топологии имеют организацию где - разрядность операционных устройств, которая определяется коэффициентом безопасности сети Петри (см. ниже). Четвертый блок 4 топологии имеет организацию Блок 5 АЛУ (фиг.3) содержит набор из N арифметико-логических устройств (подблок 37), набор из четырехканальных мультиплексоров (подблок 38), подблок 39 формирования сигналов управления мультиплексорами (элементы 39.1 и 39,2 "ИЛИ"), подблок 40 формирования кода операции для АЛУ (элемент 40 "ИЛИ"), подблок 41 формирования сигналов прямой передачи данных по каналу B для АЛУ подблок 42 формирования сигнала разрешения запуска перехода по транспортным дугам (элемент42.1 "И" и элемент 42.2 "ИЛИ), подблок 43 формирования признака переполнения разрядной сетки на АЛУ (элемент 43.1 "ИЛИ" и элемент 43.2 "И"). Входы данных канала A мультиплексоров шиной 17 подключены к выходам блоков памяти первого блока 1 топологии. Входы данных канала B мультиплексоров шиной 20 подключены к информационным выходам блока 7 формирования постусловий. Входы данных канала C мультиплексоров шиной 21 подключены к информационным выходам блока 9 ввода. Входы данных канала D мультиплексоров шиной 25 подключены к информационным выходам блока программирования. Выход элемента 39.1 "ИЛИ" подключен к старшим адресным входам мультиплексоров младшие адресные входы которых подключены к выходу элемента 39.2 "ИЛИ". Выход элемента 40 "ИЛИ" подключен к входам кода операции арифметико-логических устройств входы управления передачей данных из канала B которых подключены к выходам подблока 41, входы программирования которого шиной 27 подключены к второй группе выходов программирования блока 9 ввода. Выход элемента 40 "ИЛИ" также подключен к первому входу элемента 42.2 "ИЛИ" и к первому входу элемента 43.2 "И". Выходы мультиплексоров подключены к входам данных канала B мультиплексоров входы данных канала A которых шиной 14 подключены к выходам блока хранения текущей разметки. Информационные выходы АЛУ шиной 15 подключены к информационным входам блока 8 хранения текущей разметки. Выходы переноса из старшего разряда АЛУ подключены к входам элемента 42.1 "И" и к входам элемента 43.1 "ИЛИ". Выход элемента 42.1 "И" подключен ко второму входу элемента 42.2 "ИЛИ", выход которого проводником 28 подключен ко второму управляющему входу блока 8 хранения текущей разметки и ко второму управляющему входу блока 7 формирования постусловий. Выход элемента 43.1 "ИЛИ" подключен ко второму входу элемента 43.2 "И", выход которого проводником 30 подключен к первому управляющему входу блока 13 синхронизации. АЛУ выполняют три операции: и - операцию и - операцию и - операцию Блок 6 проверки логических условий (фиг.4) содержит набор из компараторов (подблок 46), набор из элементов "И-ИЛИ" (подблок 47) и подблок 48 формирования сигнала разрешения запуска перехода по логическим дугам (элемент 48 "И"). Входы данных канала A компараторов шиной 14 подключены к выходам блока 8 хранения текущей разметки. Входы данных канала B компараторов шиной 18 подключены к выходам третьего блока 3 топологии. Выходы компараторов подключены к первой группе входов элементов "И-ИЛИ", вторая группа входов которых шиной 19 подключена к выходам четвертого блока 4 топологии. Выходы элементов "И-ИЛИ" подключены к входам элемента 48 "И", выход которого проводником 29 подключен к первому управляющему входу блока 8 хранения текущей разметки и к первому управляющему входу блока 7 формирования постусловий. Блок 7 формирования постусловий (фиг.5) содержит набор из сумматоров (подблок 49), набор из регистров (подблок 50), подблок 51 формирования сигнала записи в регистры (элемент 51 "И-НЕ"), подблок 52 формирования признака переполнения разрядной сетки на сумматорах (элемент 52.2 "ИЛИ" и элемент 52.1 "И"). Входы данных канала сумматоров шиной 16 подключены к выходам второго блока 2 топологии. Информационные выходы сумматоров подключены к информационным входам регистров выходы которых подключены к входам данных канала сумматоров Выходы регистров также шиной 20 подключены к входам данных канала мультиплексоров блока 5 АЛУ. Первый вход элемента 51 "И-НЕ" проводником 28 подключен к выходу элемента 42.2 "ИЛИ" блока 5 АЛУ и ко второму управляющему входу блока 8 хранения текущей разметки. Второй вход элемента 51 "И-НЕ" проводником 29 подключен к выходу элемента 48 "И" блока 6 проверки логических условий и к первому управляющему входу блока 8 хранения текущей разметки. Первый вход элемента 51 "И-НЕ" также подключен к четвертому входу элемента 52.1 "И", третий вход которого подключен ко второму входу элемента 51 "И-НЕ", выход которого подключен к входам стробирования записи регистров Выходы переноса из старшего разряда сумматоров подключены к входам элемента 52.2 "ИЛИ", выход которого подключен к первому входу элемента 52.1 "И", выход которого проводником 31 подключен ко второму управляющему входу блока 13 синхронизации. Блок 8 хранения текущей разметки (фиг.6) содержит набор из регистров (подблок 53), подблок 54 формирования общего сигнала записи в регистры (элемент 54.1 "И", элемент 54.2 "НЕ", элемент 54.3 "ИЛИ"), набор из подблоков формирования раздельных сигналов записи в регистры (элемент "И" и элемент "ИЛИ-НЕ", где Информационные входы регистров шиной 15 подключены к информационным выходам АЛУ блока 8 хранения текущей разметки. Выходы регистров шиной 14 подключены к входам данных канала АЛУ блока 5 АЛУ, к информационным входам блока 10 вывода и к входам данных канала компараторов блока 6 проверки логических условий. Первый вход элемента 54.1 "И" проводником 28 подключен к элементу 42.2 "ИЛИ" блока 5 АЛУ. Второй вход 54.1 "И" проводником 29 подключен к выходу элемента 48 "И" блока 6 проверки логических условий. Выход элемента 54.1 "И" подключен к первому входу элемента 54.3, второй вход которого подключен к выходу элемента 54.2 "НЕ". Выход элемента 54.3 "ИЛИ" подключен ко вторым входам элементов "ИЛИНЕ", выходы которых подключены к входам стробирования записи регистров Первые входы элементов "ИЛИНЕ" подключены к выходам элементов первые входы которых шиной 26 подключены к первой группе выходов программирования блока 9 ввода. Блок 9 ввода (фиг.7) содержит набор из регистров (подблок 57), подблок 58 управления загрузкой регистров и подблок 59 программирования операции ввода (регистры 59.1 и Информационные входы регистров и первая группа управляющих входов подблока 58 шиной 22 шиной 22 подключены к датчикам объекта управления. Выходы регистров шиной 21 подключены к входам данных канала мультиплексоров блока 5 АЛУ. Входы разрешения параллельной загрузки данных регистров подключены к первой группе выходов подблока 58, вторая группа выходов которого подключена к входам установки в "0" регистров Информационные входы регистра 59.1 и регистра 59.2 шиной 25 подключены к информационным выходам блока 11 программирования. Выходы регистра 59.1 шиной 26 подключены к первым входам элементов "И" блока 8 хранения текущей разметки. Выходы регистра 59.2 шиной 27 подключены к входам программирования подблока 41 блока 5 АЛУ. Блок 10 вывода (фиг.8) содержит набор из регистров информационные входы которых шиной 14 подключены к выходам регистров блока 8 хранения текущей разметки. Выходы регистров шиной 23 подключены к входам исполнительных механизмов объекта управления. Блок 12 приоритетного выбора (фиг.9) состоит из счетчика 63, регистра 64, компаратора 65 и подблока 66 управления работой счетчика 63 (элемент 66.1 "НЕ" и элемент 66.2 "ИЛИ-НЕ"). Информационные входы счетчика 63 и информационные входы регистра 64 шиной 25 подключены к информационным выходам блока 11 программирования. Выход элемента 66.1 "НЕ" подключен к счетному входу "+1" счетчика 63, вход установки в "0" которого подключен к выходу элемента 66.2 "ИЛИ-НЕ". Выходы регистра 64 подключены к входам данных канала компаратора 65, входы данных канала которого подключены к выходам счетчика 63, которые шиной 24 подключены к адресным входам блоков памяти первого блока 1 топологии и аналогичным образом к адресным входам второго блока 2 топологии, к адресным входам третьего блока 3 топологии, к адресным входам четвертого блока 4 топологии. Блок 13 синхронизации (фиг.10) состоит из генератора тактовых импульсов 69, подблока 70 инициализации программирования (ждущий мультивибратор 70.1, триггер 70.2, элемент 70.3 "ИЛИ"), подблока 71, пуска-останова процессора (ждущий мультивибратор 71.1, триггер 71.2, пульт 71.3 управления блоком синхронизации, содержащий набор из трех кнопок "ПУСК", "ШАГ", "ИНИЦИАЛИЗАЦИЯ ПРОГРАММИРОВАНИЯ" и схем устранения эффекта дребезга из контактов), подблок 72 контроля переполнения разрядной сетки (триггер 72.1, элемент 72.2 "ИЛИ-НЕ") и подблок 73 коммутатора импульсов (элементы 73.1, 73.2, 73.3, 73.7, 73.12, 73.13, 73.14 "И", элементы 73.4, 73.6, 73.8, 73.15 "НЕ", элемент 73.5 "ИЛИ" и триггеры 73.9, 73.10, 73.11). Выход генератора тактовых импульсов 69 подключен к первому входу элемента 70.3 "ИЛИ", ко второму входу элемента 73.1 "И", к первому входу элемента 73.2 "И". Выход элемента 70.3 "ИЛИ" подключен к входу сброса триггера 70.2, инверсный выход которого подключен ко второму входу элемента 73.2 "И". Прямой выход триггера 70.2 подключен к первому входу элемента 73.1 "И", к входу элемента 33.1 "НЕ" первого блока 1 топологии (к аналогичным элементам второго блока 2 топологии, третьего блока 3 топологии и четвертого блока 4 топологии), ко второму входу элемента 39.1 "ИЛИ" блока 5 АЛУ, к первому входу элемента 39.2 "ИЛИ" блока 5 АЛУ, к первому входу подблока 41 блока 5 АЛУ. Прямой вход запуска ждущего мультивибратора 70.1 проводником 75 подключен к первому выходу пульта 71.3 управления блоком 13 синхронизации. Инверсный выход ждущего мультивибратора 70.1 подключен к входу установки триггера 70.2, к первому входу элемента 73.3 "И", к входу сброса триггера 72.1, к входу сброса триггера 73.11, к входу установки триггера 73.10. Кроме того, инверсный выход ждущего мультивибратора 70.1 проводником 60 подключен к третьему входу подблока 58 блока 9 ввода. Прямой вход запуска ждущего мультивибратора 71.1 проводником 76 подключен ко второму выходу пульта 71.3 управления блоком 13 синхронизации, к третьему выходу которого также подключен проводником 77 вход сброса триггера 71.2. Инверсный выход ждущего мультивибратора 71.1 подключен к входу установки триггера 71.2, инверсный выход которого подключен ко второму входу элемента 73.5 "ИЛИ", первый вход которого подключен к прямому выходу ждущего мультивибратора 71.1. Первый вход элемента 72.2 "ИЛИ-НЕ" проводником 30 подключен к выходу элемента 43.2 "И" блока 5 АЛУ. Второй вход элемента 72.2 "ИЛИ-НЕ" проводником 31 подключен к выходу элемента 52.1 "И" блока 7 формирования постусловий. Выход элемента 72.2 "ИЛИ-НЕ" подключен к входу установки триггера 72.1, инверсный выход которого подключен к третьему входу элемента 73.14 "И", к четвертому входу элемента 73.13 "И", к четвертому входу элемента 73.12 "И", второй вход которого подключен к прямому выходу триггера 73.9, инверсный выход которого подключен ко второму входу элемента 73.13 "И", третий вход которого подключен к третьему входу элемента 73.12 "И" и к прямому выходу триггера 73.10. Инверсный выход триггера 73.11 подключен ко второму входу элемента 73.14 "И", первый вход которого подключен к первому входу элемента 73.13 "И", к первому входу элемента 73.12 "И", к выходу элемента 73.2 "И", ко входу элемента 73.4 "НЕ", выход которого подключен к первому входу элемента 73.7 "И", второй вход которого подключен ко второму входу элемента 73.3 "И", к входу стробирования триггера 73.11, к выходу элемента 73.15 "НЕ", вход которого подключен к выходу элемента 73.14 "И". Третий вход элемента 73.7 "И" подключен к выходу элемента 73.5 "ИЛИ". Выход элемента 73.7 "И" подключен к входу стробирования триггера 73.10, вход сброса которого подключен к входу установки триггера 73.11 и к выходу элемента 73.8 "НЕ", вход которого проводником 68 подключен к выходу "=" компаратора 65 блока 12 приоритетного выбора. Выход элемента 73.3 "И" подключен к входу установки триггера 73.9, вход стробирования которого подключен к выходу элемента 73.6 "НЕ", вход которого подключен к выходу элемента 73.12 "И". К общему проводу подключен вход данных триггера 73.9. К положительному проводу питания подключены вход данных триггера 73.10 и вход данных триггера 73.11. Выход элемента 73.12 "И" проводником 45 подключен к первому входу элемента 39.1 "ИЛИ", ко второму входу элемента 40 "ИЛИ" блока 5 АЛУ, ко второму входу подблока 41 блока 5 АЛУ, к входам установки в "0" регистров блока 7 формирования постусловий, ко вторым входам элементов блока 8 хранения текущей разметки, ко второму входу подблока 58 блока 9 ввода, к входам стробирования записи регистров блока 10 вывода, к первому входу элемента 66.2 блока 12 приоритетного выбора. Выход элемента 73.13 "И" проводником 34 подключен к входу элемента 33.1 "НЕ" первого блока 1 топологии (к аналогичным элементам второго блока 2 топологии, третьего блока 3 топологии и четвертого блока 4 топологии), к третьему входу элемента 51 "И-НЕ" блока 7 формирования постусловий, к второму входу элемента 52.1 "И" блока 7 формирования постусловий, к третьему входу элемента 54.1 "И" блока 8 хранения текущей разметки, к входу элемента 66.1 "НЕ" блока 12 приоритетного выбора. Выход элемента 73.14 "И" проводником 44 подключен к второму входу элемента 39.2 "ИЛИ" блока 5 АЛУ. к первому входу элемента 40 "ИЛИ" блока 5 АЛУ, к третьему входу элемента 54.3 "ИЛИ" блока 8 хранения текущей разметки, ко второму входу элемента 66.2 "ИЛИНЕ" блока 12 приоритетного выбора. Блок 11 программирования (фиг.11) содержит подблок 79 приема и обработки данных, подблок 80 приема адресов, подблок 81 адресного дешифратора и подблок 82 управления операциями программирования. Первая группа входов подблока 79 приема и обработки данных подключена к первой группе выходов подблока 80 приема адресов, вторая группа выходов которого подключена к первой группе входов подблока 81 адресного дешифратора, второй вход которого подключен ко второму выходу подблока 82 управления операциями программирования, первая группа выходов которого подключена ко второй группе входов подблока 79 приема и обработки данных, выходы которого шиной 25 подключены к информационным входам блоков памяти первого блока 1 топологии (к аналогичным входам второго блока 2 топологии, третьего блока 3 топологии и четвертого блока 4 топологии), к информационным входам регистра 59.1 блока 9 ввода, к информационным входам регистра 59.2 блока 9 ввода, к входам данных канала мультиплексоров блока 5 АЛУ, к информационным входам счетчика 63 и к информационным входам регистра 64 блока 12 приоритетного выбора. Пятая группа выходов подблока 82 управления операциями программирования подключена к входам подблока 80 приема адресов, третья группа выходов которого подключена к первой группе входов подблока 82 управления операциями программирования, второй вход которого проводником 35 подключен к прямому выходу триггера 70.2 блока 13 синхронизации. Третий вход подблока 82 управления операциями программирования проводником 78 подключен к выходу элемента 73.1 "И" блока 13 синхронизации. Четвертый вход подблока 82 управления операциями программирования проводником 60 подключен к инверсному выходу ждущего мультивибратора 70.1 блока 13 синхронизации. Третий выход подблока 82 управления операциями программирования проводником 74 подключен ко второму входу элемента 70.3 "ИЛИ" блока 13 синхронизации. Четвертый выход подблока 82 управления операциями программирования проводником 67 подключен к входу разрешения записи счетчика 63 блока 12 приоритетного выбора. Первый выход подблока 81 адресного дешифратора проводником 61 подключен к входу стробирования записи регистра 64 блока 12 приоритетного выбора, к входу стробирования записи регистра 59.1 блок 9 ввода, к входу стробирования записи регистра 59.2 блока 9 ввода. Второй выход подблока 81 адресного дешифратора проводником 56 подключен к входу элемента 54.2 "НЕ" блока 8 хранения текущей разметки. Третий выход подблока 81 адресного дешифратора проводником 36.1 подключен к второму входу элемента 33.2 "И" первого блока 1 топологии. Аналогичные входы второго блока 2 топологии, третьего блока 3 топологии, четвертого блока 4 топологии соответственно проводниками 36.2, 36.3, 36.4 подключены к четвертому, пятому и шестому выходам подблока 81 адресного дешифратора соответственно. Вариантов технической реализации блока 11 программирования очень много, особенно если учесть, что каждое конкретное применение процессора Петри может предложить или потребовать свой специфический вариант аппаратной реализации этого блока, однако все возможные варианты технической реализации укладывают в структурную схему фиг.11. Заявляемое устройство оперирует с безопасными сетями Петри, поэтому разрядность всех элементов памяти и арифметико-логических устройств, используемых для хранения и преобразования информации о количестве меток в позиции и кратности дуг, связана с коэффициентом соотношением Нарушение безопасности означает переполнение разрядной сетки процессора Петри, что не допустимо, т.к. приводит к неправильному функционированию сети Петри. Особенностью заявляемого устройства является использование класса сетей Петри с логическими дугами и отказ от использования временных сетей Петри, что формирует соответствующие структуры данных (фиг.12). В сетях Петри, с которыми оперирует заявляемое устройство, присутствуют два типа дуг: транспортные, по которым могут перемещаться метки, и логические, которые непосредственно не связаны с перемещением меток по сети, и которые вводят дополнительное условие запуска перехода, тем самым реализуя некоторую наперед задаваемую логическую функцию проверки условий которая принимает значения "истина" или "ложь" ("1" или "0"). По этой причине логические дуги всегда направлены только от вершин-позиций к вершинам-переходам, а при графическом обозначении в отличие от транспортных дуг вместо стрелки имеют пустой кружок. "Логические дуги" являются обобщающим термином для ранее традиционно используемых терминов "ингибиторные", "сдерживающие", "разрешающие", "запрещающие" дуги и т.д. Функция определяющая логическую дугу от вершины-позиции к вершине переходу где - номер позиции, а - номер перехода, определяется двумя параметрами: кратностью логической дуги и функцией отношения и их комбинации равно")). величинами Функция и оказывается истинным, где в позиции ("не если между отношение - количество меток В противном случае и переход не может быть запущен. В дальнейшем для удобства представления информации о топологии сети Петри отношение записывается в числовой форме: отношение имеет код 1, отношение имеет код 2, отношение имеет код 4; отношения имеют код, равный сумме кодов составных частей. Код означает отсутствие логической дуги от позиции к переходу Фиг.12 представляет используемые структуры данных. Вся информация о топологии сети Петри содержится в четырех матрицах инцидентности На фиг.12 матрицы закодированы согласно представленному фрагменту сети Петри. Позиции входные для связи с датчиками, позиция - выходная для связи с исполнительным механизмом. Матрица определяет связи входных транспортных дуг, матрица - выходных транспортных дуг. Термины "входной" и "выходной" определяются по отношению к соответствующему переходу. Матрицы и дополняют друг друга и определяют связи логических дуг. Информация о топологии сети дополняется вектором начальной разметки векторами из переменной идентификации и позиций двумя ввода Вектор текущей разметки состоит чисел, каждое число, обозначаемое соответствует позиции количеству меток в позиции и равно Первоначальное значение вектора называется вектором начальной разметки сети Петри и обозначается Переменная всегда принимает значение, равное количеству переходов в обрабатываемой процессором сети Петри. Вектор состоит из чисел, каждое число соответствует позиции и может принимать значение 0 или 1. означает, что позиция является входной и используется для приема информации с датчиков. В противном случае Организация вектора такая же, как и у вектора означает для входной позиции что в процессе операции ввода старая информация (количество меток) в позиции будет утеряна, а на ее место будет помещена новая информация с датчиков. При (количество новая вводимая информация меток) суммируется со старой информацией и помещается в позицию т.е. информация накапливается и потери информации не происходит. Использование вектора позволяет гибко программировать операцию ввода, т.к. одни задачи требуют "разрушения старой информации", например, при отслеживании информации датчиков, другие же требуют осуществлять ввод с накоплением информации. Заявляемый процессор Петри реализует обработку приоритетных сетей Петри. Это означает, что право запуска предоставляется переходам последовательно в порядке приоритетов. Это означает, что процессор в момент обслуживания перехода использует не всю информацию матриц а лишь по одному столбцу каждой матрицы. Таким образом мы имеем векторы Кроме них чисел, каждое используются также векторы Вектор состоит из число соответствует позиции и принимает значение, равное количеству меток, которые должны быть добавлены в позицию по окончании цикла постусловий текущего запуска сети Петри, Вектор - вспомогательный вектор, используемый при вычислении нового значения вектора текущей разметки Вектор - вспомогательный вектор, используемый при вычислении нового значения вектора Векторы имеют одинаковую размерность организация вектора разрядность элементов памяти и АЛУ, определяется -безопасностью сети Петри. Условие запуска перехода определяется как функция условие запуска перехода дугам, а по логическим - условие запуска перехода по транспортным дугам. Устройство работает следующим образом. Фиг.13 представляет алгоритм функционирования процессора Петри, а фиг.14 временную диаграмму основных сигналов синхронизации. Функционирование процессора Петри начинается выполнением операций программирования. Для этого необходимо нажать кнопку "ИНИЦИАЛИЗАЦИЯ ПРОГРАММИРОВАНИЯ" пульта 73.1 управления блоком синхронизации, который при этом сформирует импульсный сигнал 75, который запустит ждущий мультивибратор 70.1 блока 13 синхронизации. При этом ждущий мультивибратор 70.1 генерирует отрицательный импульс сигнала 60, который произведет начальную установку элементов памяти блока 11 программирования и триггеров 70.2, 72.1, 73.9, 73.10, 73.11 блока 13 синхронизации. При этом триггер 70.2 заблокирует генерацию подблоком 73 основных сигналов синхронизации 34, 44, 45, разрешит элементу 73.1 "И" генерацию тактовых импульсов сигнала 78 для блока 11 программирования и сформирует сигнал 35 подтверждения выполнения операций программирования. Сигнал 35 переводит первый блок 1 топологии, второй блок 2 топологии, третий блок 3 топологии, четвертый блок 4 топологии в режим записи данных с шины 25. При этом блок 11 программирования выполняет следующие операции. В блок 9 ввода в регистр 59.1 записывается вектор а в регистр 59.2 записывается вектор При этом запись данных стробируется сигналом 61. В первый блок 1 топологии, во второй блок 2 топологии, в третий блок 3 топологии и в четвертый блок 4 топологии записываются данные матриц соответственно при стробировании записи сигналами 36.1, 36.2, 36.3, 36.4 соответственно. При этом для указания адресов памяти первому блоку 1 топологии, второму блоку 2 топологии, третьему блоку 3 топологии, четвертому блоку 4 топологии на шину 24 помещается код записываемого вектора, для этого блок 11 программирования с шины 25 сигналом 67 записывает в счетчик 63 блока 12 приоритетного выбора код после чего на шину 25 блоком 11 программирования выставляются данные соответствующего вектора. В блок 8 хранения текущей разметки записывается вектор запись стробируется сигналом 56 в регистры При этом данные вектора на входы регистров поступают с шины 25 через канал мультиплексоров и АЛУ блока 5. Для этого подблоками 39 и 41 формируются соответствующие сигналы. На входы АЛУ при этом поступает сигнал В блок 12 приоритетного выбора в регистр 64 записывается число Запись стробируется сигналом 61. В зависимости от варианта применения процессора Петри источники программирующей информации о структуре обрабатываемой сети Петри могут быть различными, например, накопитель на магнитной ленте, накопитель на магнитном диске, интегральная микросхема постоянного запоминающего устройства, микропроцессорная шина, клавишный пульт оператора и т.д., отсюда различные модификации технического построения блока 11 и режимов его работы. Но в любом случае в подблок 79 (фиг.11) подаются программирующие данные, а в подблок 80 подается адресная информация о том, куда следует поместить эти данные. При необходимости подблок 79 должен осуществлять преобразование формата и другую обработку данных. После чего данные из подблока 79 помещаются на шину 25 под управлением сигналов подблока 82. Этот же подблок 82 генерирует общий сигнал записи для подблока 81. Подблок 81 адресного дешифратора на основании информации подблока 80 определяет, в какой регистр или блок памяти процессора надо записать данные и стробирует запись одним из сигналов 36.1, 36.2, 36.3, 36.4, 56, 61. По окончании выполнения всех операций программирования подблок 82 генерирует для блока синхронизации сигнал 74 идентификации окончания цикла программирования, который сбрасывает триггер 70.2 блока 13 синхронизации, что переводит сигналы 35 и 78 в пассивное состояние и разрешает подблоку 73 генерацию основных сигналов синхронизации 34, 44, 45 для выполнения первого рабочего цикла. Здесь и в дальнейшем рабочим циклом будем называть совокупность однократного выполнения операций ввода-вывода данных и однократного запуска сети Петри, который состоит из цикла реализации предусловий и цикла реализации постусловий. Операции ввода данных и вывода данных выполняются независимо различными блоками, что дает возможность в заявляемом, устройстве совместить во времени эти две операции и синхронизировать их одним общим сигналом 45. Такой подход повышает быстродействие устройства. При этом во времени совмещаются операция вывода данных, логически соответствующая предыдущему рабочему циклу, и операция ввода, логически соответствующая текущему рабочему циклу. Рабочий цикл начинается выполнением операций ввода-вывода. Для их синхронизации блок 13 синхронизации генерирует один импульс сигнала 45. По переднему фронту этого импульса вектор из блока 8 хранения текущей разметки записывается в регистры блока 10 вывода, информация с выходов которых может непосредственно использоваться исполнительными механизмами объекта управления. Регистры блока 9 ввода предназначены для приема входной информации от датчиков объекта управления, поступившей по шине 22 во время предшествующего рабочего цикла. Запись поступающей информации в регистры обеспечивает подблок 58. Информация может поступать по шине 22 как в виде импульсных сигналов (ввод меток со стробированием), так и в виде потенциальных сигналов (например, когда требуется отследить в позиции во времени показания какого-либо датчика). Задача, решаемая подблоком 58, принять входную информацию в регистры исключить случаи ее потери и искажения, например, исключить случаи многократного ввода одной и той же информации или ввода неправильной информации. Запись входных данных в регистры может осуществляться асинхронно и в любой момент времени, за исключением моментов времени, когда приходит из блока 13 синхронизации единичный синхроимпульс сигнала 45, что означает начало операции ввода данных из регистров в регистры блока 8 хранения текущей разметки, которые хранят текущий вектор что требует стабильности данных в регистрах в этот момент, а потому исключает возможность записи данных в регистры в этот момент. При появлении единичного импульса сигнала 45 подблок 40 генерирует сигнал что настраивает блок 5 АЛУ на выполнение операции Кроме того, мультиплексоры управляемые подблоком 39, передают на вход канала АЛУ данные, поступающие на четвертую группу информационных входов блока 5 АЛУ. т.е. данные с выходов регистров Подблок 41, управляемый программно, устанавливается вектором позициях сигналы для АЛУ соответствующих для которых формирует Для всех остальных АЛУ В итоге к приходу заднего фронта синхроимпульса сигнала 45 на входах регистров для входных позиций разметка формируется новая требующая записи в регистры Причем, как отмечалось ранее, если то равно сумме вводимых меток и меток, хранившихся в позиции до момента ввода; если равно только вводимому числу меток, а информация о метках, хранимых в позиции до момента ввода, не учитывается и будет потеряна. По заднему фронту синхроимпульса сигнала 45 осуществляется запись данных с шины 15 в регистры для которых то есть только для входных позиций. При этом запись в регистры стробируется набором подблоков которые управляются по шине 26 программно устанавливаемым вектором Операция ввода на этом считается законченной. По окончании операций ввода-вывода блок синхронизации генерирует синхроимпульсов сигнала 34 для синхронизации операций в процессоре по выполнению цикла предусловий. Предусловия запуска переходов проверяются последовательно во времени согласно назначенным приоритетам. Первым обслуживается переход (самый высокий приоритет), последним - переход (самый низкий приоритет). Один синхроимпульс сигнала 34 синхронизирует все операции по обслуживанию одного перехода. Блок 12 приоритетного выбора на шине 24 генерирует последовательность кодов для обрабатываемых переходов от 0 до (согласно установленному соглашению о приоритетах). Блок 12 приоритетного выбора функционирует следующим образом. В процессе программирования блоков процессора в регистр 64 записывается число а в такте ввода-вывода сигналом 45 блок 13 синхронизации в счетчик 63 записывает код Таким образом, в момент прихода первого синхроимпульса сигнала 34 будет обслуживаться переход Содержимое счетчика 63 модифицируется по каждому заднему фронту сигнала 34, когда все действия по обслуживанию текущего перехода уже закончены. Когда содержимое счетчика 63 достигнет числа компаратор 65 в блок синхронизации выдаст единичный сигнал 68 об окончании цикла предусловий. В конце рабочего цикла в счетчик 63 сигналом 44 будет записан код При реализации предусловий текущего перехода блоки процессора Петри выполняют следующие действия. Через интервал времени, равный задержке выдачи данных подблоками памяти первого блока 1 топологии, второго блока 2 топологии, третьего блока 3 топологии, четвертого блока 4 топологии, после появления переднего фронта синхроимпульса сигнала 34 первый блок 1 топологии, второй блок 2 топологии, третий блок 3 топологии, четвертый блок 4 топологии на своих выходных шинах 17, 16, 18, 19 соответственно выставят данные векторов соответственно. Блок 5 АЛУ проверяет условие запуска перехода по транспортным дугам и формирует значение функции (сигнал 28). При этом подблок 40 настраивает АЛУ на выполнение операции вычитания. Под управление подблока 39 мультиплексоры к каналу B АЛУ подключают вторую группу информационных входов блока 5 АЛУ, т.е. шину вектора При этом АЛУ операцию анализа значений старшего разряда АЛУ значение перехода функции выполняет Подблок 42 на основе сигналов о переносе из формирует разрешения запуска по транспортным дугам (сигнал 28). Га шине 15 формируется вектор Одновременно с описанными действиями в блоке 5 АЛУ блок 6 проверки логических условий формирует значение функции разрешения запуска перехода по логическим дугам (сигнал 29). Происходит это следующим образом. Набор компараторов сравнение производит почленное векторов (т.е. сравниваются Набор элементов "И-ИЛИ" является набором схем проверки совпадения результатов сравнения компараторов и заданных функций Каждый элемент "И-ИЛИ" формирует значение функции Подблок 48 собирает сигналы всех функций и формирует сигнал 29 функции Одновременно с описанными операциями в блоке 5 АЛУ и в блоке 6 проверки логических условий блок 7 формирования постусловий формирует векторы Вектор что следует из алгоритма (фиг.13) и отмечалось ранее, накапливает постусловия всех запущенных в текущем рабочем - цикле переходов и хранится в регистрах блока формирования постусловий. Регистры в начале каждого рабочего цикла в течение такта ввода-вывода сигналом 45 сбрасываются в "0". Сумматоры подсчитывают вектор т.е. новое значение вектора на случай, если обслуживаемый переход будет запущен. Значение вектора формируется на выходах сумматоров и подается на входы регистров Подблок проверяет выполнение условий 51 запуска обслуживаемого перехода т.е. значения сигналов 28 и 29. Если оба эти сигнала равны "1", т.е. условия выполняются, то по заднему фронту текущего синхроимпульса сигнала 34 подблок 51 запишет в регистры вектор т.е. будет выполнена операция Если хоть одно из условий не будет выполнено, то переход считаться незапущенным, коррекция и будет вектора будет не нужна и запись в регистры вектора производиться не будет. Аналогичным образом в блоке 8 хранения текущей разметки подблок 54 проверяет выполнение условий (сигналы 28, 29). Если оба условия выполняются, то по заднему фронту текущего синхроимпульса сигнала 34 подблок 54 запишет в регистры с шины 15 вектор т.е. новое, откорректированное с учетом запуска перехода значение вектора текущей разметки. Если хоть одно из условий не будет выполнено, то в регистры подблоком 54 запись вектора производиться не будет, На этом действия по обслуживанию перехода в цикле предусловий считаются законченными, на шине 24 блоком приоритетного выбора модифицируется значение кода и описанная процедура реализации предусловий повторяется для перехода перехода обслужен затем для и т.д. до тех пор, пока не будет переход По окончании обслуживания перехода блок 12 приоритетного выбора считает, что все переходы обрабатываемой сети Петри в цикле предусловий обслужены, цикл предусловий окончен и генерирует в блок синхронизации сигнал 63 идентификации окончания цикла предусловий. В ответ на этот блок синхронизации прекращает генерацию синхроимпульсов сигнала 34 и генерирует одиночный синхроимпульс сигнала 44 для синхронизации операций по реализации постусловий запущенных переходов. По этому синхроимпульсу подблок 40 блока 5 АЛ У настраивает АЛУ операции мультиплексоры на выполнение Под управлением подблока 39 передают в канал B АЛУ данные с третьей группы информационных входов блока 5 АЛУ, т.е. блок 5 выполняет операцию По заднему фронту синхроимпульса сигнала 44 подблок 54 осуществляет запись в регистры вектора сигнала В целом за синхроимпульс 44 выполняется операция На этом рабочий цикл процессора считается законченным. При выполнении операции вывода в следующем рабочем цикле полученное значение вектора будет переписано в регистры блока вывода и передано исполнительным механизмам объекта управления. По окончании каждого рабочего цикла блок синхронизации запрашивает у подблока 71 пускаостанова разрешение на следующий рабочий цикл. Если запрета на начало следующего рабочего цикла не получено, то процессор автоматически переходит к началу следующего рабочего цикла. В данной аппаратной реализации блока 13 синхронизации подблоком 73 коммутатора импульсов опрашивается состояние триггера 71.2 подблока 71 пуска-останова процессора. При автоматическом режиме работы триггер 71.2 находится в состоянии "0". Наличие запрета на начало очередного рабочего цикла (триггер 71.2 в состоянии "1") означает пошаговый режим работы процессора Петри. Один шаг означает выполнение без останова любого наперед заданного целого числа рабочих циклов процессора. Для предложенного варианта аппаратной реализации блока 13 один шаг - один рабочий цикл. Выполнение одного шага инициируется подачей одиночного импульса сигнала 76 при нажатии кнопки "ШАГ" пульта 71.3 управления блоком 13 синхронизации. Из шагового режима в автоматический процессор Петри переводится подачей сигнала 77 при нажатии кнопки "ПУСК" пульта 71.3 управления блоком 13 синхронизации. Подачей сигнала 76 ("ШАГ") в автоматическом режиме процессор по окончании рабочего цикла будет переведен в состояние останова (шагового режима). Сигналы 76 "ШАГ" и 77 "ПУСК" асинхронные. При функционировании процессора возможны три случая возникновения переполнения разрядной сетки устройства: 1) при выполнении операции ввода в блоке 5 АЛУ; 2) при выполнении цикла предусловий в блоке 7 формирования постусловий при вычислении вектора ; 3) в такте постусловий в блоке 5 АЛУ при выполнении операции Во всех трех случаях переполнение разрядной сетки может возникнуть при выполнении операции суммирования. Выявление случаев переполнения разрядной сетки в блоке 5 АЛУ осуществляется подблоком 43 на основе анализа значений сигналов переноса из старшего разряда АЛУ Подблок 43 формирует сигнал 30 признака переполнения разрядной сетки в блоке 5 АЛУ. Выявление случаев переполнения разрядной сетки в блоке 7 формирования постусловий осуществляется подблоком 52, который на основе анализа значений сигналов переноса из старшего разряда сумматоров формирует сигнал 31 признака переполнения разрядной сетки в блоке 7 формирования постусловий. Во время функционирования процессора Петри подблок 72 постоянно контролирует сигналы 30 и 31. При активизации хотя бы одного из сигналов 30 и 31 подблок 72 блокирует выдачу синхроимпульсов рабочего цикла подблоком 73 и переводит процессор в состояние останова, из которого он может быть выведен только сигналом 75 инициализации операций программирования.

ДивитисяДодаткова інформація

Назва патенту англійськоюPetri processor

Автори англійськоюMateichenko Viktor Valentynovych, Kalinin Hennadii Oleksandrovych, Markin Oleh Mykhailovych, Zaporozhtsev Serhii Yuriiovych, Hutsa Oleh Mykolaiovych

Назва патенту російськоюПроцессор петри

Автори російськоюМатейченко Виктор Валентинович, Калинин Геннадий Александрович, Маркин Олег Михайлович, Запорожцев Сергей Юрьевич, Гуца Олег Николаевич

МПК / Мітки

МПК: G06F 17/00, G06F 15/00

Код посилання

<a href="https://ua.patents.su/13-15213-procesor-petri.html" target="_blank" rel="follow" title="База патентів України">Процесор петрі</a>

Попередній патент: Спосіб аналогового моделювання процесів розповсюдження звукових хвиль

Наступний патент: Спосіб вимірювання механічного недопалу палива

Випадковий патент: Спосіб виробництва ординарного міцного червоного виноградного вина "портвейн бурлюк"