Пристрій для приймання та передачі інформації з багатозначним кодуванням

Номер патенту: 5696

Опубліковано: 28.12.1994

Автори: Попович Галина Богданівна, Лосєва Тетяна Віталіївна, Коноплянко Зеновій Дмитрович

Формула / Реферат

1. Устройство для приема и передачи информации с многозначным кодированием, содержащее первый канал связи, выход которого подключен ко входу первого аналого-цифрового преобразователя, выходы которого соединены со входами первого преобразователя единичного кода в двоичный, первый преобразователь двоичного кода в единичный, выходы которого подключены ко входам первого цифро-аналогового преобразователя, отличающееся тем, что в устройство введены второй - n-й каналы связи ![]() , второй - n-й аналого-цифровые преобразователи, второй - n-й преобразователи единичного кода в двоичный, второй - n-й преобразователи двоичного кода в единичный, второй - n-й цифро-аналоговые преобразователи, ключевой коммутатор и узел управления, вход синхронизации, и управляющие входы которого являются одноименными входами устройства, выходы узла управления подключены к управляющим входам ключевого коммутатора, выходы первого преобразователя единичного кода в двоичный подключены к информационным входам первого преобразователя двоичного кода в единичный, тактовый вход которого является первым тактовым входом устройства, тактовые входы і-го преобразователя двоичного кода в единичный

, второй - n-й аналого-цифровые преобразователи, второй - n-й преобразователи единичного кода в двоичный, второй - n-й преобразователи двоичного кода в единичный, второй - n-й цифро-аналоговые преобразователи, ключевой коммутатор и узел управления, вход синхронизации, и управляющие входы которого являются одноименными входами устройства, выходы узла управления подключены к управляющим входам ключевого коммутатора, выходы первого преобразователя единичного кода в двоичный подключены к информационным входам первого преобразователя двоичного кода в единичный, тактовый вход которого является первым тактовым входом устройства, тактовые входы і-го преобразователя двоичного кода в единичный ![]() является і-ым тактовым входом устройства, выход і-го канала связи подключен ко входу і-го аналого-цифрового преобразователя, выходь которого через і-й преобразователь единичного кода в двоичный подключены к информационным входам і-го преобразователя двоичного кода в единичный, выходы которого соединены со входами i-го аналого-цифрового преобразователя, выходы первого - n-го цифро-аналоговых преобразователей подключены соответственно к первому - n-му информационным входам ключевого коммутатора первый - n-й выходы которого являются одноименными выходами устройства.

является і-ым тактовым входом устройства, выход і-го канала связи подключен ко входу і-го аналого-цифрового преобразователя, выходь которого через і-й преобразователь единичного кода в двоичный подключены к информационным входам і-го преобразователя двоичного кода в единичный, выходы которого соединены со входами i-го аналого-цифрового преобразователя, выходы первого - n-го цифро-аналоговых преобразователей подключены соответственно к первому - n-му информационным входам ключевого коммутатора первый - n-й выходы которого являются одноименными выходами устройства.

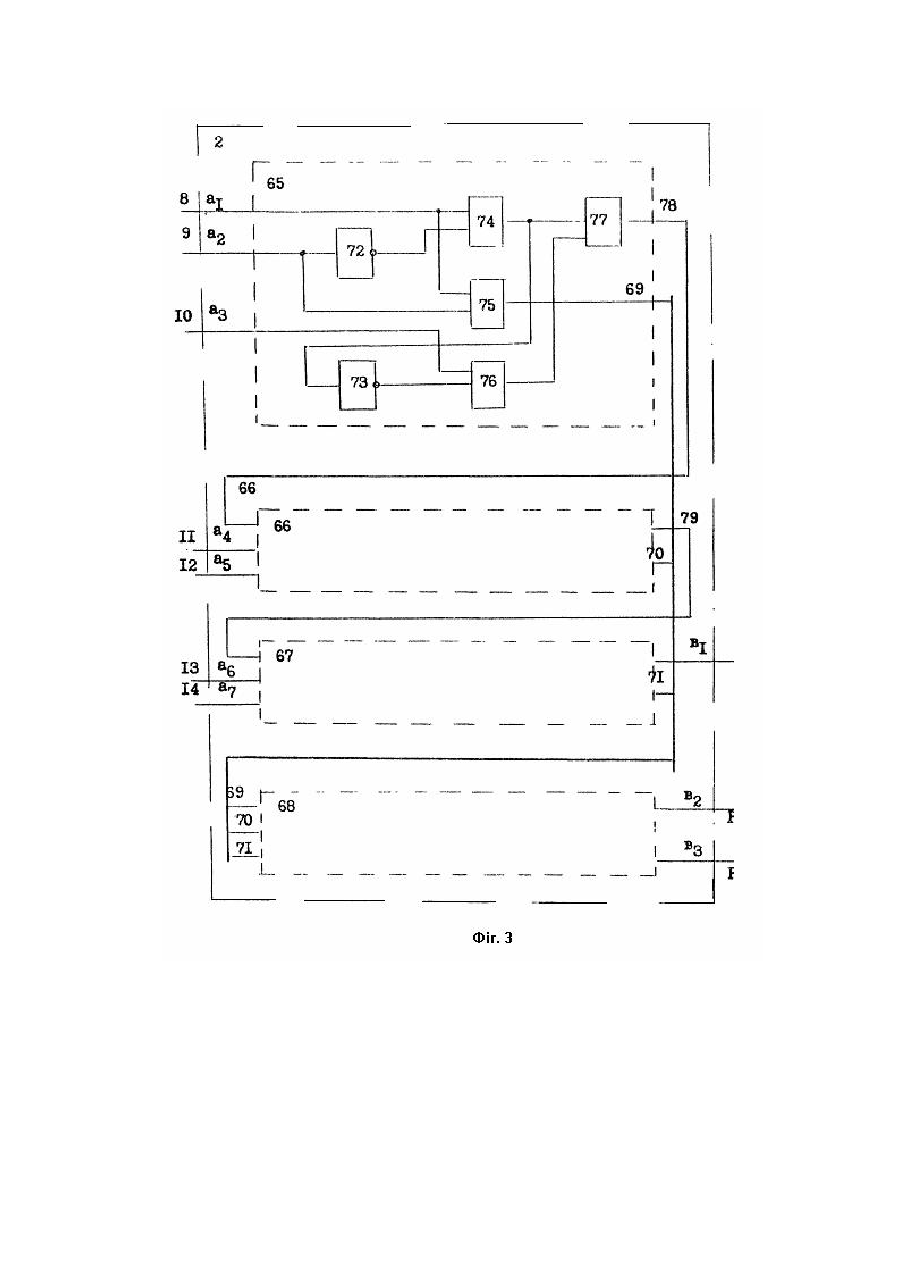

2. Устройство по п.1, отличающееся тем, что преобразователь единичного кода в двоичный содержит первый - четвертый логические блоки, каждый из которых включает в себя первый и второй элементы НЕ, первый - третийэлементы И и элемент ИЛИ, первые входы первого и второго элементов И первого логического блока объединены и являются первым входом преобразователя, выходы элементов ИЛИ в первом и втором логических блоках подключены к первым входам первого и второго элементов И соответственно во втором и третьем логических блоках, вход первого элемента НЕ и второй вход второго элемента И в каждом из первого по третий логических блоков объединены и являются соответствующими входами преобразователя, первый вход третьего элемента И в каждом из первого по третий логических блоков являются соответствующими входами преобразователя, выход второго элемента И первого логического блока соединен с первыми входами первого и второго элементов И четвертого логического блока, выход второго элемента И второго логического блока подключен к входу первого элемента НЕ и второму входу второго элемента И четвертого логического блока, выход второго элемента И третьего логического блока подключен к первому входу третьего элемента И четвертого логического блока, выходы первого и второго элементов НЕ в каждом логическом блоке соединены со вторыми входами соответственно первого и третьего элементов И того же логического блока, выход первого элемента И в каждом логическом блоке соединен с первым входом элемента ИЛИ и входом второго элемента НЕ того же логического блока, выход третьего элемента И в каждом логическом блоке подключен ко второму входу элемента ИЛИ того же логического блока, выход элемента ИЛИ третьего логического блока и выходы элемента ИЛИ и второго элемента И четвертого логического блока являются соответствующими выходами преобразователя.

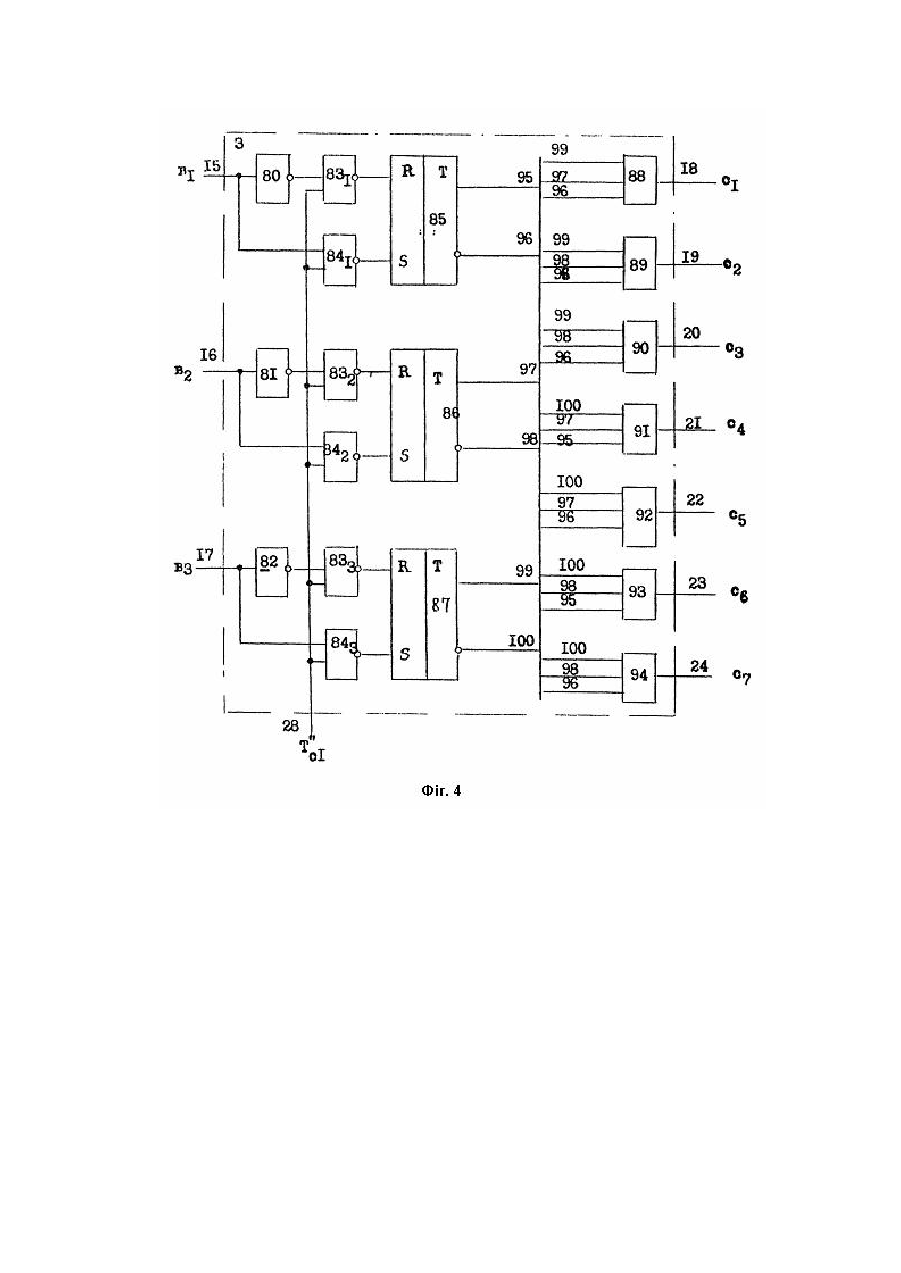

3. Устройство по п.1, отличающееся тем, что преобразователь двоичного кода в единичный содержит первый-третий элементы НЕ, первый-шестой элементы И-НЕ, первый-третий RS-триггеры и первый-седьмой элементы И, первые входы всех элементов И-НЕ объединены и являются тактовым входом преобразователя, вход j-го элемента НЕ (j = 1, 2, 3) объединен со вторым входом (2j)-го элемента И-НЕ и является соответствующим входом преобразователя, выход j-го элемента НЕ соединен со вторым входом (2j-1)-го элемента И-НЕ, выходы (2j-1)-го и (2j)-го элементов И-НЕ подключены соответственно к R и S входам j-го RS-триггера, прямые и инверсные выходы всех RS-триггеров подключены к соответствующим входам первого-седьмого элементов И, выходы которых являются выходами преобразователя.

Текст

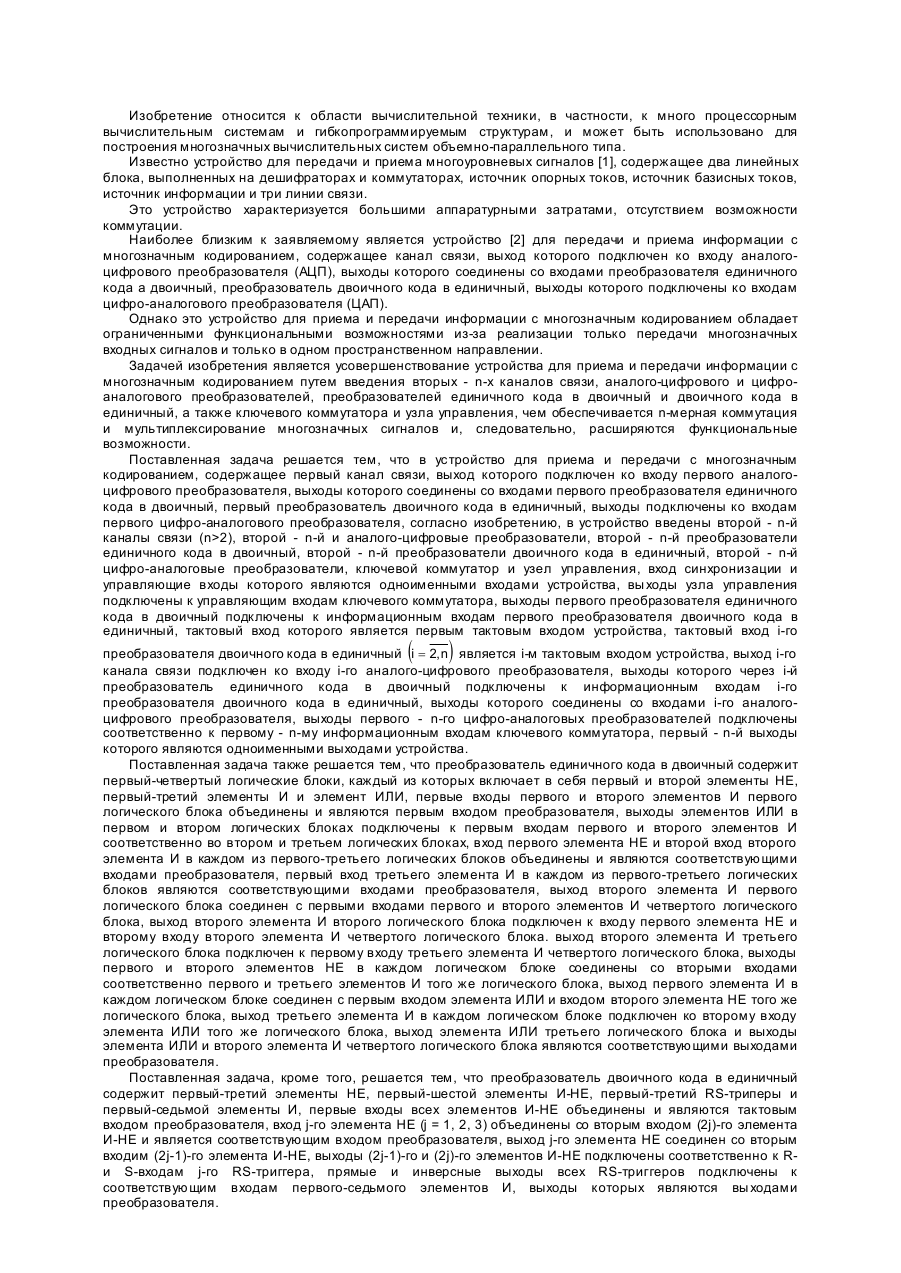

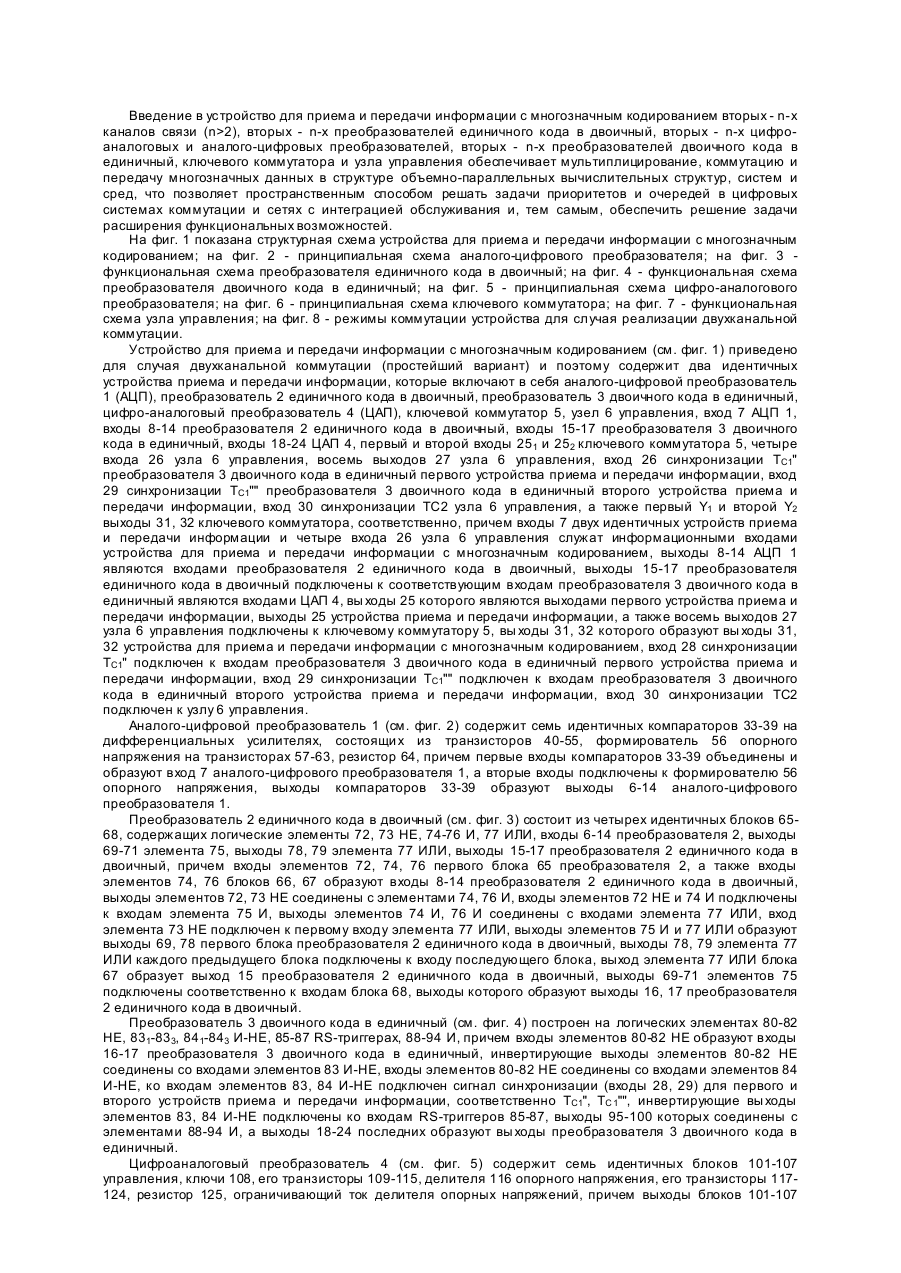

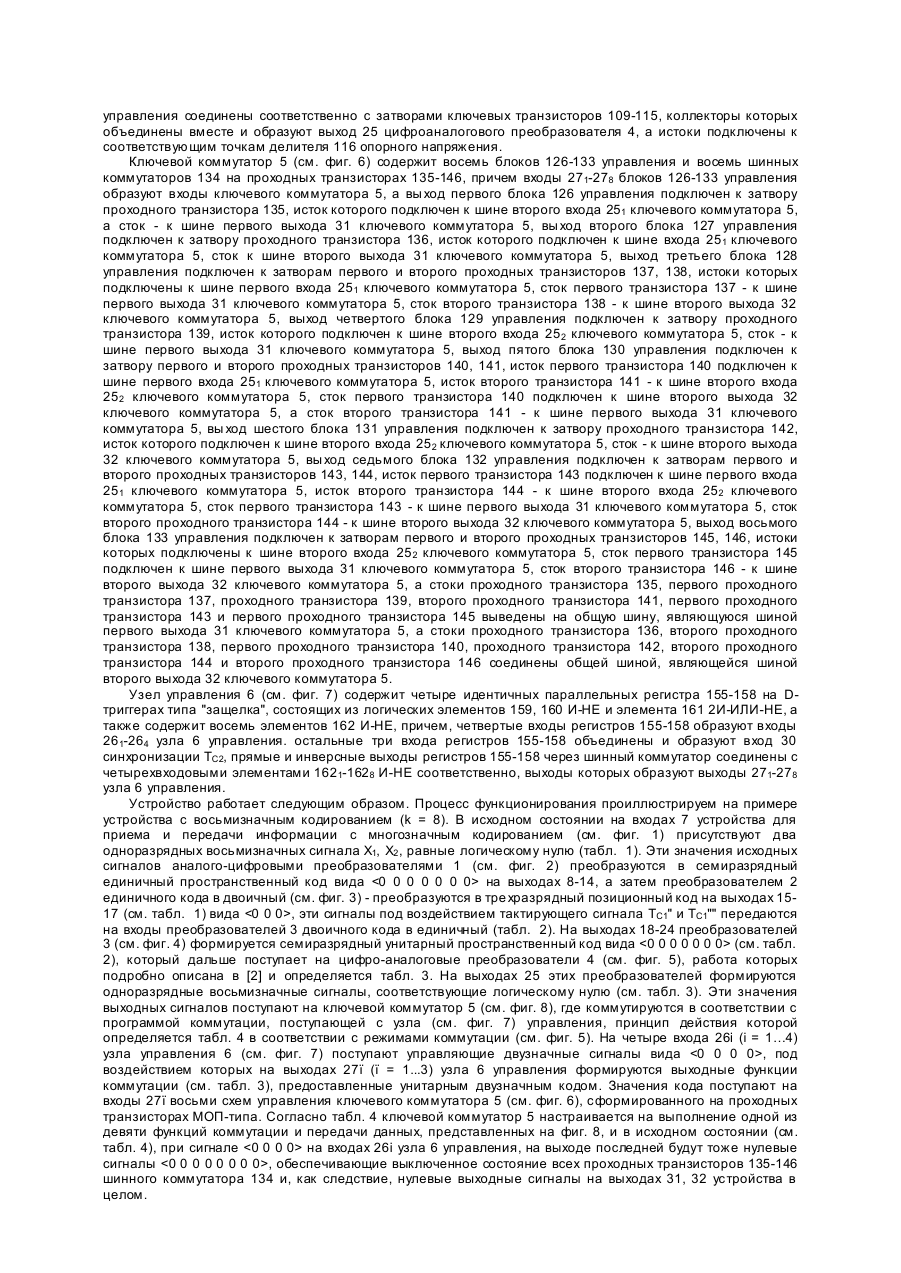

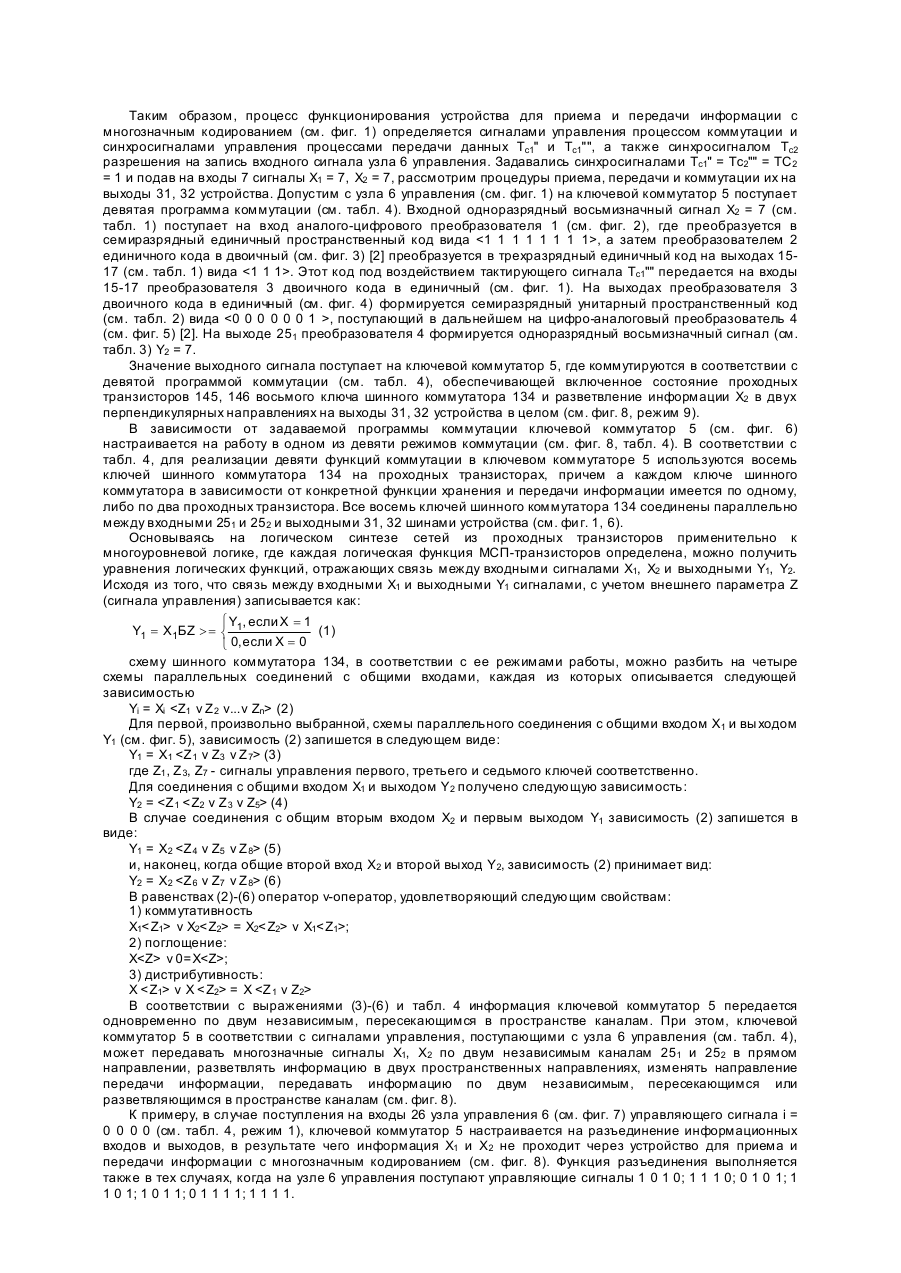

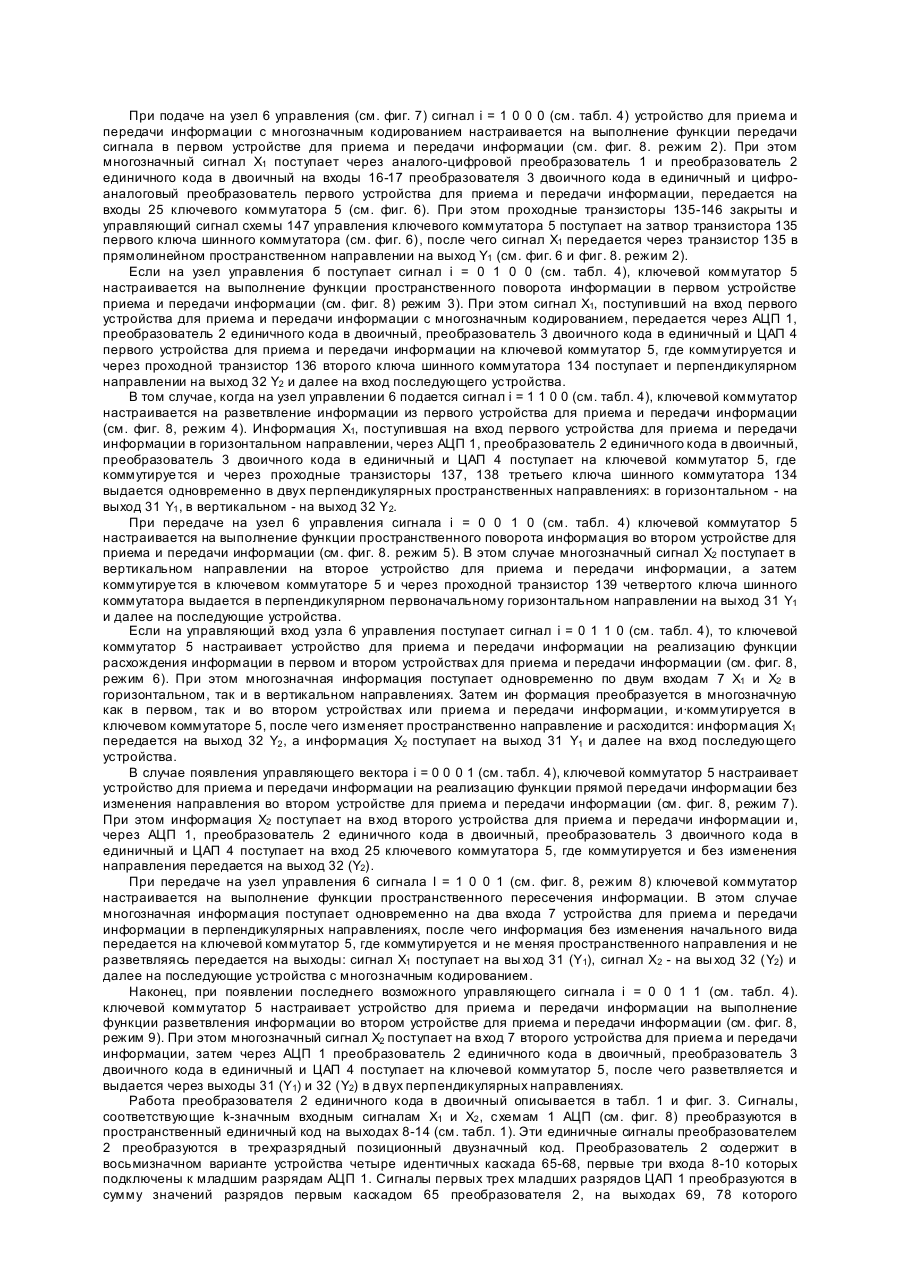

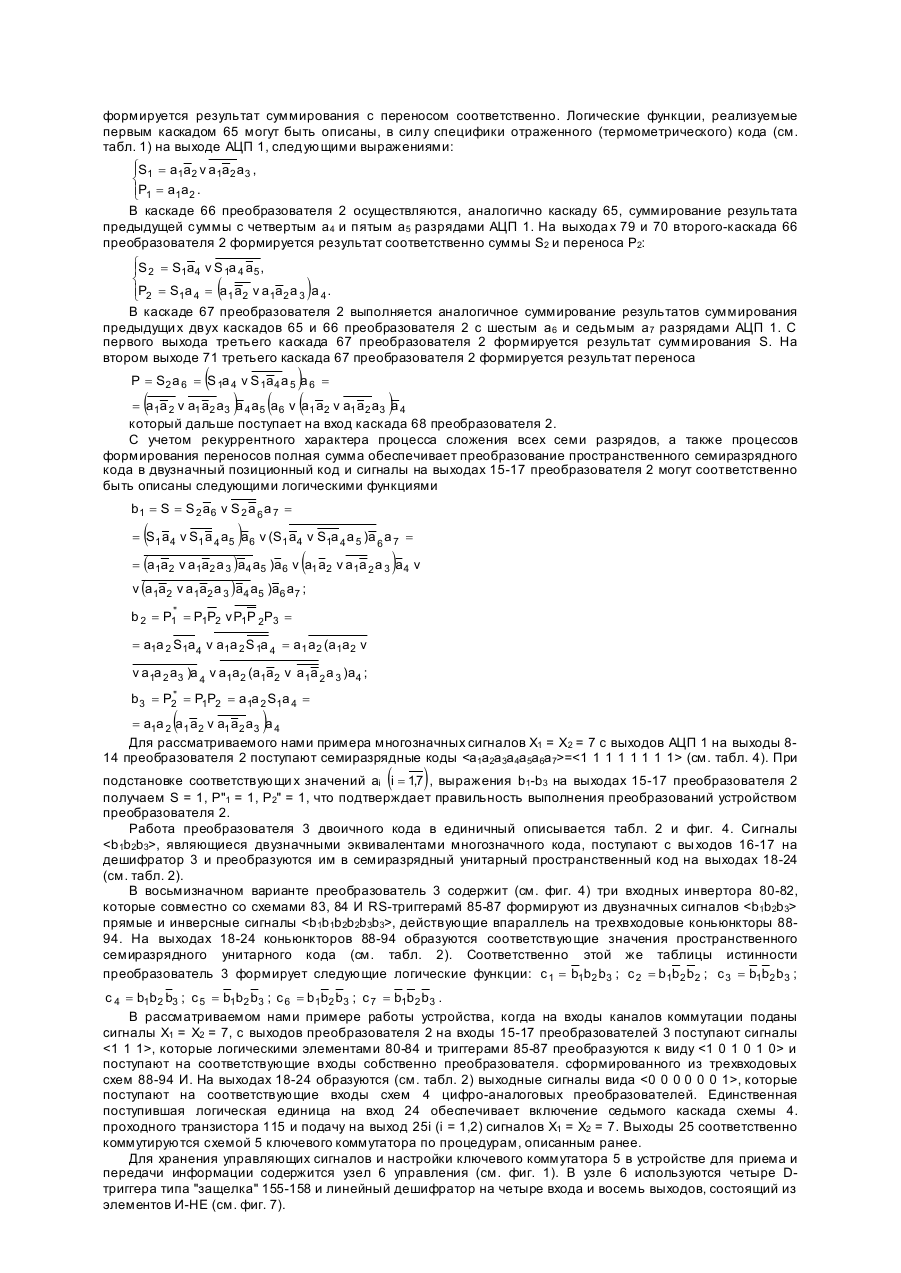

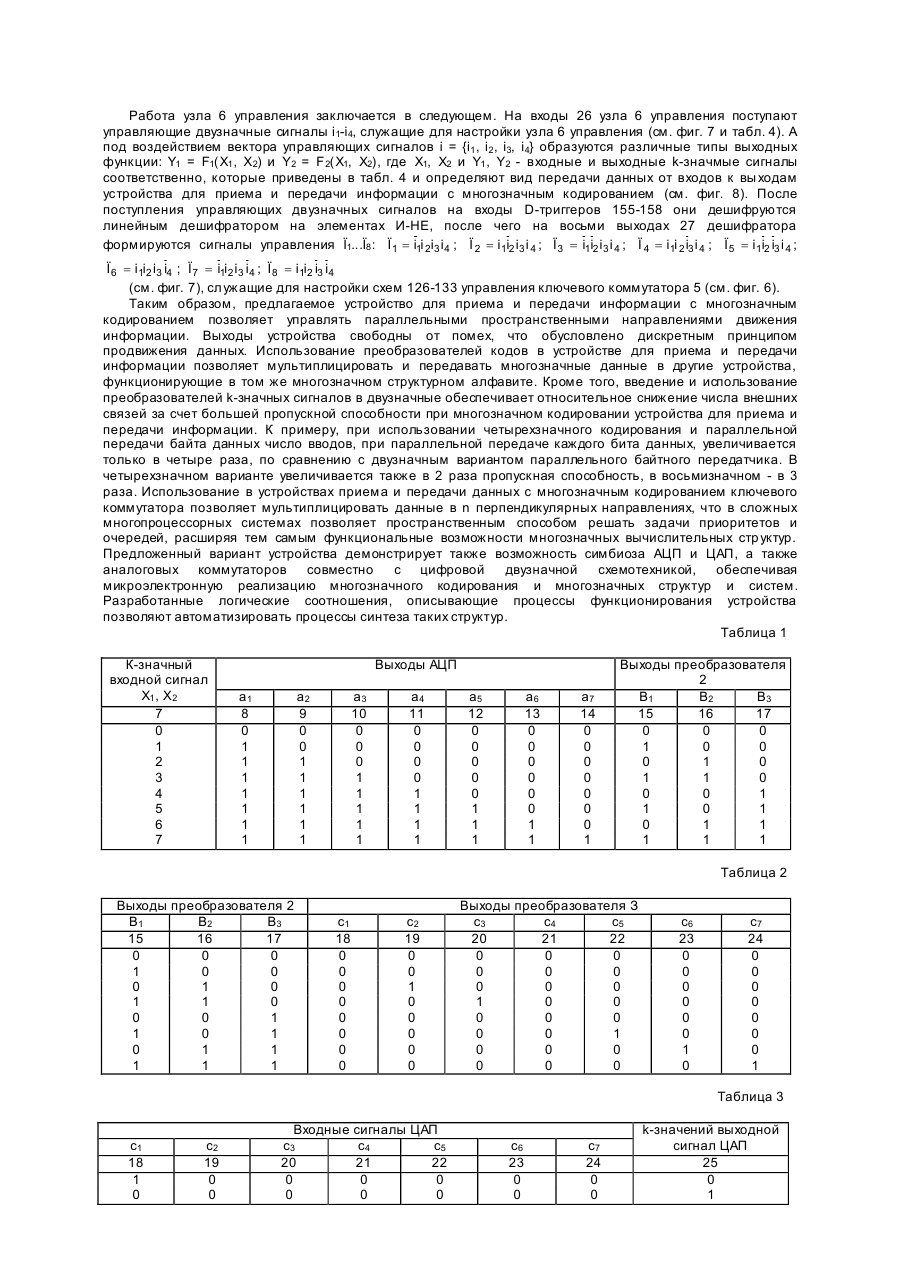

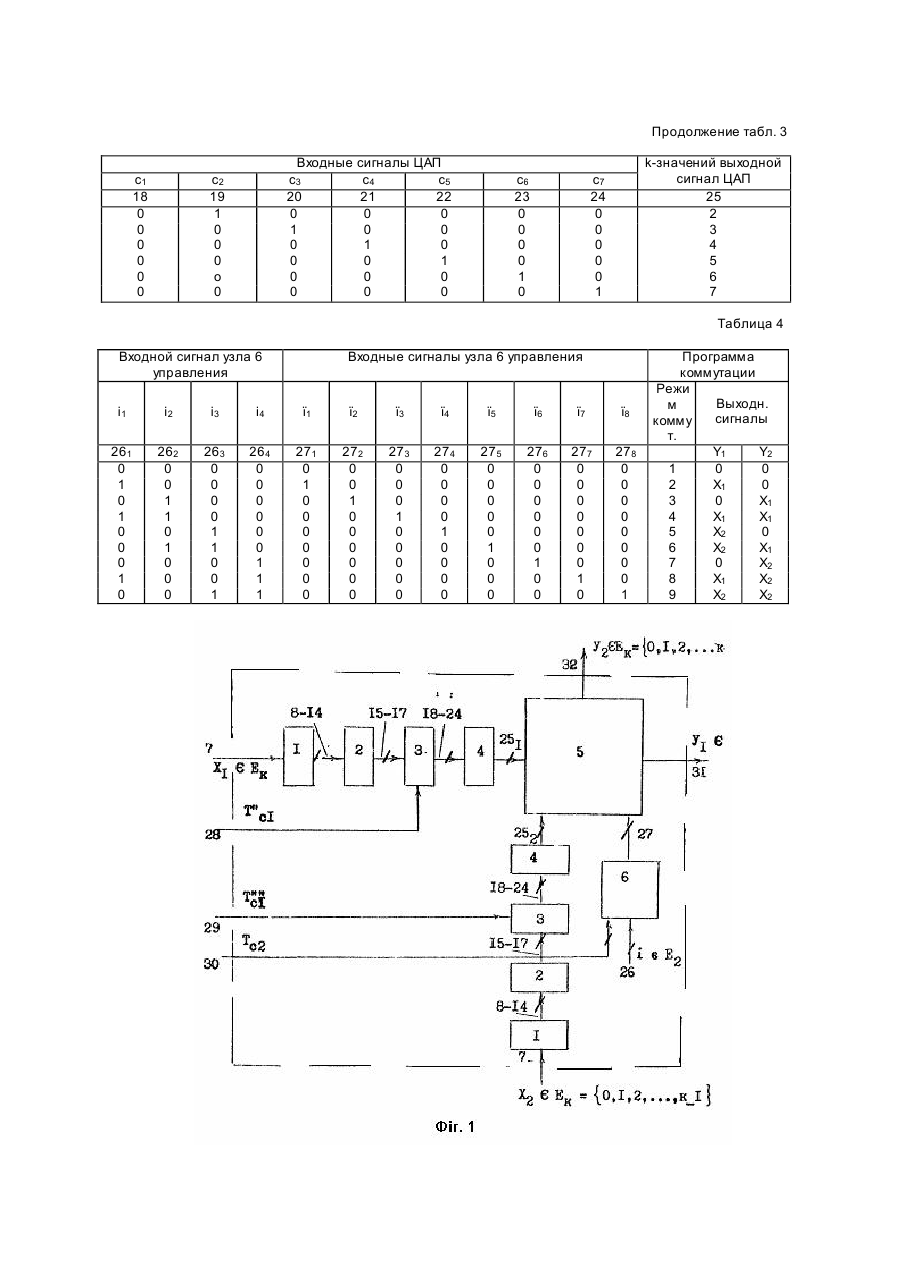

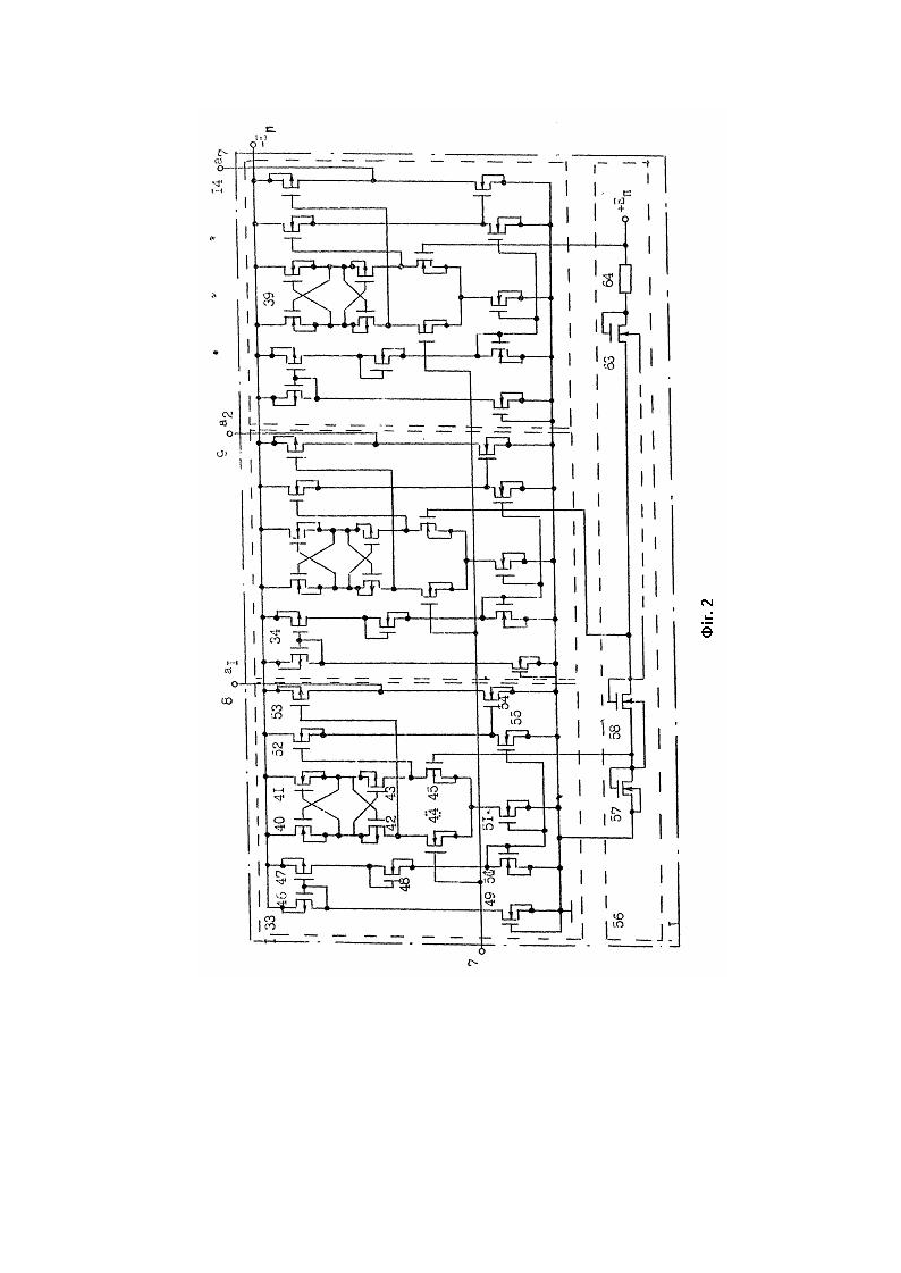

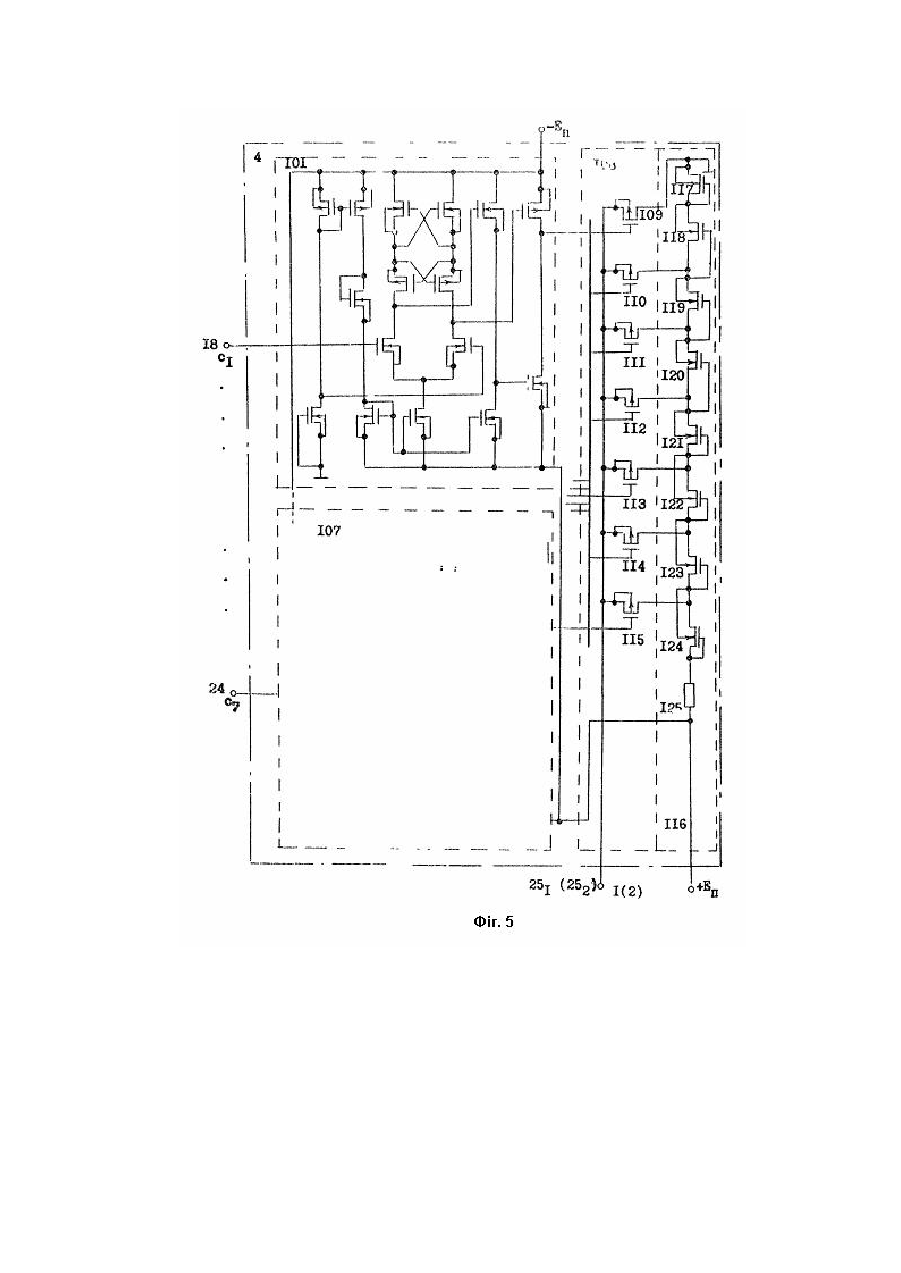

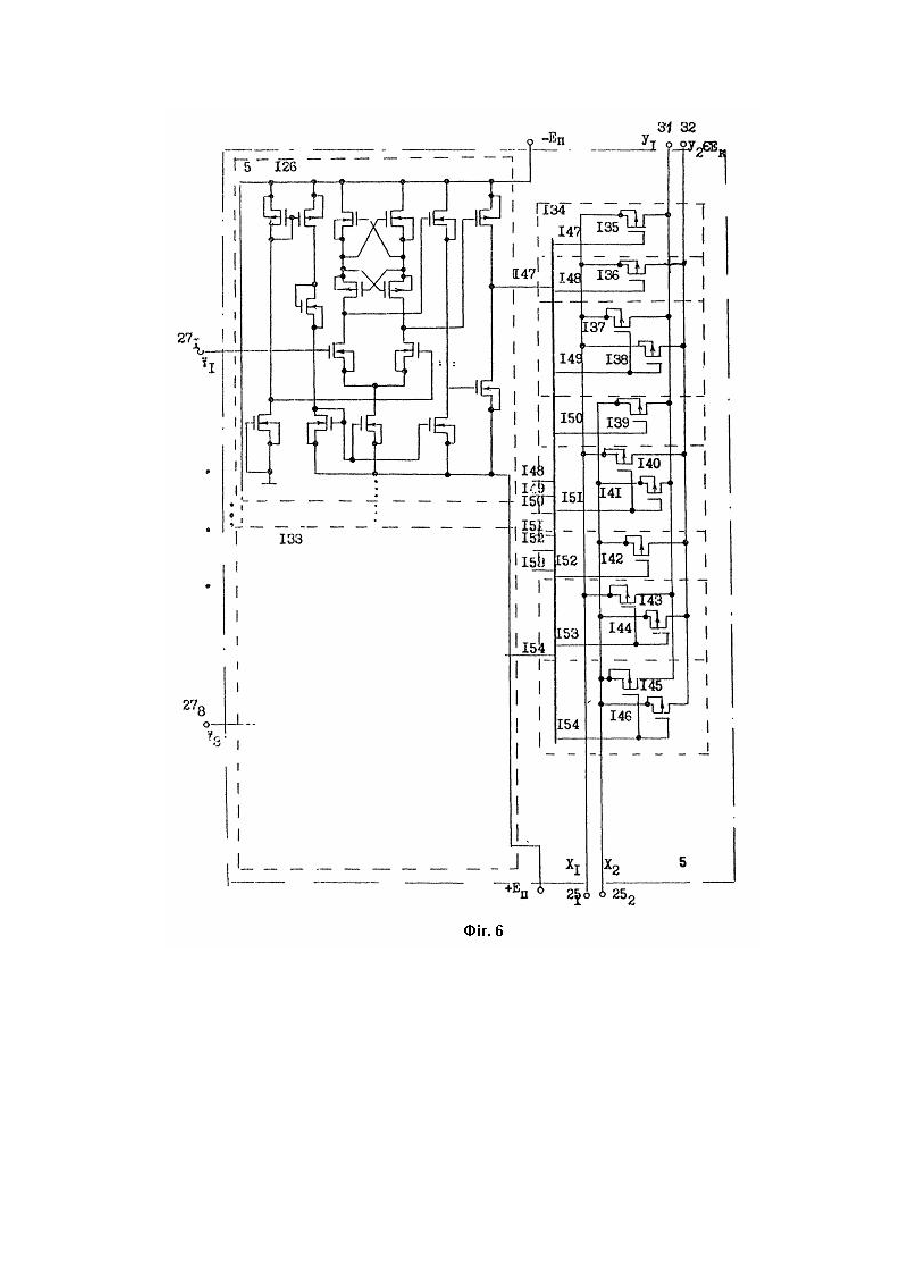

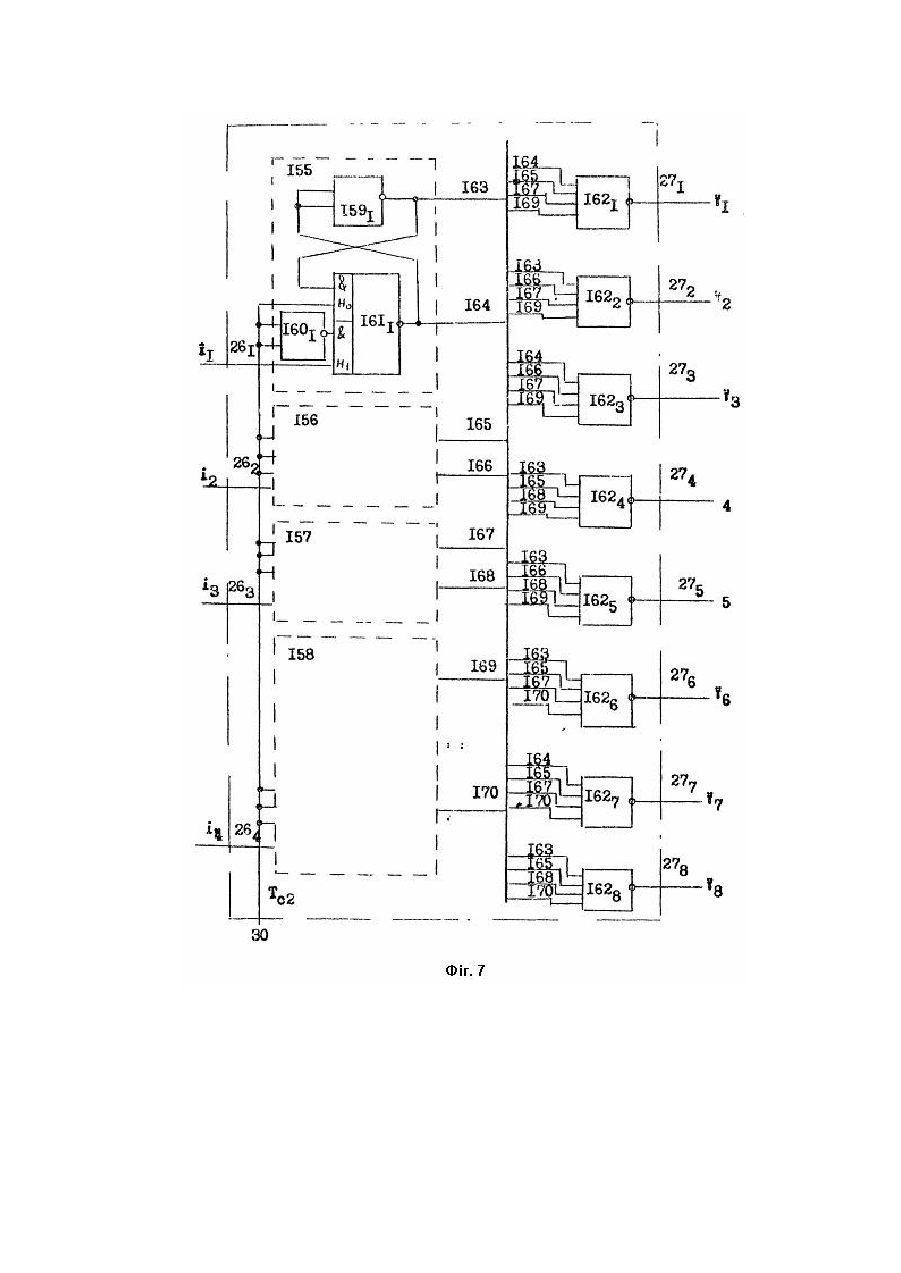

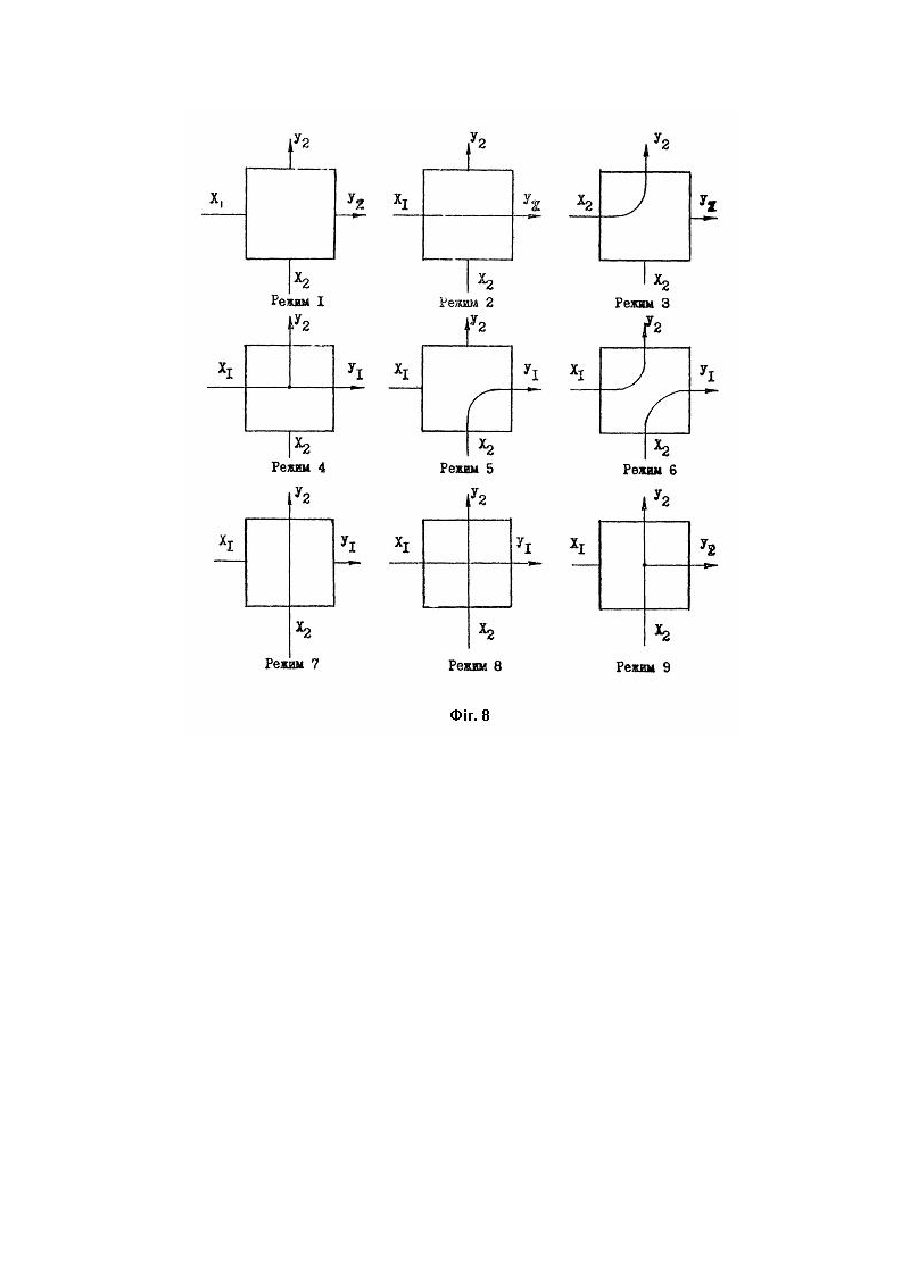

Изобретение относится к области вычислительной техники, в частности, к много процессорным вычислительным системам и гибкопрограммируемым структурам, и может быть использовано для построения многозначных вычислительных систем объемно-параллельного типа. Известно устройство для передачи и приема многоуровневых сигналов [1], содержащее два линейных блока, выполненных на дешифраторах и коммутаторах, источник опорных токов, источник базисных токов, источник информации и три линии связи. Это устройство характеризуется большими аппаратурными затратами, отсутствием возможности коммутации. Наиболее близким к заявляемому является устройство [2] для передачи и приема информации с многозначным кодированием, содержащее канал связи, выход которого подключен ко входу аналогоцифрового преобразователя (АЦП), выходы которого соединены со входами преобразователя единичного кода а двоичный, преобразователь двоичного кода в единичный, выходы которого подключены ко входам цифро-аналогового преобразователя (ЦАП). Однако это устройство для приема и передачи информации с многозначным кодированием обладает ограниченными функциональными возможностями из-за реализации только передачи многозначных входных сигналов и только в одном пространственном направлении. Задачей изобретения является усовершенствование устройства для приема и передачи информации с многозначным кодированием путем введения вторых - n-х каналов связи, аналого-цифрового и цифроаналогового преобразователей, преобразователей единичного кода в двоичный и двоичного кода в единичный, а также ключевого коммутатора и узла управления, чем обеспечивается n-мерная коммутация и мультиплексирование многозначных сигналов и, следовательно, расширяются функциональные возможности. Поставленная задача решается тем, что в устройство для приема и передачи с многозначным кодированием, содержащее первый канал связи, выход которого подключен ко входу первого аналогоцифрового преобразователя, выходы которого соединены со входами первого преобразователя единичного кода в двоичный, первый преобразователь двоичного кода в единичный, выходы подключены ко входам первого цифро-аналогового преобразователя, согласно изобретению, в устройство введены второй - n-й каналы связи (n>2), второй - n-й и аналого-цифровые преобразователи, второй - n-й преобразователи единичного кода в двоичный, второй - n-й преобразователи двоичного кода в единичный, второй - n-й цифро-аналоговые преобразователи, ключевой коммутатор и узел управления, вход синхронизации и управляющие входы которого являются одноименными входами устройства, вы ходы узла управления подключены к управляющим входам ключевого коммутатора, выходы первого преобразователя единичного кода в двоичный подключены к информационным входам первого преобразователя двоичного кода в единичный, тактовый вход которого является первым тактовым входом устройства, тактовый вход і-го ( ) преобразователя двоичного кода в единичный i = 2, n является і-м тактовым входом устройства, выход і-го канала связи подключен ко входу і-го аналого-цифрового преобразователя, выходы которого через і-й преобразователь единичного кода в двоичный подключены к информационным входам і-го преобразователя двоичного кода в единичный, выходы которого соединены со входами і-го аналогоцифрового преобразователя, выходы первого - n-го цифро-аналоговых преобразователей подключены соответственно к первому - n-му информационным входам ключевого коммутатора, первый - n-й выходы которого являются одноименными выходами устройства. Поставленная задача также решается тем, что преобразователь единичного кода в двоичный содержит первый-четвертый логические блоки, каждый из которых включает в себя первый и второй элементы НЕ, первый-третий элементы И и элемент ИЛИ, первые входы первого и второго элементов И первого логического блока объединены и являются первым входом преобразователя, выходы элементов ИЛИ в первом и втором логических блоках подключены к первым входам первого и второго элементов И соответственно во втором и третьем логических блоках, вход первого элемента НЕ и второй вход второго элемента И в каждом из первого-третьего логических блоков объединены и являются соответствующими входами преобразователя, первый вход третьего элемента И в каждом из первого-третьего логических блоков являются соответствующими входами преобразователя, выход второго элемента И первого логического блока соединен с первыми входами первого и второго элементов И четвертого логического блока, выход второго элемента И второго логического блока подключен к входу первого элемента НЕ и второму входу второго элемента И четвертого логического блока. выход второго элемента И третьего логического блока подключен к первому входу третьего элемента И четвертого логического блока, выходы первого и второго элементов НЕ в каждом логическом блоке соединены со вторыми входами соответственно первого и третьего элементов И того же логического блока, выход первого элемента И в каждом логическом блоке соединен с первым входом элемента ИЛИ и входом второго элемента НЕ того же логического блока, выход третьего элемента И в каждом логическом блоке подключен ко второму входу элемента ИЛИ того же логического блока, выход элемента ИЛИ третьего логического блока и выходы элемента ИЛИ и второго элемента И четвертого логического блока являются соответствующими выходами преобразователя. Поставленная задача, кроме того, решается тем, что преобразователь двоичного кода в единичный содержит первый-третий элементы НЕ, первый-шестой элементы И-НЕ, первый-третий RS-триперы и первый-седьмой элементы И, первые входы всех элементов И-НЕ объединены и являются тактовым входом преобразователя, вход j-го элемента НЕ (j = 1, 2, 3) объединены со вторым входом (2j)-го элемента И-НЕ и является соответствующим входом преобразователя, выход j-го элемента НЕ соединен со вторым входим (2j-1)-го элемента И-НЕ, выходы (2j-1)-го и (2j)-го элементов И-НЕ подключены соответственно к Rи S-входам j-го RS-триггера, прямые и инверсные выходы всех RS-триггеров подключены к соответствующим входам первого-седьмого элементов И, выходы которых являются вы ходами преобразователя. Введение в устройство для приема и передачи информации с многозначным кодированием вторых - n-х каналов связи (n>2), вторых - n-х преобразователей единичного кода в двоичный, вторых - n-х цифроаналоговых и аналого-цифровых преобразователей, вторых - n-х преобразователей двоичного кода в единичный, ключевого коммутатора и узла управления обеспечивает мультиплицирование, коммутацию и передачу многозначных данных в структуре объемно-параллельных вычислительных структур, систем и сред, что позволяет пространственным способом решать задачи приоритетов и очередей в цифровых системах коммутации и сетях с интеграцией обслуживания и, тем самым, обеспечить решение задачи расширения функциональных возможностей. На фиг. 1 показана структурная схема устройства для приема и передачи информации с многозначным кодированием; на фиг. 2 - принципиальная схема аналого-цифрового преобразователя; на фиг. 3 функциональная схема преобразователя единичного кода в двоичный; на фиг. 4 - функциональная схема преобразователя двоичного кода в единичный; на фиг. 5 - принципиальная схема цифро-аналогового преобразователя; на фиг. 6 - принципиальная схема ключевого коммутатора; на фиг. 7 - функциональная схема узла управления; на фиг. 8 - режимы коммутации устройства для случая реализации двухканальной коммутации. Устройство для приема и передачи информации с многозначным кодированием (см. фиг. 1) приведено для случая двухканальной коммутации (простейший вариант) и поэтому содержит два идентичных устройства приема и передачи информации, которые включают в себя аналого-цифровой преобразователь 1 (АЦП), преобразователь 2 единичного кода в двоичный, преобразователь 3 двоичного кода в единичный, цифро-аналоговый преобразователь 4 (ЦАП), ключевой коммутатор 5, узел 6 управления, вход 7 АЦП 1, входы 8-14 преобразователя 2 единичного кода в двоичный, входы 15-17 преобразователя 3 двоичного кода в единичный, входы 18-24 ЦАП 4, первый и второй входы 251 и 252 ключевого коммутатора 5, четыре входа 26 узла 6 управления, восемь выходов 27 узла 6 управления, вход 26 синхронизации ТС1" преобразователя 3 двоичного кода в единичный первого устройства приема и передачи информации, вход 29 синхронизации ТС1"" преобразователя 3 двоичного кода в единичный второго устройства приема и передачи информации, вход 30 синхронизации ТС2 узла 6 управления, а также первый Υ1 и второй Y2 выходы 31, 32 ключевого коммутатора, соответственно, причем входы 7 двух идентичных устройств приема и передачи информации и четыре входа 26 узла 6 управления служат информационными входами устройства для приема и передачи информации с многозначным кодированием, выходы 8-14 АЦП 1 являются входами преобразователя 2 единичного кода в двоичный, выходы 15-17 преобразователя единичного кода в двоичный подключены к соответствующим входам преобразователя 3 двоичного кода в единичный являются входами ЦАП 4, вы ходы 25 которого являются выходами первого устройства приема и передачи информации, выходы 25 устройства приема и передачи информации, а также восемь выходов 27 узла 6 управления подключены к ключевому коммутатору 5, вы ходы 31, 32 которого образуют вы ходы 31, 32 устройства для приема и передачи информации с многозначным кодированием, вход 28 синхронизации ТС1" подключен к входам преобразователя 3 двоичного кода в единичный первого устройства приема и передачи информации, вход 29 синхронизации ТС1"" подключен к входам преобразователя 3 двоичного кода в единичный второго устройства приема и передачи информации, вход 30 синхронизации ТС2 подключен к узлу 6 управления. Аналого-цифровой преобразователь 1 (см. фиг. 2) содержит семь идентичных компараторов 33-39 на дифференциальных усилителях, состоящи х из транзисторов 40-55, формирователь 56 опорного напряжения на транзисторах 57-63, резистор 64, причем первые входы компараторов 33-39 объединены и образуют вход 7 аналого-цифрового преобразователя 1, а вторые входы подключены к формирователю 56 опорного напряжения, выходы компараторов 33-39 образуют выходы 6-14 аналого-цифрового преобразователя 1. Преобразователь 2 единичного кода в двоичный (см. фиг. 3) состоит из четырех идентичных блоков 6568, содержащих логические элементы 72, 73 НЕ, 74-76 И, 77 ИЛИ, входы 6-14 преобразователя 2, выходы 69-71 элемента 75, выходы 78, 79 элемента 77 ИЛИ, выходы 15-17 преобразователя 2 единичного кода в двоичный, причем входы элементов 72, 74, 76 первого блока 65 преобразователя 2, а также входы элементов 74, 76 блоков 66, 67 образуют входы 8-14 преобразователя 2 единичного кода в двоичный, выходы элементов 72, 73 НЕ соединены с элементами 74, 76 И, входы элементов 72 НЕ и 74 И подключены к входам элемента 75 И, выходы элементов 74 И, 76 И соединены с входами элемента 77 ИЛИ, вход элемента 73 НЕ подключен к первому входу элемента 77 ИЛИ, выходы элементов 75 И и 77 ИЛИ образуют выходы 69, 78 первого блока преобразователя 2 единичного кода в двоичный, выходы 78, 79 элемента 77 ИЛИ каждого предыдущего блока подключены к входу последующего блока, выход элемента 77 ИЛИ блока 67 образует выход 15 преобразователя 2 единичного кода в двоичный, выходы 69-71 элементов 75 подключены соответственно к входам блока 68, выходы которого образуют выходы 16, 17 преобразователя 2 единичного кода в двоичный. Преобразователь 3 двоичного кода в единичный (см. фиг. 4) построен на логических элементах 80-82 НЕ, 831-833, 841-843 И-НЕ, 85-87 RS-триггерах, 88-94 И, причем входы элементов 80-82 НЕ образуют входы 16-17 преобразователя 3 двоичного кода в единичный, инвертирующие выходы элементов 80-82 НЕ соединены со входами элементов 83 И-НЕ, входы элементов 80-82 НЕ соединены со входами элементов 84 И-НЕ, ко входам элементов 83, 84 И-НЕ подключен сигнал синхронизации (входы 28, 29) для первого и второго устройств приема и передачи информации, соответственно ТС1", ТС 1"", инвертирующие вы ходы элементов 83, 84 И-НЕ подключены ко входам RS-триггеров 85-87, выходы 95-100 которых соединены с элементами 88-94 И, а выходы 18-24 последних образуют вы ходы преобразователя 3 двоичного кода в единичный. Цифроаналоговый преобразователь 4 (см. фиг. 5) содержит семь идентичных блоков 101-107 управления, ключи 108, его транзисторы 109-115, делителя 116 опорного напряжения, его транзисторы 117124, резистор 125, ограничивающий ток делителя опорных напряжений, причем выходы блоков 101-107 управления соединены соответственно с затворами ключевых транзисторов 109-115, коллекторы которых объединены вместе и образуют выход 25 цифроаналогового преобразователя 4, а истоки подключены к соответствующим точкам делителя 116 опорного напряжения. Ключевой коммутатор 5 (см. фиг. 6) содержит восемь блоков 126-133 управления и восемь шинных коммутаторов 134 на проходных транзисторах 135-146, причем входы 271-278 блоков 126-133 управления образуют входы ключевого коммутатора 5, а вы ход первого блока 126 управления подключен к затвору проходного транзистора 135, исток которого подключен к шине второго входа 251 ключевого коммутатора 5, а сток - к шине первого выхода 31 ключевого коммутатора 5, вы ход второго блока 127 управления подключен к затвору проходного транзистора 136, исток которого подключен к шине входа 251 ключевого коммутатора 5, сток к шине второго выхода 31 ключевого коммутатора 5, выход третьего блока 128 управления подключен к затворам первого и второго проходных транзисторов 137, 138, истоки которых подключены к шине первого входа 251 ключевого коммутатора 5, сток первого транзистора 137 - к шине первого выхода 31 ключевого коммутатора 5, сток второго транзистора 138 - к шине второго выхода 32 ключевого коммутатора 5, выход четвертого блока 129 управления подключен к затвору проходного транзистора 139, исток которого подключен к шине второго входа 252 ключевого коммутатора 5, сток - к шине первого выхода 31 ключевого коммутатора 5, выход пятого блока 130 управления подключен к затвору первого и второго проходных транзисторов 140, 141, исток первого транзистора 140 подключен к шине первого входа 251 ключевого коммутатора 5, исток второго транзистора 141 - к шине второго входа 252 ключевого коммутатора 5, сток первого транзистора 140 подключен к шине второго выхода 32 ключевого коммутатора 5, а сток второго транзистора 141 - к шине первого выхода 31 ключевого коммутатора 5, вы ход шестого блока 131 управления подключен к затвору проходного транзистора 142, исток которого подключен к шине второго входа 252 ключевого коммутатора 5, сток - к шине второго выхода 32 ключевого коммутатора 5, вы ход седьмого блока 132 управления подключен к затворам первого и второго проходных транзисторов 143, 144, исток первого транзистора 143 подключен к шине первого входа 251 ключевого коммутатора 5, исток второго транзистора 144 - к шине второго входа 252 ключевого коммутатора 5, сток первого транзистора 143 - к шине первого выхода 31 ключевого коммутатора 5, сток второго проходного транзистора 144 - к шине второго выхода 32 ключевого коммутатора 5, выход восьмого блока 133 управления подключен к затворам первого и второго проходных транзисторов 145, 146, истоки которых подключены к шине второго входа 25 2 ключевого коммутатора 5, сток первого транзистора 145 подключен к шине первого выхода 31 ключевого коммутатора 5, сток второго транзистора 146 - к шине второго выхода 32 ключевого коммутатора 5, а стоки проходного транзистора 135, первого проходного транзистора 137, проходного транзистора 139, второго проходного транзистора 141, первого проходного транзистора 143 и первого проходного транзистора 145 выведены на общую шину, являющуюся шиной первого выхода 31 ключевого коммутатора 5, а стоки проходного транзистора 136, второго проходного транзистора 138, первого проходного транзистора 140, проходного транзистора 142, второго проходного транзистора 144 и второго проходного транзистора 146 соединены общей шиной, являющейся шиной второго выхода 32 ключевого коммутатора 5. Узел управления 6 (см. фиг. 7) содержит четыре идентичных параллельных регистра 155-158 на Dтриггерах типа "защелка", состоящих из логических элементов 159, 160 И-НЕ и элемента 161 2И-ИЛИ-НЕ, а также содержит восемь элементов 162 И-НЕ, причем, четвертые входы регистров 155-158 образуют входы 261-264 узла 6 управления. остальные три входа регистров 155-158 объединены и образуют вход 30 синхронизации ТС2, прямые и инверсные выходы регистров 155-158 через шинный коммутатор соединены с четырехвходовыми элементами 1621-162 8 И-НЕ соответственно, выходы которых образуют выходы 271-278 узла 6 управления. Устройство работает следующим образом. Процесс функционирования проиллюстрируем на примере устройства с восьмизначным кодированием (k = 8). В исходном состоянии на входах 7 устройства для приема и передачи информации с многозначным кодированием (см. фиг. 1) присутствуют два одноразрядных восьмизначных сигнала Χ1, Χ2 , равные логическому нулю (табл. 1). Эти значения исходных сигналов аналого-цифровыми преобразователями 1 (см. фиг. 2) преобразуются в семиразрядный единичный пространственный код вида на выходах 8-14, а затем преобразователем 2 единичного кода в двоичный (см. фиг. 3) - преобразуются в тре хразрядный позиционный код на выходах 1517 (см. табл. 1) вида , эти сигналы под воздействием тактирующего сигнала ТС1" и ТС1"" передаются на входы преобразователей 3 двоичного кода в единичный (табл. 2). На выходах 18-24 преобразователей 3 (см. фиг. 4) формируется семиразрядный унитарный пространственный код вида (см. табл. 2), который дальше поступает на цифро-аналоговые преобразователи 4 (см. фиг. 5), работа которых подробно описана в [2] и определяется табл. 3. На выходах 25 этих преобразователей формируются одноразрядные восьмизначные сигналы, соответствующие логическому нулю (см. табл. 3). Эти значения выходных сигналов поступают на ключевой коммутатор 5 (см. фиг. 8), где коммутируются в соответствии с программой коммутации, поступающей с узла (см. фиг. 7) управления, принцип действия которой определяется табл. 4 в соответствии с режимами коммутации (см. фиг. 5). На четыре входа 26і (і = 1…4) узла управления 6 (см. фиг. 7) поступают управляющие двузначные сигналы вида , под воздействием которых на выходах 27ї (ї = 1...3) узла 6 управления формируются выходные функции коммутации (см. табл. 3), предоставленные унитарным двузначным кодом. Значения кода поступают на входы 27ї восьми схем управления ключевого коммутатора 5 (см. фиг. 6), сформированного на проходных транзисторах МОП-типа. Согласно табл. 4 ключевой коммутатор 5 настраивается на выполнение одной из девяти функций коммутации и передачи данных, представленных на фиг. 8, и в исходном состоянии (см. табл. 4), при сигнале на входах 26і узла 6 управления, на выходе последней будут тоже нулевые сигналы , обеспечивающие выключенное состояние всех проходных транзисторов 135-146 шинного коммутатора 134 и, как следствие, нулевые выходные сигналы на выходах 31, 32 устройства в целом. Таким образом, процесс функционирования устройства для приема и передачи информации с многозначным кодированием (см. фиг. 1) определяется сигналами управления процессом коммутации и синхросигналами управления процессами передачи данных Тс1" и Тс1"", а также синхросигналом Тс2 разрешения на запись входного сигнала узла 6 управления. Задавались синхросигналами Тс1" = Тс2"" = ТС2 = 1 и подав на входы 7 сигналы Χ1 = 7, Х2 = 7, рассмотрим процедуры приема, передачи и коммутации их на выходы 31, 32 устройства. Допустим с узла 6 управления (см. фиг. 1) на ключевой коммутатор 5 поступает девятая программа коммутации (см. табл. 4). Входной одноразрядный восьмизначный сигнал Х2 = 7 (см. табл. 1) поступает на вход аналого-цифрового преобразователя 1 (см. фиг. 2), где преобразуется в семиразрядный единичный пространственный код вида , а затем преобразователем 2 единичного кода в двоичный (см. фиг. 3) [2] преобразуется в трехразрядный единичный код на выходах 1517 (см. табл. 1) вида . Этот код под воздействием тактирующего сигнала Тс1"" передается на входы 15-17 преобразователя 3 двоичного кода в единичный (см. фиг. 1). На выходах преобразователя 3 двоичного кода в единичный (см. фиг. 4) формируется семиразрядный унитарный пространственный код (см. табл. 2) вида , поступающий в дальнейшем на цифро-аналоговый преобразователь 4 (см. фиг. 5) [2]. На выходе 251 преобразователя 4 формируется одноразрядный восьмизначный сигнал (см. табл. 3) Y2 = 7. Значение выходного сигнала поступает на ключевой коммутатор 5, где коммутируются в соответствии с девятой программой коммутации (см. табл. 4), обеспечивающей включенное состояние проходных транзисторов 145, 146 восьмого ключа шинного коммутатора 134 и разветвление информации Х2 в двух перпендикулярных направлениях на выходы 31, 32 устройства в целом (см. фиг. 8, режим 9). В зависимости от задаваемой программы коммутации ключевой коммутатор 5 (см. фиг. 6) настраивается на работу в одном из девяти режимов коммутации (см. фиг. 8, табл. 4). В соответствии с табл. 4, для реализации девяти функций коммутации в ключевом коммутаторе 5 используются восемь ключей шинного коммутатора 134 на проходных транзисторах, причем а каждом ключе шинного коммутатора в зависимости от конкретной функции хранения и передачи информации имеется по одному, либо по два проходных транзистора. Все восемь ключей шинного коммутатора 134 соединены параллельно между входными 251 и 252 и выходными 31, 32 шинами устройства (см. фи г. 1, 6). Основываясь на логическом синтезе сетей из проходных транзисторов применительно к многоуровневой логике, где каждая логическая функция МСП-транзисторов определена, можно получить уравнения логических функций, отражающих связь между входными сигналами Χ1, Х2 и выходными Υ1, Υ2. Исходя из того, что связь между входными Χ1 и выходными Υ1 сигналами, с учетом внешнего параметра Ζ (сигнала управления) записывается как: ì Y , если Х = 1 Y1 = X1БZ > = í 1 (1) î 0, если Х = 0 схему шинного коммутатора 134, в соответствии с ее режимами работы, можно разбить на четыре схемы параллельных соединений с общими входами, каждая из которых описывается следующей зависимостью Yi = Xi (2) Для первой, произвольно выбранной, схемы параллельного соединения с общими входом Χ1 и вы ходом Υ1 (см. фиг. 5), зависимость (2) запишется в следующем виде: Y1 = X1 (3) где Z1 , Z 3, Ζ7 - сигналы управления первого, третьего и седьмого ключей соответственно. Для соединения с общими входом Χ1 и выходом Υ2 получено следующую зависимость: Y2 =

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for multivalued coding receive and data transmission

Автори англійськоюKonoplianko Zenovii Dmytrovych, Popovych Halyna Bohdanivna, Losieva Tetiana Vitalivna

Назва патенту російськоюУстройство для приема и передачи информации с многозначным кодированием

Автори російськоюКоноплянко Зеновий Дмитриевич, Попович Галина Богдановна, Лосева Татьяна Витальевна

МПК / Мітки

МПК: G08C 19/28, H03M 5/00

Мітки: пристрій, приймання, інформації, передачі, багатозначним, кодуванням

Код посилання

<a href="https://ua.patents.su/15-5696-pristrijj-dlya-prijjmannya-ta-peredachi-informaci-z-bagatoznachnim-koduvannyam.html" target="_blank" rel="follow" title="База патентів України">Пристрій для приймання та передачі інформації з багатозначним кодуванням</a>

Попередній патент: Спосіб виготовлення ємності з металу з внутрішньою оболонкою

Наступний патент: Стереофонічна акустична система

Випадковий патент: Установка фільтраційного сушіння сипких матеріалів