Система керування

Номер патенту: 56399

Опубліковано: 15.07.2004

Автори: Чигирин Юрій Трохимович, Остапов Анатолій Олександрович, Маранов Олександр Вікторович, Чигирин Олег Трохимович

Формула / Реферат

Система керування, що складається з багаторозрядного цифрового лічильного каналу, дешифратора, схеми керування, яка включає формувач і два елементи затримки, і генератора, вихід якого з'єднано з першими входами першого багаторозрядного цифрового лічильного каналу, схеми керування і дешифратора, вихід якого з'єднано з виходом системи керування, вхід схеми керування через перший елемент затримки, перший формувач і другий елемент затримки з'єднано з першим виходом схеми керування, другий вихід якої з'єднано з входом другого елемента затримки та виходом першого формувача, яка відрізняється тим, що запроваджено три [в загальному випадку (m-1) багаторозрядні цифрові лічильні канали, де m = 4,5,6,...] багаторозрядні цифрові лічильні канали, вісім (2m) груп схем І, чотири (m) схеми контролю, групу схем АБО, схему І-НІ, схему парності і п'ять схем І, вихід першого багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами першої групи схем І і першої схеми контролю, перший, другий і третій виходи якої відповідно з'єднані з нульовими входами розрядів першого багаторозрядного цифрового лічильного каналу, першим входом другої групи схем І, другим входом першої групи схем І, вихід якої з'єднано з першим входом групи схем АБО, вихід якої з'єднано з другими входами другої, четвертої, шостої і восьмої (2m) груп схем І і другим входом дешифратора, вихід другого багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами третьої групи схем І і другої схеми контролю, перший, другий і третій виходи якої відповідно з'єднані з нульовими входами розрядів другого багаторозрядного цифрового лічильного каналу, першим входом четвертої групи схем І, другим входом третьої групи схем І, вихід якої з'єднано з другим входом групи схем АБО, вихід третього багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами п'ятої групи схем І і третьої схеми контролю, перший, другий і третій виходи якої відповідно з'єднані з нульовими входами розрядів третього багаторозрядного цифрового лічильного каналу, першим входом шостої групи схем І, другим входом п'ятої групи схем І, вихід якої з'єднано з третім входом групи схем АБО, вихід четвертого (m) багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами сьомої (2m-1) групи схем І і четвертої (m) схеми контролю, перший, другий і третій виходи якої відповідно з'єднані з нульовими входами розрядів четвертого (m) багаторозрядного цифрового лічильного каналу, першим входом восьмої (2m) групи схем І, другим входом сьомої (2m-1) групи схем І, вихід якої з'єднано з четвертим (m) входом групи схем АБО, вихід другої групи схем І з'єднано з одиничними входами розрядів першого багаторозрядного цифрового лічильного каналу, вихід четвертої групи схем І з'єднано з одиничними входами розрядів другого багаторозрядного цифрового лічильного каналу, вихід шостої групи схем І з'єднано з одиничними входами розрядів третього багаторозрядного цифрового лічильного каналу, вихід восьмої (2m) групи схем І з'єднано з одиничними входами розрядів четвертого (m) багаторозрядного цифрового лічильного каналу, другий вхід першої схеми контролю з'єднано з другими входами другої, третьої і четвертої (2m) схем контролю і першим виходом схеми керування, другий вихід якої з'єднано з третім входом першої схеми контролю, третім входом другої схеми контролю, третім входом третьої схеми контролю і третім входом четвертої (m) схеми контролю, четвертий вихід першої схеми контролю з'єднано з першим входом схеми І-НІ, другий, третій і четвертий входи якої з'єднані відповідно з четвертим виходом другої схеми контролю, з четвертим виходом третьої схеми контролю і з четвертим виходом четвертої (m) схеми контролю, п'ятий вихід першої схеми контролю з'єднано з першим входом першої схеми І, другий, третій і четвертий входи якої з'єднані відповідно з п'ятим виходом другої схеми контролю, з п'ятим виходом третьої схеми контролю і з п'ятим виходом четвертої (m) схеми контролю, входи першої схеми парності відповідно з'єднані з виходом схеми І-НІ і з виходом першої схеми І, вихід першої схеми парності з'єднано з першими входами другої, третьої, четвертої і п'ятої схем І, другий вихід першої схеми контролю з'єднано з другим входом другої схеми І, вихід якої з'єднано з четвертим входом першої схеми контролю, другий вихід другої схеми контролю з'єднано з другим входом третьої схеми І, вихід якої з'єднано з четвертим входом другої схеми контролю, другий вихід третьої схеми контролю з'єднано з другим входом четвертої схеми І, вихід якої з'єднано з четвертим входом третьої схеми контролю, другий вихід четвертої (m) схеми контролю з'єднано з другим входом п'ятої схеми І, вихід якої з'єднано з четвертим входом четвертої (m) схеми контролю, кожна схема контролю складається з двох схем парності, двох елементів затримки, другого формувача і схеми прогнозу, яка включає лічильний тригер, схему І, дві схеми АБО і формувач переходу непарних розрядів, який складається з формувачів переходу непарних розрядів, перший вхід схеми прогнозу з'єднано з першим входом схеми контролю, першим входом першої схеми АБО, інші входи якої з'єднані відповідно з виходами формувача переходу непарних розрядів, входи якого з'єднані з першим входом схеми прогнозу, другий вхід якої з'єднано з третім входом схеми контролю, першим входом шостої схеми І, вихід першої схеми АБО через другий вхід шостої схеми І, другу схему АБО і лічильний тригер з'єднано з першим виходом схеми прогнозу і першим входом другої схеми парності, другий вхід якої з'єднано з виходом третьої схеми парності, входи якої з'єднані з першим входом схеми контролю, другий вхід якої з'єднано з третім входом другої схеми парності, вихід якої через третій і четвертий елементи затримки з'єднано з другим виходом схеми контролю, перший вихід якої з'єднано з входом четвертого елемента затримки і виходом третього елемента затримки, третій вихід схеми контролю з'єднано через другий формувач з виходом другої схеми парності, перший вхід другої схеми парності з'єднано з четвертим виходом схеми контролю, п'ятий вихід якої з'єднано з другим виходом лічильного тригера і другим виходом схеми прогнозу, третій вхід якої з'єднано з другим входом другої схеми АБО і третім входом схеми контролю.

Текст

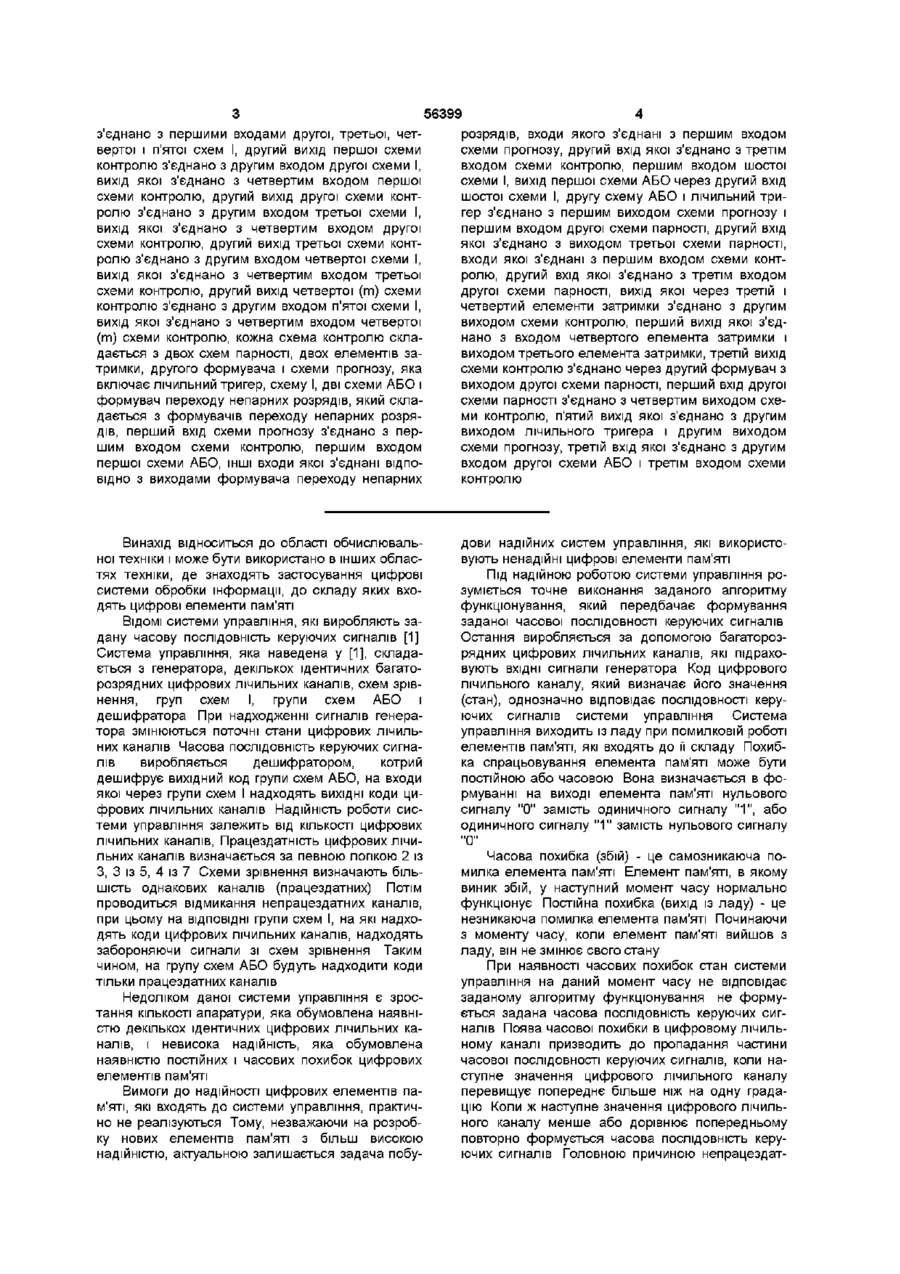

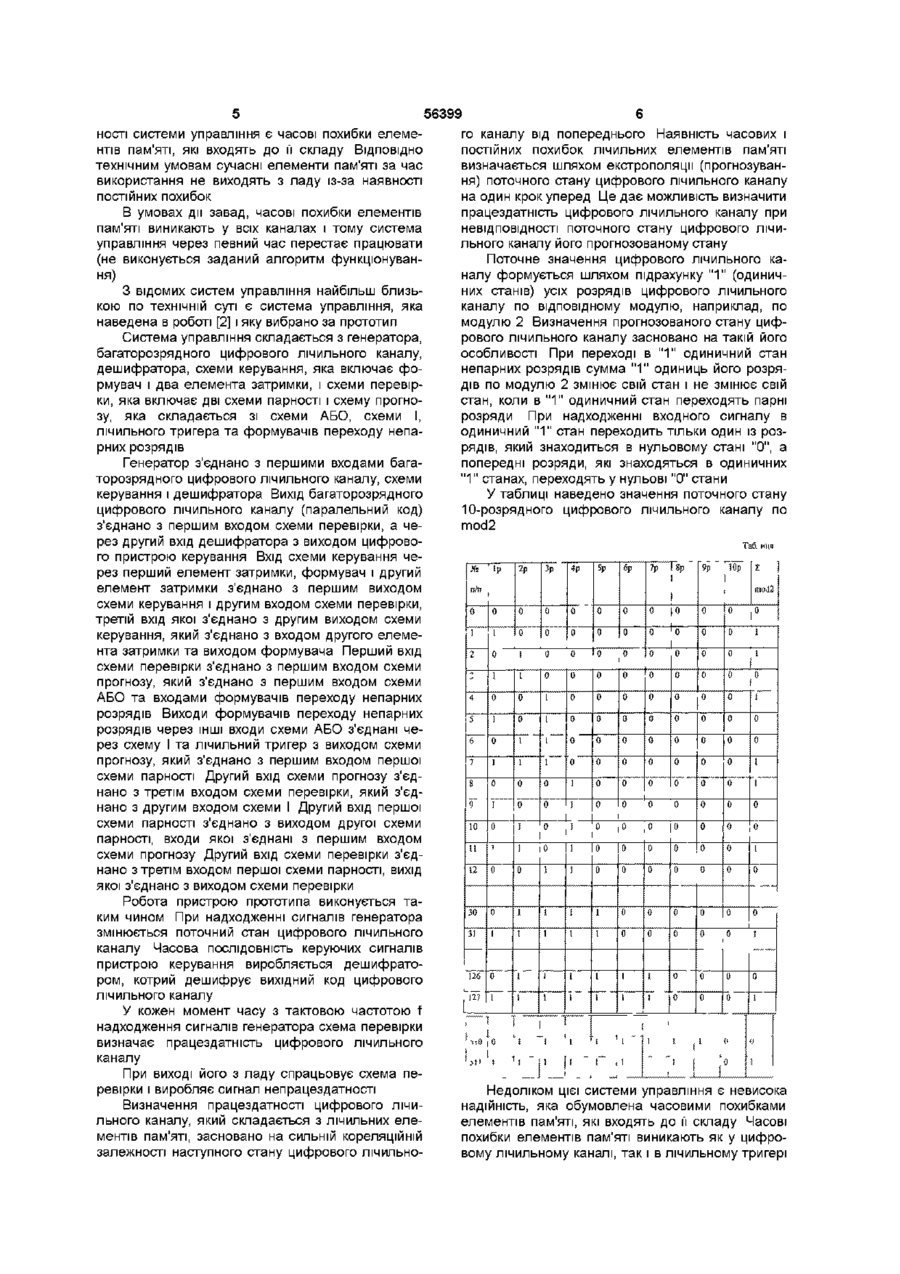

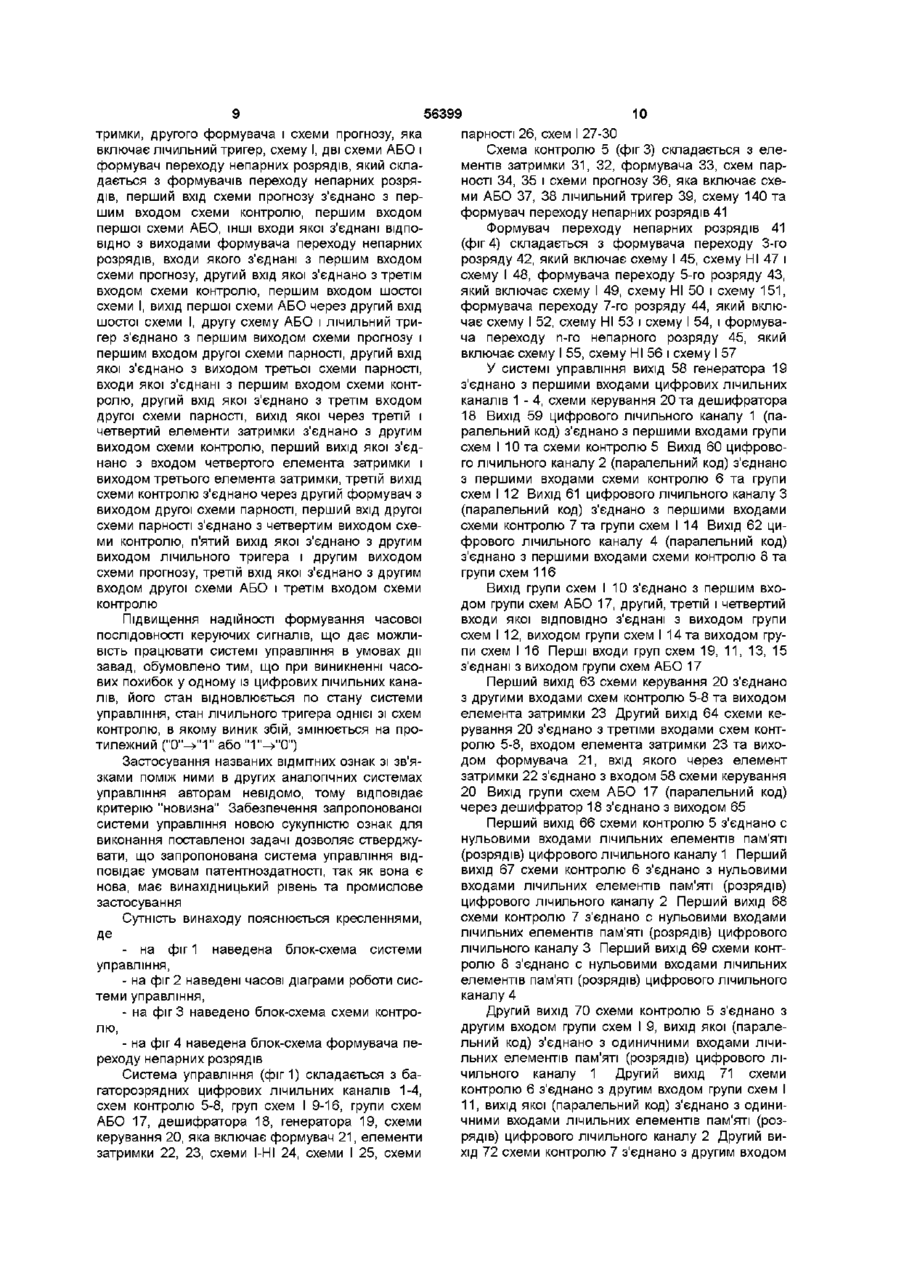

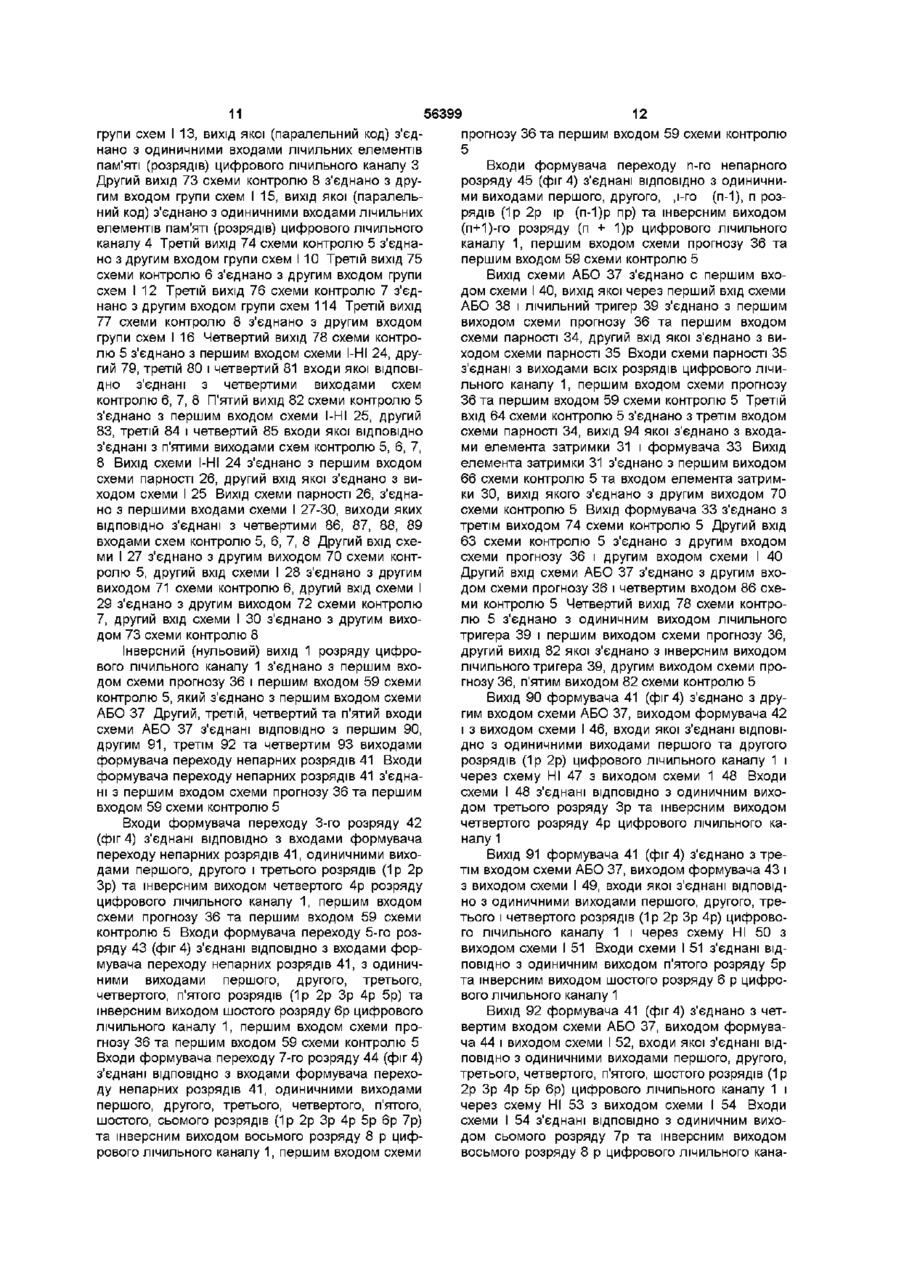

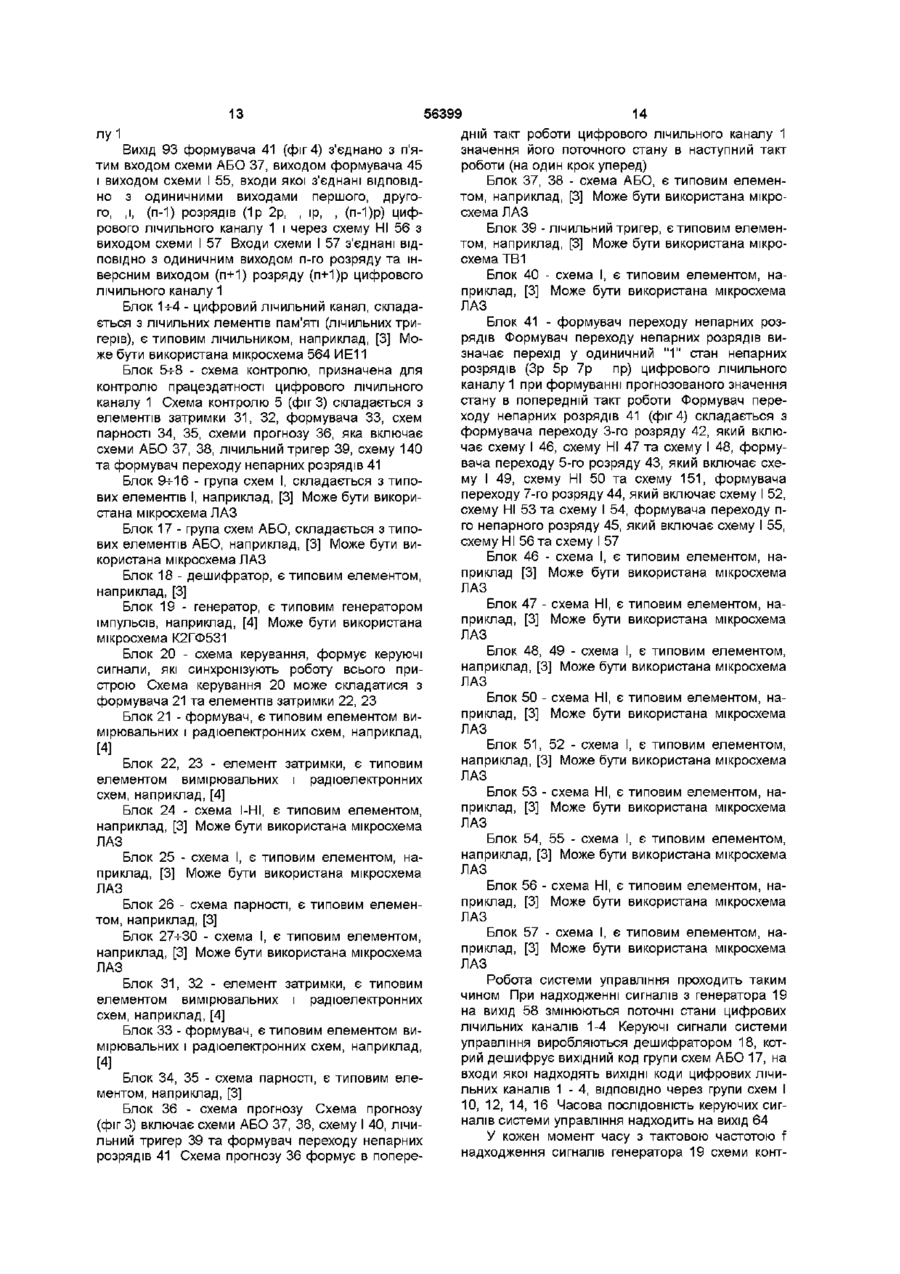

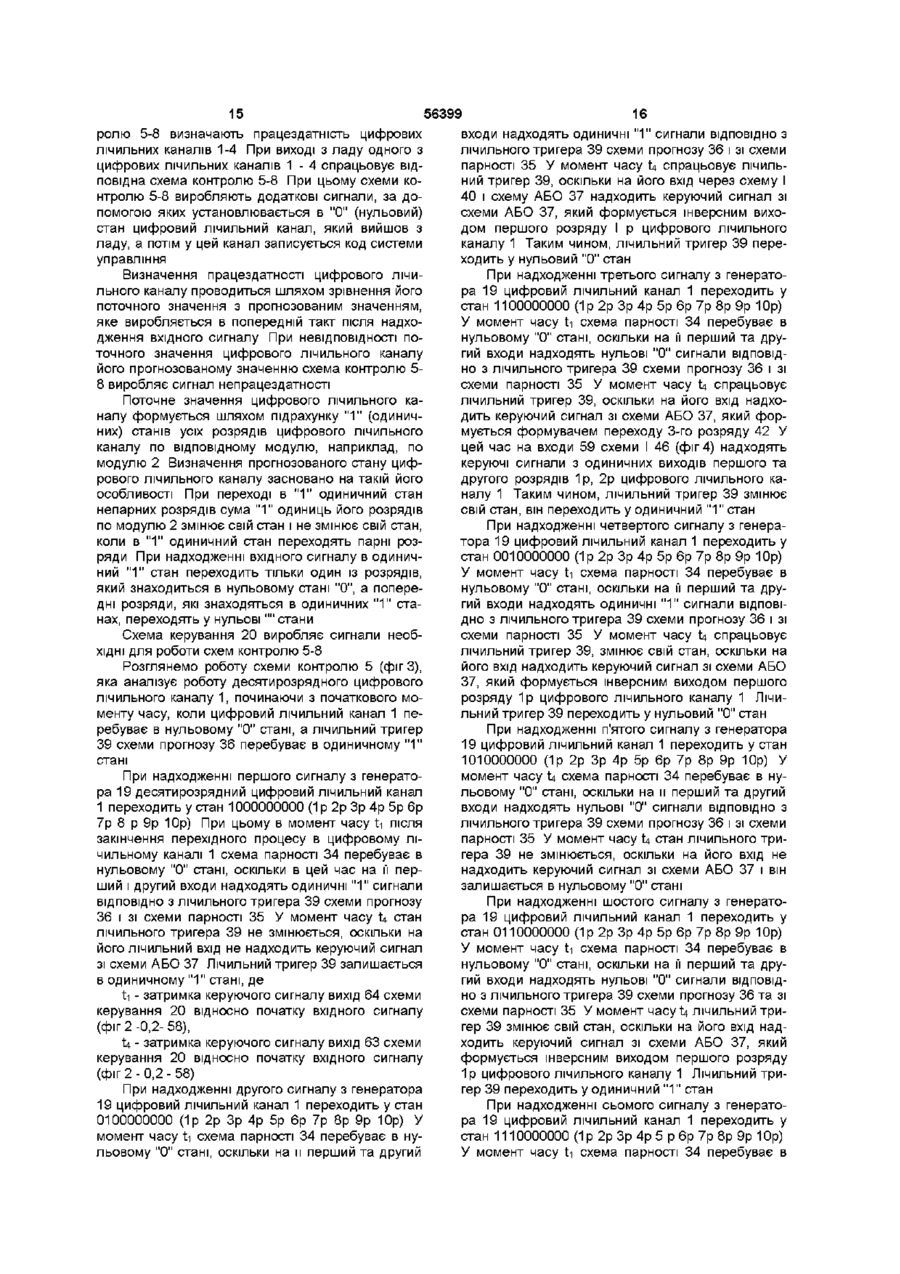

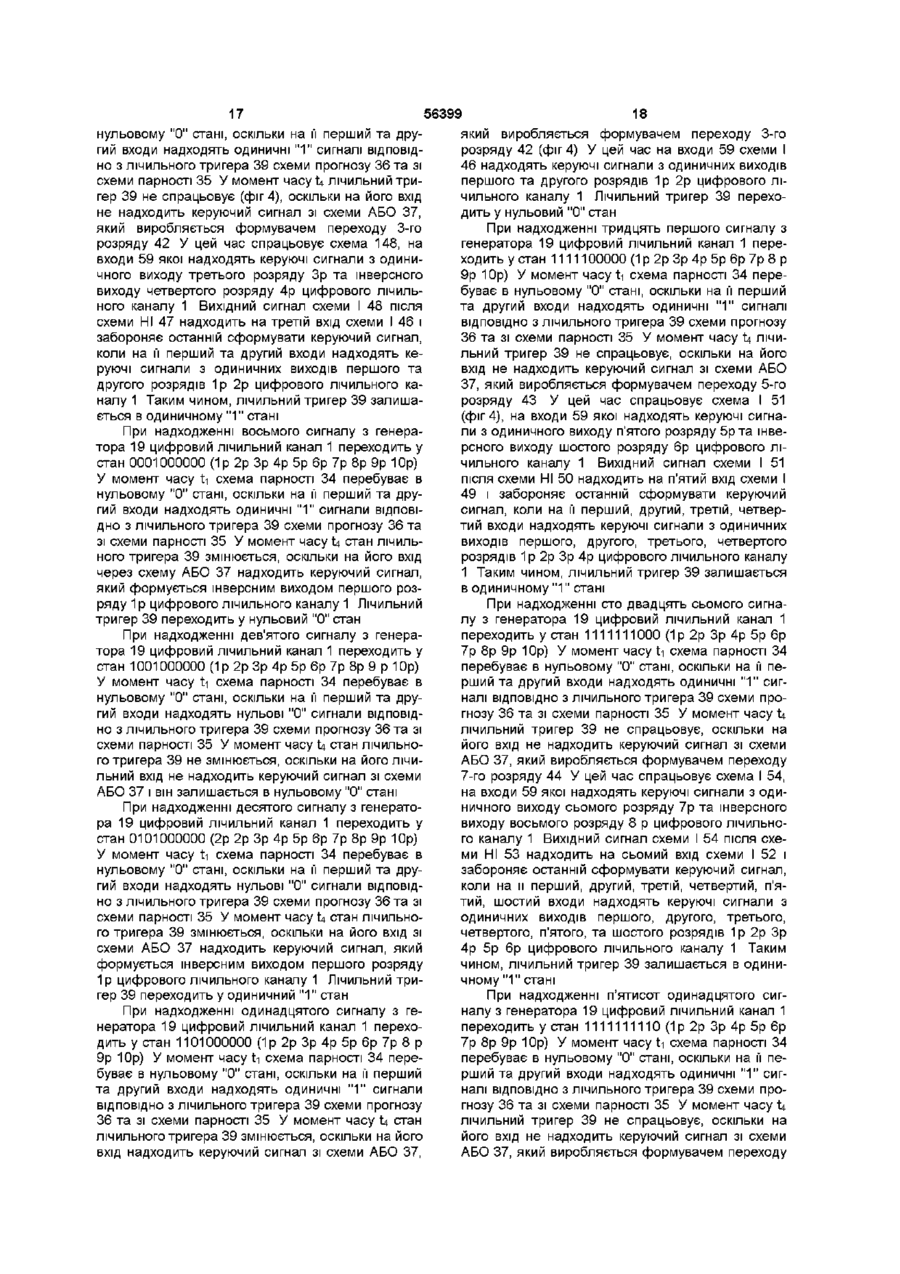

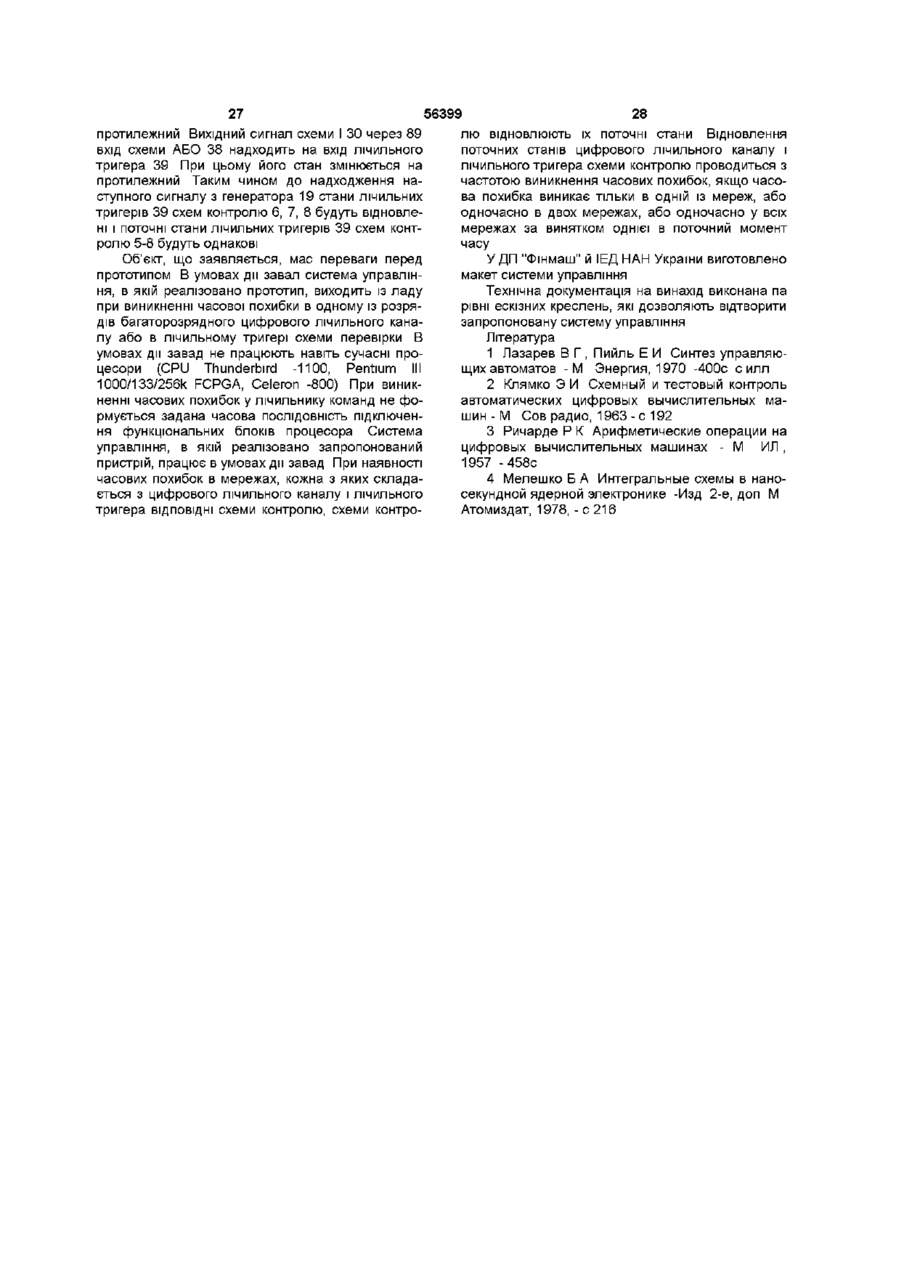

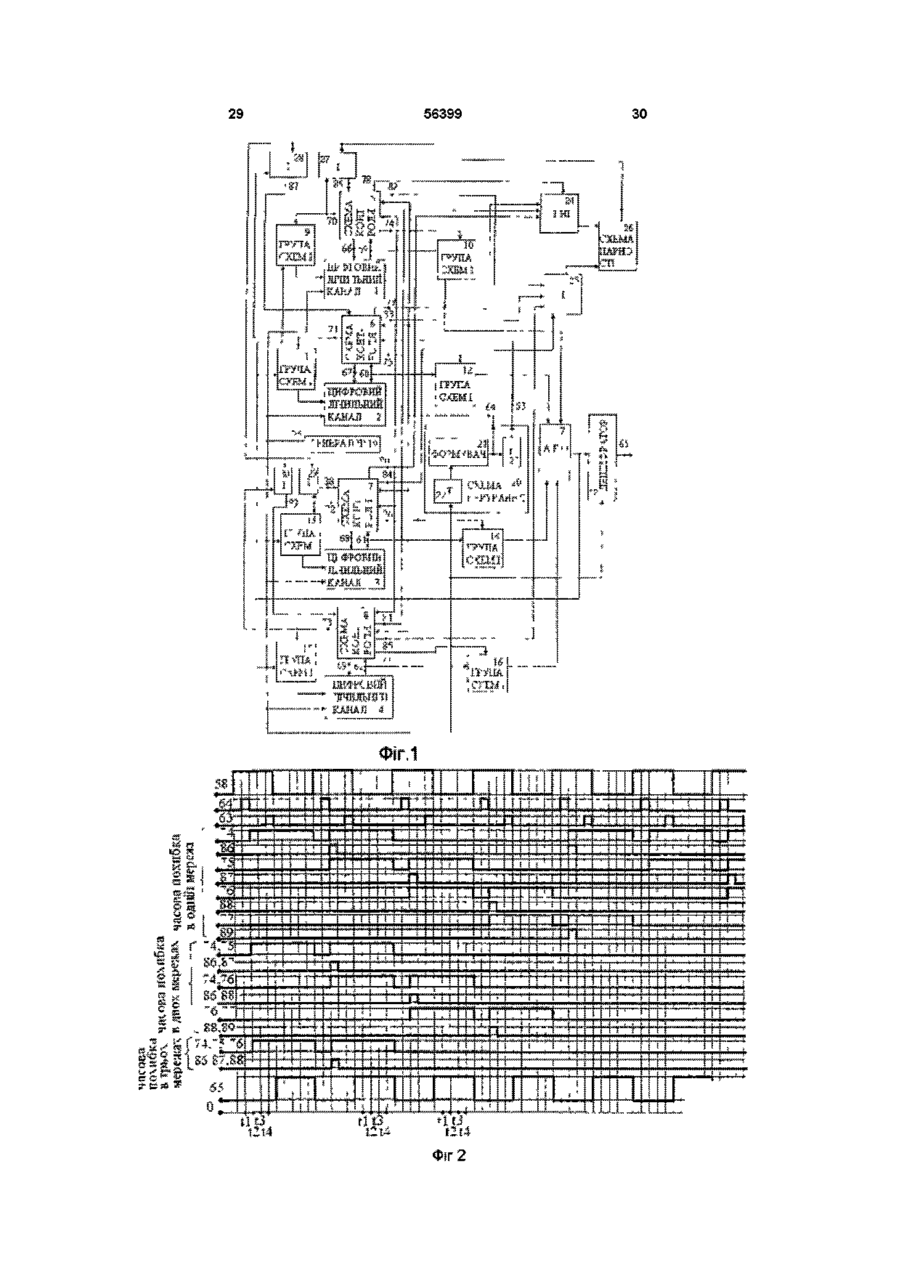

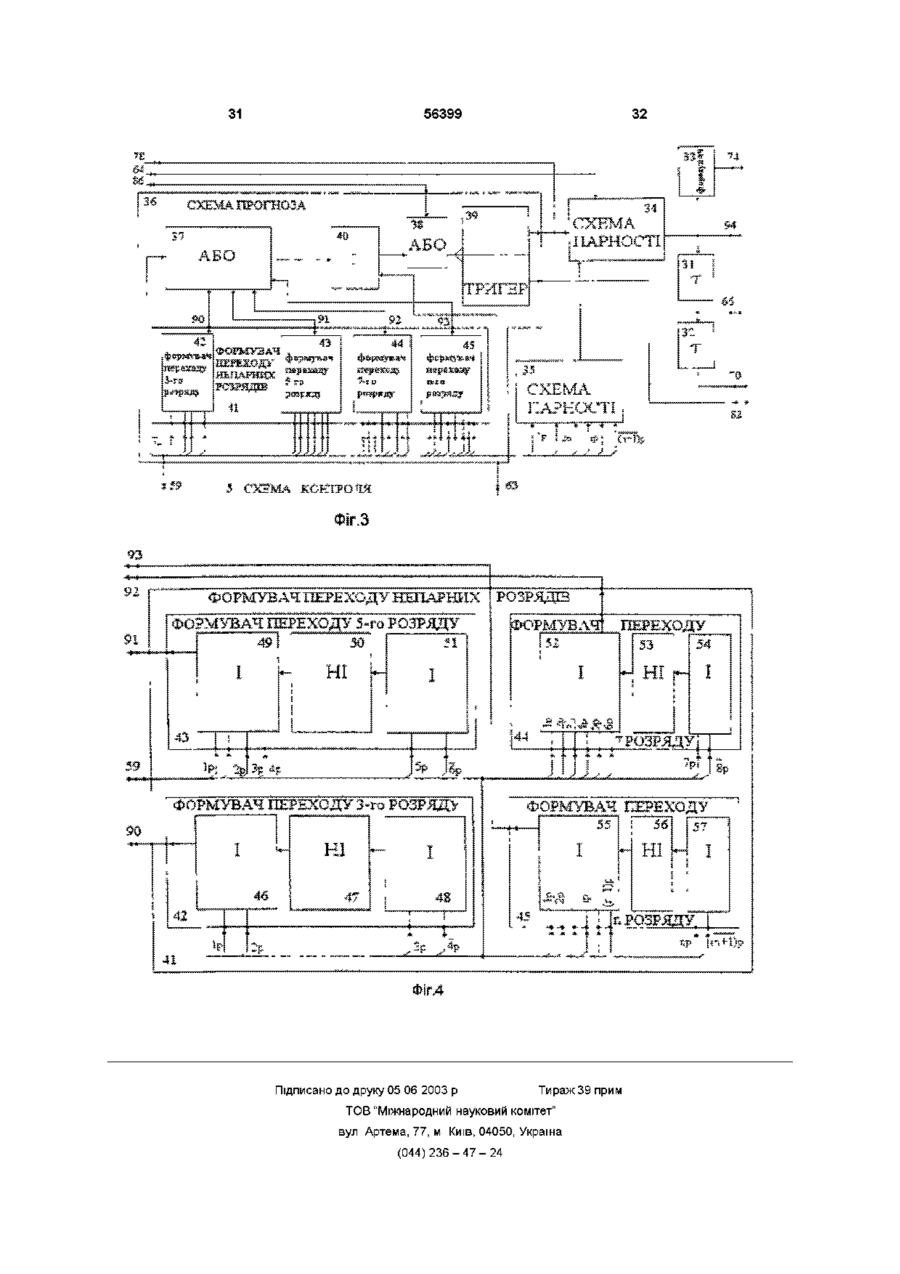

Система керування, що складається з багаторозрядного цифрового лічильного каналу, дешифратора, схеми керування, яка включає формувач і два елементи затримки, і генератора, вихід якого з'єднано з першими входами першого багаторозрядного цифрового лічильного каналу, схеми керування і дешифратора, вихід якого з'єднано з виходом системи керування, вхід схеми керування через перший елемент затримки, перший формувач і другий елемент затримки з'єднано з першим виходом схеми керування, другий вихід якої з'єднано з входом другого елемента затримки та виходом першого формувача, яка відрізняється тим, що запроваджено три [в загальному випадку (т-1) багаторозрядні цифрові ЛІЧИЛЬНІ канали, де m = 4,5,6, ] багаторозрядні цифрові ЛІЧИЛЬНІ канали, ВІСІМ (2т) груп схем І, чотири ( т ) схеми контролю, групу схем АБО, схему 1І I, схему парності -— і п'ять схем І, вихід першого багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами першої групи схем І і першої схеми контроля, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів першого багаторозрядного цифрового лічильного каналу, першим входом другої групи схем І, другим входом першої групи схем І, вихід якої з'єднано з першим входом групи схем АБО, вихід якої з'єднано з другими входами другої, четвертої, шостої і восьмої (2т) груп схем І і другим входом дешифратора, вихід другого багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами третьої групи схем І і другої схеми контролю, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів другого багаторозрядного цифрового лічильного каналу, першим входом четвертої групи схем І, другим входом третьої групи схем І, вихід якої з'єднано з другим входом групи схем АБО, вихід третього багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами п'ятої групи схем І і третьої схеми контролю, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів третього багаторозрядного цифрового лічильного каналу, першим входом шостої групи схем І, другим входом п'ятої групи схем І, вихід якої з'єднано з третім входом групи схем АБО, вихід четвертого ( т ) багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами сьомої (2т-1) групи схем І і четвертої ( т ) схеми контролю, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів четвертого ( т ) багаторозрядного цифрового лічильного каналу, першим входом восьмої (2т) групи схем І, другим входом сьомої (2т-1) групи схем І, вихід якої з'єднано з четвертим ( т ) входом групи схем АБО, вихід другої групи схем І з'єднано з одиничними входами розрядів першого багаторозрядного цифрового лічильного каналу, вихід четвертої групи схем І з'єднано з одиничними входами розрядів другого багаторозрядного цифрового лічильного каналу, вихід шостої групи схем І з'єднано з одиничними входами розрядів третього багаторозрядного цифрового лічильного каналу, вихід восьмої (2т) групи схем І з'єднано з одиничними входами розрядів четвертого ( т ) багаторозрядного цифрового лічильного каналу, другий вхід першої схеми контролю з'єднано з другими входами другої, третьої і четвертої (2т) схем контролю і першим виходом схеми керування, другий вихід якої з'єднано з третім входом першої схеми контролю, третім входом другої схеми контролю, третім входом третьої схеми контролю і третім входом четвертої ( т ) схеми контролю, четвертий вихід першої схеми контролю з'єднано з першим входом схеми 1І I, другий, третій і -— четвертий входи якої з'єднані ВІДПОВІДНО З четвертим виходом другої схеми контролю, з четвертим виходом третьої схеми контролю і з четвертим виходом четвертої ( т ) схеми контролю, п'ятий вихід першої схеми контролю з'єднано з першим входом першої схеми І, другий, третій і четвертий входи якої з'єднані ВІДПОВІДНО З П'ЯТИМ ВИХОДОМ другої схеми контролю, з п'ятим виходом третьої схеми контролю і з п'ятим виходом четвертої ( т ) схеми контролю, входи першої схеми парності ВІДПОВІДНО з'єднані з виходом схеми І-НІ і з виходом першої схеми І, вихід першої схеми парності о> со (О ю 56399 розрядів, входи якого з єднані з першим входом з єднано з першими входами другої, третьої, четсхеми прогнозу, другий вхід якої з'єднано з третім вертої і п'ятої схем І, другий вихід першої схеми входом схеми контролю, першим входом шостої контролю з'єднано з другим входом другої схеми І, схеми І, вихід першої схеми АБО через другий вхід вихід якої з'єднано з четвертим входом першої шостої схеми І, другу схему АБО і лічильний трисхеми контролю, другий вихід другої схеми контгер з'єднано з першим виходом схеми прогнозу і ролю з'єднано з другим входом третьої схеми І, першим входом другої схеми парності, другий вхід вихід якої з'єднано з четвертим входом другої якої з'єднано з виходом третьої схеми парності, схеми контролю, другий вихід третьої схеми контвходи якої з'єднані з першим входом схеми контролю з'єднано з другим входом четвертої схеми І, ролю, другий вхід якої з'єднано з третім входом вихід якої з'єднано з четвертим входом третьої другої схеми парності, вихід якої через третій і схеми контролю, другий вихід четвертої (т) схеми четвертий елементи затримки з'єднано з другим контролю з'єднано з другим входом п'ятої схеми І, виходом схеми контролю, перший вихід якої з'єдвихід якої з'єднано з четвертим входом четвертої нано з входом четвертого елемента затримки і (т) схеми контролю, кожна схема контролю склавиходом третього елемента затримки, третій вихід дається з двох схем парності, двох елементів засхеми контролю з'єднано через другий формувач з тримки, другого формувача і схеми прогнозу, яка виходом другої схеми парності, перший вхід другої включає лічильний тригер, схему І, дві схеми АБО і схеми парності з'єднано з четвертим виходом схеформувач переходу непарних розрядів, який склами контролю, п'ятий вихід якої з'єднано з другим дається з формувачів переходу непарних розрявиходом лічильного тригера і другим виходом дів, перший вхід схеми прогнозу з'єднано з персхеми прогнозу, третій вхід якої з'єднано з другим шим входом схеми контролю, першим входом входом другої схеми АБО і третім входом схеми першої схеми АБО, ІНШІ ВХОДИ якої з'єднані ВІДПОконтролю ВІДНО з виходами формувача переходу непарних Винахід відноситься до області обчислювальної техніки і може бути використано в інших областях техніки, де знаходять застосування цифрові системи обробки інформації, до складу яких входять цифрові елементи пам'яті ВІДОМІ системи управління, які виробляють задану часову ПОСЛІДОВНІСТЬ керуючих сигналів [1] Система управління, яка наведена у [1], складається з генератора, декількох ідентичних багаторозрядних цифрових лічильних каналів, схем зрівнення, груп схем І, групи схем АБО і дешифратора При надходженні сигналів генератора змінюються поточні стани цифрових лічильних каналів Часова ПОСЛІДОВНІСТЬ керуючих сигналів виробляється дешифратором, котрий дешифрує вихідний код групи схем АБО, на входи якої через групи схем І надходять ВИХІДНІ КОДИ цифрових лічильних каналів Надійність роботи системи управління залежить від КІЛЬКОСТІ цифрових лічильних каналів, Працездатність цифрових лічильних каналів визначається за певною логікою 2 із З, 3 із 5, 4 із 7 Схеми зрівнення визначають більшість однакових каналів (працездатних) Потім проводиться відмикання непрацездатних каналів, при цьому на ВІДПОВІДНІ групи схем І, на які надходять коди цифрових лічильних каналів, надходять забороняючи сигнали зі схем зрівнення Таким чином, на групу схем АБО будуть надходити коди тільки працездатних каналів Недоліком даної системи управління є зростання КІЛЬКОСТІ апаратури, яка обумовлена наявністю декількох ідентичних цифрових лічильних каналів, і невисока надійність, яка обумовлена наявністю постійних і часових похибок цифрових елементів пам'яті Вимоги до надійності цифрових елементів пам'яті, які входять до системи управління, практично не реалізуються Тому, незважаючи на розробку нових елементів пам'яті з більш високою надійністю, актуальною залишається задача побу дови надійних систем управління, які використовують ненадійні цифрові елементи пам'яті Під надійною роботою системи управління розуміється точне виконання заданого алгоритму функціонування, який передбачає формування заданої часової ПОСЛІДОВНОСТІ керуючих сигналів Остання виробляється за допомогою багаторозрядних цифрових лічильних каналів, які підраховують ВХІДНІ сигнали генератора Код цифрового лічильного каналу, який визначає його значення (стан), однозначно відповідає ПОСЛІДОВНОСТІ керуючих сигналів системи управління Система управління виходить із ладу при помилковій роботі елементів пам'яті, які входять до її складу Похибка спрацьовування елемента пам'яті може бути постійною або часовою Вона визначається в формуванні на виході елемента пам'яті нульового сигналу "0" замість одиничного сигналу " 1 " , або одиничного сигналу " 1 " замість нульового сигналу "0" Часова похибка (збій) - це самозникаюча помилка елемента пам'яті Елемент пам'яті, в якому виник збій, у наступний момент часу нормально функціонує Постійна похибка (вихід із ладу) - це незникаюча помилка елемента пам'яті Починаючи з моменту часу, коли елемент пам'яті вийшов з ладу, він не змінює свого стану При наявності часових похибок стан системи управління на даний момент часу не відповідає заданому алгоритму функціонування не формується задана часова ПОСЛІДОВНІСТЬ керуючих сигналів Поява часової похибки в цифровому лічильному каналі призводить до пропадання частини часової ПОСЛІДОВНОСТІ керуючих сигналів, коли наступне значення цифрового лічильного каналу перевищує попереднє більше ніж на одну градацію Коли ж наступне значення цифрового лічильного каналу менше або дорівнює попередньому повторно формується часова ПОСЛІДОВНІСТЬ керуючих сигналів Головною причиною непрацездат ності системи управління є часові похибки елементів пам'яті, які входять до її складу ВІДПОВІДНО технічним умовам сучасні елементи пам'яті за час використання не виходять з ладу із-за наявності постійних похибок В умовах дії завад, часові похибки елементів пам'яті виникають у всіх каналах і тому система управління через певний час перестає працювати (не виконується заданий алгоритм функціонування) З відомих систем управління найбільш близькою по технічній суті є система управління, яка наведена в роботі [2] і яку вибрано за прототип Система управління складається з генератора, багаторозрядного цифрового лічильного каналу, дешифратора, схеми керування, яка включає формувач і два елемента затримки, і схеми перевірки, яка включає дві схеми парності і схему прогнозу, яка складається зі схеми АБО, схеми І, лічильного тригера та формувачів переходу непарних розрядів Генератор з'єднано з першими входами багаторозрядного цифрового лічильного каналу, схеми керування і дешифратора Вихід багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першим входом схеми перевірки, а через другий вхід дешифратора з виходом цифрового пристрою керування Вхід схеми керування через перший елемент затримки, формувач і другий елемент затримки з'єднано з першим виходом схеми керування і другим входом схеми перевірки, третій вхід якої з'єднано з другим виходом схеми керування, який з'єднано з входом другого елемента затримки та виходом формувача Перший вхід схеми перевірки з'єднано з першим входом схеми прогнозу, який з'єднано з першим входом схеми АБО та входами формувачів переходу непарних розрядів Виходи формувачів переходу непарних розрядів через ІНШІ входи схеми АБО з'єднані через схему І та лічильний тригер з виходом схеми прогнозу, який з'єднано з першим входом першої схеми парності Другий вхід схеми прогнозу з'єднано з третім входом схеми перевірки, який з'єднано з другим входом схеми І Другий вхід першої схеми парності з'єднано з виходом другої схеми парності, входи якої з'єднані з першим входом схеми прогнозу Другий вхід схеми перевірки з'єднано з третім входом першої схеми парності, вихід якої з'єднано з виходом схеми перевірки Робота пристрою прототипа виконується таким чином При надходженні сигналів генератора змінюється поточний стан цифрового лічильного каналу Часова ПОСЛІДОВНІСТЬ керуючих сигналів пристрою керування виробляється дешифратором, котрий дешифрує вихідний код цифрового лічильного каналу У кожен момент часу з тактовою частотою f надходження сигналів генератора схема перевірки визначає працездатність цифрового лічильного каналу При виході його з ладу спрацьовує схема перевірки і виробляє сигнал непрацездатності Визначення працездатності цифрового лічильного каналу, який складається з лічильних елементів пам'яті, засновано на сильній кореляційній залежності наступного стану цифрового лічильно 56399 го каналу від попереднього Наявність часових і постійних похибок лічильних елементів пам'яті визначається шляхом екстрополяцм (прогнозування) поточного стану цифрового лічильного каналу на один крок уперед Це дає можливість визначити працездатність цифрового лічильного каналу при невідповідності поточного стану цифрового лічильного каналу його прогнозованому стану Поточне значення цифрового лічильного каналу формується шляхом підрахунку " 1 " (одиничних станів) усіх розрядів цифрового лічильного каналу по відповідному модулю, наприклад, по модулю 2 Визначення прогнозованого стану цифрового лічильного каналу засновано на такій його особливості При переході в " 1 " одиничний стан непарних розрядів сумма " 1 " одиниць його розрядів по модулю 2 змінює свій стан і не змінює свій стан, коли в " 1 " одиничний стан переходять парні розряди При надходженні входного сигналу в одиничний " 1 " стан переходить тільки один із розрядів, який знаходиться в нульовому стані "0", а попередні розряди, які знаходяться в одиничних " 1 " станах, переходять у нульові "0" стани У таблиці наведено значення поточного стану 10-розрядного цифрового лічильного каналу по mod2 Таб. идя Недоліком цієї системи управління є невисока надійність, яка обумовлена часовими похибками елементів пам'яті, які входять до її складу Часові похибки елементів пам'яті виникають як у цифровому лічильному каналі, так і в лічильному тригері 56399 8 тьої групи схем І, вихід якої з єднано з другим входом групи схем АБО, вихід третього багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами п'ятої групи схем І і третьої схеми контролю, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів третього багаторозрядного цифрового лічильного каналу, першим входом шостої групи схем І, другим входом п'ятої групи схем І, вихід якої з'єднано з третім входом групи схеми АБО, вихід четвертого ( т ) багаторозрядного цифрового лічильного каналу (паралельний код) з'єднано з першими входами сьомої (2т-1) групи схем І і четвертої ( т ) схеми контролю, перший, другий і третій виходи якої ВІДПОВІДНО з'єднані з нульовими входами розрядів четвертого ( т ) багаторозрядного цифрового лічильного каналу, першим входом восьмої (2т) групи схем І, другим входом сьомої (2т-1) групи схем І, вихід якої з'єднано з четвертим ( т ) входом групи схем АБО, вихід другої групи схем І з'єднано з одиничними входами розрядів першого багаторозрядного цифрового лічильного каналу, вихід четвертої групи схем І з'єднано з одиничними входами розрядів другого багаторозЗадачею винаходу є створення системи рядного цифрового лічильного каналу, вихід шосуправління, яка забезпечує надійне формування тої групи схем І з'єднано з одиничними входами заданої часової ПОСЛІДОВНОСТІ керуючих сигналів в розрядів третього багаторозрядного цифрового умовах дії завад лічильного каналу, вихід восьмої (2т) групи схем І Для підвищення надійності формування задаз'єднано з одиничними входами розрядів четверної часової ПОСЛІДОВНОСТІ керуючих сигналів в того ( т ) багаторозрядного цифрового лічильного умовах дії завад у систему управління, яка склаканалу, другий вхід першої схеми контролю з'єддається з багаторозрядного цифрового лічильного нано з другими входами другої, третьої і четвертої каналу, дешифратора, схеми керування, яка вклю(2т) схем контролю і першим виходом схеми кечає формувач і два елемента затримки, і генерарування, другий вихід якої з'єднано з третім вхотора, вихід якого з'єднано з першими входами дом першої схеми контролю, третім входом другої першого багаторозрядного цифрового лічильного схеми контролю, третім входом третьої схеми конканалу, схеми керування і дешифратора, вихід тролю і третім входом четвертої ( т ) схеми контроякого з'єднано з виходом системи управління, вхід лю, четвертий вихід першої схеми контролю з'єдсхеми керування через перший елемент затримки, нано з першим входом схеми 1І I, другий, третій і -— перший формувач і другий елемент затримки з'єдчетвертий входи якої з'єднані ВІДПОВІДНО З четвернано з першим виходом схеми керування, другий тим виходом другої схеми контролю, з четвертим вихід якої з'єднано з входом другого елемента виходом третьої схеми контролю і з четвертим затримки та виходом першого формувача, додатвиходом четвертої ( т ) схеми контролю, п'ятий ково запроваджено три [в загальному випадку ( т вихід першої схеми контролю з'єднано з першим 1) багаторозрядні цифрові ЛІЧИЛЬНІ канали, де входом першої схеми І, другий, третій і четвертий т=4,5,6, ] багаторозрядні цифрові ЛІЧИЛЬНІ канавходи якої з'єднані ВІДПОВІДНО З П'ЯТИМ ВИХОДОМ ли, ВІСІМ (2т) груп схем І, чотири ( т ) схеми контдругої схеми контролю, з п'ятим виходом третьої ролю, групу схем АБО, схему 1І I, схему парності і -— схеми контролю і з п'ятим виходом четвертої ( т ) п'ять схем І, вихід першого багаторозрядного цифсхеми контролю, входи першої схеми парності рового лічильного каналу (паралельний код) з'єдВІДПОВІДНО з'єднані з виходом схеми І-НІ і з вихонано з першими входами першої групи схем І і дом першої схеми І, вихід першої схеми парності першої схеми контролю, перший, другий і третій з'єднано з першими входами другої, третьої, четвиходи якої ВІДПОВІДНО з'єднані з нульовими вховертої і п'ятої схем І, другий вихід першої схеми дами розрядів першого багаторозрядного цифроконтролю з'єднано з другим входом другої схеми І, вого лічильного каналу, першим входом другої вихід якої з'єднано з четвертим входом першої групи схем І, другим входом першої групи схем І, схеми контролю, другий вихід другої схеми контвихід якої з'єднано з першим входом групи схем ролю з'єднано з другим входом третьої схеми І, АБО, вихід якої з'єднано з другими входами другої, вихід якої з'єднано з четвертим входом другої четвертої, шостої і восьмої (2т) груп схем І і друсхеми контролю, другий вихід третьої схеми контгим входом дешифратора, вихід другого багатороролю з'єднано з другим входом четвертої схеми І, зрядного цифрового лічильного каналу (паралельвихід якої з'єднано з четвертим входом третьої ний код) з'єднано з першими входами третьої схеми контролю, другий вихід четвертої ( т ) схеми групи схем І і другої схеми контролю, перший, друконтролю з'єднано з другим входом п'ятої схеми І, гий і третій виходи якої ВІДПОВІДНО з'єднані з нувихід якої з'єднано з четвертим входом четвертої льовими входами розрядів другого багаторозряд(т) схеми контролю, кожна схема контролю скланого цифрового лічильного каналу, першим дається з двох схем парності, двох елементів завходом четвертої групи схем І, другим входом тресхеми перевірки У першому випадку в умовах дії завад система управління після появи часової похибки в цифровому лічильному каналі перестає працювати, тому що не виконується заданий алгоритм функціонування не формується задана часова ПОСЛІДОВНІСТЬ керуючих сигналів Поява часової похибки в цифровому лічильному каналі призводить до пропадання частини часової ПОСЛІДОВНОСТІ керуючих сигналів, коли наступне значення цифрового лічильного каналу перевищує попереднє більше ніж на одну градацію Коли ж наступне значення цифрового лічильного каналу менше або дорівнює попередньому повторно формується часова ПОСЛІДОВНІСТЬ керуючих сигналів, у другому випадку формується задана часова ПОСЛІДОВНІСТЬ керуючих сигналів, а схема перевірки виробляє сигнал непрацездатності Якщо часова похибка елементів пам'яті виникає спочатку у лічильному тригері схеми перевірки, а через деякий час у цифровому лічильному каналі, то не формується задана часова ПОСЛІДОВНІСТЬ керуючих сигналів, а схема перевірки виробляє сигнал працездатності тримки, другого формувача і схеми прогнозу, яка включає лічильний тригер, схему І, дві схеми АБО і формувач переходу непарних розрядів, який складається з формувачів переходу непарних розрядів, перший вхід схеми прогнозу з'єднано з першим входом схеми контролю, першим входом першої схеми АБО, ІНШІ ВХОДИ якої з'єднані ВІДПОВІДНО з виходами формувача переходу непарних розрядів, входи якого з'єднані з першим входом схеми прогнозу, другий вхід якої з'єднано з третім входом схеми контролю, першим входом шостої схеми І, вихід першої схеми АБО через другий вхід шостої схеми І, другу схему АБО і лічильний тригер з'єднано з першим виходом схеми прогнозу і першим входом другої схеми парності, другий вхід якої з'єднано з виходом третьої схеми парності, входи якої з'єднані з першим входом схеми контролю, другий вхід якої з'єднано з третім входом другої схеми парності, вихід якої через третій і четвертий елементи затримки з'єднано з другим виходом схеми контролю, перший вихід якої з'єднано з входом четвертого елемента затримки і виходом третього елемента затримки, третій вихід схеми контролю з'єднано через другий формувач з виходом другої схеми парності, перший вхід другої схеми парності з'єднано з четвертим виходом схеми контролю, п'ятий вихід якої з'єднано з другим виходом лічильного тригера і другим виходом схеми прогнозу, третій вхід якої з'єднано з другим входом другої схеми АБО і третім входом схеми контролю Підвищення надійності формування часової ПОСЛІДОВНОСТІ керуючих сигналів, що дає можливість працювати системі управління в умовах дії завад, обумовлено тим, що при виникненні часових похибок у одному із цифрових лічильних каналів, його стан відновлюється по стану системи управління, стан лічильного тригера однієї зі схем контролю, в якому виник збій, змінюється на протилежний ("0"^"1" або "1"^"0") Застосування названих ВІДМІТНИХ ознак зі зв'язками поміж ними в других аналогічних системах управління авторам невідомо, тому відповідає критерію "новизна" Забезпечення запропонованої системи управління новою сукупністю ознак для виконання поставленоїзадачі дозволяє стверджувати, що запропонована система управління відповідає умовам патентноздатності, так як вона є нова, має винахідницький рівень та промислове застосування Сутність винаходу пояснюється кресленнями, Де - на фіг 1 наведена блок-схема системи управління, - на фіг 2 наведені часові діаграми роботи системи управління, - на фіг 3 наведено блок-схема схеми контролю, - на фіг 4 наведена блок-схема формувача переходу непарних розрядів Система управління (фиг 1) складається з багаторозрядних цифрових лічильних каналів 1-4, схем контролю 5-8, груп схем І 9-16, групи схем АБО 17, дешифратора 18, генератора 19, схеми керування 20, яка включає формувач 21, елементи затримки 22, 23, схеми І-НІ 24, схеми І 25, схеми 56399 10 парності 26, схем І 27-30 Схема контролю 5 (фіг 3) складається з елементів затримки 31, 32, формувача 33, схем парності 34, 35 і схеми прогнозу 36, яка включає схеми АБО 37, 38 лічильний тригер 39, схему 140 та формувач переходу непарних розрядів 41 Формувач переходу непарних розрядів 41 (фіг 4) складається з формувача переходу 3-го розряду 42, який включає схему І 45, схему НІ 47 і схему І 48, формувача переходу 5-го розряду 43, який включає схему І 49, схему НІ 50 і схему 151, формувача переходу 7-го розряду 44, який включає схему І 52, схему НІ 53 і схему І 54, і формувача переходу п-го непарного розряду 45, який включає схему І 55, схему НІ 56 і схему І 57 У системі управління вихід 58 генератора 19 з'єднано з першими входами цифрових лічильних каналів 1 - 4, схеми керування 20 та дешифратора 18 Вихід 59 цифрового лічильного каналу 1 (паралельний код) з'єднано з першими входами групи схем І 10 та схеми контролю 5 Вихід 60 цифрового лічильного каналу 2 (паралельний код) з'єднано з першими входами схеми контролю 6 та групи схем І 12 Вихід 61 цифрового лічильного каналу З (паралельний код) з'єднано з першими входами схеми контролю 7 та групи схем І 14 Вихід 62 цифрового лічильного каналу 4 (паралельний код) з'єднано з першими входами схеми контролю 8 та групи схем 116 Вихід групи схем І 10 з'єднано з першим входом групи схем АБО 17, другий, третій і четвертий входи якої ВІДПОВІДНО з'єднані з виходом групи схем І 12, виходом групи схем І 14 та виходом групи схем І 16 Перші входи груп схем 19, 11, 13, 15 з'єднані з виходом групи схем АБО 17 Перший вихід 63 схеми керування 20 з'єднано з другими входами схем контролю 5-8 та виходом елемента затримки 23 Другий вихід 64 схеми керування 20 з'єднано з третіми входами схем контролю 5-8, входом елемента затримки 23 та виходом формувача 21, вхід якого через елемент затримки 22 з'єднано з входом 58 схеми керування 20 Вихід групи схем АБО 17 (паралельний код) через дешифратор 18 з'єднано з виходом 65 Перший вихід 66 схеми контролю 5 з'єднано с нульовими входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 1 Перший вихід 67 схеми контролю 6 з'єднано з нульовими входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 2 Перший вихід 68 схеми контролю 7 з'єднано с нульовими входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 3 Перший вихід 69 схеми контролю 8 з'єднано с нульовими входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 4 Другий вихід 70 схеми контролю 5 з'єднано з другим входом групи схем І 9, вихід якої (паралельний код) з'єднано з одиничними входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 1 Другий вихід 71 схеми контролю 6 з'єднано з другим входом групи схем І 11, вихід якої (паралельний код) з'єднано з одиничними входами лічильних елементів пам'яті (розрядів) цифрового лічильного каналу 2 Другий вихід 72 схеми контролю 7 з'єднано з другим входом 12 11 56399 групи схем І 13, вихід якої (паралельний код) з'єдпрогнозу 36 та першим входом 59 схеми контролю нано з одиничними входами лічильних елементів 5 пам'яті (розрядів) цифрового лічильного каналу З Входи формувача переходу n-го непарного Другий вихід 73 схеми контролю 8 з'єднано з друрозряду 45 (фіг 4) з'єднані ВІДПОВІДНО З ОДИНИЧНИгим входом групи схем І 15, вихід якої (паралельМИ виходами першого, другого, ,і-го (п-1), п розний код) з'єднано з одиничними входами лічильних рядів (1р 2р ір (п-1)р пр) та інверсним виходом елементів пам'яті (розрядів) цифрового лічильного (п+1)-го розряду (п + 1)р цифрового лічильного каналу 4 Третій вихід 74 схеми контролю 5 з'єднаканалу 1, першим входом схеми прогнозу 36 та но з другим входом групи схем І 10 Третій вихід 75 першим входом 59 схеми контролю 5 схеми контролю 6 з'єднано з другим входом групи Вихід схеми АБО 37 з'єднано с першим вхосхем І 12 Третій вихід 76 схеми контролю 7 з'єддом схеми І 40, вихід якої через перший вхід схеми нано з другим входом групи схем 114 Третій вихід АБО 38 і лічильний тригер 39 з'єднано з першим 77 схеми контролю 8 з'єднано з другим входом виходом схеми прогнозу 36 та першим входом групи схем І 16 Четвертий вихід 78 схеми контросхеми парності 34, другий вхід якої з'єднано з вилю 5 з'єднано з першим входом схеми І-НІ 24, друходом схеми парності 35 Входи схеми парності 35 гий 79, третій 80 і четвертий 81 входи якої ВІДПОВІз'єднані з виходами всіх розрядів цифрового лічиДНО з'єднані з четвертими виходами схем льного каналу 1, першим входом схеми прогнозу контролю 6, 7, 8 П'ятий вихід 82 схеми контролю 5 36 та першим входом 59 схеми контролю 5 Третій з'єднано з першим входом схеми І-НІ 25, другий вхід 64 схеми контролю 5 з'єднано з третім входом 83, третій 84 і четвертий 85 входи якої ВІДПОВІДНО схеми парності 34, вихід 94 якої з'єднано з входаз'єднані з п'ятими виходами схем контролю 5, 6, 7, ми елемента затримки 31 і формувача 33 Вихід 8 Вихід схеми І-НІ 24 з'єднано з першим входом елемента затримки 31 з'єднано з першим виходом схеми парності 26, другий вхід якої з'єднано з ви66 схеми контролю 5 та входом елемента затримходом схеми І 25 Вихід схеми парності 26, з'єднаки ЗО, вихід якого з'єднано з другим виходом 70 но з першими входами схеми І 27-30, виходи яких схеми контролю 5 Вихід формувача 33 з'єднано з ВІДПОВІДНО з'єднані з четвертими 86, 87, 88, 89 третім виходом 74 схеми контролю 5 Другий вхід входами схем контролю 5, 6, 7, 8 Другий вхід схе63 схеми контролю 5 з'єднано з другим входом ми І 27 з'єднано з другим виходом 70 схеми контсхеми прогнозу 36 і другим входом схеми І 40 ролю 5, другий вхід схеми І 28 з'єднано з другим Другий вхід схеми АБО 37 з'єднано з другим вховиходом 71 схеми контролю 6, другий вхід схеми І дом схеми прогнозу 36 і четвертим входом 86 схе29 з'єднано з другим виходом 72 схеми контролю ми контролю 5 Четвертий вихід 78 схеми контро7, другий вхід схеми І ЗО з'єднано з другим вихолю 5 з'єднано з одиничним виходом лічильного дом 73 схеми контролю 8 тригера 39 і першим виходом схеми прогнозу 36, другий вихід 82 якої з'єднано з інверсним виходом Інверсний (нульовий) вихід 1 розряду цифролічильного тригера 39, другим виходом схеми прового лічильного каналу 1 з'єднано з першим вхогнозу 36, п'ятим виходом 82 схеми контролю 5 дом схеми прогнозу 36 і першим входом 59 схеми контролю 5, який з'єднано з першим входом схеми Вихід 90 формувача 41 (фіг 4) з'єднано з друАБО 37 Другий, третій, четвертий та п'ятий входи гим входом схеми АБО 37, виходом формувача 42 схеми АБО 37 з'єднані ВІДПОВІДНО З першим 90, і з виходом схеми І 46, входи якої з'єднані ВІДПОВІдругим 91, третім 92 та четвертим 93 виходами ДНО з одиничними виходами першого та другого формувача переходу непарних розрядів 41 Входи розрядів (1р 2р) цифрового лічильного каналу 1 і формувача переходу непарних розрядів 41 з'єдначерез схему НІ 47 з виходом схеми 1 48 Входи ні з першим входом схеми прогнозу 36 та першим схеми І 48 з'єднані ВІДПОВІДНО З ОДИНИЧНИМ ВИХОвходом 59 схеми контролю 5 ДОМ третього розряду Зр та інверсним виходом четвертого розряду 4р цифрового лічильного каВходи формувача переходу 3-го розряду 42 налу 1 (фіг 4) з'єднані ВІДПОВІДНО з входами формувача переходу непарних розрядів 41, одиничними вихоВихід 91 формувача 41 (фіг 4) з'єднано з тредами першого, другого і третього розрядів (1р 2р тім входом схеми АБО 37, виходом формувача 43 і Зр) та інверсним виходом четвертого 4р розряду з виходом схеми І 49, входи якої з'єднані ВІДПОВІДцифрового лічильного каналу 1, першим входом НО з одиничними виходами першого, другого, тресхеми прогнозу 36 та першим входом 59 схеми тього і четвертого розрядів (1р 2р Зр 4р) цифровоконтролю 5 Входи формувача переходу 5-го розго лічильного каналу 1 і через схему НІ 50 з ряду 43 (фіг 4) з'єднані ВІДПОВІДНО З входами форвиходом схеми І 51 Входи схеми І 51 з'єднані ВІДмувача переходу непарних розрядів 41, з одиничПОВІДНО з одиничним виходом п'ятого розряду 5р ними виходами першого, другого, третього, та інверсним виходом шостого розряду 6 р цифрочетвертого, п'ятого розрядів (1р 2р Зр 4р 5р) та вого лічильного каналу 1 інверсним виходом шостого розряду 6р цифрового Вихід 92 формувача 41 (фіг 4) з'єднано з четлічильного каналу 1, першим входом схеми провертим входом схеми АБО 37, виходом формувагнозу 36 та першим входом 59 схеми контролю 5 ча 44 і виходом схеми І 52, входи якої з'єднані ВІДВходи формувача переходу 7-го розряду 44 (фіг 4) ПОВІДНО з одиничними виходами першого, другого, з'єднані ВІДПОВІДНО з входами формувача перехотретього, четвертого, п'ятого, шостого розрядів (1р ду непарних розрядів 41, одиничними виходами 2р Зр 4р 5р 6р) цифрового лічильного каналу 1 і першого, другого, третього, четвертого, п'ятого, через схему НІ 53 з виходом схеми І 54 Входи шостого, сьомого розрядів (1р 2р Зр 4р 5р 6р 7р) схеми І 54 з'єднані ВІДПОВІДНО З ОДИНИЧНИМ ВИХОта інверсним виходом восьмого розряду 8 р цифДОМ сьомого розряду 7р та інверсним виходом рового лічильного каналу 1, першим входом схеми восьмого розряду 8 р цифрового лічильного кана 13 56399 14 дній такт роботи цифрового лічильного каналу 1 значення його поточного стану в наступний такт Вихід 93 формувача 41 (фіг 4) з'єднано з п'яроботи (на один крок уперед) тим входом схеми АБО 37, виходом формувача 45 і виходом схеми І 55, входи якої з'єднані ВІДПОВІДБлок 37, 38 - схема АБО, є типовим елеменНО з одиничними виходами першого, друготом, наприклад, [3] Може бути використана мікрого, ,і, (п-1) розрядів (1р 2р, , ір, , (п-1)р) цифсхема ЛАЗ рового лічильного каналу 1 і через схему НІ 56 з Блок 39 - лічильний тригер, є типовим елеменвиходом схеми І 57 Входи схеми І 57 з'єднані ВІДтом, наприклад, [3] Може бути використана мікроПОВІДНО з одиничним виходом п-го розряду та інсхема ТВ1 версним виходом (п+1) розряду (п+1)р цифрового Блок 40 - схема І, є типовим елементом, налічильного каналу 1 приклад, [3] Може бути використана мікросхема ЛАЗ Блок 1-ь4 - цифровий лічильний канал, складається з лічильних лементів пам'яті (лічильних триБлок 41 - формувач переходу непарних розгерів), є типовим лічильником, наприклад, [3] Морядів Формувач переходу непарних розрядів виже бути використана мікросхема 564 ИЕ11 значає перехід у одиничний " 1 " стан непарних розрядів (Зр 5р 7р пр) цифрового лічильного Блок 5-ь8 - схема контролю, призначена для каналу 1 при формуванні прогнозованого значення контролю працездатності цифрового лічильного стану в попередній такт роботи Формувач переканалу 1 Схема контролю 5 (фіг 3) складається з ходу непарних розрядів 41 (фіг 4) складається з елементів затримки 31, 32, формувача 33, схем формувача переходу 3-го розряду 42, який вклюпарності 34, 35, схеми прогнозу 36, яка включає чає схему І 46, схему НІ 47 та схему І 48, формусхеми АБО 37, 38, лічильний тригер 39, схему 140 вача переходу 5-го розряду 43, який включає схета формувач переходу непарних розрядів 41 му І 49, схему НІ 50 та схему 151, формувача Блок 9-Й 6 - група схем І, складається з типопереходу 7-го розряду 44, який включає схему І 52, вих елементів І, наприклад, [3] Може бути викорисхему НІ 53 та схему І 54, формувача переходу пстана мікросхема ЛАЗ го непарного розряду 45, який включає схему І 55, Блок 17 - група схем АБО, складається з типосхему НІ 56 та схему І 57 вих елементів АБО, наприклад, [3] Може бути виБлок 46 - схема І, є типовим елементом, накористана мікросхема ЛАЗ приклад [3] Може бути використана мікросхема Блок 18 - дешифратор, є типовим елементом, ЛАЗ наприклад, [3] Блок 47 - схема НІ, є типовим елементом, наБлок 19 - генератор, є типовим генератором приклад, [3] Може бути використана мікросхема імпульсів, наприклад, [4] Може бути використана ЛАЗ мікросхема К2ГФ531 Блок 48, 49 - схема І, є типовим елементом, Блок 20 - схема керування, формує керуючі наприклад, [3] Може бути використана мікросхема сигнали, які синхронізують роботу всього приЛАЗ строю Схема керування 20 може складатися з Блок 50 - схема НІ, є типовим елементом, наформувача 21 та елементів затримки 22, 23 приклад, [3] Може бути використана мікросхема Блок 21 - формувач, є типовим елементом виЛАЗ мірювальних і радіоелектронних схем, наприклад, Блок 51, 52 - схема І, є типовим елементом, [4] наприклад, [3] Може бути використана мікросхема Блок 22, 23 - елемент затримки, є типовим ЛАЗ елементом вимірювальних і радіоелектронних Блок 53 - схема НІ, є типовим елементом, насхем, наприклад, [4] приклад, [3] Може бути використана мікросхема Блок 24 - схема 1І I, є типовим елементом, -— ЛАЗ наприклад, [3] Може бути використана мікросхема Блок 54, 55 - схема І, є типовим елементом, ЛАЗ наприклад, [3] Може бути використана мікросхема Блок 25 - схема І, є типовим елементом, наЛАЗ приклад, [3] Може бути використана мікросхема Блок 56 - схема НІ, є типовим елементом, наЛАЗ приклад, [3] Може бути використана мікросхема Блок 26 - схема парності, є типовим елеменЛАЗ том, наприклад, [3] Блок 57 - схема І, є типовим елементом, наБлок 27-ьЗО - схема І, є типовим елементом, приклад, [3] Може бути використана мікросхема наприклад, [3] Може бути використана мікросхема ЛАЗ ЛАЗ Робота системи управління проходить таким Блок 31, 32 - елемент затримки, є типовим чином При надходженні сигналів з генератора 19 елементом вимірювальних і радіоелектронних на вихід 58 змінюються поточні стани цифрових схем, наприклад, [4] лічильних каналів 1-4 Керуючі сигнали системи Блок 33 - формувач, є типовим елементом виуправління виробляються дешифратором 18, котмірювальних і радіоелектронних схем, наприклад, рий дешифрує вихідний код групи схем АБО 17, на [4] входи якої надходять ВИХІДНІ КОДИ цифрових лічиБлок 34, 35 - схема парності, є типовим елельних каналів 1 - 4, ВІДПОВІДНО через групи схем І ментом, наприклад, [3] 10, 12, 14, 16 Часова ПОСЛІДОВНІСТЬ керуючих сигБлок 36 - схема прогнозу Схема прогнозу налів системи управління надходить на вихід 64 (фіг 3) включає схеми АБО 37, 38, схему І 40, лічиУ кожен момент часу з тактовою частотою f льний тригер 39 та формувач переходу непарних надходження сигналів генератора 19 схеми контрозрядів 41 Схема прогнозу 36 формує в поперелу 1 16 15 56399 ролю 5-8 визначають працездатність цифрових входи надходять одиничні " 1 " сигнали ВІДПОВІДНО З лічильних каналів 1-4 При виході з ладу одного з ЛІЧИЛЬНОГО тригера 39 схеми прогнозу 36 і зі схеми цифрових лічильних каналів 1 - 4 спрацьовує відпарності 35 У момент часу U спрацьовує лічильповідна схема контролю 5-8 При цьому схеми коний тригер 39, оскільки на його вхід через схему І нтролю 5-8 виробляють додаткові сигнали, за до40 і схему АБО 37 надходить керуючий сигнал зі помогою яких установлювається в "0" (нульовий) схеми АБО 37, який формується інверсним вихостан цифровий лічильний канал, який вийшов з дом першого розряду І р цифрового лічильного ладу, а потім у цей канал записується код системи каналу 1 Таким чином, лічильний тригер 39 переуправління ходить у нульовий "0" стан Визначення працездатності цифрового лічиПри надходженні третього сигналу з генератольного каналу проводиться шляхом зрівнення його ра 19 цифровий лічильний канал 1 переходить у поточного значення з прогнозованим значенням, стан 1100000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) яке виробляється в попередній такт після надхоУ момент часу ti схема парності 34 перебуває в дження вхідного сигналу При невідповідності понульовому "0" стані, оскільки на її перший та друточного значення цифрового лічильного каналу гий входи надходять нульові "0" сигнали ВІДПОВІДйого прогнозованому значенню схема контролю 5НО з лічильного тригера 39 схеми прогнозу 36 і зі 8 виробляє сигнал непрацездатності схеми парності 35 У момент часу U спрацьовує лічильний тригер 39, оскільки на його вхід надхоПоточне значення цифрового лічильного кадить керуючий сигнал зі схеми АБО 37, який форналу формується шляхом підрахунку " 1 " (одиничмується формувачем переходу 3-го розряду 42 У них) станів усіх розрядів цифрового лічильного цей час на входи 59 схеми І 46 (фіг 4) надходять каналу по відповідному модулю, наприклад, по керуючі сигнали з одиничних виходів першого та модулю 2 Визначення прогнозованого стану цифдругого розрядів 1р, 2р цифрового лічильного карового лічильного каналу засновано на такій його налу 1 Таким чином, лічильний тригер 39 змінює особливості При переході в " 1 " одиничний стан свій стан, він переходить у одиничний " 1 " стан непарних розрядів сума " 1 " одиниць його розрядів по модулю 2 змінює свій стан і не змінює свій стан, При надходженні четвертого сигналу з генераколи в " 1 " одиничний стан переходять парні розтора 19 цифровий лічильний канал 1 переходить у ряди При надходженні вхідного сигналу в одиничстан 0010000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) ний " 1 " стан переходить тільки один із розрядів, У момент часу ti схема парності 34 перебуває в який знаходиться в нульовому стані "0", а поперенульовому "0" стані, оскільки на її перший та друдні розряди, які знаходяться в одиничних " 1 " стагий входи надходять одиничні " 1 " сигнали ВІДПОВІнах, переходять у нульові"" стани ДНО з лічильного тригера 39 схеми прогнозу 36 і зі схеми парності 35 У момент часу U спрацьовує Схема керування 20 виробляє сигнали необлічильний тригер 39, змінює свій стан, оскільки на хідні для роботи схем контролю 5-8 його вхід надходить керуючий сигнал зі схеми АБО Розглянемо роботу схеми контролю 5 (фігЗ), 37, який формується інверсним виходом першого яка аналізує роботу десятирозрядного цифрового розряду 1р цифрового лічильного каналу 1 Лічилічильного каналу 1, починаючи з початкового мольний тригер 39 переходить у нульовий "0" стан менту часу, коли цифровий лічильний канал 1 перебуває в нульовому "0" стані, а лічильний тригер При надходженні п'ятого сигналу з генератора 39 схеми прогнозу 36 перебуває в одиничному " 1 " 19 цифровий лічильний канал 1 переходить у стан стані 1010000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) У момент часу U схема парності 34 перебуває в нуПри надходженні першого сигналу з генератольовому "0" стані, оскільки на и перший та другий ра 19 десятирозрядний цифровий лічильний канал входи надходять нульові "0" сигнали ВІДПОВІДНО З 1 переходить у стан 1000000000 (1 р 2р Зр 4р 5р 6р ЛІЧИЛЬНОГО тригера 39 схеми прогнозу 36 і зі схеми 7р 8 р 9р 10р) При цьому в момент часу ti після парності 35 У момент часу U стан лічильного тризакінчення перехідного процесу в цифровому лігера 39 не змінюється, оскільки на його вхід не чильному каналі 1 схема парності 34 перебуває в надходить керуючий сигнал зі схеми АБО 37 і він нульовому "0" стані, оскільки в цей час на її перзалишається в нульовому "0" стані ший і другий входи надходять одиничні " 1 " сигнали ВІДПОВІДНО з лічильного тригера 39 схеми прогнозу При надходженні шостого сигналу з генерато36 і зі схеми парності 35 У момент часу U стан ра 19 цифровий лічильний канал 1 переходить у лічильного тригера 39 не змінюється, оскільки на стан 0110000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) його лічильний вхід не надходить керуючий сигнал У момент часу ti схема парності 34 перебуває в зі схеми АБО 37 Лічильний тригер 39 залишається нульовому "0" стані, оскільки на її перший та друв одиничному " 1 " стані, де гий входи надходять нульові "0" сигнали ВІДПОВІДНО з лічильного тригера 39 схеми прогнозу 36 та зі ti - затримка керуючого сигналу вихід 64 схеми схеми парності 35 У момент часу U лічильний трикерування 20 відносно початку вхідного сигналу гер 39 змінює свій стан, оскільки на його вхід над(фіг 2-0,2-58), ходить керуючий сигнал зі схеми АБО 37, який U - затримка керуючого сигналу вихід 63 схеми формується інверсним виходом першого розряду керування 20 відносно початку вхідного сигналу 1 р цифрового лічильного каналу 1 Лічильний три(фіг 2-0,2-58) гер 39 переходить у одиничний " 1 " стан При надходженні другого сигналу з генератора 19 цифровий лічильний канал 1 переходить у стан При надходженні сьомого сигналу з генерато0100000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) У ра 19 цифровий лічильний канал 1 переходить у момент часу ti схема парності 34 перебуває в нустан 1110000000 (1 р 2р Зр 4р 5 р 6р 7р 8р 9р 10р) льовому "0" стані, оскільки на и перший та другий У момент часу ti схема парності 34 перебуває в 18 17 56399 нульовому "0" стані, оскільки на її перший та друякий виробляється формувачем переходу 3-го гий входи надходять одиничні " 1 " сигналі ВІДПОВІДрозряду 42 (фіг 4) У цей час на входи 59 схеми І НО з лічильного тригера 39 схеми прогнозу 36 та зі 46 надходять керуючі сигнали з одиничних виходів схеми парності 35 У момент часу U лічильний трипершого та другого розрядів 1 р 2р цифрового лігер 39 не спрацьовує (фіг 4), оскільки на його вхід чильного каналу 1 Лічильний тригер 39 перехоне надходить керуючий сигнал зі схеми АБО 37, дить у нульовий "0"стан який виробляється формувачем переходу 3-го При надходженні тридцять першого сигналу з розряду 42 У цей час спрацьовує схема 148, на генератора 19 цифровий лічильний канал 1 перевходи 59 якої надходять керуючі сигнали з одиниходить у стан 1111100000 (1 р 2р Зр 4р 5р 6р 7р 8 р чного виходу третього розряду Зр та інверсного 9р Юр) У момент часу ti схема парності 34 перевиходу четвертого розряду 4р цифрового лічильбуває в нульовому "0" стані, оскільки на її перший ного каналу 1 Вихідний сигнал схеми І 48 після та другий входи надходять одиничні " 1 " сигналі схеми НІ 47 надходить на третій вхід схеми І 46 і ВІДПОВІДНО з лічильного тригера 39 схеми прогнозу забороняє останній сформувати керуючий сигнал, 36 та зі схеми парності 35 У момент часу U лічиколи на її перший та другий входи надходять кельний тригер 39 не спрацьовує, оскільки на його руючі сигнали з одиничних виходів першого та вхід не надходить керуючий сигнал зі схеми АБО другого розрядів 1 р 2р цифрового лічильного ка37, який виробляється формувачем переходу 5-го налу 1 Таким чином, лічильний тригер 39 залишарозряду 43 У цей час спрацьовує схема І 51 ється в одиничному " 1 " стані (фіг 4), на входи 59 якої надходять керуючі сигнали з одиничного виходу п'ятого розряду 5рта інвеПри надходженні восьмого сигналу з генерарсного виходу шостого розряду 6р цифрового літора 19 цифровий лічильний канал 1 переходить у чильного каналу 1 Вихідний сигнал схеми І 51 стан 0001000000 (1р 2р Зр 4р 5р 6р 7р 8р 9р Юр) після схеми НІ 50 надходить на п'ятий вхід схеми І У момент часу ti схема парності 34 перебуває в 49 і забороняє останній сформувати керуючий нульовому "0" стані, оскільки на її перший та друсигнал, коли на її перший, другий, третій, четвергий входи надходять одиничні " 1 " сигнали ВІДПОВІтий входи надходять керуючі сигнали з одиничних ДНО з лічильного тригера 39 схеми прогнозу 36 та виходів першого, другого, третього, четвертого зі схеми парності 35 У момент часу U стан лічильрозрядів 1р 2р Зр 4р цифрового лічильного каналу ного тригера 39 змінюється, оскільки на його вхід 1 Таким чином, лічильний тригер 39 залишається через схему АБО 37 надходить керуючий сигнал, в одиничному " 1 " стані який формується інверсним виходом першого розряду 1 р цифрового лічильного каналу 1 Лічильний При надходженні сто двадцять сьомого сигнатригер 39 переходить у нульовий "0" стан лу з генератора 19 цифровий лічильний канал 1 переходить у стан 1111111000 (1 р 2р Зр 4р 5р 6р При надходженні дев'ятого сигналу з генера7р 8р 9р Юр) У момент часу ti схема парності 34 тора 19 цифровий лічильний канал 1 переходить у перебуває в нульовому "0" стані, оскільки на її пестан 1001000000 (1 р 2р Зр 4р 5р 6р 7р 8р 9 р 10р) рший та другий входи надходять одиничні " 1 " сигУ момент часу ti схема парності 34 перебуває в налі ВІДПОВІДНО з лічильного тригера 39 схеми пронульовому "0" стані, оскільки на її перший та другнозу 36 та зі схеми парності 35 У момент часу U гий входи надходять нульові "0" сигнали ВІДПОВІДлічильний тригер 39 не спрацьовує, оскільки на НО з лічильного тригера 39 схеми прогнозу 36 та зі його вхід не надходить керуючий сигнал зі схеми схеми парності 35 У момент часу U стан лічильноАБО 37, який виробляється формувачем переходу го тригера 39 не змінюється, оскільки на його лічи7-го розряду 44 У цей час спрацьовує схема І 54, льний вхід не надходить керуючий сигнал зі схеми на входи 59 якої надходять керуючі сигнали з одиАБО 37 і він залишається в нульовому "0" стані ничного виходу сьомого розряду 7р та інверсного При надходженні десятого сигналу з генератовиходу восьмого розряду 8 р цифрового лічильнора 19 цифровий лічильний канал 1 переходить у го каналу 1 Вихідний сигнал схеми І 54 після схестан 0101000000 (2р 2р Зр 4р 5р 6р 7р 8р 9р Юр) ми НІ 53 надходить на сьомий вхід схеми І 52 і У момент часу ti схема парності 34 перебуває в забороняє останній сформувати керуючий сигнал, нульовому "0" стані, оскільки на її перший та друколи на и перший, другий, третій, четвертий, п'ягий входи надходять нульові "0" сигнали ВІДПОВІДтий, шостий входи надходять керуючі сигнали з НО з лічильного тригера 39 схеми прогнозу 36 та зі одиничних виходів першого, другого, третього, схеми парності 35 У момент часу U стан лічильночетвертого, п'ятого, та шостого розрядів 1р 2р Зр го тригера 39 змінюється, оскільки на його вхід зі 4р 5р 6р цифрового лічильного каналу 1 Таким схеми АБО 37 надходить керуючий сигнал, який чином, лічильний тригер 39 залишається в одиниформується інверсним виходом першого розряду чному " 1 " стані 1 р цифрового лічильного каналу 1 Лічильний тригер 39 переходить у одиничний " 1 " стан При надходженні п'ятисот одинадцятого сигналу з генератора 19 цифровий лічильний канал 1 При надходженні одинадцятого сигналу з гепереходить у стан 1111111110 (1 р 2р Зр 4р 5р 6р нератора 19 цифровий лічильний канал 1 перехо7р 8р 9р Юр) У момент часу ti схема парності 34 дить у стан 1101000000 (1р 2р Зр 4р 5р 6р 7р 8 р перебуває в нульовому "0" стані, оскільки на її пе9р Юр) У момент часу ti схема парності 34 перерший та другий входи надходять одиничні " 1 " сигбуває в нульовому "0" стані, оскільки на її перший налі ВІДПОВІДНО з лічильного тригера 39 схеми прота другий входи надходять одиничні " 1 " сигнали гнозу 36 та зі схеми парності 35 У момент часу U ВІДПОВІДНО з лічильного тригера 39 схеми прогнозу лічильний тригер 39 не спрацьовує, оскільки на 36 та зі схеми парності 35 У момент часу U стан його вхід не надходить керуючий сигнал зі схеми лічильного тригера 39 змінюється, оскільки на його АБО 37, який виробляється формувачем переходу вхід надходить керуючий сигнал зі схеми АБО 37, 19 56399 п-го непарного розряду 45 У цей час спрацьовує схема I 57, на входи 59 якої надходять керуючі сигнали з одиничного виходу дев'ятого розряду 9р та інверсного виходу десятого розряду 10р цифрового лічильного каналу 1 Вихідний сигнал схеми І 57 після схеми НІ 56 надходить на дев'ятий вхід схеми І 55 і забороняє останній сформувати керуючий сигнал, коли на її перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий входи надходять керуючі сигнали з одиничних виходів першого, другого, третього, четвертого, п'ятого, шостого, сьомого та восьмого розрядів 1 р 2р Зр 4р 5р 6р 7р 8р цифрового лічильного каналу 1 Таким чином, лічильний тригер 39 залишається в одиничному " 1 " стані Таким чином, схема контролю 5 перевіряє працездатність цифрового лічильного каналу 1 після надходження кожного сигналу з генератора 19 При наявності часової похибки в цифровому лічильному каналі 1 схема парності 34 схеми контролю 5 виробляє на виході 94 керуючий сигнал Останній за допомогою елементів затримки 31, 32 переформується в додаткові сигнали, які з'являються на виходах 66, 70 схеми контролю 5 Наприклад, часова похибка виникла в другому розряді цифрового лічильного каналу 1 після надходження п'ятого і одинадцятого сигналів з генератора 19 У першому випадку цифровий лічильний канал 1 переходить у стан 1110000000 замість 1010000000 У момент часу ti спрацьовує схема парності 34, оскільки на и перший та другий входи надходять різні сигнали нульовий "0" сигнал з лічильного тригера 39 схеми прогнозу 36 і одиничний " 1 " сигнал зі схеми парності 35 У другому випадку цифровий лічильний канал 1 переходить у стан 1111000000 замість 1011000000 У момент часу ti спрацьовує схема парності 34, оскільки на її перший та другий входи надходять різні сигнали ВІДПОВІДНО одиничний " 1 " сигнал з лічильного тригера 39 схеми прогнозу 36 та нульовий "0" зі схеми парності 35 Сигнал, який з'являється на виході 66, у момент часу І2 установлює в нульовий "0" стан цифровий лічильний канал 1 Сигнал, який з'являється на виході 70, у момент часу t3, дозволяє роботу групи схем І 9 При цьому вихідний код схеми АБО 17 (стан системи управління) переписується в лічильний канал 1, де Ь - затримка керуючого сигналу на виході 66 схеми контролю 5 відносно початку вхідного сигналу (фіг 2 - 0,2-58), t3 - затримка керуючого сигналу на виході 70 схеми контролю 5 відносно початку вхідного сигналу (фіг 2 - 0,2-58), ti

ДивитисяДодаткова інформація

Назва патенту англійськоюControl system

Автори англійськоюMaranov Oleksandr Viktorovych, Ostapov Anatolii Oleksandrovych, Chyhyryn Oleh Trokhymovych, Chygyryn Yurii Trokhymovych

Назва патенту російськоюСистема управления

Автори російськоюМаранов Александр Викторович, Остапов Анатолий Александрович, Чигирин Олег Трофимович, Чигирин Юрий Трофимович

МПК / Мітки

МПК: G06F 11/00

Код посилання

<a href="https://ua.patents.su/16-56399-sistema-keruvannya.html" target="_blank" rel="follow" title="База патентів України">Система керування</a>

Попередній патент: Спосіб ідентифікації кадрів нульової швидкості та приймальна підсистема для його здійснення (варіанти)

Наступний патент: Пристосування для держаків зубів мотовила жниварки

Випадковий патент: Атравматична внутрішньовенна голка