Пристрій для визначення еквівалентності бінарних матриць

Номер патенту: 33713

Опубліковано: 10.07.2008

Автори: Сіроклин Віталій Павлович, Дідик Наталія Олексіївна, Кошовий Микола Дмитрович, Павлик Ганна Володимирівна

Формула / Реферат

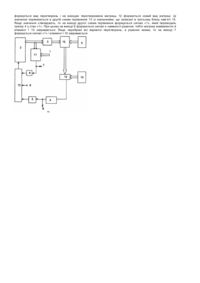

Пристрій для визначення еквівалентності бінарних матриць, що містить групу інформаційних входів, лічильник, перший блок пам'яті, тригер, перший і другий елементи НІ, вихід ознаки відсутності рішення, вихід ознаки наявності рішення, керуючий вхід, елемент І, першу схему порівняння, причому вихід тригера з'єднаний із виходом ознаки наявності рішення та через перший елемент HI з першим входом елемента І, керуючий вхід з'єднаний із другим входом елемента І, вихід елемента І з'єднаний з рахунковим входом лічильника, виходи якого з'єднані з адресними входами першого блока пам'яті та першою групою входів першої схеми порівняння, керуючий вхід з'єднаний з другим входом елемента І, група інформаційних входів з'єднана з другою групою входів першої схеми порівняння, вихід якої з'єднаний з виходом ознаки відсутності рішення та через другий елемент HI з'єднаний з третім входом елемента І, який відрізняється тим, що містить перетворювач матриць, другу схему порівняння, другий та третій блоки пам'яті, причому виходи першого блока пам'яті з'єднані з першою групою входів перетворювача матриць, виходи другого блока пам'яті з'єднані з другою групою входів перетворювача матриць, виходи якого з'єднані з першою групою входів другої схеми порівняння, виходи третього блока пам'яті з'єднані з другою групою входів другої схеми порівняння, виходи другої схеми порівняння з'єднані з входом тригера.

Текст

Корисна модель відноситься до обчислювальної техніки й призначена для рішення задачі визначення еквівалентності бінарних матриць. Відомий пристрій для рішення логічних рівнянь [а.с. СРСР N1411768, кл. G06F15/20, опубл. 23.07.88р.], що містить лічильник, елемент І, перший і другий елементи НІ, тригер, операційний блок, блок порівняння, п груп по m елементів І. Недоліком відомого пристрою є низькі функціональні можливості. Відомий пристрій для розв’язання комбінаторно - логічних задач [Патент України №38565, м.кл. G06F15/20, опубл. Бюл. №4, 2001р.], що містить К груп інфомаційних входів по n розрядів у кожній, виходи результату, лічильник, блок пам’яті, тригер, перший і другий елементи HI, вихід ознаки відсутності рішення, вихід ознаки наявності рішення, керуючий вхід, перший елемент І, причому вихід тригера з’єднаний з виходом ознаки наявності рішення, та через перший елемент НІ з першим входом першого елемента І, керуючий вхід з’єднаний з другим входом першого елемента І та з керуючим входом блока пам’яті , вихід першого елемента І з’єднаний з рахунковим входом лічильника, виходи якого з’єднані з адресними входами блока пам’яті, К блоків обчислення значення співмножника, другий елемент І, виходи блока пам’яті з’єднані з першими групами входів блоків обчислення значення співмножника, і-та група інформаційних входів з’єднана з другою групою входів і-го блоку обчислення значення співмножника, виходи блоків обчислення значення співмножника з’єднані з відповідними входами другого елементу І, вихід якого з’єднаний з одиничним входом тригера. Недоліком відомого пристрою є низькі функціональні можливості. Найбільш близьким по технічній суті й результату, що досягається, є комбінаторно-логічний процесор [Патент України №54065 A, G06F15/20.// №2002043571; Заявл. 29.04.2002; Опубл. 17.02.2003, Бюл. №2], який має групу інформаційних входів, лічильник, перший блок пам’яті, тригер, перший і другий елементи НІ, вихід ознаки відсутності рішення, вихід ознаки наявності рішення, керуючий вхід, елемент І, першу схему порівняння, причому вихід тригера з’єднаний із виходом ознаки наявності рішення, та через перший елемент HI з першим входом елемента І, керуючий вхід з’єднаний із другим входом елемента І, вихід елемента І з’єднаний Із рахунковим входом лічильника, виходи якого з’єднані з адресними входами першого блока пам’яті та першою групою входів першої схеми порівняння, керуючий вхід з’єднаний з другим входом елемента І, група інформаційних входів з’єднана з другою групою входів першої схеми порівняння, вихід якої з’єднаний з виходом ознаки відсутності рішення та через другий елемент HI з’єднаний з третім входом елемента І. Недоліком відомого пристрою є низькі функціональні можливості. В основу корисної моделі поставлено задачу вдосконалити пристрій для визначення еквівалентності бінарних матриць шляхом введення нового складу елементів, та нової організації взаємозв’язків між ними забезпечити ширші функціональні можливості, а саме - спроможність визначати еквівалентність бінарних матриць. Поставлене завдання вирішується тим, що пристрій для визначення еквівалентності бінарних матриць, який має групу інформаційних входів, лічильник, перший блок пам’яті, тригер, перший і другий елементи HI, вихід ознаки відсутності рішення, вихід ознаки наявності рішення, керуючий вхід, елемент І, першу схему порівняння, причому вихід тригера з’єднаний із виходом ознаки наявності рішення, та через перший елемент HI з першим входом елемента І, керуючий вхід з’єднаний із другим входом елемента І, вихід елемента І з’єднаний з рахунковим входом лічильника, виходи якого з’єднані з адресними входами першого блока пам’яті та першою групою входів першої схеми порівняння, керуючий вхід з’єднаний з другим входом елемента І, група інформаційних входів з’єднана з другою групою входів першої схеми порівняння, вихід якої з’єднаний з виходом ознаки відсутності рішення та через другий елемент HI з’єднаний з третім входом елемента І, згідно з корисною моделлю містить перетворювач матриць, другу схему порівняння, другий та третій блоки пам’яті, причому виходи першого блоку пам’яті з’єднані з першою групою входів перетворювача матриць, виходи другого блоку пам’яті з’єднані з другою групою входів перетворювача матриць, виходи якого з’єднані з першою групою входів другої схеми порівняння, виходи третього блоку пам’яті з’єднані з другою групою входів другої схеми порівняння, виходи другої схеми порівняння з’єднані з входом тригера. Заявлений пристрій має новий склад елементів, та нову організацію взаємозв’язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості винаходу. Технічний результат, як наслідок цих властивостей - ширші функціональні можливості. На Фіг. представлена функціональна схема пристрою для визначення еквівалентності бінарних матриць. Пристрій для визначення еквівалентності бінарних матриць має групу інформаційних входів 1, лічильник 2, перший блок пам’яті 3, тригер 4, перший і другий елементи HI 5 та 6, вихід ознаки відсутності рішення 7, вихід ознаки наявності рішення 8, керуючий вхід 9, елемент І 10, першу схему порівняння 11, перетворювач матриць 12, другу схему порівняння 13, другий та третій блоки пам’яті 14 та 15, причому вихід тригера 4 з’єднаний із виходом ознаки наявності рішення 8, та через перший елемент HI 5 з першим входом елемента І, керуючий вхід 9 з’єднаний із другим входом елемента I 10, вихід елемента І 10 з’єднаний з рахунковим входом лічильника 2, виходи якого з’єднані з адресними входами першого блока пам’яті 5 та першою групою входів першої схеми порівняння 11, керуючий вхід 9 з’єднаний з другим входом елемента І 10, група інформаційних входів 1 з’єднана з другою групою входів першої схеми порівняння 11, вихід якої з’єднаний з виходом ознаки відсутності рішення 7 та через другий елемент HI 6 з’єднаний з третім входом елемента І 10, виходи першого блоку 3 пам’яті з’єднані з першою групою входів перетворювача матриць 12, виходи другого блоку пам’яті 14 з’єднані з другою групою входів перетворювача матриць 12, виходи якого з’єднані з першою групою входів другої схеми порівняння 13, виходи третього блоку пам’яті 15 з’єднані з другою групою входів другої схеми порівняння 13, виходи другої схеми порівняння 13 з’єднані з входом тригера 4. Працює пристрій для визначення еквівалентності бінарних матриць задач таким чином. На інформаційні входи 1 подається двійковий код значення кількості варіантів перетворень матриць. Спочатку тригер 4 та лічильник 2 знаходяться в стані "0". На керуючий вхід 7 подаються імпульси, що поступово змінюють стан лічильника 2. Для кожного значення коду, що поступає на перший блок пам’яті 3 на його виході формується вид перетворень і на виходах перетворювача матриць 12 формується новий вид матриці. Ці значення порівнюються в другій схеми порівняння 13 зі значеннями, що записані в третьому блоку пам’яті 15. Якщо значення співпадають, то на виході другої схеми порівняння формується сигнал «1», який переводить тригер 4 у стан «1». При цьому на виході 8 формується сигнал о наявності рішення, тобто матриці еквівалентні й елемент І 10 закривається. Якщо перебрані всі варіанти перетворень, а рішення немає, то на виході 7 формується сигнал «1» і елемент І 10 закривається.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determination of equivalence of binary matrixes

Автори англійськоюKoshovyi Mykola Dmytrovych, Pavlyk Hanna Volodymyrivna, Siroklyn Vitalii Pavlovych, Didyk Natalia Oleksiivna

Назва патенту російськоюУстройство для определения эквивалентности бинарных матриц

Автори російськоюКошевой Николай Дмитриевич, Павлик Анна Владимировна, Сироклин Виталий Павлович, Дидык Наталья Алексеевна

МПК / Мітки

МПК: G06F 15/00

Мітки: матриць, бінарних, визначення, пристрій, еквівалентності

Код посилання

<a href="https://ua.patents.su/2-33713-pristrijj-dlya-viznachennya-ekvivalentnosti-binarnikh-matric.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення еквівалентності бінарних матриць</a>

Попередній патент: Спосіб алопластики пахового каналу

Наступний патент: Фазовий спосіб визначення навантаження, відповідного умовній границі міцності деревини

Випадковий патент: Правило