Пристрій та спосіб обробки даних

Номер патенту: 99256

Опубліковано: 10.08.2012

Формула / Реферат

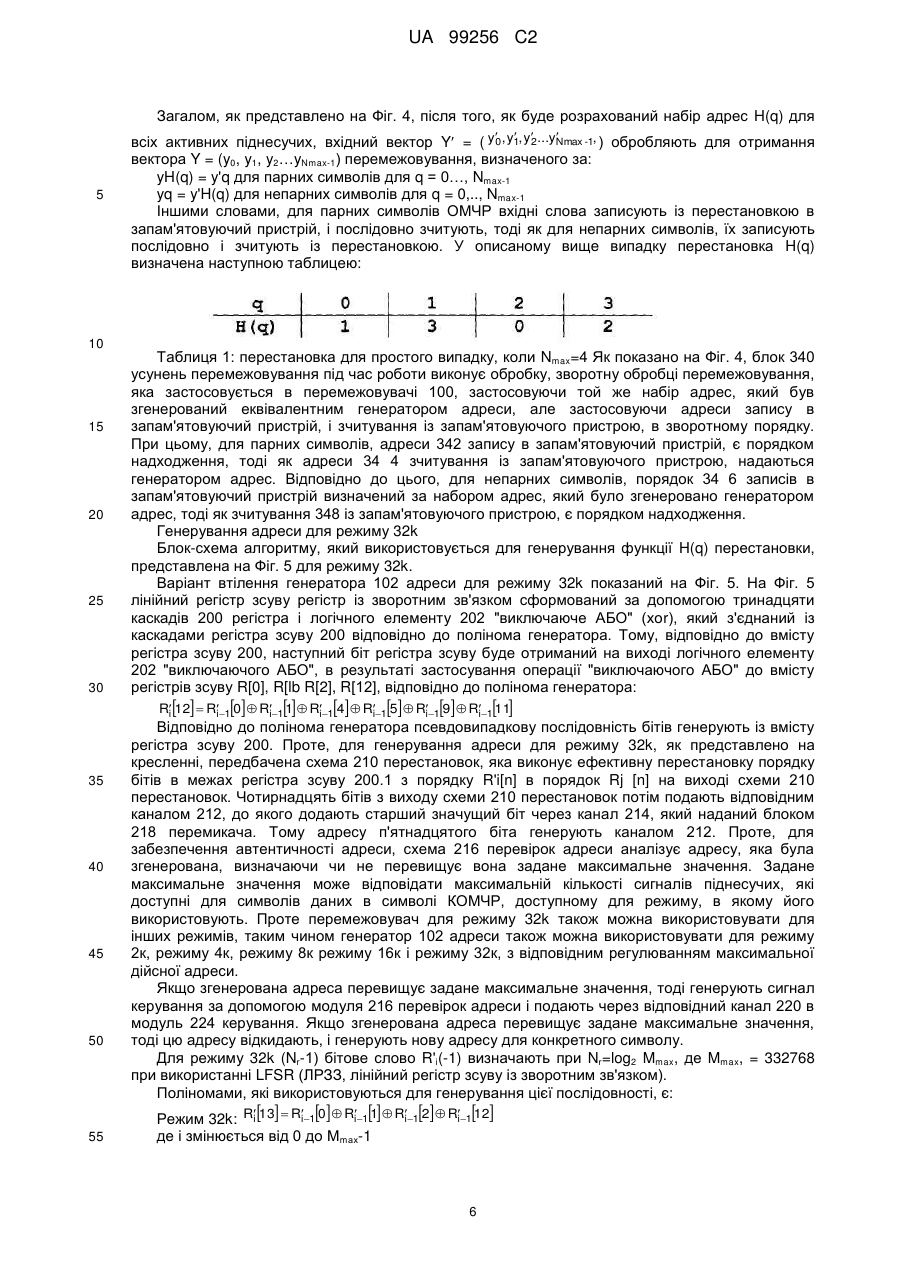

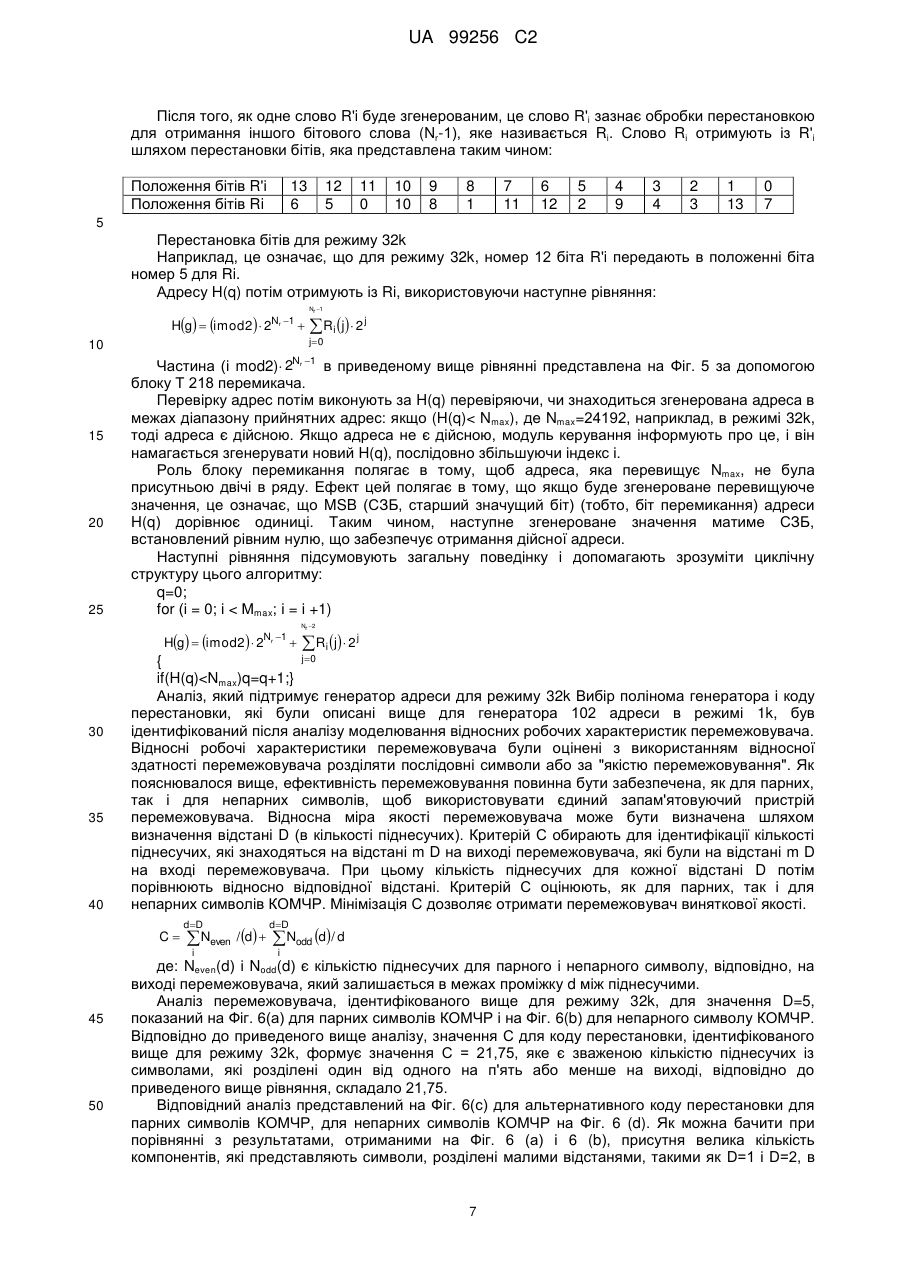

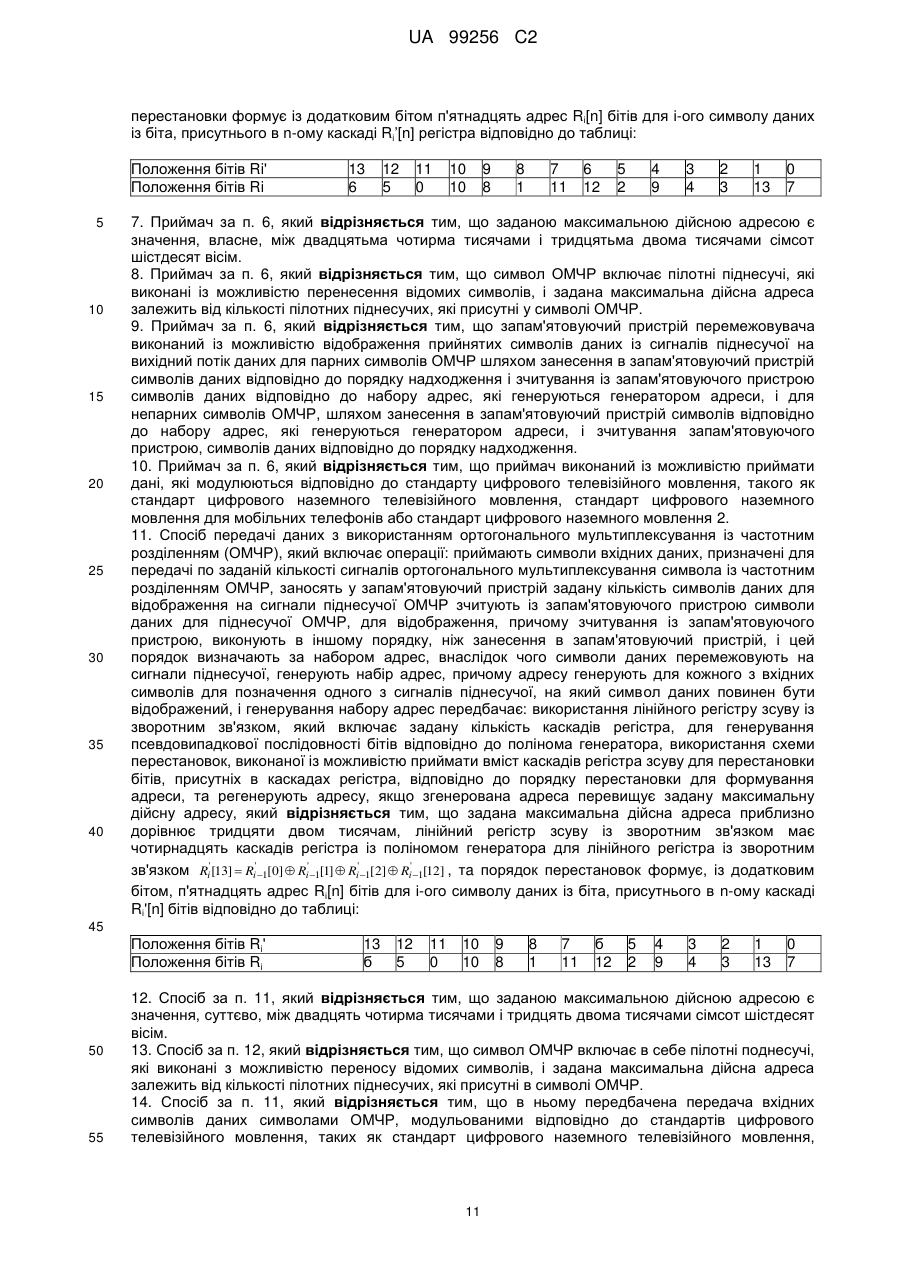

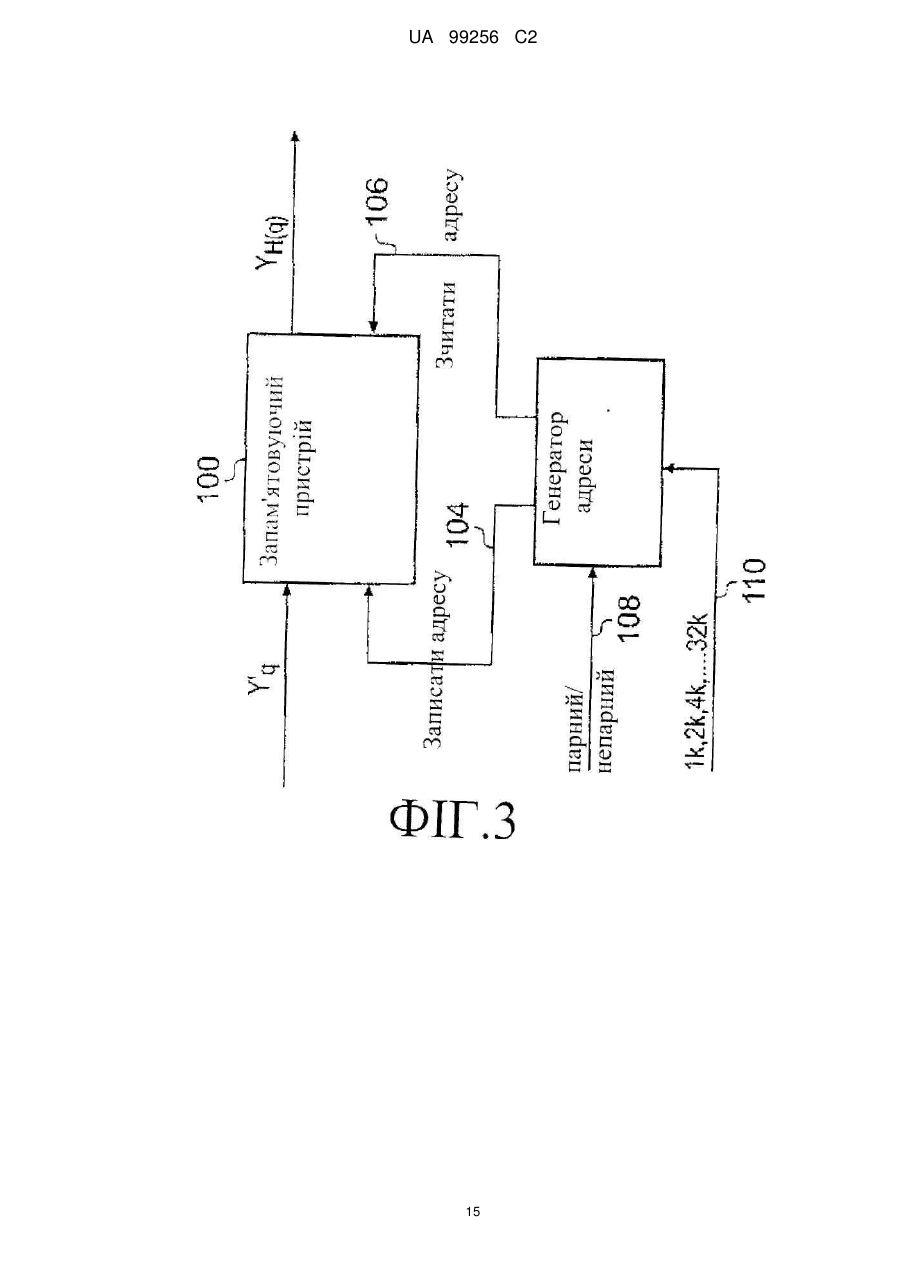

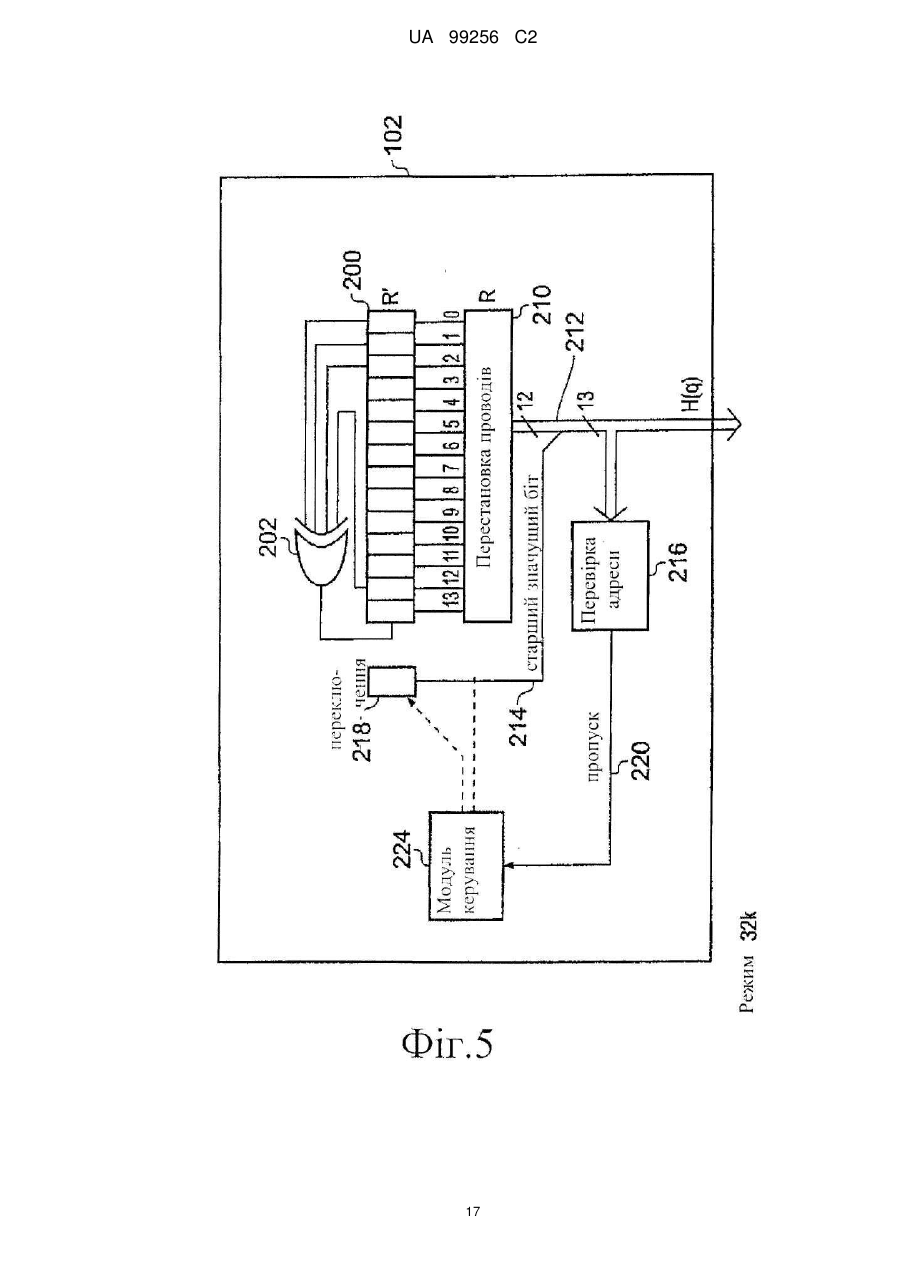

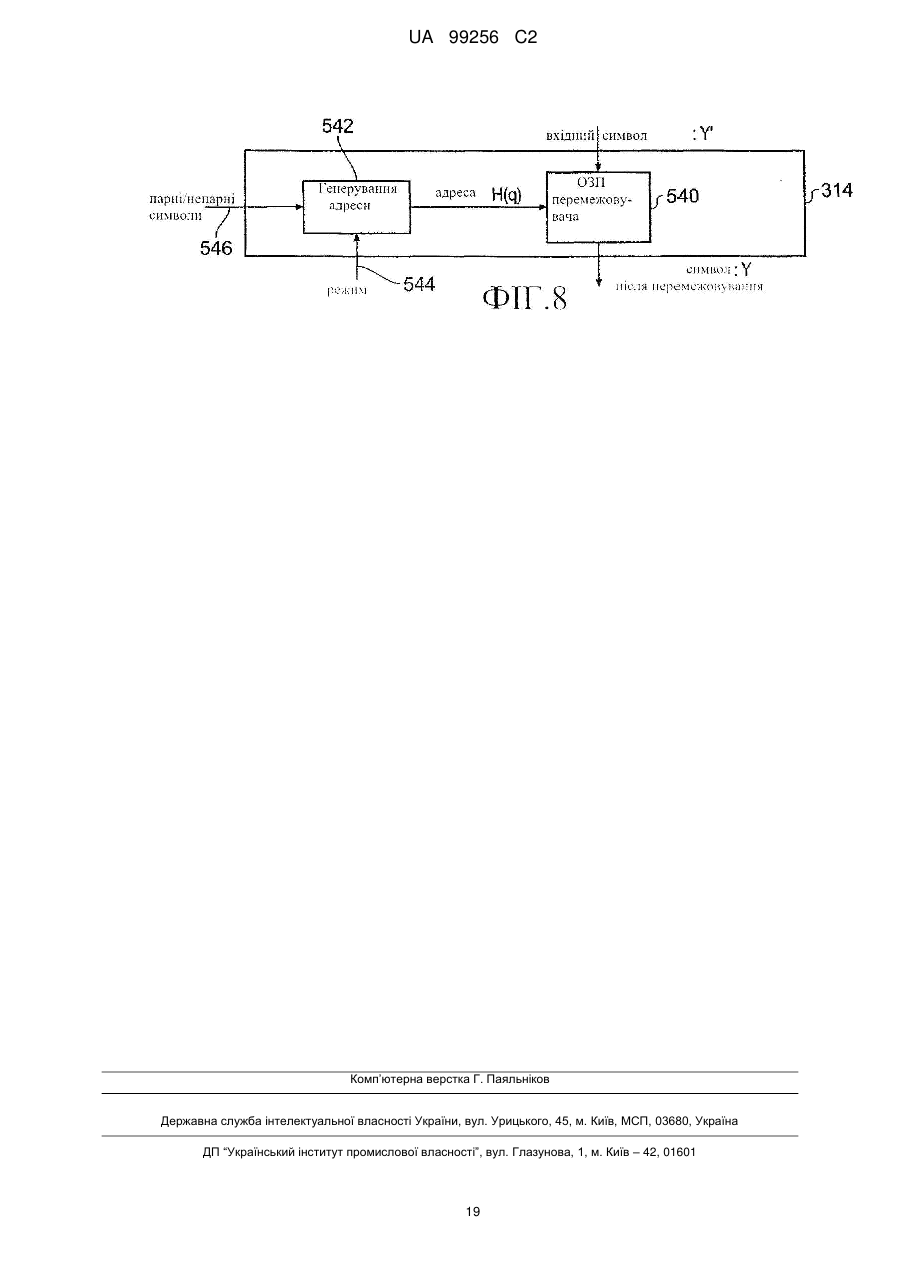

1. Передавач для передачі даних з використанням ортогонального мультиплексування із частотним розділенням (ОМЧР), причому передавач містить пристрій обробки даних, виконаний із можливістю відображення вхідних символів, призначених для передачі на задану кількість сигналів піднесучої ортогонального мультиплексованого із частотним розділенням (ОМЧР) символу, при цьому даний пристрій обробки даних містить: перемежовувач, виконаний із можливістю заносити у запам'ятовуючий пристрій задану кількість символів даних для відображення на сигнали піднесучої ОМЧР, і зчитувати запам'ятовуючого пристрою символи даних для піднесучих ОМЧР, для виконання відображення, причому зчитування із запам'ятовуючого пристрою, виконують в іншому порядку, ніж занесення в запам'ятовуючий пристрій, при цьому порядок визначають за набором адрес, внаслідок чого символи даних перемежовують по сигналу піднесучої, генератор адреси, виконаний із можливістю генерувати набір адрес, причому адреси генерують для кожного з вхідних символів для позначення одного з сигналів піднесучої, на який символ даних потрібно відобразити, і цей генератор адреси містить: лінійний регістр зсуву із зворотним зв'язком, який включає задану кількість каскадів регістра і виконаний із можливістю генерувати псевдовипадкову послідовність бітів відповідно до полінома генератора, схему перестановки, виконану із можливістю прийому вмісту каскадів регістра зсуву і перестановки бітів, присутніх в каскадах регістра, відповідно до порядку перестановки для формування адреси однієї з піднесучих ОМЧР, і модуль керування, виконаний з можливістю в комбінації із схемою перевірки адреси генерувати адресу, якщо згенерована адреса перевищує задану максимальну дійсну адресу, який відрізняється тим, що задана максимальна дійсна адреса складає приблизно тридцять дві тисячі, лінійний регістр зсуву із зворотнім зв'язком має чотирнадцять каскадів регістра з поліномом генератора для лінійного регістра зсуву із зворотнім зв'язком ![]() , i порядок перестановки формує з додатковим бітом, п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із бітів, які присутні n-ому каскаді регістра Ri[n] згідно таблиці:

, i порядок перестановки формує з додатковим бітом, п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із бітів, які присутні n-ому каскаді регістра Ri[n] згідно таблиці:

Положення бітів R'i

13

12

11

10

9

8

7

б

5

4

3

2

1

0

Положення бітів Ri

6

5

0

10

8

1

11

12

2

9

4

3

13

7

2. Передавач за п. 1, який відрізняється тим, що заданою максимальною дійсною адресою є значення, власне, між двадцятьма чотирма тисячами та тридцятьма двома тисячами сімсот шістдесят вісім.

3. Передавач за п. 1, який відрізняється тим, що символ ОМЧР включає пілотні піднесучі, призначені для перенесення відомих символів, і задана максимальна дійсна адреса залежить від кількості символів пілотних піднесучих, які присутні у символі ОМЧР.

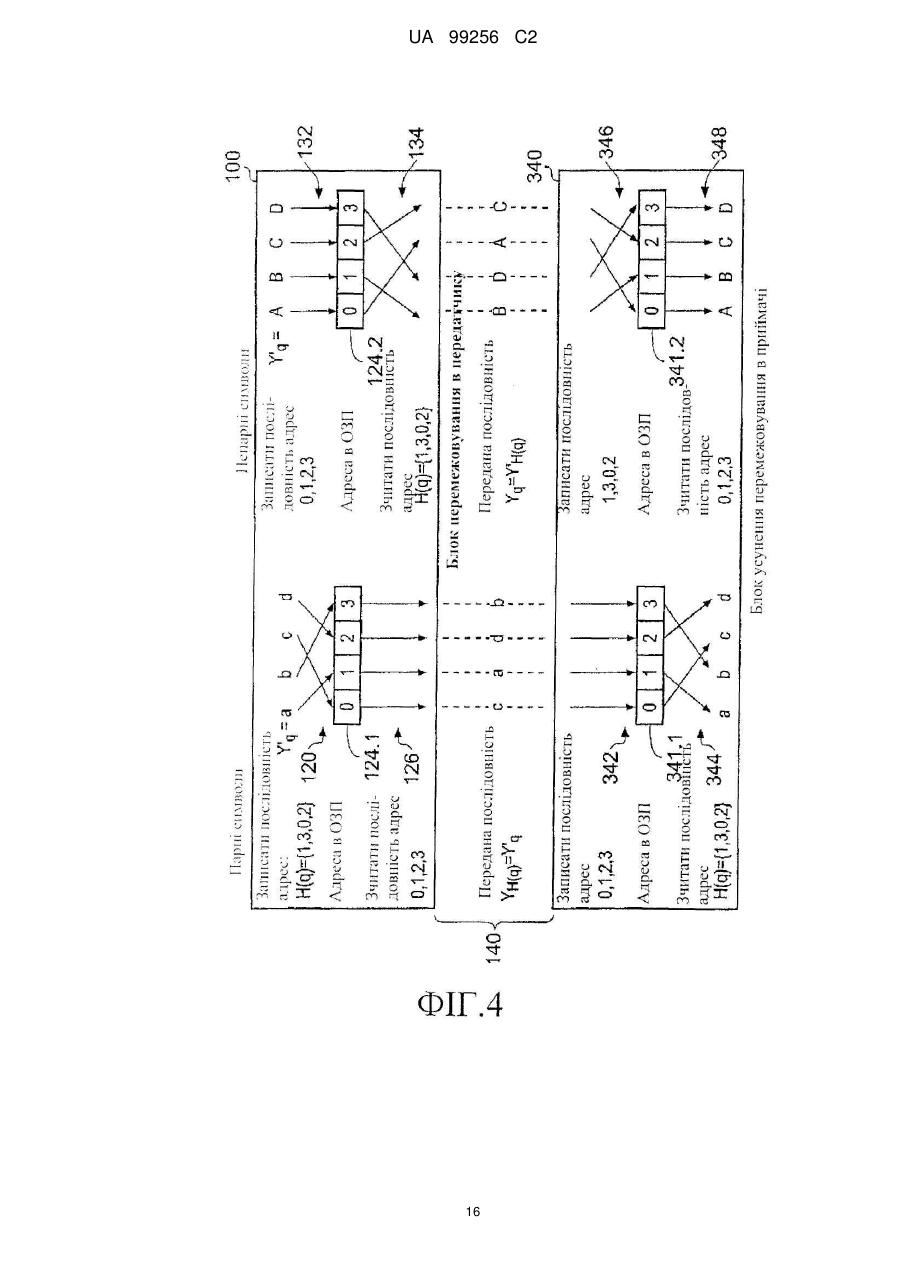

4. Передавач за п. 1, який відрізняється тим, що запам'ятовуючий пристрій перемежовувача виконаний із можливістю відображення символів вхідних даних на сигнали піднесучих для парних символів ОМЧР шляхом занесення в запам'ятовуючий пристрій символів даних відповідно до набору адрес, які генеруються генератором адреси, і зчитування із запам'ятовуючого пристрою, в порядку надходження, і для непарних символів ОМЧР, шляхом занесення в запам'ятовуючий пристрій символів даних в порядку надходження і зчитування із запам'ятовуючого пристрою, символів даних відповідно до набору адрес, які генеруються генератором адреси.

5. Передавач за п. 1, який відрізняється тим, що передавач виконаний із можливістю передавати дані відповідно до стандарту цифрового телевізійного мовлення, такого як стандарт цифрового наземного телевізійного мовлення, стандарт цифрового наземного мовлення для мобільних телефонів або стандарт цифрового наземного мовлення 2.

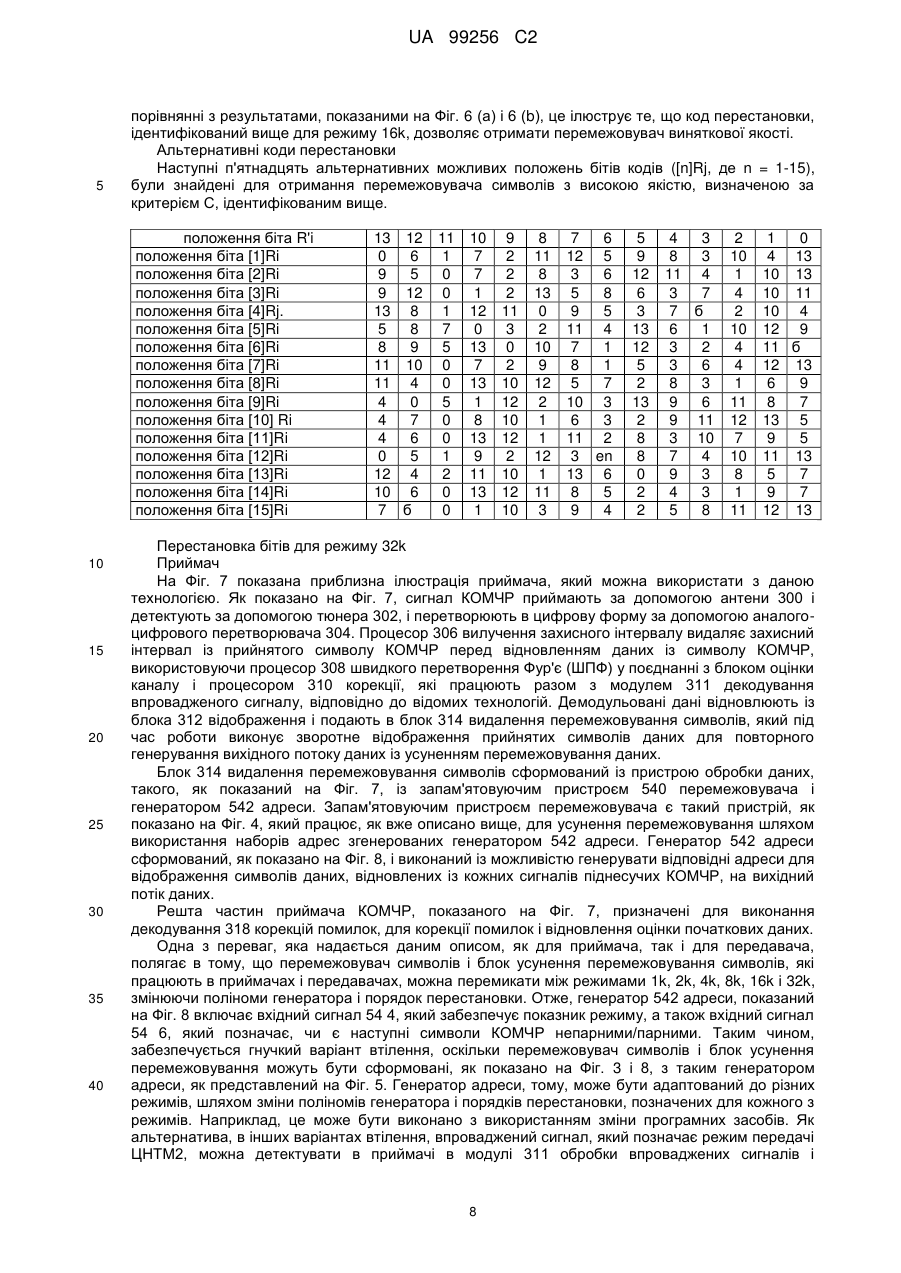

6. Приймач для прийому даних з сигналу, модульованого з використанням ортогонального мультиплексування із частотним розділенням (ОМЧР), причому приймач містить пристрій обробки даних, виконаний із можливістю відображати символи, прийняті із заданої кількості сигналів піднесучих ортогонального мультиплексованого символу із частотним розділенням (ОМЧР), у вихідний потік символів, причому цей пристрій обробки даних містить: блок усунення перемежовування, виконаний із можливістю занесення в запам'ятовуючий пристрій заданої кількості символів даних із сигналів піднесучих ОМЧР, і зчитувати із запам'ятовуючого пристрою символи даних у вихідний потік символів для виконання відображення, причому зчитування із запам'ятовуючого пристрою відрізняється за порядком від занесення в запам'ятовуючий пристрій причому порядок визначають за набором адрес, внаслідок чого в символах даних усувають перемежовування із сигналів піднесучих ОМЧР, генератор адреси виконаний із можливістю генерування набору адрес, причому адресу генерують для кожного з символів даних, що приймаються, для позначення сигналу піднесучої ОМЧР, із якої прийнятий символ даних потрібно відобразити у вхідний потік символів, де даний генератор адреси містить: лінійний регістр зсуву із зворотним зв'язком, який включає задану кількість каскадів регістра і виконаний із можливістю генерувати псевдовипадкову послідовність бітів відповідно до полінома генератора схему перестановки, виконану із можливістю приймати вміст каскадів регістра зсуву і виконувати перестановку бітів, присутніх в каскадах регістра, відповідно до порядку перестановки для формування адреси однієї з піднесучих ОМЧР, і модуль керування, виконаний із можливістю, в комбінації із схемою перевірки адреси, регенерувати адресу, якщо згенерована адреса перевищує задану максимальну дійсну адресу, який відрізняється тим, що задана максимальна дійсна адреса приблизно дорівнює тридцяти двом тисячам, лінійний регістр зсуву із зворотним зв'язком має чотирнадцять каскадів регістра із поліномом генератора для лінійного регістра із зворотним зв'язком ![]() , і порядок перестановки формує із додатковим бітом п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із біта, присутнього в n-ому каскаді Ri’[n] регістра відповідно до таблиці:

, і порядок перестановки формує із додатковим бітом п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із біта, присутнього в n-ому каскаді Ri’[n] регістра відповідно до таблиці:

Положення бітів Ri'

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Положення бітів Ri

6

5

0

10

8

1

11

12

2

9

4

3

13

7

7. Приймач за п. 6, який відрізняється тим, що заданою максимальною дійсною адресою є значення, власне, між двадцятьма чотирма тисячами і тридцятьма двома тисячами сімсот шістдесят вісім.

8. Приймач за п. 6, який відрізняється тим, що символ ОМЧР включає пілотні піднесучі, які виконані із можливістю перенесення відомих символів, і задана максимальна дійсна адреса залежить від кількості пілотних піднесучих, які присутні у символі ОМЧР.

9. Приймач за п. 6, який відрізняється тим, що запам'ятовуючий пристрій перемежовувача виконаний із можливістю відображення прийнятих символів даних із сигналів піднесучої на вихідний потік даних для парних символів ОМЧР шляхом занесення в запам'ятовуючий пристрій символів даних відповідно до порядку надходження і зчитування із запам'ятовуючого пристрою символів даних відповідно до набору адрес, які генеруються генератором адреси, і для непарних символів ОМЧР, шляхом занесення в запам'ятовуючий пристрій символів відповідно до набору адрес, які генеруються генератором адреси, і зчитування запам'ятовуючого пристрою, символів даних відповідно до порядку надходження.

10. Приймач за п. 6, який відрізняється тим, що приймач виконаний із можливістю приймати дані, які модулюються відповідно до стандарту цифрового телевізійного мовлення, такого як стандарт цифрового наземного телевізійного мовлення, стандарт цифрового наземного мовлення для мобільних телефонів або стандарт цифрового наземного мовлення 2.

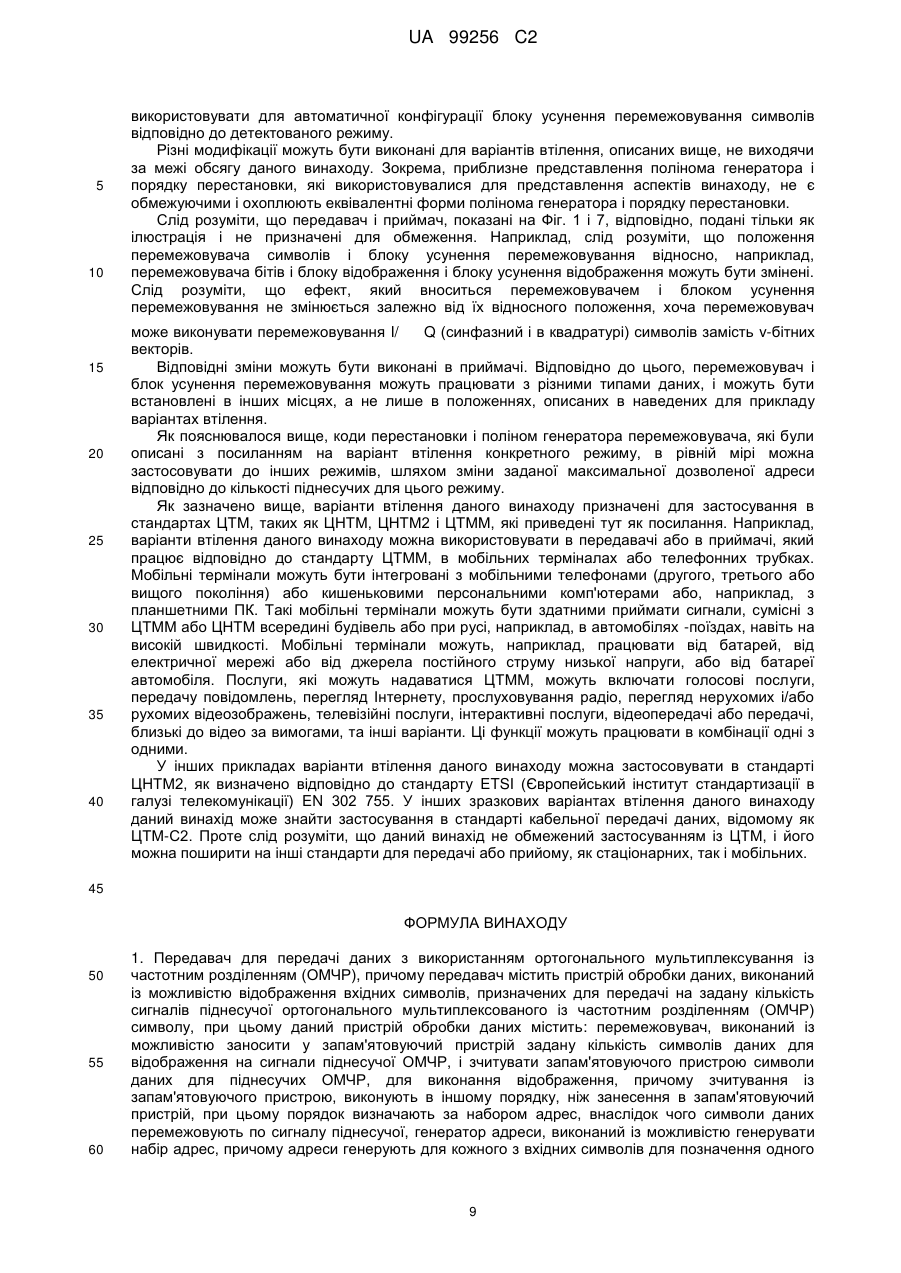

11. Спосіб передачі даних з використанням ортогонального мультиплексування із частотним розділенням (ОМЧР), який включає операції: приймають символи вхідних даних, призначені для передачі по заданій кількості сигналів ортогонального мультиплексування символа із частотним розділенням ОМЧР, заносять у запам'ятовуючий пристрій задану кількість символів даних для відображення на сигнали піднесучої ОМЧР зчитують із запам'ятовуючого пристрою символи даних для піднесучої ОМЧР, для відображення, причому зчитування із запам'ятовуючого пристрою, виконують в іншому порядку, ніж занесення в запам'ятовуючий пристрій, і цей порядок визначають за набором адрес, внаслідок чого символи даних перемежовують на сигнали піднесучої. генерують набір адрес, причому адресу генерують для кожного з вхідних символів для позначення одного з сигналів піднесучої, на який символ даних повинен бути відображений, і генерування набору адрес передбачає: використання лінійного регістру зсуву із зворотним зв'язком, який включає задану кількість каскадів регістра, для генерування псевдовипадкової послідовності бітів відповідно до полінома генератора, використання схеми перестановок, виконаної із можливістю приймати вміст каскадів регістра зсуву для перестановки бітів, присутніх в каскадах регістра, відповідно до порядку перестановки для формування адреси, та регенерують адресу, якщо згенерована адреса перевищує задану максимальну дійсну адресу, який відрізняється тим, що задана максимальна дійсна адреса приблизно дорівнює тридцяти двом тисячам, лінійний регістр зсуву із зворотним зв'язком має чотирнадцять каскадів регістра із поліномом генератора для лінійного регістра із зворотним зв'язком ![]() , тa порядок перестановок формує, із додатковим бітом, п'ятнадцять адрес Rі[n] бітів для і-ого символу даних із біта, присутнього в n-ому каскаді Ri'[n] бітів відповідно до таблиці:

, тa порядок перестановок формує, із додатковим бітом, п'ятнадцять адрес Rі[n] бітів для і-ого символу даних із біта, присутнього в n-ому каскаді Ri'[n] бітів відповідно до таблиці:

Положення бітів Ri'

13

12

11

10

9

8

7

б

5

4

3

2

1

0

Положення бітів Ri

б

5

0

10

8

1

11

12

2

9

4

3

13

7

12. Спосіб за п. 11, який відрізняється тим, що заданою максимальною дійсною адресою є значення, суттєво, між двадцять чотирма тисячами і тридцять двома тисячами сімсот шістдесят вісім.

13. Спосіб за п. 12, який відрізняється тим, що символ ОМЧР включає в себе пілотні поднесучі, які виконані з можливістю переносу відомих символів, і задана максимальна дійсна адреса залежить від кількості пілотних піднесучих, які присутні в символі ОМЧР.

14. Спосіб за п. 11, який відрізняється тим, що в ньому передбачена передача вхідних символів даних символами ОМЧР, модульованими відповідно до стандартів цифрового телевізійного мовлення, таких як стандарт цифрового наземного телевізійного мовлення, стандарт цифрового наземного мовлення для мобільних телефонів або стандарт цифрового наземного мовлення 2.

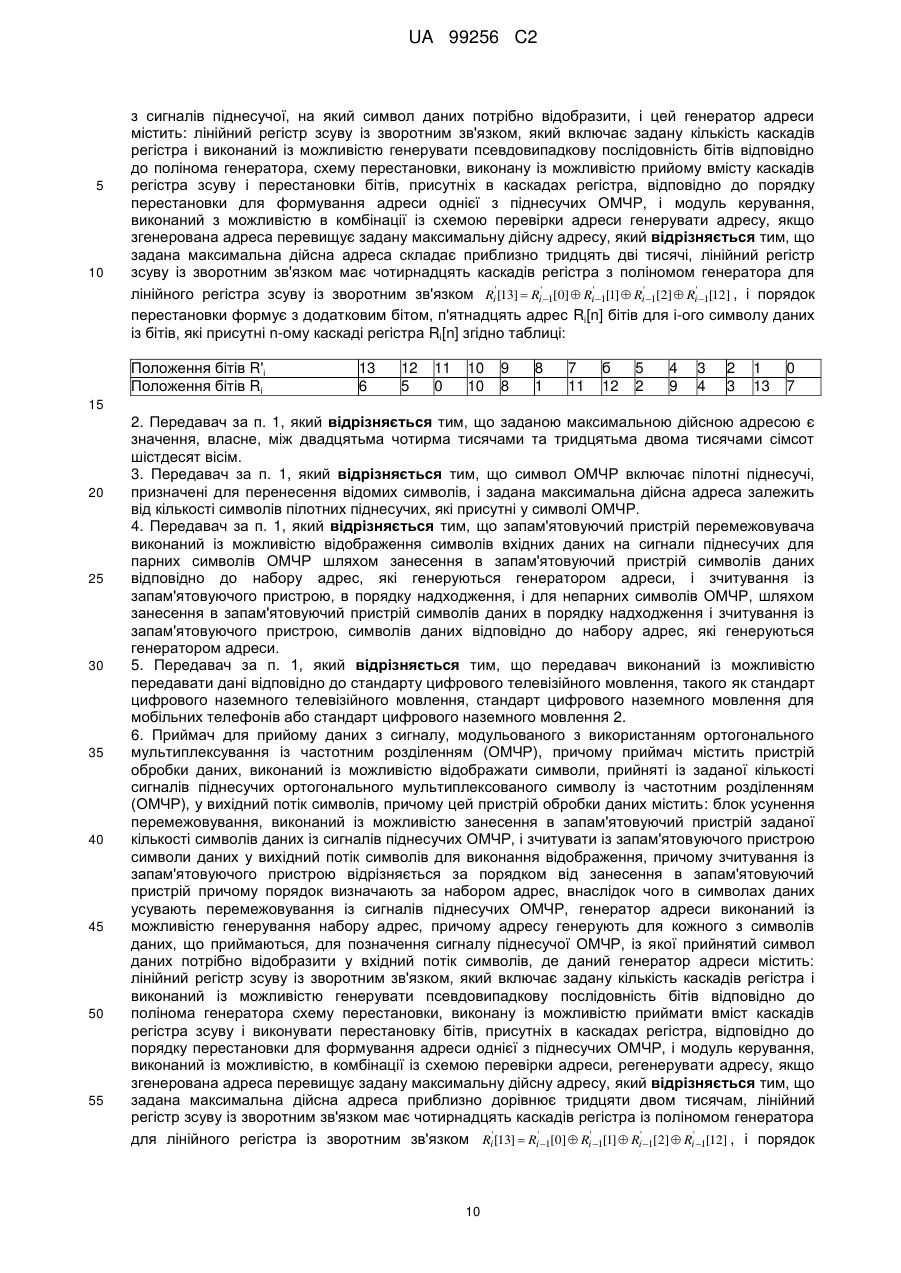

15. Спосіб прийому даних з символів, модульованих з ортогональним мультиплексуванням з частотним розділенням (ОМЧР) символу на потік вихідних символів, причому даний спосіб передбачає, що приймають символи даних з заданої кількості сигналів піднесучих ортогонального мультиплексування з частотним розділенням (ОМЧР) символу для формування у вихідний потік символів, заносять в запам'ятовуючий пристрій задану кількість символів даних із сигналів піднесучих ОМЧР, зчитують із запам'ятовуючого пристрою символи даних в вихідний потік даних для відображення, причому зчитування із запам'ятовуючого пристрою виконують в іншому порядку, ніж занесення в запам'ятовуючий пристрій, і цей порядок визначають за набором адрес, в результаті чого в символах даних видаляють перемежовування із сигналів піднесучих ОМЧР, генерують набір адрес, причому адресу генерують для кожного із прийнятих символів даних, для позначення сигналу піднесучої ОМЧР, із якої прийнятий символ даних необхідно відобразити в вихідний потік символу, де генерування набору адрес передбачає: використання лінійного регістру зсуву із зворотнім зв'язком, який містить в собі задану кількість каскадів регістра, для генерування псевдовипадкової послідовності бітів відповідно до поліному генератора, використання схеми перестановки для прийому вмісту каскадів регістра зсуву та перестановки бітів, які є присутніми в каскадах регістра, відповідно до порядку перестановки для формування адреси, та регенерують адресу, коли згенерована адреса перевищує задану максимальну дійсну адресу, який відрізняється тим, що задана максимальна дійсна адреса приблизно становить тридцять дві тисячі, лінійний регістр зсуву із зворотнім зв'язком має чотирнадцять каскадів регістра з поліномом генератора для лінійного регістра зсуву із зворотнім зв'язком ![]() , і порядок перестановок формує, з додатковим бітом, п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із біта, який присутній в n-ому каскаді R'i[n] згідно таблиці:

, і порядок перестановок формує, з додатковим бітом, п'ятнадцять адрес Ri[n] бітів для і-ого символу даних із біта, який присутній в n-ому каскаді R'i[n] згідно таблиці:

Положення бітів R'i

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Положення бітів Ri

6

5

0

10

8

1

11

12

2

9

4

3

13

7

16. Спосіб за п. 15, який відрізняється тим, що задана максимальна дійсна адреса має значення, суттєво, між двадцять чотирма тисячами та тридцять двома тисячами сімсот шістдесят вісім.

17. Спосіб за п. 15, який відрізняється тим, що символ ОМЧР включає в себе пілотні піднесучі, які виконані з можливістю переносу відомих символів, і задана максимальна дійсна адреса залежить від кількості символів пілотних піднесучих, присутніх в символі ОМЧР.

18. Спосіб за п. 15, який відрізняється тим, що прийом заданої кількості символів даних із символу ОМЧР включає прийом даних відповідно до стандарту цифрового телевізійного мовлення, такого як стандарт цифрового наземного телевізійного мовлення, стандарт цифрового наземного мовлення для мобільних телефонів або стандарт цифрового наземного мовлення 2.

Текст

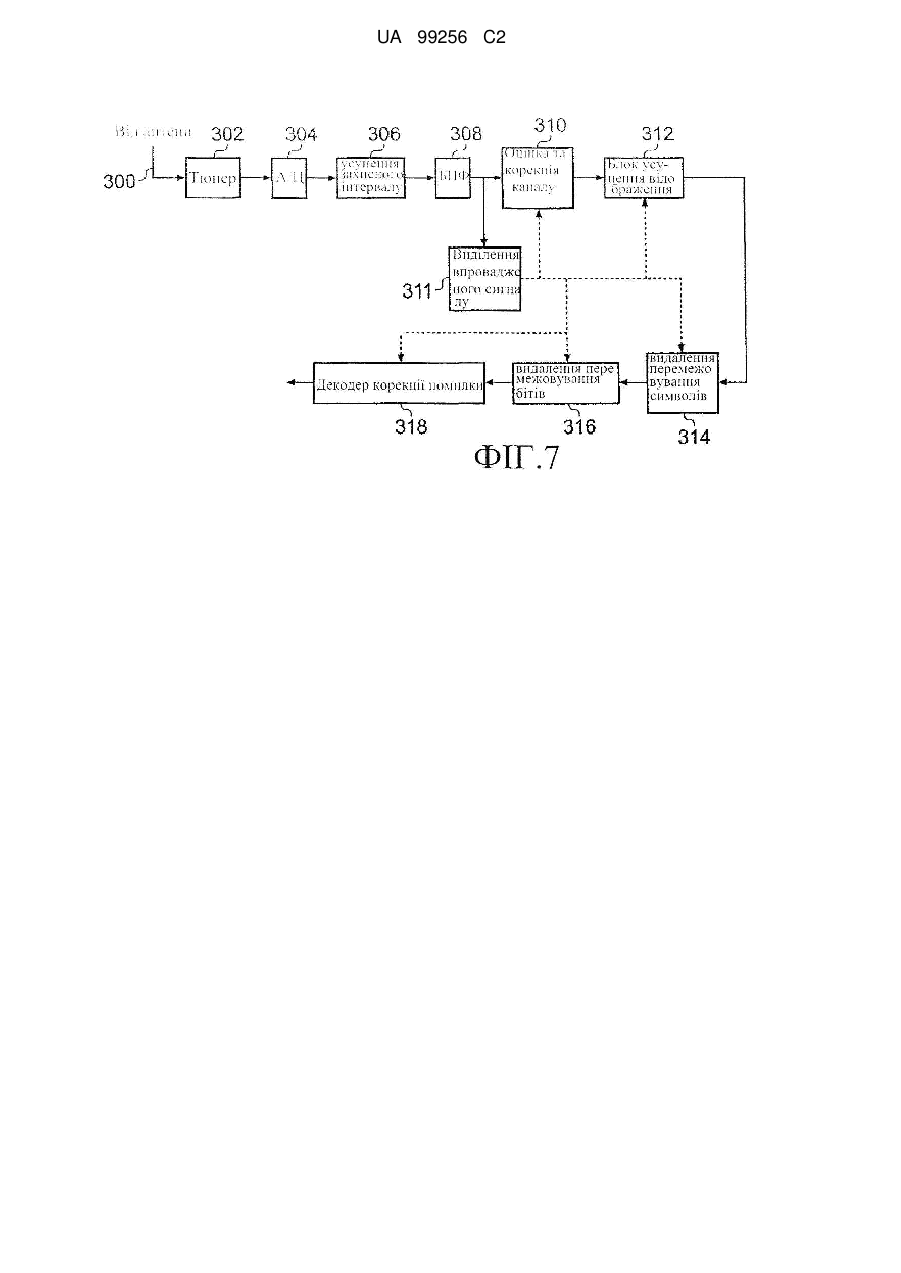

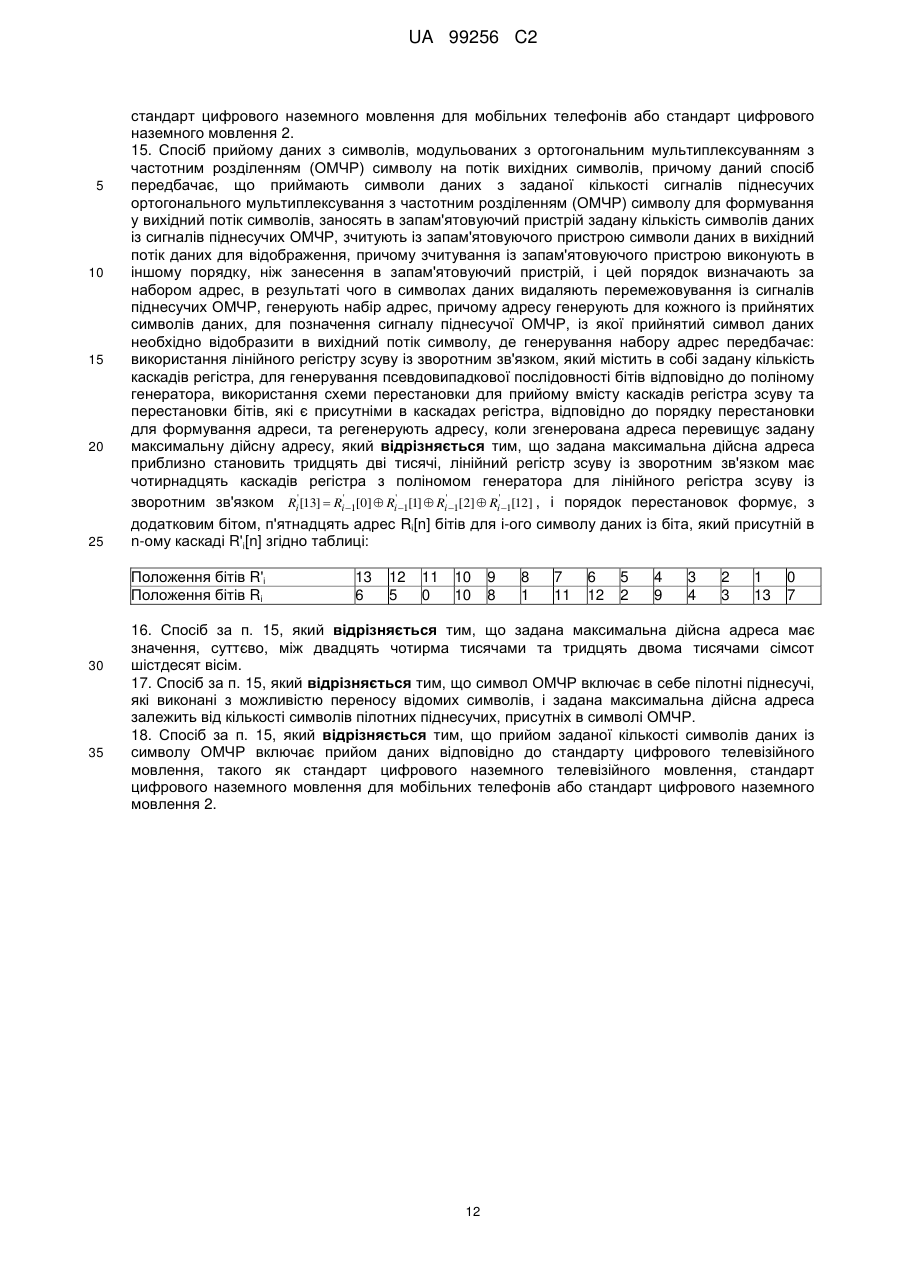

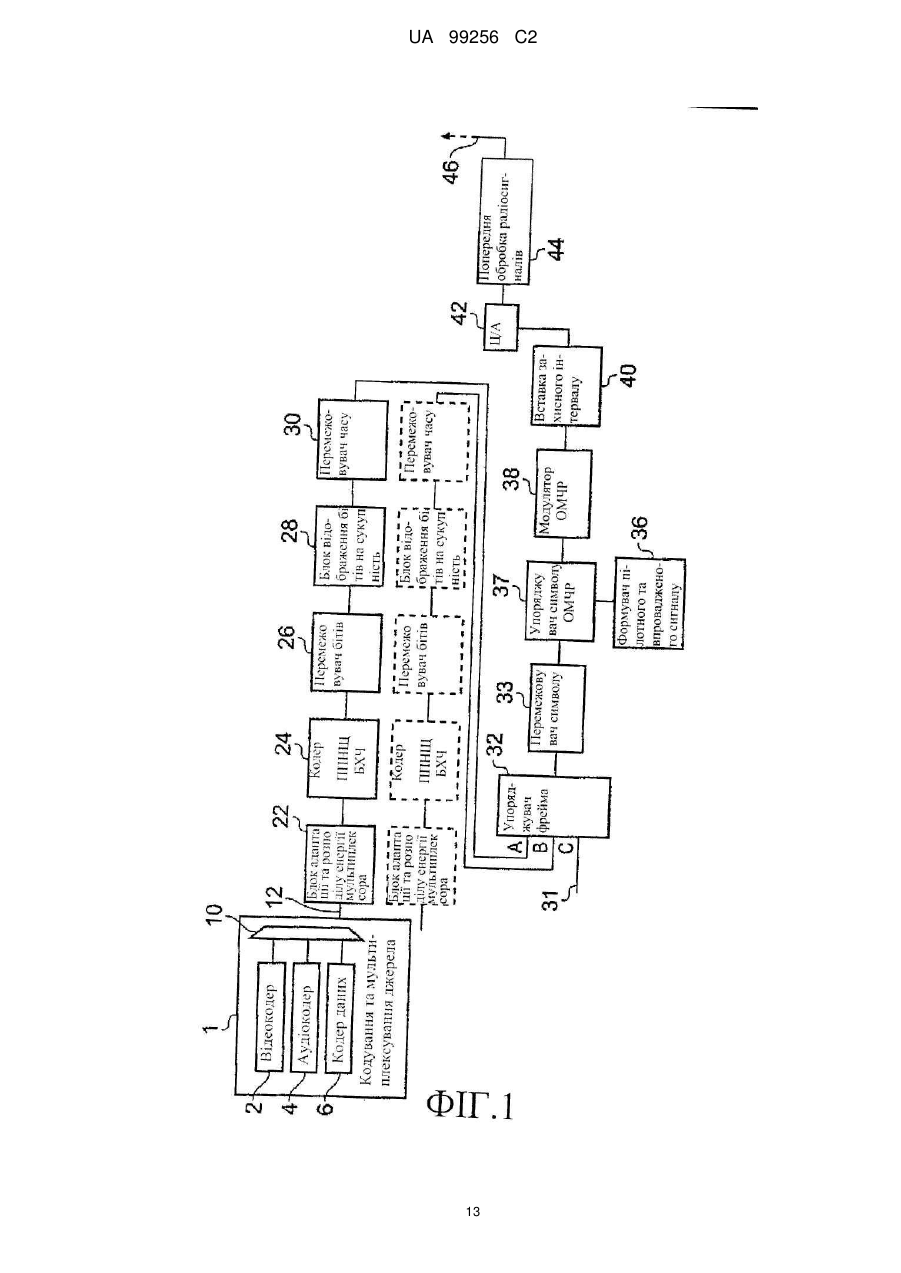

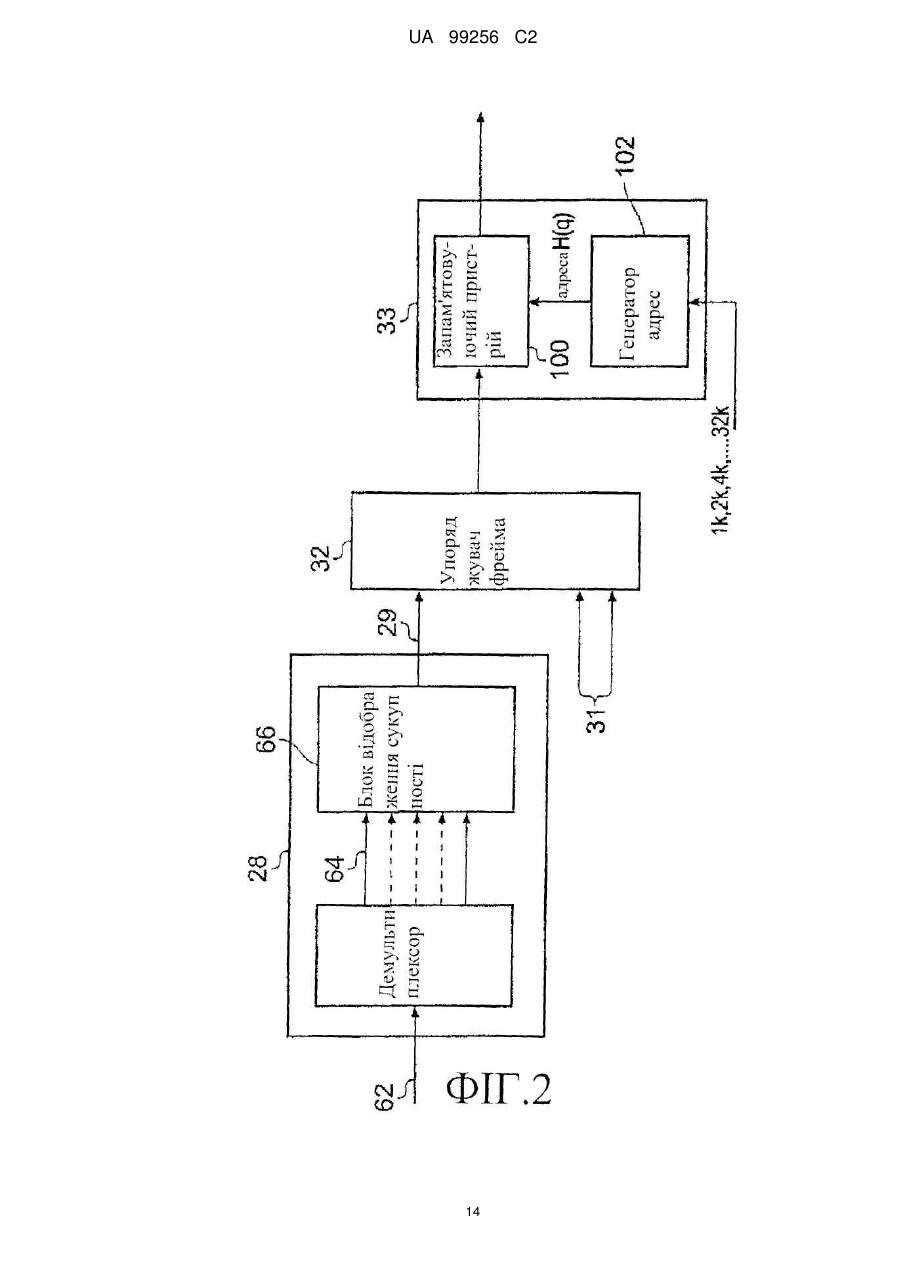

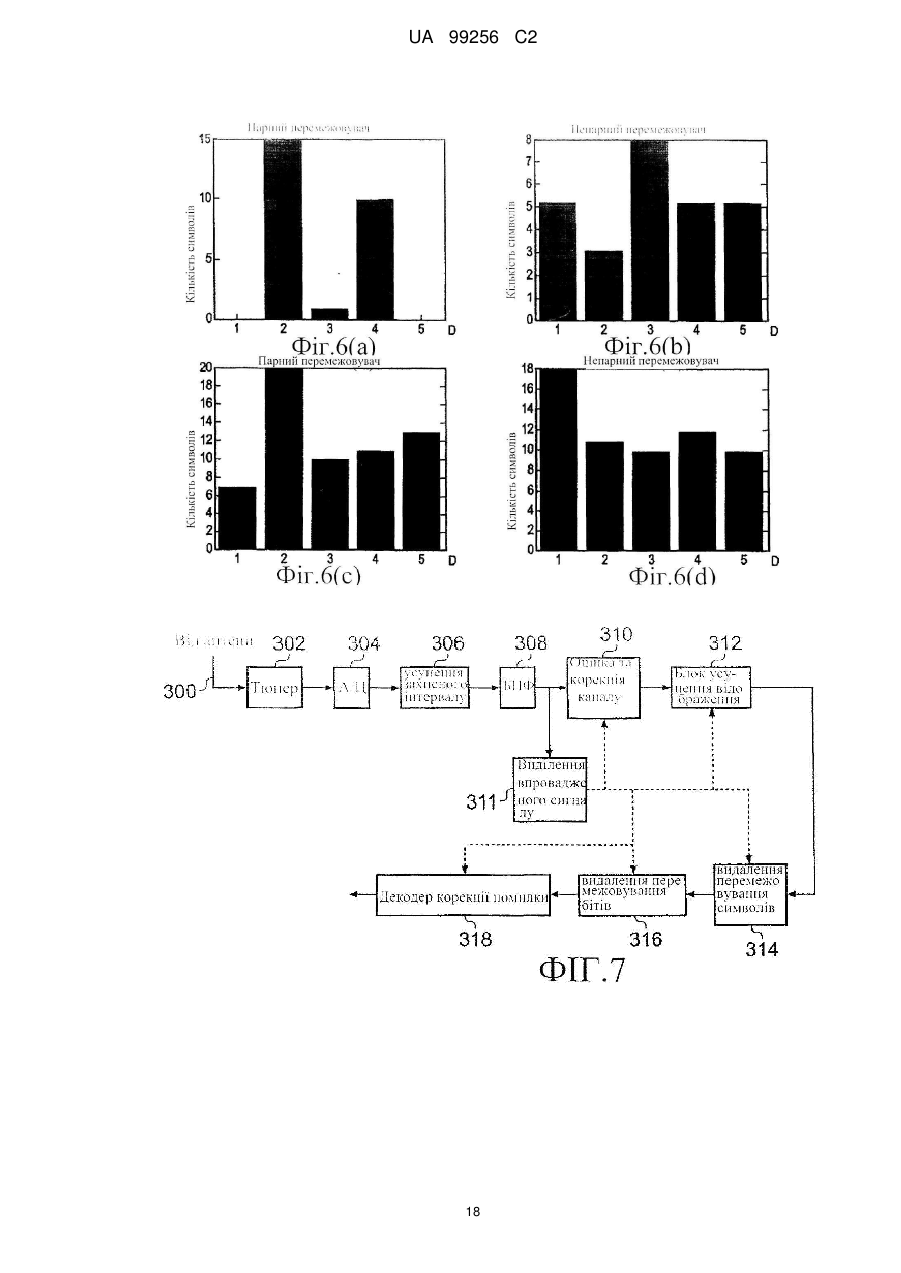

Реферат: Пристрій обробки даних відображає вхідні символи, призначені для передачі, в задану кількість сигналів піднесучої ортогонального мультиплексованого з частотним розділенням (ОМЧР) символу. Процесор обробки даних включає в себе запам'ятовуючий пристрій перемежовувача, який зчитує задану кількість символів даних для відображення на сигнали піднесучої ОМЧР. Запам'ятовуючий пристрій перемежовувача зчитує символи даних на піднесучі ОМЧР для виконання відображення, причому зчитування із запам'ятовуючого пристрою виконують в іншому порядку, ніж занесення в запам'ятовуючий пристрій, порядок визначають за набором адрес, в результаті чого символи даних перемежовують на сигнали піднесучої. Набір адрес генерують із генератора адреси, який містить лінійний регістр зсуву із зворотним зв'язком і схему перестановок. UA 99256 C2 (12) UA 99256 C2 UA 99256 C2 5 10 15 20 25 30 35 40 45 50 55 60 Даний винахід відноситься до пристрою обробки даних, який під час роботи відображує вхідні символи на сигнали піднесучої ортогонального мультиплексованого з частотним розділенням (OFDM, ОМЧР) символу. Даний винахід також відноситься до генератора адреси, який використовується при записі символів та/зчитувані символів з запам'ятовуючого пристрою перемежовувача. Даний винахід також відноситься до пристрою обробки даних, який під час роботи відображає символи, прийняті із заданої кількості сигналів піднесучих символів ОМЧР на вихідний потік символів. Варіанти втілення даного винаходу дозволяють отримати передавач/приймач ОМЧР. У стандарті цифрового наземного телевізійного мовлення (DVB-T, ЦНТМ) використовується ортогональне мультиплексування з частотним розділенням каналів (ОМЧР), для передачі даних, які представлені відеозображеннями і звуками, в приймачі через радіосигнали широкомовної передачі. Як відомо, існують дві моделі для стандарту ЦНТМ, відомі як режим 2к і 8к. Режим 2к забезпечує 2048 піднесучих, тоді як в режимі 8к передбачається 8192 піднесучих. Аналогічно, для стандарту цифрового телевізійного мовлення для мобільних телефонів (DVB-H, ЦТММ) був передбачений режим 4к, в якому кількість піднесучих складає 4096. Для покращення цілісності даних, які передаються з використанням ЦНТМ або ЦТММ, передбачений перемежовувач символів для перемежовування символів вхідних даних, і ці символи відображають на сигнали піднесучих символу ОМЧР. Такий перемежовувач символів містить запам'ятовуючий пристрій пєремежовувача в комбінації з генератором адреси. Генератор адреси генерує адреси для кожного з вхідних символів, причому кожна адреса позначає один з сигналів піднесучих символу ОМЧР, на яких слід відображати символ даних. Для режиму 2к і для режиму 8к були розкриті компоновки генерування адрес в стандарті ЦНТМ для відображення. Аналогічно, для режиму 4к в стандарті ЦТММ, була передбачена компоновка генерування адрес для відображення, і генератор адреси для втілення цього відображення розкритий в заявці на європейській патент 04251667.4. Генератор адреси містить лінійний регістр зсуву із зворотним зв'язком, який під час роботи генерує псевдовипадкову послідовність бітів і схему перестановки. Схема перестановки виконує перестановку порядку вмісту лінійного регістра зі зворотним зв'язком для генерування адреси. Адреса забезпечує показник для однієї з піднесучих ОМЧР, для перенесення символу вхідних даних, збереженого в запам'ятовуючому пристрої пєремежовувача для відображення вхідних символів на сигнали піднесучих символу ОМЧР. Аналогічно, генератор адреси в приймачі виконаний з можливістю генерування адрес запам'ятовуючого пристрою пєремежовувача для зберігання символів даних, які приймаються із піднесучих символів ОМЧР, для зчитування символів даних і формування вихідного потоку даних. Відповідно до додаткового розвитку стандарту цифрового наземного телевізійного мовлення, відомого як ЦНТМ2, було запропоновано передбачити додаткові режими для передачі даних. Сутність винаходу Відповідно до аспекту даного винаходу запропонований пристрій обробки даних, виконаний з можливістю відображати вхідні символи, призначені для передачі, на задану кількість сигналів піднесучої ортогональних мультиплексованих з частотним розділенням (ОМЧР) символів. Пристрій обробки даних містить перемежовувач, який під час роботи заносить в запам'ятовуючий пристрій задану кількість символів даних, для відображення на сигнали піднесучої ОМЧР, і зчитування із запам'ятовуючого пристрою символів даних для піднесучих ОМЧР, для виконання відображення. Зчитування із запам'ятовуючого пристрою виконують в іншому порядку, ніж занесення в запам'ятовуючий пристрій причому порядок визначається за набором адрес, внаслідок чого виконують перемежовування символів даних на сигнали піднесучих. Набір адрес визначають за допомогою генератора адреси, причому адресу генерують для кожного з вхідних символів для позначення одного з сигналів піднесучої, на які потрібно виконати відображення символу даних. Генератор адреси містить лінійний регістр зсуву із зворотним зв'язком, який включає задану кількість каскадів регістра і, який виконаний з можливістю генерувати псевдовипадкову послідовність бітів відповідно до полінома генератора, і схему перестановки, і модуль керування. Схема перестановки виконана з можливістю приймати вміст каскадів регістра зсуву і виконувати перестановку бітів, присутніх в каскадах регістра, відповідно до порядку перестановки для формування адреси однієї з піднесучих ОМЧР. Модуль керування виконано з можливістю разом із схемою перевірки адреси регенерувати адресу, коли згенерована адреса перевищує задану максимальну дійсну адресу. Пристрій обробки даних відрізняється тим, що задана максимальна дійсна адреса наближено дорівнює 1 UA 99256 C2 тридцять двом тисячам, лінійний регістр зсуву із зворотнім зв'язком має чотирнадцять каскадів регістра з поліномом генератора для лінійного регістра зсуву із зворотнім зв'язком R13 R10 R11 R12 R112, i i i i i і порядок перестановки формує, використовуючи додатковий біт, п'ятнадцять адрес Ri[n] бітів для і-того символу даних із біта, який є присутнім в 5 i n-ому каскаді R [n] регістра згідно таблиці: Положення бітів R'і Положення бітів Ri 10 15 20 25 30 35 40 45 50 55 13 6 12 5 11 0 10 10 9 8 8 1 7 11 6 12 5 2 4 9 3 4 2 3 1 13 0 7 Хоча із стандарту ЦНТМ відоме надання режиму 2к і режиму 8к, і стандарт ЦТММ описує режим 4к, було запропоновано розробити режим 32к для ЦНТМ2. Хоча режим 8к забезпечує компоновку для встановлення одночастотної мережі з достатніми захисними періодами для розміщення великих періодів затримки на поширення між передавачами DVB (ЦТМ), режим 2к, як відомо, забезпечує перевагу в мобільних застосуваннях. Це пов'язано з тим, що період символу 2к складає тільки одну четверту періоду символу 8к, що дозволяє частіше виконувати оновлення оцінки каналу, що забезпечує для приймача можливість відстежувати варіації за часом каналу, точніше використовуючи ефект Доплера та інші ефекти. Режим 2к, тому, є більш бажаним для мобільних застосувань. Для забезпечення більш рознесеного розміщення передавачів ЦТМ в межах одночастотної мережі було запропоновано розробити режим 32к. Для втілення режиму 32к перемежовувач символу повинен бути пристосований для відображення символів вхідних даних на сигнали піднесучих символів ОМЧР. Варіанти втілення даного винаходу дозволяють розробити пристрій обробки даних, виконаний з можливістю виконання функції перемежовувача символів, для відображення символів даних, призначених для передачі, на символ ОМЧР, який має приблизно тридцять дві тисячі сигналів піднесучої. У одному варіанті втілення кількість сигналів піднесучих може бути величиною, яка знаходиться власне, між двадцятьма чотирма тисячами і тридцятьма двома тисячами сімсот шістдесят вісім. Крім того, символ ОМЧР може включати пілотні піднесучі, які призначені для перенесення відомих символів, і задана максимальна дійсна адреса залежить від кількості символів пілотні піднесучі, присутніх у символі ОМЧР. Таким чином, режим 32k може бути передбаченим, наприклад, для стандарту ЦТМ, такого як ЦНТМ2, ЦНТМ або ЦТММ. Відображення символів даних, призначених для передачі, на сигнали піднесучих символу ОМЧР, де кількість сигналів піднесучої приблизно складає тридцять дві тисячі, є технічним завданням, яке вимагає аналізу моделюванням і випробувань для встановлення відповідного полінома генератора для лінійного регістра із зворотним зв'язком і порядку перестановки. Це пов'язано з тим, що відображення вимагає, щоб символи перемежовувались на сигнали піднесучої, внаслідок чого послідовні символи вхідного потоку даних були б розділені за частотою на найбільшу можливу величину для оптимізації робочих характеристик схем кодування з корекцією помилок. Схеми кодування з корекцією помилок, такі як кодування LDCP/BCH (ППНЩ/БЧХ, код перевірки на парність з низькою щільністю/ код Бозе-Чоудхурі-Хоквінгема), які були запропоновані для ЦНТМ2, працюють краще, коли шуми і деградація значень символу в результаті передачі даних будуть не скорельованими. Наземні широкомовні канали можуть вводити корельовані загасання, як в області часу, так і в області частоти. При цьому, в результаті рознесення кодованих символів на різні сигнали піднесучих символів ОМЧР, на як можна більшу відстань, можна поліпшити робочі характеристики схем кодування корекції помилок. Як пояснюється нижче, проаналізувавши характеристики моделювання визначили, що поліном генератора для лінійного регістра із зворотним зв'язком у поєднанні з порядком схеми перестановки, позначеним вище, забезпечують гарні робочі характеристики. Крім того, завдяки наданню компоновки, яка може втілювати генерування адреси для кожного з режимів 2к, режиму 4к і режиму 8к, змінюючи відведення полінома генератора для лінійного регістра із зворотним зв'язком і порядку перестановки, може бути передбачений економічний варіант втілення перемежовувача символів для режиму 32к. Крім того, передавач і приймач можна перемикати між режимом 2к, режимом 4к, режимом 8к і режимом 32к шляхом зміни полінома генератора і порядків перестановки. Це може бути виконано за допомогою програмних засобів (або упроваджених сигналів), внаслідок чого забезпечується гнучке втілення. Додатковий біт, який використовується для формування адреси із вмісту лінійного регістра із зворотним зв'язком, може бути сформований за допомогою схеми перемикання, яка перемикає 2 UA 99256 C2 5 10 15 20 25 30 35 40 45 50 55 60 свій стан з 1 на 0 для кожної адреси, так, щоб знизити вірогідність того, що, якщо адреса перевищує задану максимальну дійсну адресу, то така адреса буде дійсною адресою. У одному прикладі додатковим бітом є старший значущий біт. Різні аспекти і властивості даного винаходу визначені в прикладеній формулі винаходу. Додаткові аспекти даного винаходу включають пристрій і спосіб обробки даних, які призначені для відображення символів, які приймаються із заданої кількості сигналів піднесучих для ортогонально мультиплексованого з частотним розділенням (ОМЧР) символу у вихідний потік символів, а також до передавача і приймача. Короткий опис креслень Варіанти втілення даного винаходу будуть описані нижче лише як приклад із посиланням на креслення, які додаються, на яких однакові деталі позначені відповідними номерами посилальних позицій, і на яких: на Фіг. 1 показана блок-схема передавача кодованого ОМЧР, який можна використовувати, наприклад, із стандартом ЦНТМ2; на Фіг. 2 показана блок-схема частини передавача, представленого на Фіг. 1,'на якій блок відображення символів і упоряджувач фрейма ілюструють роботу перемежовувача на Фіг. З показана блок-схема перемежовувача символів, представленого на Фіг. 2; на Фіг. 4 показана блок-схема запам'ятовуючого пристрою, представленого на Фіг. З, і відповідного блоку усунення перемежовування символів в приймачі; на Фіг. 5 показана блок-схема генератора адреси, представленого на Фіг. З, для режиму 16k; на Фіг. 6(а) показана схема, яка ілюструє результати для перемежовувача, який використовує генератор адреси, представлений на Фіг. 5, для парних символів ОМЧР, і на Фіг. 6(b) показана схема, яка ілюструє результати моделювання конструкції для непарних символів ОМЧР, тоді як на Фіг. 6(с) показана схема, яка ілюструє співрозмірні результати для генератора адреси з використанням іншого коду перестановки для парних символів ОМЧР, і на Фіг. 6(d) показана відповідна схема для непарних символів ОМЧР; На Фіг. 7 показана блок-схема приймача кодованого ОМЧР, який можна використовувати, наприклад, із стандартом ЦНТМ2; На Фіг. 8 показана блок-схема перемежовувача символів, який можна бачити на Фіг. 7. Докладний опис винаходу Було запропоновано розширити низку режимів, які є доступними в стандарті ЦНТМ2, так, щоб вони включали режим Ik, режим 16k і режим 32k. Даний опис покликаний ілюструвати роботу перемежовувача символів відповідно до даного опису, хоча буде зрозуміло, що перемежовувач символів можна використовувати в інших режимах і для інших стандартів DVB. На Фіг. 1 подано приклад блок-схеми ОМЧР кодованого передавача, який можна використовувати, наприклад, для передачі відео зображення і звукових сигналів відповідно до стандарту ЦНТМ2. На Фіг. 1 джерело програми генерує дані, призначені для передачі передавачем COFDM (КОМЧР). Відеокодер 2 і аудіо кодер 4, і кодер 6 даних генерують відео, аудіо та інші дані для передачі, які подають в мультиплексор 10 програм. Вихід мультиплексора 10 програм формує мультиплексований потік з іншою інформацією, потрібною для передачі відео, аудіо та інших даних. Мультиплексор 10 забезпечує потік по сполучному каналу 12. Тут може бути присутньою велика кількість таких мультиплексованих потоків, які подають в різні відгалуження А, В і так далі Для простоти описано тільки відгалуження А. Як показано на Фіг. 1, передавач 20 СОМЧР приймає потік в блоці 22 адаптації і розподілу енергії мультиплексора. Блок 22 адаптації і розподілу енергії мультиплексора вносить елемент випадковості в дані і передає відповідні дані в кодер 24 прямих корекції помилок, який виконує кодування корекції помилок потоку. Перемежовувач 26 бітів передбачений для перемежовування кодованих бітів даних, які, для прикладу ЦНТМ2, є виходом кодера LDCP/BCH (ППНЩ/БЧХ, код перевірки на парність з низькою щільністю/ код Бозе-ЧоудхуріХоквінгема). Вихід з перемежовувача 2 6 бітів подають в блок 2 8 відображень бітів на сукупність, який відображає групи бітів в точці сукупності, яку потрібно використовувати для передачі бітів кодованих даних. Виходи блоку 28 відображеннями бітів на сукупність є мітками на точках сукупності, які є дійсними і уявними компонентами. Мітки точки сукупності є символами даних, сформованими з двох або більше бітів, залежно від того, яка схема модуляції використовується. Вони називатимуться тут комірками даних. Ці комірки даних передають через перемежовувач ЗО за часом, робота якого полягає в перемежовуванні комірок даних, отриманих з багатьох кодових слів ППНЩ. Комірки даних приймають упоряджувач 32 фрейма, і ці комірки даних отримують на відгалуженні В і так далі, на Фіг. 1, через інші канали 31. Упоряджувач 32 фрейма потім формує велику кількість комірок даних у послідовності, які повинні бути передані по символах СОМЧР, 3 UA 99256 C2 де символи СОМЧР містять велику кількість комірок даних, і кожна комірка даних відображається на одну з піднесучих. Кількість піднесучих залежить від режиму роботи системи, перелік яких може включати один з поміж режимів 1k, 2k, 4k, 8k, 16k або 32k, для кожного з яких потрібна різна кількість піднесучих у відповідно, наприклад, до наступної таблиці: 5 Режим 1K 2K 4K 8K 16K 32K 10 15 20 25 30 35 40 45 50 Кількість піднесучих 756 1512 3024 6048 12096 24192 Кількість піднесучих, прийнята в ЦНТМ/М Таким чином, в одному прикладі кількість піднесучих для режиму 32k складає двадцять чотири тисячі сто дев'яносто дві. Для системи ЦНТМ2 кількість піднесучих на символ ОМЧР може змінюватися залежно від кількості пілотних та інших зарезервованих піднесучих. Таким чином, в ЦНТМ2, на відміну від ЦНТМ, кількість піднесучих для перенесення даних не фіксовано. Широкомовні станції можуть обирати один з наступних режимів роботи: 1k, 2k, 4k, 8k, 16k, 32k, кожен з яких забезпечує певний діапазон піднесучих даних на символ ОМЧР, при цьому максимум, доступний для кожного з цих режимів, складає 1024, 2048, 4096, 8192, 16384, 32768, відповідно. У ЦНТМ2 фрейм фізичного рівня складається з великої кількості символів ОМЧР. Зазвичай фрейм починається з однієї або більше преамбули або Р2 символів ОМЧР, після яких слідує деяка кількість символів ОМЧР, які несуть корисне навантаження. Кінець фрейма фізичного рівня помічений символами, які замикають фрейм. Для кожного режиму роботи кількість піднесучих може відрізнятися для кожного типу символів. Крім того, вона може змінюватися для кожного з них, залежно від того, чи обрано розширення смуги пропускання; чи дозволено деяке резервування тону і відповідно до чого була обрана структура пілотних піднесучих. При цьому узагальнення конкретної кількості піднесучих на символ ОМЧР є важко здійсненним. Проте перемежовувач частоти для кожного режиму може перемежовувати будьякий символ, кількість піднесучих якого є меншою або рівною максимально доступній кількості піднесучих для даного режиму. Наприклад, в режимі 1k, перемежовувач може працювати для символів з кількістю піднесучих, меншою або рівною 1024, і для режиму 16k з кількістю піднесучих, меншою або рівною 16384. Послідовність комірок даних, які переносяться в кожному символі КОМЧР, потім передають в перемежовувач 33 символу. Символ КОМЧР потім генерують за допомогою блоку 37 упоряджувача символу КОМЧР, який вводить пілотні сигнали і сигнали синхронізації, які подаються з формувача 36 пілотного і впровадженого сигналу. Модулятор 38 ОМЧР потім формує символ ОМЧР в області часу, який передає в процесор 4 0 вставки захисту для генерування інтервалу захисту між символами, і потім в цифровий і аналоговий перетворювач 42 і, нарешті, в підсилювач радіочастоти в блоці 4 4 попередньої обробки RF (РЧ, радіочастотної) для передачі, зрештою, передавачем КОМЧР через антену 46. Надання режиму 32k Для формування нового режиму 32k повинні бути визначені, наприклад, декілька елементів, один з яких є перемежовувачем 33 символу 32k. Блок 28 відображень біта на сукупність, перемежовувач 33 символу і упоряджувач 32 фрейма детальніше показаний на Фіг. 2. Як пояснювалося вище, даний винахід забезпечує можливість надання квазіоптимального відображення символів даних на сигнали піднесучої ОМЧР. Відповідно до зразкової технології, передбачений перемежовувач символів, який виконує оптимальне відображення символів вхідних даних на сигнали КОМЧР, піднесучої, відповідно до коду перестановки і полінома генератора, який був перевірений шляхом аналізу за допомогою моделювання. На Фіг. 2 представлена докладніша приблизна ілюстрація блоку 28 відображень біта на сукупність символу і упоряджувача 32 фрейма для ілюстрації зразкового варіанту втілення даної технології. Біти даних, прийняті з перемежовувача 2 6 бітів через канал 62, групують в набори бітів, які необхідно відобразити на комірку даних, відповідно до кількості бітів на символ, передбаченої схемою модуляції. Групи бітів, які формують слово даних, подають паралельно через канали 64 передачі даних в процесор 66 відображень. Процесор 66 відображень потім обирає один з символів даних, відповідно до заздалегідь призначеного відображення. Точка сукупності представлена дійсними і уявними компонентами, які подаються у вхідний канал 2 9, як один з наборів вхідних даних для упоряджувача 32 фрейма. 4 UA 99256 C2 5 10 15 20 25 30 35 40 45 50 55 Упоряджувач 32 фрейма приймає комірки даних з блоку 28 відображень біта на сукупність через канал 2 9 разом з комірками даних з інших каналів 31. Після побудови фрейма з великої кількості послідовностей комірок КОМЧР, комірку кожного символу КОМЧР потім записують в запам'ятовуючий пристрій 100 перемежовувача і зчитують з запам'ятовуючого пристрою 100 перемежовувача, відповідно до адрес запису і адрес зчитування, які генеруються генератором 102 адреси. Відповідно до порядку запису і зчитування отримують перемежовування комірок даних шляхом генерування відповідних адрес. Робота генератора 102 адреси і запам'ятовуючого пристрою 100 перемежовувача будуть детальніше описані нижче, з посиланням на Фіг. З, 4 і 5. Комірки даних після перемежовування потім комбінують з пілотними символами і символами синхронізації, прийнятими з формувача 36 пілотного і впровадженого сигналу в упоряджувачі 37 символів ОМЧР, для формування символу КОМЧР, який подають в модулятор 38 ОМЧР, як це пояснювалося вище. Перемежовувач На Фіг. 3 подано приклад частин перемежовувача 33 символів, який ілюструє дану технологію перемежовування символів. На Фіг. З комірки вхідних даних з упоряджувача 32 фрейма записують в запам'ятовуючий пристрій 100 перемежовувача. Комірки даних записують в запам'ятовуючий пристрій 100 перемежовувача відповідно до адреси запису яка надходить з генератора 102 адреси по каналу 104, і зчитують з запам'ятовуючого пристрою 100 перемежовувача, відповідно до зчитаної адреси, поданої з генератора 102 адреси по каналу 106. Генератор 102 адреси генерує адресу запису і адресу зчитування, як пояснюється нижче, залежно від того, чи є символ КОМЧР непарним або парним, що ідентифікується за сигналом, який подається з каналу 108, і залежно від обраного режиму, який ідентифікують за сигналом, який надходить із каналу 110. Як пояснювалося вище, режим може бути одним з поміж режиму Ik, режиму 2к, режиму 4к, режиму 8к, режиму Ібк або режиму 32к. Як пояснюється нижче, адресу запису і адресу зчитування генерують по-різному для парних і непарних символів ОМЧР, як пояснювалося відповідно до посилань на Фіг. 4, яка є прикладом втілення запам'ятовуючого пристрою 100 перемежовувача. У прикладі, показаному на Фіг. 4, запам'ятовуючий пристрій перемежовувача показаний як такий, що містить верхню частину 100, яка ілюструє роботу запам'ятовуючого пристрою перемежовувача в передавачі, і нижню частину 340, яка ілюструє роботу запам'ятовуючого пристрою перемежовувача в приймачі. Перемежовувач 100 і блок 34 0 усунення перемежовування показані разом на Фіг. 4, для наочності при описі їх роботи. Як показано на Фіг. 4, представлення зв'язку між перемежовувачем 100 і блоком 340 усунення перемежовування через інші пристрої і через канал передачі було спрощене і представлене як секція 140 між перемежовувачем 100 і блоком 340 усунення перемежовування. Робота перемежовувача 100 описана в наступних параграфах: Хоча на Фіг. 4 подано приклад тільки чотирьох комірок вхідних даних як приклад чотирьох сигналів піднесучої символу КОМЧР, слід розуміти, що методика, яка ілюструється на Фіг. 4, може бути поширена на більшу кількість піднесучих, наприклад, на 756 для режиму 1k, 1512 для режиму 2к, 3024 для режиму 4к і 6048 для режиму 8к, 12096 для режиму 16к і 24192 для режиму 32к. Вхідна і вихідна адресація запам'ятовуючого пристрою 100 перемежовувача показаного на Фіг. 4, представлені для парних і непарних символів. Для парних символів КОМЧР комірки даних відбирають із вхідного каналу 77 і записують в запам'ятовуючий пристрій перемежовувача 124.1, відповідно до послідовності адрес 120, яка згенерована для кожного символу КОМЧР за допомогою генератора 102 адрес. Адреси запису застосовують для парного символу таким чином, щоб, як це подано, перемежовування виконувалось шляхом перестановки адрес запису. Тому, для кожного символу після перемежовування y(h(q)) = у (q). Для непарних символів використовують той же запам'ятовуючий пристрій 124.2 перемежовувача. Проте, як показано на Фіг. 4, для непарних символів порядок 132 запису є тією ж послідовністю адрес, яка використовувалася для зчитування попереднього парного символу 12 6. Ця властивість дозволяє втілювати перемежовувач для парних і непарних символів так, що в ньому використовуватиметься тільки один запам'ятовуючий пристрій 100 перемежовувача, в якому передбачена операція зчитування, яка виконується для заданої адреси перед операцією запису. Комірки даних, записані в запам'ятовуючий пристрій 124 перемежовувача під час непарних символів, потім зчитують в послідовності 134, яка генерується генератором 102 адрес для наступного символу КОМЧР і так далі. Таким чином, генерують тільки одну адресу на символ, при цьому занесення в запам'ятовуючий пристрій, і зчитування із запам'ятовуючого пристрою, для непарних/парних символів КОМЧР виконують одночасно. 5 UA 99256 C2 Загалом, як представлено на Фіг. 4, після того, як буде розрахований набір адрес H(q) для 5 10 15 20 25 30 35 40 45 50 55 0 2 Nmax -1, ) обробляють для отримання всіх активних піднесучих, вхідний вектор Y = ( y , y1, y ...y вектора Y = (y0, y1, y2…yNmax-1) перемежовування, визначеного за: yH(q) = y'q для парних символів для q = 0…, Nmax-1 yq = y'H(q) для непарних символів для q = 0,.., Nmax-1 Іншими словами, для парних символів ОМЧР вхідні слова записують із перестановкою в запам'ятовуючий пристрій, і послідовно зчитують, тоді як для непарних символів, їх записують послідовно і зчитують із перестановкою. У описаному вище випадку перестановка H(q) визначена наступною таблицею: Таблиця 1: перестановка для простого випадку, коли Nmax=4 Як показано на Фіг. 4, блок 340 усунень перемежовування під час роботи виконує обробку, зворотну обробці перемежовування, яка застосовується в перемежовувачі 100, застосовуючи той же набір адрес, який був згенерований еквівалентним генератором адреси, але застосовуючи адреси запису в запам'ятовуючий пристрій, і зчитування із запам'ятовуючого пристрою, в зворотному порядку. При цьому, для парних символів, адреси 342 запису в запам'ятовуючий пристрій, є порядком надходження, тоді як адреси 34 4 зчитування із запам'ятовуючого пристрою, надаються генератором адрес. Відповідно до цього, для непарних символів, порядок 34 6 записів в запам'ятовуючий пристрій визначений за набором адрес, який було згенеровано генератором адрес, тоді як зчитування 348 із запам'ятовуючого пристрою, є порядком надходження. Генерування адреси для режиму 32k Блок-схема алгоритму, який використовується для генерування функції H(q) перестановки, представлена на Фіг. 5 для режиму 32k. Варіант втілення генератора 102 адреси для режиму 32k показаний на Фіг. 5. На Фіг. 5 лінійний регістр зсуву регістр із зворотним зв'язком сформований за допомогою тринадцяти каскадів 200 регістра і логічного елементу 202 "виключаюче АБО" (хоr), який з'єднаний із каскадами регістра зсуву 200 відповідно до полінома генератора. Тому, відповідно до вмісту регістра зсуву 200, наступний біт регістра зсуву буде отриманий на виході логічного елементу 202 "виключаючого АБО", в результаті застосування операції "виключаючого АБО" до вмісту регістрів зсуву R[0], R[lb R[2], R[12], відповідно до полінома генератора: R12 R10 R11 R14 R15 R19 R111 i i i i i i i Відповідно до полінома генератора псевдовипадкову послідовність бітів генерують із вмісту регістра зсуву 200. Проте, для генерування адреси для режиму 32k, як представлено на кресленні, передбачена схема 210 перестановок, яка виконує ефективну перестановку порядку бітів в межах регістра зсуву 200.1 з порядку R'i[n] в порядок Rj [n] на виході схеми 210 перестановок. Чотирнадцять бітів з виходу схеми 210 перестановок потім подають відповідним каналом 212, до якого додають старший значущий біт через канал 214, який наданий блоком 218 перемикача. Тому адресу п'ятнадцятого біта генерують каналом 212. Проте, для забезпечення автентичності адреси, схема 216 перевірок адреси аналізує адресу, яка була згенерована, визначаючи чи не перевищує вона задане максимальне значення. Задане максимальне значення може відповідати максимальній кількості сигналів піднесучих, які доступні для символів даних в символі КОМЧР, доступному для режиму, в якому його використовують. Проте перемежовувач для режиму 32k також можна використовувати для інших режимів, таким чином генератор 102 адреси також можна використовувати для режиму 2к, режиму 4к, режиму 8к режиму 16к і режиму 32к, з відповідним регулюванням максимальної дійсної адреси. Якщо згенерована адреса перевищує задане максимальне значення, тоді генерують сигнал керування за допомогою модуля 216 перевірок адреси і подають через відповідний канал 220 в модуль 224 керування. Якщо згенерована адреса перевищує задане максимальне значення, тоді цю адресу відкидають, і генерують нову адресу для конкретного символу. Для режиму 32k (Nr-1) бітове слово R'i(-1) визначають при Nr=log2 Mmax, де Mmax, = 332768 при використанні LFSR (ЛРЗЗ, лінійний регістр зсуву із зворотним зв'язком). Поліномами, які використовуються для генерування цієї послідовності, є: i i i i i Режим 32k: R13 R10 R11 R12 R112 де і змінюється від 0 до Мmах-1 6 UA 99256 C2 Після того, як одне слово R'i буде згенерованим, це слово R'i зазнає обробки перестановкою для отримання іншого бітового слова (Nr-1), яке називається Ri. Слово Ri отримують із R'i шляхом перестановки бітів, яка представлена таким чином: Положення бітів R'і Положення бітів Ri 13 6 12 5 11 0 10 10 9 8 8 1 7 11 6 12 5 2 4 9 3 4 2 3 1 13 0 7 5 Перестановка бітів для режиму 32k Наприклад, це означає, що для режиму 32k, номер 12 біта R'i передають в положенні біта номер 5 для Ri. Адресу H(q) потім отримують із Ri, використовуючи наступне рівняння: Hg i mod2 2Nr 1 10 Nr 1 Ri j 2 j j0 Nr 1 15 20 25 Частина (і mod2) 2 в приведеному вище рівнянні представлена на Фіг. 5 за допомогою блоку Т 218 перемикача. Перевірку адрес потім виконують за H(q) перевіряючи, чи знаходиться згенерована адреса в межах діапазону прийнятних адрес: якщо (H(q)< Nmax), де Nmax=24192, наприклад, в режимі 32k, тоді адреса є дійсною. Якщо адреса не є дійсною, модуль керування інформують про це, і він намагається згенерувати новий H(q), послідовно збільшуючи індекс і. Роль блоку перемикання полягає в тому, щоб адреса, яка перевищує Nmax, не була присутньою двічі в ряду. Ефект цей полягає в тому, що якщо буде згенероване перевищуюче значення, це означає, що MSB (СЗБ, старший значущий біт) (тобто, біт перемикання) адреси H(q) дорівнює одиниці. Таким чином, наступне згенероване значення матиме СЗБ, встановлений рівним нулю, що забезпечує отримання дійсної адреси. Наступні рівняння підсумовують загальну поведінку і допомагають зрозуміти циклічну структуру цього алгоритму: q=0; for (і = 0; і < Мmax; і = і +1) Hg i mod2 2 Nr 1 30 35 40 Ri j 2 j j0 dD dD i 50 { if(H(q)

ДивитисяДодаткова інформація

Назва патенту англійськоюData processing apparatus and method

Автори англійськоюTaylor Matthen Paul Athol, Atungsiri Samuel Asanberg

Назва патенту російськоюУстройство и способ обработки данных

Автори російськоюТейлор Метью Пол Атол, Атунгсири Семюель Асанбенг

МПК / Мітки

МПК: G06F 12/02

Мітки: даних, пристрій, спосіб, обробки

Код посилання

<a href="https://ua.patents.su/21-99256-pristrijj-ta-sposib-obrobki-danikh.html" target="_blank" rel="follow" title="База патентів України">Пристрій та спосіб обробки даних</a>

Попередній патент: Самохідна сільськогосподарська робоча машина

Наступний патент: Спосіб одержання 3-заміщених 2-аміно-5-галогенбензамідів

Випадковий патент: Штифт для випалювання виробів на стільникових підставках