Буферний каскад

Номер патенту: 22794

Опубліковано: 25.04.2007

Автори: Азаров Олексій Дмитрович, Лукащук Олександр Олександрович, Богомолов Сергій Віталійович, Крупельницький Леонід Віталійович

Формула / Реферат

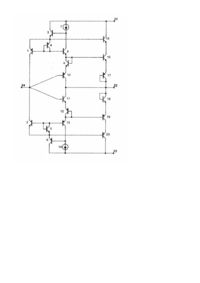

Буферний каскад, який містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п’ятого транзисторів, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, базу і колектор дев'ятого транзистора з'єднано з базою третього транзистора, а також з емітером першого транзистора, базу і колектор десятого транзистора з'єднано з базою шостого транзистора, колектор першого транзистора з'єднано з першим виводом першого джерела струму, другі виводи першого і другого джерела струму, а також колектори другого і сьомого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шестого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази та колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що у нього додатково введено тринадцятий, чотирнадцятий, п'ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий транзистори, причому колектори тринадцятого і чотирнадцятого транзисторів об'єднано та з'єднано з вхідною шиною, а також з базами четвертого і п'ятого транзисторів, бази тринадцятого і чотирнадцятого транзисторів з'єднано з базами та колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами першого і восьмого транзисторів відповідно, емітери тринадцятого і чотирнадцятого транзисторів з'єднано з емітерами п'ятнадцятого, сімнадцятого та шістнадцятого, вісімнадцятого транзисторів відповідно, а також з базами другого і сьомого транзисторів відповідно, колектори п'ятнадцятого і шістнадцятого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, бази п'ятнадцятого і шістнадцятого транзисторів з'єднано з першими виводами першого і другого джерела струму відповідно, а також з колекторами першого і восьмого транзисторів відповідно, емітер восьмого транзистора з'єднано з базою та колектором десятого транзистора, а також з базою шостого транзистора, колектори четвертого і п'ятого транзисторів об'єднано та з'єднано з базою та колектором одинадцятого і дванадцятого транзисторів, а також з вихідною шиною.

Текст

Корисна модель відноситься до вимірювальної техніки і може бути використана в аналогово-цифрових перетворювачах і цифрових вимірювальних приладах. Відомо буферний пристрій [Бахтиаров Г.Д., Малинин В.В., Школин В.П. Аналого-цифровые преобразователи / Под ред. Г.Д. Бахтиарова. - М.: Советское радио, 1980. - 280 с. ил. Рис. 6.28 на стр. 150.], який містить вісім транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та ви хідну шини. Бази четвертого та п'ятого транзисторів з'єднано з вхідною шиною. Емітери четвертого та п'ятого транзисторів з'єднано з емітерами першого та восьмого транзисторів відповідно, та з базами третього та шостого транзисторів відповідно, колектори четвертого та п'ятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами сьомого та другого транзисторів відповідно. Бази і колектори першого і восьмого транзисторів з'єднано з базами другого та сьомого транзисторів відповідно, а також з'єднано з шинами додатного та від'ємного живлення через перше та друге джерела струму відповідно. Колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно. Емітери третього та шостого транзисторів з'єднано з вихідною шиною. Основним недоліком цього пристрою є низька точність, що викликано значною вихідною напругою зміщення нуля через неідентичність параметрів пар n – р - n та р – n - р транзисторів у верхньому та нижньому каналах. За прототип обрано буферний пристрій [Д.п. № 15896 НОЗК 5/22, G05B 1/00, 2006], який містить вісім транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та ви хідну шини, причому вхідн у шину з'єднано з базами четвертого та п'ятого транзисторів, колектори яких з'єднано з колекторами шостого та третього транзисторів відповідно, та емітерами сьомого та другого транзисторів відповідно, база та колектор першого транзистора об'єднані і приєднані до шини додатного живлення через перше джерело струму, а також до бази другого транзистора, база сьомого транзистора з'єднана з шиною від'ємного живлення через друге джерело струму, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, відрізняється тим, що у нього введено дев'ятий, десятий, одинадцятий, дванадцятий транзистори, причому база кожного з них з'єднана з його колектором, емітер восьмого транзистора з'єднано з базою сьомого транзистора та першим виводом другого джерела струму, емітери дев'ятого та десятого транзисторів з'єднано з емітерами четвертого та п'ятого транзисторів відповідно, бази та колектори дев'ятого та десятого транзисторів з'єднано з базами третього та шостого транзисторів відповідно, а також базу та колектор дев'ятого транзистора з'єднано з емітером першого транзистора, базу та колектор десятого транзистора з'єднано з базою та колектором восьмого -транзистора, емітери третього та шостого транзисторів з'єднано з емітерами одинадцятого та дванадцятого транзисторів відповідно, бази і колектори одинадцятого та дванадцятого транзисторів з'єднано з вихідною шиною. Недоліками прототипу є низька точність роботи схеми, яка обумовлена великим рівнем вхідного стр уму зміщення, а також велика споживана потужність, що споживається від джерел напруги живлення. В основу корисної моделі поставлено задачу створення буферного каскаду, в якому за рахунок введення нових елементів та зв'язків між ними зменшується вхідний стр ум зміщення, завдяки чому підвищується точність роботи, а також зменшення споживаної потужності. Поставлена задача досягається тим, що в буферний пристрій, який містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідн у шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери четвертого і п'ятого транзисторів з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, базу і колектор дев'ятого транзистора з'єднано з базою третього транзистора, а також з емітером першого транзистора, базу і колектор десятого транзистора з'єднано з базою шостого транзистора, колектор першого транзистора з'єднано з першим виводом першого джерела струму, другі виводи першого і другого джерела струму, а також колектори другого і сьомого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази та колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, введено тринадцятий, чотирнадцятий, п'ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий транзистори, причому колектори тринадцятого і чотирнадцятого транзисторів об'єднано та з'єднано з вхідною шиною, а також з базами четвертого і п'ятого транзисторів, бази тринадцятого і чотирнадцятого транзисторів з'єднано з базами та колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами першого і восьмого транзисторів відповідно, емітери тринадцятого і чотирнадцятого транзисторів з'єднано з емітерами п'ятнадцятого, сімнадцятого, та шістнадцятого, вісімнадцятого транзисторів відповідно, а також з базами другого і сьомого транзисторів відповідно, колектори п'ятнадцятого і шістнадцятого транзисторів з'єднано з шинами додатного і від'ємного живлення відповідно, бази п'ятнадцятого І шістнадцятого транзисторів з'єднано з першими виводами першого і другого джерела струму відповідно, а також з колекторами першого і восьмого транзисторів відповідно, емітер восьмого транзистора з'єднано з базою та колектором десятого транзистора, а також з базою шостого транзистора, емітери четвертого і п'ятого транзисторів об'єднано та з'єднано з базою та колектором одинадцятого і дванадцятого транзисторів, а також з вихідною шиною. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 24, яку з'єднано з колекторами тринадцятого 1 і чотирнадцятого 2 транзисторів, а також з базами четвертого 10 і п'ятого 11 транзисторів, бази тринадцятого 1 і чотирнадцятого 2 транзисторів з'єднано з базами та колекторами сімнадцятого 4 і вісімнадцятого 5 транзисторів відповідно, а також з базами першого 8 і восьмого 13 транзисторів відповідно, емітери тринадцятого 1 і чотирнадцятого 2 транзисторів з'єднано з емітерами п'ятнадцятого З, сімнадцятого 4 та шістнадцятого 6, вісімнадцятого 5 транзисторів відповідно, а також з базами другого 15 і сьомого 20 транзисторів відповідно, бази п'ятнадцятого 3 і шістнадцятого 6 транзисторів з'єднано з першими виводами першого 7 і другого 14 джерел струму відповідно, а також з колекторами першого 8 і восьмого 13 транзисторів відповідно, колектор п'ятнадцятого 3 і другого 15 транзисторів, а також другий вивід першого джерела струму 7 з'єднано з шиною додатного живлення 21, колектори шістнадцятого 6 і сьомого 20 транзисторів, а також другий вивід другого джерела струму 14 з'єднано з шиною від'ємного живлення 23, емітери першого 8 і восьмого 13 транзисторів з'єднано з базами та колекторами дев'ятого 9 і десятого 12 транзисторів відповідно, а також з базами третього 16 і шостого 19 транзисторів відповідно, емітери дев'ятого 9 і десятого 12 транзисторів з'єднано з емітерами четвертого 10 і п'ятого 11 транзисторів відповідно, емітери другого 15 і сьомого 20 транзисторів з'єднано з колекторами третього 16 і шостого 19 транзисторів відповідно, емітери третього 16 і шостого 19 транзисторів з'єднано з емітерами одинадцятого 17 і дванадцятого 18 транзисторів відповідно, колектори четвертого 10 і п'ятого 11 транзисторів об'єднано та з'єднано з базами та колекторами одинадцятого 17 і дванадцятого 18 транзисторів, а також з вихідною шиною 22. Буферний каскад працює таким чином: якщо напруга на вхідній шині 24 збільшується, то потенціал емітерів четвертого 10 і дев'ятого 9 транзисторів, а також п'ятого 11 і десятого 12 транзисторів збільшується. При цьому потенціал емітерів третього 16 і шостого 19 транзисторів, а також колекторів одинадцятого 17 і дванадцятого 18 транзисторів збільшується. У цьому випадку напруга на вихідній шині 22 збільшується пропорційно збільшенню напруги на вхідній шині 24. Якщо напруга на вхідній шині 24 зменшується, то потенціал емітерів четвертого 10 і дев'ятого 9 транзисторів, а також п'ятого 11 і десятого 12 транзисторів зменшується. При цьому потенціал емітерів третього 16 і шостого 19 транзисторів, а також колекторів одинадцятого 17 і дванадцятого 18 транзисторів зменшується. У цьому випадку напруга на ви хідній шині 22 зменшується пропорційно зменшенню напруги на вхідній шині 24. Зменшення похибки передачі вхідної напруги на вихід схеми досягається компенсацією базових струмів четвертого 10 і п'ятого 11 транзисторів. Для цього у схему вводяться перший 8 і восьмий 13 транзистори, які є давачами базових струмів, у базове коло першого 8 транзистора вводиться відбивач струму на тринадцятому 1 і сімнадцятому 4 транзисторах, а в базове коло восьмого 13 транзистора вводиться відбивач струму на чотирнадцятому 2 і вісімнадцятому 5 транзисторах. При цьому значення вхідного струму зміщення: Iвх = Iб10 - Iб11 + I k1 – I k2 , де Iб10, Iб 11- базові струми транзисторів 10 та 11 відповідно, Ik1 , I k2 - колекторні струми транзисторів 1 та 2 відповідно. Якщо коефіцієнт передачі по струму b першого 8, четвертого 10, п'ятого 11, восьмого 13 транзисторів однакові, Ik1 » Iб8, I k2 » Iб13 де Iб8, Iб13 стр уми транзисторів 8 та 13 відповідно. Таким чином вхідне значення струму зміщення наближається до нуля. Другою складовою похибки передачі є залежність емітерних струмів четвертого 10 і п'ятого 11 транзисторів від значень базових струмів другого 15 і сьомого 20 транзисторів відповідно, які змінюються під час зміни напруги живлення. Для зменшення складової цієї похибки у схему введені емітерні повторювачі на п'ятнадцятому 3 і шістнадцятому 6 транзисторах відповідно. Зменшення енергоспоживання в схемі досягається об'єднанням колекторів четвертого 10 і п'ятого 11 транзисторів та підключенням до виходу схеми. U+ л. = U- л. I = Iзм2 жив жив В схемі прототипу, якщо зм1 та , Iзм1 , Iзм2 - стр уми зміщення першого 7 та другого 14 джерел струмів відповідно, U+ л. , U- л. - напруги шин додатного 21 та від'ємного 23 живлення жив жив відповідно. Таким чином споживана потужність для винаходу: ' Pсn = 2U живл × 2Ізм Для прототипу споживана потужність: " Pcn = 2Uживл × 3Ізм ' " де Pсn , Pcn - споживані потужності винаходом і прототипом відповідно, Ізм - струм зміщення. Множники при Uживл позначають кількість джерел живлення, а множники при Ізм - кількість каскадів схеми.

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych, Lukaschuk Oleksandr Oleksandrovych, Krupelnytskyi Leonid Vitaliiovych

Назва патенту російськоюБуферный каскад

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич, Лукащук Александр Александрович, Крупельницкий Леонид Витальевич

МПК / Мітки

МПК: H03F 3/26

Код посилання

<a href="https://ua.patents.su/3-22794-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Спосіб одержання циклопентадієну

Наступний патент: Вібраційний високочастотний пристрій для розвантаження і очищення кузовів автомобілів-самоскидів

Випадковий патент: Вимірювач об'єму круглих лісоматеріалів