Буферний каскад

Номер патенту: 21553

Опубліковано: 15.03.2007

Автори: Азаров Олексій Дмитрович, Богомолов Сергій Віталійович, Лукащук Олександр Олександрович

Формула / Реферат

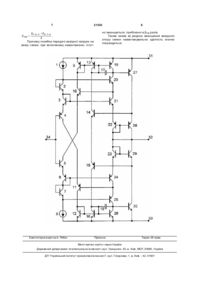

Буферний каскад, що містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери яких з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, базу і колектор дев'ятого транзистора з'єднано з базою третього транзистора, а також з емітером першого транзистора, базу і колектор десятого транзистора з'єднано з базою і колектором восьмого транзистора, а також з базою шостого транзистора, базу і колектор першого транзистора з'єднано з базою другого транзистора та шиною додатного живлення через перше джерело струму, емітер восьмого транзистора з'єднано з базою сьомого транзистора та з шиною від'ємного живлення через друге джерело струму, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що у нього введено тринадцятий, чотирнадцятий, п'ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий, дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий, двадцять третій, двадцять четвертий, двадцять п'ятий, двадцять шостий транзистори, перший і другий конденсатори, причому емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з колекторами п'ятого і четвертого транзисторів відповідно, їх бази з'єднано з емітерами другого і сьомого транзисторів відповідно, а також колекторами третього і шостого транзисторів відповідно, їх колектори з'єднано з базами і колекторами тринадцятого, сімнадцятого та чотирнадцятого, вісімнадцятого транзисторів відповідно, а також з базами двадцять першого і двадцять другого транзисторів відповідно, а також з колекторами дев'ятнадцятого і двадцятого транзисторів відповідно та з першими виводами першого і другого конденсаторів відповідно, другі виводи першого і другого конденсаторів з'єднано з колекторами другого, двадцять першого та сьомого, двадцять другого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з емітерами двадцять п'ятого і двадцять шостого транзисторів відповідно, а також з базами дев'ятнадцятого і двадцятого транзисторів відповідно, емітери дев'ятнадцятого і двадцятого транзисторів об'єднано, емітери тринадцятого, сімнадцятого, двадцять першого, двадцять третього транзисторів з'єднано з шиною додатного живлення, емітери чотирнадцятого, вісімнадцятого, двадцять другого, двадцять четвертого транзисторів з'єднано з шиною від'ємного живлення, бази і колектори двадцять п'ятого і двадцять шостого транзисторів об'єднано та з'єднано з базами і колекторами одинадцятого і дванадцятого транзисторів, а також з вихідною шиною.

Текст

Буферний каскад, що містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери яких з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, базу і колектор дев'ятого транзистора з'єднано з базою третього транзистора, а також з емітером першого транзистора, базу і колектор десятого транзистора з'єднано з базою і колектором восьмого транзистора, а також з базою шостого транзистора, базу і колектор першого транзистора з'єднано з базою другого транзистора та шиною додатного живлення через перше джерело струму, емітер восьмого транзистора з'єднано з базою сьомого транзистора та з шиною від'ємного живлення через друге джерело струму, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, який відрізняється тим, що у нього введено тринадцятий, чотирнадцятий, п'ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий, дев'ятнадцятий, двадцятий, двадцять перший, двадцять U 2 UA 1 3 21553 лення, вхідн у та ви хідну шини. Бази четвертого та п'ятого транзисторів з'єднано з вхідною шиною. Емітери четвертого та п'ятого транзисторів з'єднано з емітерами першого та восьмого транзисторів відповідно, та з базами третього та шостого транзисторів відповідно, колектори четвертого та п'ятого транзисторів з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами сьомого та другого транзисторів відповідно. Бази і колектори першого і восьмого транзисторів з'єднано з базами другого та сьомого транзисторів відповідно, а також з'єднано з шинами додатного та від'ємного живлення через перше та друге джерела струму відповідно. Колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно. Емітери третього та шостого транзисторів з'єднано з вихідною шиною. Основним недоліком аналогу є низька точність, яка обумовлена наявністю вихідної напруги зміщення нуля через неідентичність параметрів пар n-р-n та р-n-р транзисторів у верхньому та нижньому каналах. За прототип обрано буферний пристрій [Д.п. №15896 Н03К5/22, G05B1/00, 2006], який містить дванадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідн у та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери яких з'єднано з емітерами дев'ятого та десятого транзисторів відповідно, а колектори їх з'єднано з колекторами шостого та третього транзисторів відповідно, а також з емітерами сьомого та другого транзисторів відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднані, та з'єднані з базами третього та шостого транзисторів відповідно, крім того база і колектор дев'ятого транзистора з'єднана з емітером першого транзистора, а база і колектор десятого транзистора з'єднана з базою і колектором восьмого транзистора, базу і колектор першого транзистора з'єднано з базою другого транзистора та з шиною додатного живлення через перше джерело струму, емітер восьмого транзистора з'єднано з базою сьомого транзистора та з шиною від'ємного живленням через друге джерело струму, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення відповідно, емітери третього та шостого транзисторів з'єднано з емітерами одинадцятого та дванадцятого транзисторів відповідно, бази та колектори одинадцятого та дванадцятого транзисторів з'єднано з вихідною шиною. Недоліками прототипу є низька навантажувальна здатність, яка обумовлена підвищеним опором схеми, що призводить до збільшення похибки коефіцієнта передачі при підключенні навантаження до виходу схеми. В основу корисної моделі поставлено задачу створення буферного каскаду, в якому за рахунок введення нових елементів та зв'язків між ними зменшується вихідний опір, завдяки чому підвищується навантажувальна здатність та зменшується похибка коефіцієнта передачі. Поставлена задача досягається тим, що в буферний пристрій, який містить дванадцять транзи 4 сторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами четвертого та п'ятого транзисторів, емітери яких з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, базу і колектор дев'ятого транзистора з'єднано з базою третього транзистора, а також з емітером першого транзистора, базу і колектор десятого транзистора з'єднано з базою і колектором восьмого транзистора, а також з базою шостого транзистора, базу і колектор першого транзистора з'єднано з базою другого транзистора та шиною додатного живлення через перше джерело струму, емітер восьмого транзистора з'єднано з базою сьомого транзистора та з шиною від'ємного живлення через друге джерело струму, емітери другого і сьомого транзисторів з'єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з'єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази і колектори одинадцятого і дванадцятого транзисторів з'єднано з вихідною шиною, введено тринадцятий, чотирнадцятий, п'ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий, дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий, двадцять третій, двадцять четвертий, двадцять п'ятий, двадцять шостий транзистори, перший і другий конденсатори, причому емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з колекторами п'ятого і четвертого транзисторів відповідно, їх бази з'єднано з емітерами другого і сьомого транзисторів відповідно, а також колекторами третього і шостого транзисторів відповідно, їх колектори з'єднано з базами і колекторами тринадцятого, сімнадцятого та чотирнадцятого, вісімнадцятого транзисторів відповідно, а також з базами двадцять першого і двадцять другого транзисторів відповідно, а також з колекторами дев'ятнадцятого і двадцятого транзисторів відповідно та з першими виводами першого і другого конденсаторів відповідно, другі виводи першого і другого конденсаторів з'єднано з колекторами другого, двадцять першого та сьомого, двадцять другого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з емітерами двадцять п'ятого і двадцять шостого транзисторів відповідно, а також з базами дев'ятнадцятого і двадцятого транзисторів відповідно, емітери дев'ятнадцятого і двадцятого транзисторів об'єднано, емітери тринадцятого, сімнадцятого, двадцять першого, двадцять третього транзисторів з'єднано з шиною додатного живлення, емітери чотирнадцятого, вісімнадцятого, двадцять другого, двадцять четвертого транзисторів з'єднано з шиною від'ємного живлення, бази і колектори двадцять п'ятого і двадцять шостого транзисторів об'єднано та з'єднано з базами і колекторами одинадцятого і дванадцятого транзисторів, а також з вихідною шиною. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 34, яку з'єднано з базами четвертого 4 та п'ятого 5 транзисторів, 5 21553 емітери яких з'єднано з емітерами дев'ятого 3 і десятого 6 транзисторів відповідно, їх колектори з'єднано з емітерами шістнадцятого 11 і п'ятнадцятого 10 транзисторів відповідно, базу і колектор дев'ятого 3 транзистора з'єднано з базою третього 21 транзистора, а також з емітером першого 2 транзистора, базу і колектор десятого 6 транзистора з'єднано з базою і колектором восьмого 7 транзистора, а також з базою шостого 24 транзистора, базу і колектор першого 2 транзистора з'єднано з базою другого 20 транзистора та шиною додатного живлення 31 через перше джерело струму 1, емітер восьмого 7 транзистора з'єднано з базою сьомого 25 транзистора та з шиною від'ємного живлення 33 через друге джерело струму 8, бази п'ятнадцятого 10 і шістнадцятого 20 транзисторів з'єднано з емітерами другого 20 і сьомого 25 транзисторів відповідно, а також з колекторами третього 21 і шостого 24 транзисторів відповідно, емітери третього 21 і шостого 24 транзисторів з'єднано з емітерами одинадцятого 22 і дванадцятого 23 транзисторів відповідно, колектори п'ятнадцятого 10 і шістнадцятого 11 транзисторів з'єднано з базами і колекторами тринадцятого 9, сімнадцятого 13 та чотирнадцятого 12, вісімнадцятого 16 транзисторів відповідно, а також з базами двадцять першого 19 і двадцять другого 26 транзисторів відповідно, а також з колекторами дев'ятнадцятого 14 і двадцятого 15 транзисторів відповідно та з першими виводами першого 17 і другого 18 конденсаторів відповідно, другі виводи першого 17 і другого 18 конденсаторів з'єднано з колекторами другого 20, двадцять першого 19 та сьомого 25, двадцять другого 26 транзисторів відповідно, а також з базами двадцять третього 27 і двадцять четвертого 30 транзисторів відповідно, колектори двадцять третього 27 і двадцять четвертого 30 транзисторів з'єднано з емітерами двадцять п'ятого 28 і двадцять шостого 29 транзисторів відповідно, а також з базами дев'ятнадцятого 14 і двадцятого 15 транзисторів відповідно, емітери дев'ятнадцятого 14 і двадцятого 15 транзисторів об'єднано, емітери тринадцятого 9, сімнадцятого 13, двадцять першого 19, двадцять третього 27 транзисторів з'єднано з шиною додатного живлення 31, емітери чотирнадцятого 12, вісімнадцятого 16, двадцять другого 26, двадцять четвертого 30 транзисторів з'єднано з шиною від'ємного живлення 33, бази і колектори двадцять п'ятого 28 і двадцять шостого 29 транзисторів об'єднано та з'єднано з базами і колекторами одинадцятого 22 і дванадцятого 23 транзисторів, а також з вихідною шиною 32. Буферний каскад працює таким чином: якщо напруга на вхідній шині 34 збільшується, то п'ятий транзистор 5 привідкривається, четвертий транзистор 4 призакривається, при цьому напруга на емітерах цих транзисторів збільшується, також відповідно збільшується напруга на емітерах третього 21 та шостого 24 транзисторів, що в свою чергу призводить до збільшення напруги на колекторах одинадцятого 22 та дванадцятого 23 транзисторів, які приєднані до вихідної шини 32 пристрою, тому напруга на ви хідній шині 32 також збільшується. Якщо напруга на вхідній шині 34 зменшується, 6 то п'ятий транзистор 5 призакривається, четвертий транзистор 4 привідкривається, при цьому напруга на емітерах цих транзисторів зменшується, також відповідно зменшується напруга на емітерах третього 21 та шостого 24 транзисторів, що в свою чергу призводить до зменшення напруги на колекторах одинадцятого 22 та дванадцятого 23 транзисторів, які приєднані до вихідної шини 32 пристрою, тому напруга на ви хідній шині 32 також зменшується. У запропонованому пристрої мають місце наступні співвідношення відповідно для верхнього та для нижнього каналів: U'в их = Uв х + Up -n- p + Un-p -n + Un -p -n + Up- n-p , бе 4 бе3 бе 21 бе 22 U"в их = Uв х - Un- p- n + Up-n -p + Up -n -p + Un -p- n . бе 5 бе 6 бе 24 бе 23 Враховуючи, що ΔUвих=Uвих-Uвх, для верхнього та для нижнього каналів отримуємо: DUв их = U"в их = Un-p -n - Un-p -n + Up -n -p - Up -n -p » 0B . бе бе бе бе Відбувається параметрична компенсація похибок статичної передатної характеристики. Другий 20 та сьомий 25 транзистори, які є каскодним каскадом, забезпечують постійну напругу на переходах колектор-емітер третього 21 та шостого 24 транзисторів і сприяють зменшенню впливу зміни напруг шин додатного 31 та від'ємного 33 живлення і підвищують швидкодію схеми. Збільшення навантажувальної здатності схеми здійснюється за рахунок введення до схеми додаткових підсилювальних каскадів на двадцять третьому 27 і двадцять четвертому 30, які включені в кола від'ємного зворотного зв'язку. Колектори двадцять третього 27 і двадцять четвертого 30 транзисторів підключено до емітерів двадцять п'ятого 28 і двадцять шостого 29 транзисторів відповідно, які працюють в діодному режимі, та підключено до струмової підвіски на дев'ятнадцятому 14 і двадцятому 15 транзисторах. Термін "підвіска" означає, що наскрізні колекторні струми дев'ятнадцятого 14 і двадцятого 15 транзисторів приблизно однакові і не залежать від вихідного струму схеми, який протікає в навантаженні. Колекторні струми дев'ятнадцятого 14 і двадцятого 15 транзисторів відповідно поступають на колектори сімнадцятого 13 і вісімнадцятого 16 транзисторів у діодному вмиканні, які разом з двадцять першим 19 і двадцять другим 26 транзисторами є струмовими дзеркалами. При цьому колекторні струми дев'ятнадцятого 14 і двадцятого 15 транзисторів відбиваються через колекторні кола двадцять першого 19 і двадцять другого 26 транзисторів і задають потрібний режим роботи по постійному струмові двадцять третього 27 і двадцять четвертого 30 транзисторів відповідно. Слід зауважити що колекторні струми одинадцятого 22, дванадцятого 23, дев'ятнадцятого 14, двадцятого 15 транзисторів будуть приблизно однаковими. Перший 17 та другий 18 конденсатори призначені коригування перехідної характеристики схеми. За рахунок дії зворотного зв'язку вихідний опір схеми в порівнянні з прототипом значно зменшується і сягає значення: (r + r ) || (re23 + re24 ) , rвих » e22 e21 bcep 7 b cep = bn -p -n + b p- n-p , 21553 2 Причому похибка передачі вихідної напруги на вихід схеми, при включеному навантаженні, істот Комп’ютерна в ерстка А. Рябко 8 но зменшується, приблизно в βсер разів. Таким чином за рахунок зменшення вихідного опору схеми навантажувальна здатність значно покращується. Підписне Тираж 26 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюIntermediate amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Lukaschuk Oleksandr Oleksandrovych, Bohomolov Serhii Vitaliiovych

Назва патенту російськоюПромежуточный усилитель

Автори російськоюАзаров Алексей Дмитриевич, Лукащук Александр Александрович, Богомолов Сергей Витальевич

МПК / Мітки

МПК: H03F 3/26

Код посилання

<a href="https://ua.patents.su/4-21553-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Спосіб лікування алкогольної залежності

Наступний патент: Спосіб передпосівної обробки насіння сої

Випадковий патент: Жилет