Однорозрядний суматор на мон транзисторах

Формула / Реферат

Однорозрядний суматор на МОН транзисторах, який має в своєму складі два навантажувальні транзистори і шість функціональних транзисторів, входи першого і другого операндів, вхід переноса та виходи суми і переноса, причому стоки першого і другого функціональних транзисторів з'єднані між собою і під'єднані до витоку третього, до заслонів четвертого і п'ятого функціональних транзисторів і до стоку першого навантажувального транзистора, витоки першого і п'ятого функціональних транзисторів з'єднані між собою і під'єднані до заслону другого функціонального транзистора і до входу першого операнда, заслон першого функціонального транзистора з'єднаний з витоком другого функціонального транзистора і під'єднаний до входу другого операнда, заслон третього функціонального транзистора з'єднаний з витоком четвертого функціонального транзистора і під'єднаний до входу переноса, стоки третього і четвертого функціональних транзисторів з'єднані між собою і під'єднані до стоку другого навантажувального транзистора і до виходу суми, стоки п'ятого і шостого функціональних транзисторів з'єднані між собою і під'єднані до виходу переноса, при цьому заслони і витоки першого і другого навантажувальних транзисторів під'єднані до шини живлення, який відрізняється тим, що додатково містить сьомий функціональний і третій навантажувальний транзистори, причому їх стоки з'єднані між собою і під'єднані до заслону шостого функціонального транзистора, витік якого з'єднаний зі входом переноса, витік сьомого функціонального транзистора під'єднаний до загальної шини, а його заслон з'єднаний з заслоном п'ятого функціонального транзистора, заслон і витік третього навантажувального транзистора під'єднані до шини живлення.

Текст

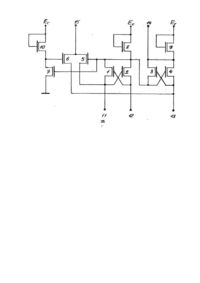

Винахід відноситься до обчислювальної техніки і може бути використаний для побудови обчислювальних вузлів в складі спеціалізованих ВІС на основі МОН транзисторів. Відомий однорозрядний суматор на МОН транзисторах, який має в своєму складі вісім функціональних і чотири навантажувальні транзистори [Авт. св. СРСР № 1357945. кл. G 06 F 7/50, опублік., 1987]. Реалізація даного однорозрядного суматора на МОН транзисторах вимагає значних апаратних витрат. Відомий однорозрядний суматор на МОН транзисторах, який складається з шести функціональних, трьох навантажувальних транзисторів та одного діода [Авт. св. СРСР №1432505, кл. G 06 F 7/50, опублік., 1988]. В даному однорозрядному суматорі, якщо на входах операндів встановлені сигнали різних рівнів, а на вході переносу присутній сигнал низького рівня, то на виході переноса зформується сигнал логічного нуля, рівний прямому падінню напруги на діоді. Також необхідно відмітити, що для формування вихідного сигналу переноса, вихід суми з'єднаний з заслоном одного з внутрішніх функціональних транзисторів. Даний взаємозв'язок збільшує ви хідну ємність і, відповідно, тривалість перехідних процесів на виході суми. Ці особливості побудови відомого однорозрядного суматора на МОН транзисторах знижують завадостійкість і надійність функціонування ВІС в цілому. Найбільш близьким до пропонованого є відомий однорозрядний суматор на МОН транзисторах, який має в своєму складі шість функціональних і два навантажувальні транзистори, входи першого і другого операндів, вхід переноса та виходи суми і переноса, причому стоки першого і другого функціональних транзисторів з'єднані між собою і під'єднані до витоку третього, до заслонів четвертого і п'ятого функціональних транзисторів і до стоку першого навантажувального транзистора, витоки першого і п'ятого функціональних транзисторів з'єднані між собою і під'єднані до заслону другого функціонального транзистора та до входу першого операнда, заслон першого функціонального транзистора з'єднаний з витоком другого функціонального транзистора і під'єднаний до входу другого операнда, заслон третього функціонального транзистора з'єднаний з витоком четвертого функціонального транзистора і під'єднаний до входу переноса, стоки третього і четвертого функціональних транзисторів з'єднані між собою і під'єднані до стоку другого навантажувального транзистора і до виходу суми, стоки п'ятого і шостого функціональних транзисторів з'єднані між собою і під'єднані до виходу переноса, при цьому заслони і витоки першого і другого навантажувальних транзисторів під'єднані до шини живлення [Авт. св. СРСР №1441387, кл. G 06 F 7/50, опублік., 1988]. Додатково у складі відомого однорозрядного суматора на МОН транзисторах для формування вихідного переносу використані два функціональні і один навантажувальний транзистор. При цьому, вихід суми з'єднаний з заслоном шостого функціонального транзистора. Даний взаємозв'язок збільшує ви хідну ємність виходу суми, що, в свою чергу, викликає збільшення часу протікання перехідних процесів на цьому виході. Таким чином інтегральна реалізація відомого однорозрядного суматора на МОН транзисторах вимагає вісім функціональних і три навантажувальні транзистори. В основу винаходу поставлене завдання створити однорозрядний суматор на МОН транзисторах, в якому нові елементи і взаємозв'язки дозволили б спростити формування вихідного переноса і, за рахунок цього, зменшити загальні апаратні витрати інтегральної реалізації приладу. Поставлене завдання досягається за рахунок того, що однорозрядний суматор на МОН транзисторах, який має в своєму складі шість функціональних транзисторів і два навантажувальні транзистори, входи першого і другого операндів, вхід переноса та виходи суми і переноса, причому стоки першого і другого функціонального транзисторів з'єднані між собою і під'єднані до витоку третього, до заслонів четвертого і п'ятого функціональних транзисторів і до стоку першого навантажувального транзистора, витоки першого і п'ятого функціональних транзисторів з'єднані між собою і під'єднані до заслону другого функціонального транзистора та до входу першого операнда, заслон першого функціонального транзистора з'єднаний з витоком другого функціонального транзистора і під'єднаний до входу другого операнда, заслон третього функціонального транзистора з'єднаний з витоком четвертого функціонального транзистора і під'єднаний до входу переноса, стоки третього і четвертого функціональних транзисторів з'єднані між собою і під'єднані до стоку другого навантажувального транзистора і до виходу суми, стоки п'ятого і шостого функціональних транзисторів з'єднані між собою і під'єднані до виходу переноса, при цьому заслони і витоки першого і другого навантажувальних транзисторів під'єднані до шини живлення, згідно винаходу, додатково містить сьомий функціональний і третій навантажувальний транзистори, причому їх стоки з'єднані між собою і під'єднані до заслону шостого функціонального транзистора, витік якого з'єднаний зі входом переноса, витік сьомого функціонального транзистора під'єднаний до загальної шини, а його заслон з'єднаний з заслоном п'ятого функціонального транзистора, заслон і витік третього навантажувального транзистора під'єднані до шини живлення. Введення нових взаємозв'язків і допоміжних елементів зменшило загальні апаратні витрати інтегральної реалізації однорозрядного суматора на МОН транзисторах на один функціональний транзистор, в порівнянні з відомим пристроєм, за рахунок спрощення алгоритму формування значення вихідного переносу: якщо рівні вхідних операндів однакові, то значення вихідного переносу співпадає зі значенням одного з операндів, в іншому випадку, вихідний перенос рівний вхідному. На кресленні представлена принципова електрична схема запропонованого однорозрядного суматора на МОН транзисторах. Однорозрядний суматор на МОН транзисторах має, в своєму складі сім 1...7 функціональних і три 8...10 навантажувальні транзистори, входи першого 11 і другого 12 операндів, вхід переноса 131 виходи суми 14 та переноса 15, причому стоки першого 1 і другого 2 функціональних транзисторів з'єднані між собою і під'єднані до витоку третього 3, до заслонів четвертого 4. п'ятого 5 і сьомого 7 функціональних транзисторів та до стоку першого 8 навантажувального транзистора, витоки першого 1 і п'ятого 5 функціональних транзисторів з'єднані між собою і під'єднані до заслону другого 2 функціонального транзистора і до входу 11 першого операнда, заслон першого 1 функціонального транзистора з'єднаний з витоком другого 2 функціонального транзистора і під'єднаний до входу 12 другого операнда, заслон третього 3 функціонального транзисторів з'єднаний з витоками четвертого 4 і шостого б функціональних транзисторів і під'єднаний до входу переноса 13, стоки третього З і четвертого 4 функціональних транзисторів з'єднані між собою і під'єднані до стоку другого 9 навантажувального транзистора і до виходу суми 14, стоки п'ятого 5 і шостого 6 функціональних транзисторів з'єднані між собою і під'єднані до виходу переноса 15, стоки сьомого 7 функціонального та третього 10 навантажувального транзисторів з'єднані між собою і під'єднані до заслону шостого 6 функціонального транзистора, при цьому заслони і витоки першого 8, другого 9 та третього 10 навантажувальних транзисторів під'єднані до шини живлення, а витік сьомого 7 функціонального транзистора з'єднаний з загальною шиною. Транзистори 1,218 складають елемент рівнозначності, тобто, якщо на входи операндів 11 і 12 подано сигнали однакових рівнів, то на їх об'єднаних стоках встановиться сигнал високого рівня. Наприклад, якщо на входа х операндів 11 і 12 присутні сигнали низьких рівнів і, відповідно, на заслонах транзисторів 1 і 2 тоже, то ці транзистори закриються і на стік транзистора 8 поступить високий потенціал шини живлення. В випадку, якщо на входах операндів 11 і 12 будуть сигнали високого рівня, то транзистори 1 і 2 відкриються, але високий потенціал шини живлення на їх стоках збережеться, так як на їх витоках також високий потенціал. Якщо на входах операндів 11 і 12 присутні сигнали різних рівнів, то на стоках транзисторів 1 і 2 встановиться низький потенціал. Тобто, сигнал високого рівня з одного зі входів операндів 11 або 12 відкриє, другий 2 або перший 1 транзистор, який передасть на свій стік сигнал низького рівня з Іншого входа операнда, відповідно, 12 або 11. Транзистори 3, 4 і 9 також утворюють елемент рівнозначності аналогічний розглянутому вище елементу рівнозначності на транзисторах 1,2 і 8. Використовуючи сигнал, утворений на об'єднаних стоках транзисторів 1, 2 і 8 першого елемента рівнозначності, і сигнал на вході переноса 13, на об'єднаних стоках транзисторів 3,4 і 9 формується потенціал, який поступає на вихід суми 14. Таким чином, формування значення суми S описується наступним співвідношенням де "Å" - операція додавання по модулю два; А і В - значення вхідних операндів; РО - значення вхідного переноса. Сигнал, зформований на об'єднаних стоках транзисторів 1, 2 і 8, також поступає на заслони п'ятого 5 і сьомого 7 транзисторів. Транзистори 7 і 10 утворюють. Інвертуючий вентиль і, таким чином, на заслон шостого 6 транзистора подається потенціал протилежний потенціалу на заслоні п'ятого 5 транзистора. Якщо на заслоні п'ятого транзистора 5 високий потенціал, то він відкриється і на його стік поступить потенціал сигнала зі входа першого операнда 11, при цьому транзистор 6 закритий. В випадку, якщо на заслоні п'ятого транзистора 5 сигнал низького рівня, то даний транзистор закриється, а транзистор 6 відкриється і на його вихід поступить потенціал зі входа переноса 13. Утворений таким чином сигнал подається на вихід переноса 15. Формування значення вихідного переноса Рn описується наступним співвідношенням Таким чином, за рахунок введення додаткових елементів і відповідних взаємозв'язків спростився алгоритм формування вихідного переноса і внаслідок цього на один функціональний транзистор зменшились загальні апаратні витрати Інтегральної реалізації однорозрядного суматора на МОН транзисторах, в порівнянні з відомим приладом. Також можна відмітити, що зменшена вихідна ємність І, відповідно, тривалість перехідних процесів на виході суми.

ДивитисяДодаткова інформація

Назва патенту англійськоюSingle-digit adder based on mos transistors

Автори англійськоюPankov Ruslan Stepanovych

Назва патенту російськоюОдноразрядный сумматор на моп-транзисторах

Автори російськоюПаньков Руслан Степанович

МПК / Мітки

МПК: G06F 7/48, G06F 7/503

Мітки: мон, суматор, транзисторах, однорозрядний

Код посилання

<a href="https://ua.patents.su/3-23051-odnorozryadnijj-sumator-na-mon-tranzistorakh.html" target="_blank" rel="follow" title="База патентів України">Однорозрядний суматор на мон транзисторах</a>

Попередній патент: Електричноскануючий вихрострумовий перетворювач

Наступний патент: Пристрій для подрібнення

Випадковий патент: Спосіб лікування хворих на контузійну травму ока