Цифровий формувач квадратурних складових

Номер патенту: 3680

Опубліковано: 15.12.2004

Формула / Реферат

Цифровий формувач квадратурних складових, що містить аналого-цифровий перетворювач, на перший вхід якого надходить вхідний сигнал, а вихід з'єднаний з першим входом помножувача, вихід якого з'єднаний з першим входом суматора, який відрізняється тим, що в нього введено: лінію затримки, два регістри і блок керування, на вхід якого надходить імпульс початкового установлення, при цьому перші входи лінії затримки і регістрів з'єднані з виходом суматора, а перший вихід блока керування з'єднаний з другим входом аналого-цифрового перетворювача, другий вихід якого з'єднаний з другим входом помножувача, а третій вихід з'єднаний з другим входом лінії затримки, у свою чергу четвертий і п'ятий виходи з'єднані з другими входами регістрів, а виходи регістрів є виходами цифрового формувача квадратурних складових.

Текст

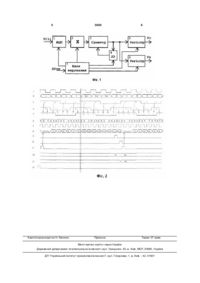

Цифровий формувач квадратурних складових, що містить аналого-цифровий перетворювач, на перший вхід якого надходить вхідний сигнал, а вихід з'єднаний з першим входом помножувача, вихід якого з'єднаний з першим входом суматора, 3 3680 4 ознак корисної моделі і технічним результатом 14 - імпульс ПУст. полягає в такому. Цифровий формувач квадратурних складових, Завдяки тому, що введено лінію затримки, два що заявляється, працює таким чином. регістри і блок керування, при цьому перші входи На перший вхід АЦП 1 надходить сигнал U(t), лінії затримки і регістрів з'єднані з виходом сумаякий перетворюється у цифрову форму при надтора, на вхід блока керування надходить імпульс ходженні на другий вхід АЦП 1 перепадів з логічпочаткового установлення, а перший вхід блока ного нуля в логічну одиницю (див. Фіг.2, діагр.1), і керування з'єднаний з другим входом аналогонадходить на перший вхід помножувача 2 (див. цифрового перетворювача, другий вихід якого Фіг.2 діагр.2) з'єднаний з другим входом помножувача, а третій Математичні співвідношення між частотою сивихід з'єднаний з другим входом лінії затримки, у гналу U(t) і частотою дискретизації такі ж, як у просвою чергу четвертий і п'ятий виходи з'єднані з тотипі (див. [2], стор.112, рис.5-10а). Діаграми, що другими входами регістрів, а виходи регістрів є ілюструють аналогію, наведено на Фіг.2, 3 4. Фазовиходами цифрового формувача квадратурних ві співвідношення усіх керуючих послідовностей на складових, зменшено обсяг апаратури. виходах блока керування 7 установлюються імпуПоставлене завдання вирішується у цифрольсом початкового установлення (див. Фіг.2, дівому формувачі квадратурних складових, що заагр.14). являється (див. Фіг.1), який містить АЦП 1, помноПомножувач 2 двічі за період зміни даних на жувач 2, суматор 3, у який додатково введено виході АЦП 1 помножує одні й ті самі дані на одилінію затримки (ЛЗ) 4, два регістри 5 і 6 і блок кеницю, спочатку з урахуванням знаку множення для рування 7. При цьому на перший вхід АЦП 1 надзразкової Sin-послідовності, а потім - з ура хуванходить вхідний сигнал U(t), другий вхід з'єднаний з ням знаку множення для зразкової Cosпершим виходом блока керування 7, а вихід з'єдпослідовності. Результуючу послідовність, яка кенаний з першим входом помножувача 2. Другий рує знаком множення, наведено на Фіг.2, діагр.5. вхід помножувача 2 з'єднаний з другим входом Дані з виходу помножувача 2 надходять на пеблока керування 7, а вихід з'єднаний з першим рший вхід суматора 3 (див. Фіг.2, діагр.6, де S і С виходом суматора 3. Другий вхід суматора 3 з'єдмісця в часі, які відповідають обчисленню, відповінаний з виходом ЛЗ 4, а вихід з'єднаний з першидно, Sin-квадратури і Cos-квадратури). На др угий ми входами ЛЗ 4 і регістрів 5 і 6. Другий вхід ЛЗ 4 вхід суматора 3 надходять дані з виходу ЛЗ 4, заз'єднаний з третім виходом блока керування 7, тримані у ній на два такти під впливом перепадів з четвертий і п'ятий виходи якого з'єднані з другими логічного нуля. в логічну одиницю (див. Фіг.2, дівходами регістрів 5 і 6 відповідно. На вхід блока агр.7). Дані в ЛЗ 4 обнуляються на першому такті керування надходить імпульс початкового устано(див. Фіг.2, діагр.8) і не впливають на суму, що влення (ПУст). На виході регістра 5 з'являється обчислюється суматором 3 у перших двох тактах. перша квадратурна складова Vc, а на виході регісДалі на другому вході суматора 3 послідовно з'явтра 6 з'являється друга квадратурна складова Vs. ляються затримані в ЛЗ 4 на два такти проміжні Робота цифрового формувача квадратурних суми Sin-квадратури і Cos-квадратури. складових пояснюється часовими діаграмами на Після надходження на перший вхід помножуФіг.2, де: вача 2 N-відліку даних АЦП 1 на виході ЛЗ 4 послі1 - тактові імпульси, що подаються з першого довно з'являться суми N-1 відліків. На виході сувходу блока керування 7 на другий вхід АЦП 1; матора 3 послідовно з'являються повні суми, що 2 - дані на виході АЦП 1; відповідають Sin-квадратурі і Cos-квадратурі для N 3 - знак множення для зразкової Sinвідліків даних АЦП 1, які записуються у регістри 6 і послідовності; 5 відповідно при надходженні на Їх другі входи 4 - знак множення для зразкової Cosімпульсів запису (див. Фіг.2, діагр.9, 10). послідовності; Далі АЦП 1 здійснює перший відлік даних з 5 - результуюча послідовність знаку множення, нової N-послідовності, обнуляються дані в ЛЗ 4, і яка подається з другого ви ходу блока керування 7 цикл обчислень повторюється. на другий вхід помножувача 2; Таким чином цифровий формувач квадратур6 - дані на виході помножувача 2; них складових, що заявляється, вирішує постав7 - тактові імпульси, що подаються з першого лене завдання, використовуючи тільки один повиходу блока керування 7 на другий вхід ЛЗ 4; множувач і тільки один суматор, чим досягається 8 - дані на виході ЛЗ 4; зменшення обсягу апаратури. 9 - імпульс запису, що подається з п'ятого виПомножувач 2 виконує функцію множення на ходу блока керування 7 на другий вхід регістра 6; плюс чи мінус одиницю і може бути реалізований 10 - імпульс запису, що подається з шостого багатьма засобами, від спеціалізованих мікросхем виходу блока керування 7 на другий вхід до комбінаційної логічної схеми. регістра 5; Реалізація ЛЗ 4 також може бути виконана ба11 - імпульс, що обнуляє дані в ЛЗ 4, який гатьма засобами, наприклад послідовним вклюнадходить на її другий вхід з третього виходу блоченням двох регістрів. ка керування 7; Блок керування може бути виконаний у вигляді 12 - дані Sin-квадратури на виході регістра 6; комбінаційної логічної схеми багатьма відомими 13 - дані Cos-квадратури на виході регістра 5; схемотехнічними заходами. 5 Комп’ютерна в ерстка Н. Лисенко 3680 6 Підписне Тираж 37 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Автори англійськоюKrupinov Yurii Oleksandrovych

Автори російськоюКрупинов Юрий Александрович

МПК / Мітки

МПК: G01S 7/285

Мітки: складових, формувач, цифровий, квадратурних

Код посилання

<a href="https://ua.patents.su/3-3680-cifrovijj-formuvach-kvadraturnikh-skladovikh.html" target="_blank" rel="follow" title="База патентів України">Цифровий формувач квадратурних складових</a>

Попередній патент: Датчик безпеки вивантажувального транспортера сільськогосподарської машини

Наступний патент: Спосіб підготовки молока при виробництві твердих сичужних сирів

Випадковий патент: Система і спосіб для збирання і моніторингу даних певного простору