Комірка для виконання математичних операцій над числами за змінним модулем

Номер патенту: 64491

Опубліковано: 16.02.2004

Автори: Михайлюк Антон Юрійович, Тарасенко Володимир Петрович, Максименко Микола Юрійович, Тесленко Олександр Кирилович

Формула / Реферат

Комірка для виконання математичних операцій над числами за змінним модулем, що містить першу та другу логічні схеми додавання за модулем 2 та першу схему логічного множення, яка відрізняється тим, що до її складу додатково введено логічну схему формування сигналу перенесення до старших розрядів при відніманні з додаванням, логічну схему формування позики при відніманні, логічну схему формування позики при відніманні з додаванням, логічну схему формування сигналу "Дорівнює", логічну схему формуваннясигналу "Більше", схему логічного додавання, інвертор, другу та третю схеми логічного множення, та вона має з першого по третій первинні входи, перший та другий бокові входи "Дорівнює" та "Більше" відповідно, входи перенесення із молодших розрядів при додаванні, позики із поточного розряду при відніманні і позики із поточного розряду при відніманні з додаванням, при цьому входи логічної схеми формування сигналу перенесення до старших розрядів при відніманні з додаванням та логічної схеми формування позики при відніманні з додаванням з'єднано з первинними входами, входом перенесення із молодших розрядів при додаванні та входом позики із поточного розряду при відніманні з додаванням; входи логічної схеми формування позики при відніманні - з першим та другим первинними входами та входом позики із поточного розряду при відніманні; входи логічної схеми формування сигналу "Дорівнює" - з первинними входами та боковим входом "Дорівнює"; входи логічної схеми формування сигналу "Більше" - з первинними входами, боковими входами "Дорівнює" та "Більше"; входи другої логічної схеми додавання за модулем 2 - з третім первинним входом, входом перенесення із молодших розрядів при додаванні та входом позики із поточного розряду при відніманні з додаванням; входи першої логічної схеми додавання за модулем 2 - з першим та другим первинними входами та виходами першої та другої схем логічного множення; входи третьої схеми логічного множення - зі входом позики із поточного розряду при відніманні та виходом логічної схеми формування сигналу "Дорівнює"; входи схеми логічного додавання - з виходом логічної схеми формування сигналу "Більше" та виходом третьої схему логічного множення; вхід інвертора - з виходом схеми логічного додавання; входи першої схеми логічного множення - з виходом другої логічної схеми додавання за модулем 2 та виходом схеми логічного додавання; входи другої схеми логічного множення - зі входом позики із поточного розряду при відніманні та з виходом інвертора, причому виходи логічної схеми формування сигналу перенесення до старших розрядів при відніманні з додаванням, логічної схеми формування позики при відніманні, логічної схеми формування позики при відніманні з додаванням, логічної схеми формування сигналу "Дорівнює", логічної схеми формування сигналу "Більше" і вихід першої логічної схеми додавання за модулем 2 є виходами комірки для виконання математичних операцій над числами за змінним модулем.

Текст

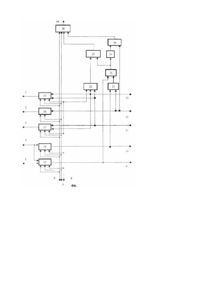

Винахід належить до обчислювальної техніки і може бути використаним у спеціалізованих обчислювальних пристроях для побудови швидкодіючих віднімачів за змінним модулем, системах несиметричних криптографічних перетворень, системах цифрового підпису. Відомий комбінаційний двійковий додавач [1], який діє за принципом групового перенесення і складається з m груп (m=1,..., n), при цьому кожна група містить вісім однорозрядних комбінаційних двійкових додавачів, вісім блоків формування розрядних сигналів генерації та транзиту перенесення, блок формування внутрішньогрупових перенесень, а також блок формування міжгрупового перенесення. Недоліком даного додавача є відсутність безпосередньої можливості додавання цілих чисел за модулем, який не є ступенем двійки. Найбільш близьким до запропонованого винаходу є додавач за змінним модулем [2], комірка якого містить дві логічні схеми додавання за модулем 2 та схему ло гічного множення, при цьому перший та другий входи першої логічної схеми додавання за модулем 2 з'єднано зі входами відповідних розрядних значень відповідно першого та другого операндів пристрою, а вхід перенесення під'єднано до першого виходу перенесення попередньої комірки (за винятком першої), вихід суми першої логічної схеми додавання за модулем 2 під'єднано до першого інформаційного входу другої логічної схеми додавання за модулем 2, вхід перенесення другої логічної схеми додавання за модулем 2 під'єднано до другого виходу перенесення попередньої комірки (за винятком першої), перший та другий виходи перенесення останньої комірки під'єднано відповідно до першого та другого входів елемента АБО, ви хід якого під'єднано до першого входу схеми логічного множення комірки, другий вхід схеми логічного множення комірки з'єднано з інформаційним входом переповнення комірки, а вихід - з другим інформаційним входом другої логічної схеми додавання за модулем 2. Недоліком даного додавача є низька швидкодія, що обумовлена наявністю зворотного зв'язку між елементом АБО та схемою логічного множення. Задачею даного винаходу є удосконалення комірки для виконання математичних операцій над числами за змінним модулем шляхом автономного формування у комірці сигналів перенесення у старші розряди, сигналів позики із старших розрядів та сигналів порівняння старших розрядів для передачі у молодші розряди, що забезпечує підвищення швидкодії. Поставлена задача вирішується тим, що в комірку для виконання математичних операцій над числами за змінним модулем, яка містить першу та другу логічні схеми додавання за модулем 2 та першу схему логічного множення, додатково введено логічну схему формування сигналу перенесення до старших розрядів при відніманні з додаванням, логічну схему формування позики при відніманні, логічну схему формування позики при відніманні з додаванням, логічну схему формування сигналу "Дорівнює", логічну схему формування сигналу “Більше”, схему логічного додавання, інвертор, другу та третю схеми логічного множення, та вона має з першого по третій первинні входи, перший та другий бокові входи "Дорівнює" та “Більше” відповідно, входи перенесення із молодших розрядів при додаванні, позики із поточного розряду при відніманні і позики із поточного розряду при відніманні з додаванням, при цьому входи логічної схеми формування сигналу перенесення до старших розрядів при відніманні з додаванням та логічної схеми формування позики при відніманні з додаванням з'єднано з первинними входами, входом перенесення із молодших розрядів при додаванні та входом позики із поточного розряду при відніманні з додаванням; входи логічної схеми формування позики при відніманні - з першим та другим первинними входами та входом позики із поточного розряду при відніманні; входи логічної схеми формування сигналу "Дорівнює" - з первинними входами та першим боковим входом "Дорівнює" входи логічної схеми формування сигналу "Більше" - з первинними входами, боковими входами "Дорівнює" та "Більше"; входи другої логічної схеми додавання за модулем 2 - з третім первинним входом, входом перенесення із молодших розрядів при додаванні та входом позики із поточного розряду при відніманні з додаванням; входи першої логічної схеми додавання за модулем 2 - з першим та другим первинними входами та виходами першої та другої схем логічного множення; входи третьої схеми логічного множення - зі входом позики із поточного розряду при відніманні та виходом логічної схеми формування сигналу "Дорівнює"; входи схеми логічного додавання - з виходом логічної схеми формування сигналу "Більше" та ви ходом третьої схеми логічного множення; вхід інвертора - з виходом схеми логічного додавання; входи першої схеми логічного множення - з виходом другої логічної схеми додавання за модулем 2 та виходом схеми логічного додавання; входи другої схеми логічного множення - зі входом позики із поточного розряду при відніманні та з виходом інвертора. На кресленні (фіг.) зображено функціональну схему комірки для виконання математичних операцій над числами за змінним модулем. Комірка містить логічну схему 15 формування сигналу перенесення до старших розрядів при відніманні з додаванням, логічну схему 16 формування позики при відніманні, логічну схему 17 формування позики при відніманні з додаванням, логічну схему 18 формування сигналу "Дорівнює", логічн у схему 19 формування сигналу "Більше", першу логічну схему 20 додавача за модулем 2, третю схему 21 логічного множення, другу логічн у схему 22 додавача за модулем 2, схему 23 логічного додавання, інвертор 24, першу та другу схеми 25 та 26 логічного множення, при цьому входи логічної схеми 15 формування сигналу перенесення до старших розрядів при відніманні з додаванням та логічної схеми 17 формування позики при відніманні з додаванням з'єднано з першим по третій первинними входами, відповідно 6, 7, 8, входом 11 перенесення із молодших розрядів при додаванні та входом 13 позики із поточного розряду при відніманні з додаванням; входи логічної схеми 16 формування позики при відніманні - з першим та другим первинними входами, 6, 7 відповідно, та входом 12 позики із поточного розряду при відніманні; входи логічної схеми 18 формування сигналу "Дорівнює" - з першим по третій первинними входами, відповідно 6, 7, 8, та боковим входом 4 "Дорівнює"; входи логічної схеми 19 формування сигналу "Більше" - з першим по третій первинними входами, відповідно 6, 7, 8, першим та другим боковими входами 4 "Дорівнює" та 5 "Більше" відповідно; входи другої логічної схеми 22 додавання за модулем 2 - з третім первинним входом 8, входом 11 перенесення із молодших розрядів при додаванні та входом 13 позики із поточного розряду при відніманні з додаванням; входи першої логічної схеми 20 додавання за модулем 2 - з першим та другим первинними входами, 6, 7 відповідно, та виходами першої 25 та другої 26 схем логічного множення; входи третьої схеми 21 логічного множення - зі входом 12 позики із поточного розряду при відніманні та виходом 10 логічної схеми 18 формування сигналу "Дорівнює"; входи схеми 23 логічного додавання - з виходом 9 логічної схеми 19 формування сигналу "Більше" та виходом третьої схеми 21 логічного множення; вхід інвертора 24 - з виходом схеми 23 логічного додавання; входи першої схеми 25 логічного множення - з виходом другої логічної схеми 22 додавання за модулем 2 та виходом схеми 23 логічного додавання; входи другої схеми 26 логічного множення - зі входом 12 позики із поточного розряду при відніманні та з виходом інвертора 24. Виходами комірки для виконання математичних операцій над числами за змінним модулем є вихід 1 логічної схеми 15 формування сигналу перенесення до старших розрядів при відніманні з додаванням, вихід 2 логічної схеми 16 формування позики при відніманні, вихід 3 логічної схеми 17 формування позики при відніманні з додаванням, вихід 10 логічної схеми 18 формування сигналу "Дорівнює", вихід 9 логічної схеми 19 формування сигналу "Більше" та вихід 14 першої логічної схеми 20 додавання за модулем 2. Запропонований винахід працює наступним чином. На первинні входи 6, 7 та 8 комірки надходять значення розрядів з однаковою вагою (хі, уі, рі) двійкових кодів відповідно чисел X, Y та Р, а на виході 14 комірки формується значення розряду з тією самою вагою числа Z (zі, i=0, 1,.., n-1, n - розрядність Р). На вхід 13 комірки надходить сигнал перенесення з молодших розрядів при додаванні Р (якщо XYі+1, а на виході 10 формується сигнал "Більше", який має значення "1", якщо Xi>Yi. Таким чином нульове значеннях сигналів на входах 4 та 5 (або на виходах 9 та 10) визначають співвідношення Xi+1

ДивитисяДодаткова інформація

Назва патенту англійськоюCell for performing mathematical operations on numbers with a variable absolute value

Автори англійськоюTarasenko Volodymyr Petrovych, Mykhailiuk Anton Yuriiovych, Teslenko Oleksandr Kyrylovych

Назва патенту російськоюЯчейка для выполнения математических операций над числами с переменным модулем

Автори російськоюТарасенко Владимир Петрович, Михайлюк Антон Юрьевич, Тесленко Александр Кирилович

МПК / Мітки

МПК: G06F 7/505, G06F 7/50

Мітки: модулем, виконання, числами, змінним, математичних, операцій, комірка

Код посилання

<a href="https://ua.patents.su/3-64491-komirka-dlya-vikonannya-matematichnikh-operacijj-nad-chislami-za-zminnim-modulem.html" target="_blank" rel="follow" title="База патентів України">Комірка для виконання математичних операцій над числами за змінним модулем</a>

Попередній патент: Спосіб візуалізації течії газового потоку

Наступний патент: Пристрій для ущільнення пет-пляшок

Випадковий патент: Знаряддя для нарізання щілин