Комірка однорідного обчислювального середовища

Номер патенту: 21850

Опубліковано: 30.04.1998

Автори: Кисіль Богдан Васильович, Стрямець Сергій Петрович, Грицик Володимир Володимирович

Формула / Реферат

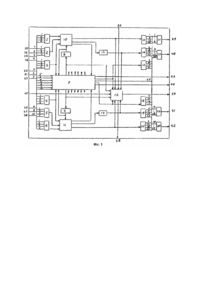

1. Комірка однорідного обчислювального середовища, яка має п'ять мультиплексорів, два дешифратори, два арифметико-логічних елементи, два елементи затримки, п'ятьдемультиплексорів, до того ж інфомаційні входи першого, другого, третього, четвергого та п'ятого мультиплексорів з'єднані з інформаційними входами комірки, виходи першого та другого мультиплексорів з'єднані з першим та другим інформаційними входами першого арифметико-логічного елемента, налаштовуючий вхід якого з'єднаний з виходом першого дешифратора, виходи третього та четвертого мультиплексорів з'єднані з першим та другим інформаційними входами другого арифметико-логічного елемента, налаштовуючий вхід якого з'єднаний з виходом другого дешифратора, яка відрізняється тим, що введені шостий мультиплексор, блок регістрів, блок діагностики, шостий де-мультиплексор, та чотири елементи АБО, до того ж вихід п'ятого мультиплексора з'єднаний з третім інформаційним входом першого арифметико-логічного елемента і першим інформаційним входом блока регістрів, інформаційні входи шостого мультиплексора з'єднані з інформаційними входами комірки, вихід шостого мультиплексора з'єднаний з третім інформаційним входом другого арифметико-логічного елемента та другим інформаційним входом блоку регістрів, перший та другий управляючі входи якого з'єднані з виходами першого та другого дешифраторів, перші виходи першого та другого блоків арифметико-логічних елементів з'єднані з першим та другим входами блоку діагностики і з входами першого та другого демультиплексорів, другі виходи першого та другого блоків арифметико-логічних елементів з'єднані з входами першого та другого елементів затримки, виходи яких з'єднані з третім та четвертим входами блоку діагностики та з входами третього та четвертого демультиплексорів, треті виходи першого та другого блоків арифметико-логічних елементів з'єднані з третім та четвертим інформаційними входами блоку регістрів, перший та другий налаштовуючі входи якого з'єднані з налаштовуючими входами комірки, третій та четвертий управляючі входи блоку регістрів з'єднані з управляючими входами комірки, перший та другий програмні входи блоку регістрів з'єднані з першим та другим програмними входами комірки, перший та другий програмні виходи блоку регістрів з'єднані з першим та другим програмними виходами комірки, перший управляючий вихід блоку регістрів з'єднаний з входом першого дешифратора та з п'ятим входом блоку діагностики, другий, третій та п'ятий управляючі виходи бтоку регістрів з'єднані з управляючими входами відповідно п'ятого, другого та першого мультиплексорів; четвертий, шостий та сьомий управляючі виходи блоку регістрів з'єднані з управляючими входами першого, другого та третього демультиплексорів відповідно, восьмий управляючий вихід блоку регістрів з'єднаний з входами другого дешифратора та з шостим входом блока діагностики, дев'ятий, десятий та дванадцатий управляючі виходи блоку регістрів з'єднані з управляючими входами шостого, четвертого та третього мультиплексорів відповідно, одинадцатий, тринадцятий та чотирнадцятий управляючі виходи блоку регістрів з'єднані з управляючими входами четвертого, п'ятого та шостого демультиплексорів відповідно, п'ятий інформаційний вхід блоку регістрів з'єднаний з першим інформаційним входом комірки, перший інформаційний вихід блоку регістрів з'єднаний з п'ятим входом другого елементу АБО, другий інформаційний вихід блоку регістрів з'єднаний з входом п'ятого демультиплексора та з сьомим входом блоку діагностики, восьмий вхід якого з'єднаний з третім інформаційним виходом блоку регістрів та з входом шостого демультиплексора, перші виходи всіх демультиплексорів з'єднані з входами першого елемента АБО, треті з третім, а четверті з входами четвертого елемента АБО, виходи елементів АБО являються інформаційними виходами комірки, перший та другий входи ознаки помилки блоку діагностики з'єднані з першим та другим входами ознаки помилки комірки, перший та другий виходи ознаки помилки блоку діагностики з'єднані з першим та другим виходами ознаки помилки комірки.

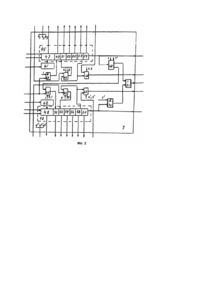

2. Комірка однорідного обчислювального середовища по п. 1, яка відрізняється тим, що блок регістрів має перший та другий налаштовуючі регістри, перший та другий лічильники, перший, другий, третій, четвертий та п'ятий комутатори, декомутатор, перший та другий елементи І, елемент АБО, до того ж налаштовуючі входи першого та другого налаштовуючих регістрів підключені до програмних входів блоку регістрів, налаштовуючий вихід першого налаштовуючого регістру підключений до першого налаштовуючого виходу блоку регістрів та до входу декомутатора, другого до другого налаштовуючого виходу блоку регістрів та до першого входу другого елементу І, вихід якого підключений до першого входу елементу АБО, другий вхід якого підключений до першого виходу декомутатора, вихід елементу АБО підключений до першого інформаційного виходу блоку регістрів, управляючі входи блоку регістрів підключені до управляючих входів лічильників, виходи яких підключені до перших входів налаштовуючих регістрів, перший, другий, третій, четвертий, п'ятий, шостий та сьомий управляючі виходи першого налаштовуючого регістру підключені до першого, другого, третього, четвертого, п'ятого, шостого та сьомого управляючих виходів блоку регістрів, перший, другий, третій, четвертий, п'ятий, шостий та сьомий управляючі виходи другого налаштовуючого регістру підключені до восьмого, дев'ятого, десятого, одинадцятого, дванадцятого, тринадцятого та чотирнадцятого управляючих виходів блоку регістрів, перший інформаційний вхід блоку регістрів підключений до першого входу комутатора, другий вхід якого підключений до восьмого виходу першого налаштовуючого регістру та до першого входу другого комутатора, другий вхід якого підключений до третього інформаційного входу блоку регістрів, а вихід підключений до другого інформаційного виходу блоку регістрів, другий інформаційний вхід блоку регістрів підключений до першого входу третього комутатора, другий вхід якого підключений до восьмого виходу другого налаштовуючого регістру та до першого входу четвертого комутатора, другий вхід якого підключений до четвертого інформаційного входу блоку регістрів, а вихід підключений до третього інформаційного виходу блоку регістрів, п'ятий інформаційний, вхід блоку регістрів піключений до першого входу першого елементу І та до першого входу п'ятого комутатора, другий вхід якого підключений до другого виходу декомутатора, а вихід підключений до другого входу другого налаштовуючого регістру, третій вхід якого підключений до виходу третього комутатора, вихід першого елемента І підключений до другого входу першого налаштовуючого регістру, третій вхід якого підключений до виходу першого комутатора, перший вхід першої групи управляючих входів блоку регістрів підключений до другого входу першого елементу І, та до перших управляючих входів декомутатора та п'ятого комутатора, другий вхід першої групи управляючих. входів блоку регістрів підключений до першого управляючого входу першого комутатора, та до управляючого входу другого комутатора, третій вхід першої групи підключений до другого управляючого входу першого комутатора та до управляючого входу другого комутатора, перший вхід другої гру-пи управляючих входів блоку регістрів підключений до другого входу другого елементу І, другого управляючого входу декомутатора, та до другого управляючого входу п'ятого комутатора, другий вхід другої групи управляючих входів підключений до першого управляючого входу третього комутатора та до управляючого входу четвертого комутатора, третій вхід другої групи підключений до другого управляючого входу третього комутатора та до управляючого входу четвертого комутатора.

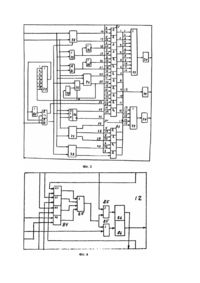

3. Комірка однорідного обчислювального середовища по п. 1, яка відрізняється тим, що блок АЛЕ має комутатор, суматор, перший, другий, третій та четвертий регістри, мультиплексор, тригер, суматор по модулю два, схему виділення першої та останньої одиниці з безперервного посилання імпульсів, перший, другий, третій та четвертий елементи АБО, перший, другий та третій інвертори, перший, другий та третій елементи І, першу та другу групи елементів І, до того ж перший інформаційний вхід блоку АЛЕ підключений до першого входу комутатора, до перших входів перших елементів АБО та І, до першого входу суматора, до входу S тригера, до першого входу суматора по модулю два, та до першого входу схеми виділення, другий інформаційний вхід блоку АЛЕ підключений до другого входу комутатора, до других входів перших елементів АБО та І, до другого входу суматора, до входу R тригера, до другого входу суматора по модулю два, третій інформаційний вхід блоку АЛЕ підключений до перших входів другого та третього елементів 1, сім входів другого елементу АБО підключені до перших семи управляючих входів групи управляючих входів блоку АЛЕ, вихід другого елементу АБО підключений до другого входу третього елементу І та до входу першого інвертора, вихід якого підключений до другого входу другого елементу І, вихід якого підключений до першого входу третього елементу АБО, та до входу першого регістру, вихід якого підключений до другого входу блоку АЛЕ, вихід третього елементу І підключений до управляючого входу комутатора, до першого входу мультиплексора, до входу Т тригера та до другого входу схеми виділення, перші входи елементів І першої групи підключені до управляючих входів з четвертого по п'ятнадцяту групи управляючих входів блоку АЛЕ, перші входи другої групи елементів І підключені до управляючих входів з четвертої по сьому групи управляючих входів блоку АЛЕ, перший вихід комутатора підключений до другого входу першого елементу І першої групи, другий вихід комутатора підключений до другого входу першого елементу І другої групи, другі входи другого та п'ятого елементів І першої групи підключені до виходу суми суматора, вихід перенесення-одиниці якого підключений до другого входу другого елементу І другої групи, та до входу другого регістру, вихід якого підключений до другого входу мультиплексора, управляючий вхід якого підключений до восьмого управляючого входу групи управляючих входів АЛЕ, а вихід підключений до входу одиниці перенесення суматора» другий вхід третього елементу І першої групи підключений до прямого виходу тригера, інверсний вихід якого підключений до другого виходу третього елементу І другої групи, другий вхід четвертого елементу І першої групи підключений до першого виходу схеми виділення, другий вихід який підключений до другого входу четвертого елементу І другої групи, другий вхід шостого елементу І першої групи підключений до виходу другого інвертора, вхід якого підключений до виходу першого елементу АБО та до другого входу сьомого елементу І першої групи, другий вхід восьмого елементу І першої групи підключений до виходу третього інвертора, вхід якого підключений до виходу першого елементу І та до другого входу дев'ятого елементу І першої групи, другі входи десятого, одинадцятого та дванадцятого елементів І першої групи підключені відповідно до першого, другого та третього виходів суматора по модулю два, виходи першої групи елементів І підключені до входів четвертого елементу АБО, вихід якого підключений до входу третього регістру, вихід якого підключений до першого виходу блоку АЛЕ, виходи другої групи елементів І підключені до входів третього елементу АБО, вихід якого підключений до входу четвертого регістру, вихід якого підключений до третього виходу блоку АЛЕ. 4. Комірка однорідного обчислювального середовища по п. 1, яка відрізняється тим, що блок діагностики має перший, другий, третій та четвертий елементи "виключаюче АБО" перший, другий та третій елементи АБО, перший та другий регістри, до того ж перший та другий входи блоку діагностики з'єднані з першим та другим входами першого елементу "виключаючого АБО", третій та четвертий входи блоку діагностики з'єднані з першим та другим входами другого елементу "виключаючого АБО", п'ятий та шостий входи блоку діагностики з'єднані з першим та другим входами третього елементу "виключаючого АБО", сьомий та восьмий входи блоку діагностики з'єднані з першим та другим входами четвертого елементу "виключаючого АБО", виходи всіх злементів "виключаючих АБО" з'єднані з входами першого елементу АБО, вихід якого з'єднаний з першими входами другого та третього елементів АБО, другі входи яких підключені до першого та другого входів ознаки помилки комірки, а виходи підключені до входів першого та другого регістрів, виходи яких з'єднані з першим та другим виходами ознаки помилки блоку діагностики.

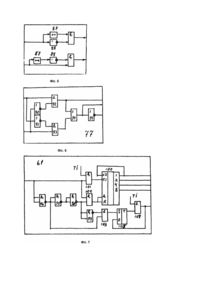

5. Комірка однорідного обчислювального середовища па п. 1, яка відрізняється тим, що суматор по модулю два містить три інвертори, два елементи І, та один елемент АБО, при чому перший інформаційний вхід з'єднаний з входом першого інвертора та з першим входом першого елемента І, другий вхід якого підключений до виходу другого інвертора, а вихід до першого входу елемента АБО і до першого інформаційного виходу, другий інформаційний вхід підключений до входу другого інвертора, та до першого входу другого елемента І, другий вхід якого підключений до виходу першого інвертора, а вихід до другого входу елемента АБО, вихід якого підключений до другого інформаційного виходу, та до входу третього інвертора, вихід якого підключений до третього виходу суматора по модулю два.

6. Комірка однорідного обчислювального середовища по п. 1, яка відрізняється тим, що лічильник містить чотири інвертори, чотири елементи І, RS-тригер, та двійковий лічильник, при чому управляючий вхід підключений до перших входів першого та другого елементів І, та до входу першого інвертора, вихід якого підключений до першого входу третього елемента І, та до входу другого інвертора, вихід якого підключений до входу третього інвертора, вихід якого підключений до другого входу першого елемента І, та до входу четвертого інвертора, вихід якого підключений до входу S-тригера, вихід якого підключений до першого входу четвертого елемента І, на другий вхід якого подаються тактові імпульси, а вихід підключений до входу R тригера, і до управляючого виходу лічильника, вихід першого елемента І підключений до входу R двійкового лічильника, вхід С1 якого підключений до виходу другого елемента І, на другий вхід якого подаються тактові імпульси, виходи двійкового лічильника є виходами лічильника до першого з яких підключений вхід С2.

Текст

Винахід відноситься до обчислювальної техніки та дозволяє будувати матрицю обчислювальних комірок однорідного середовища універсальної обчислювальної системи. Відома комірка обчислювального середовища, яка має арифметико-логічний елемент, регістр команд, дешифратор, три елементи затримки, три комутатора входів та чотири комутатора виходів [1]. Недоліками цієї комірки являються мала продуктивність із-за невеликого набору функцій, які виконуються, та недостатня надійність із-за відсутності апаратних засобів, які дозволяють роботи контроль правильності виконання команд. Найбільш близьким технічним рішенням до даного винаходу є комірка однорідного обчислювального середовища, яка має чотири інформаційні входи, п'ять мультиплексорів, чотири налаштовуваних входи, три арифметико-логічних елементи, три дешифратора, чотири елементи затримки, п'ять демультиплексорів, чотири інформаційних виходи [2]. Недоліками цієї комірки являються недостатня надійність із-за відсутності зв'язку між операційним та налаштовуючим каналами. В основу винаходу покладена задача розширення функціональних можливостей комірки однорідного обчислювального середовища за рахунок реалізації можливості обміну інформацією між налаштовуючим каналом та каналом даних і поліпшення функції самодіагностування. На фіг.1 представлена функціональна схема комірки; на фіг.2 - блок регістрів; на фіг.3 - арифметикологічний елемент; на фіг.4 - блок діагностики; на фіг.5 - схема виділення першої та останньої одиниці з безперервної посилки імпульсів, на фіг.6 - схема суматора по модулю два, на фіг.7 - лічильник. Комірка має вхідні мультиплексори 1 - 6, блок регістрів 7, два дешифратори 8 та 9, два арифметикологічних елементи (АЛЕ) 10 та 11, блок діагностики 12, елементи затримки 13 та 14, вихідні мультиплексори 15 - 20, чотири елементи АБО 21 - 24, інформаційні входи 25 - 28, налаштовуючі входи 29 - 32, входи управління лічильників КОП 33 - 34, входи ознаки помилки попередньої комірки 35 (рядки), 36 (стовпчики), виходи ознаки помилки 37, 38, інформаційні виходи 39 - 42, налаштовуючі виходи 43, 44. Блок регістрів має два налаштовуючих регістри 45, 46, які містять поля коду операцій (КОП) 47, 48, поля адресу входів АЛЕ 49, 51 та 50, 52, поля адресу виходів АЛЕ 55, 56, поля адресу входів транзиту 53, 54, поля адресу виходів транзитів з затримкою 57, 58, та без затримки 59, 60. Крім того блок регістрів має два лічильники 61, 62, п'ять комутаторів 63 - 67, декомутатор 68, два елементи І 69, 70, елемент АБО 71. Арифметико-логічний елемент має комутатор 72, суматор 73, чотири регістри 74, мультиплексор 75, RST тригер 76, суматор по модулю два 77, схему виділення першої та останньої одиниці з безперервної посилки імпульсів 78, чотири елементи АБО 79, три інвертори 80, три елементи І 81, дві групи елементів І 82 та 83. Блок діагностики має групу елементів "виключаюче АБО" 84, три елементи АБО 85, два регістри 86. Схема виділення першої та останньої одиниці з безперервної посилки імпульсів має два елементи затримки 87, два інвертори 88 та два елементи І 89. Суматор по модулю два має три елементи АБО-НІ 90, 91, 95, два елементи І 92, 93, один елемент АБО 94, два входи, три виходи. Лічильник має чотири інвертори 96 - 99, чотири елементи І 101 - 104, RS-тригер 105 та двійковий лічильник 100. Заявлена сукупність признаків невідома ні з аналогів, ні з прототипу, і приводить до розширення функціональних можливостей комірки ООС, за рахунок реалізації можливості обміну інформацією між налаштовуючим каналом та каналом даних і поліпшення функції самодіагностування, тобто відповідає критерію "суттєві відмінності". Пристрій працює слідуючим чином. Перед початком рішення задачі виконується запис двох команд в регістри команд 45 та 46 послідовним кодом через налаштовуючі входи 31 та 32 по сигналу дозволу вводу програм, який подається на налаштовуючі входи 29 та 30. По закінченню сигналу, який дозволяє ввід програми, коди двох команд запам'ятовуються в регістрах 45 та 46 і комірка переходить в динамічний режим виконання операцій. Дешифратори 8 та 9 (схеми 1), входи яких з'єднані з виходами полів 47 та 48 налаштовуючих регістрів 45 та 46, а виходи підключені до управляючих входів АЛЕ 10 та 11 і до управляючих входів ГК (генерації констант) блоку регістрів 7, налаштовує їх на виконання операцій згідно кодам операцій, записаних в полях 47 та 48 блоку регістрів 7. АЛЕ 10 та 11 можуть бути налаштовані на виконання операцій незалежно один від одного або ж на виконання однакової операції. При виконанні АЛЕ 10 та 11 однакової операції блок діагностики 12 виконує порівняння результатів обчислень, і в випадку їх неспівпадіння на виходах комірки 37 та 38 з'являється сигнал ознаки помилки. При цьому блок діагностики також робить контроль правильності налаштування полів КОП 47 та 48 блоку регістрів 7. Комірка приймає дані з чотирьох інформаційних входів 25 - 28 через мультиплексори 1 - 3 та 4 - 6 в залежності від управляючих сигналів, які поступають на ці мультиплексори. Дані для першого АЛЕ 10 поступають через мультиплексори 1 - 3, для другого АЛЕ 11 через мультиплексори 4 - 6. Адреси прийому даних визначаються вихідними сигналами полів 49, 51, 53 та 50, 52, 54 налаштовуючих регістрів 47 та 48. АЛЕ 10 та 11 незалежно один від одного можуть виконувати операції над двома змінними, результати обчислень з АЛЕ 10 через демультиплексор 15, а з АЛЕ 11 через демультиплексор 20 поступають на інформаційні виходи 39 - 42 комірки. Напрямок вигрузки визначається управляючими сигналами, які поступають на демультиплексори з полів 55 та 56 блоку регістрів 7. При роботі АЛЕ 10 та 11 з двома змінними коміркою здійснюється два транзити вхідних даних через мультиплексори 1 та 6, та видаються через демультиплексори 16, 17 та 18, 19, а через демультиплексори 16 та 19 з затримкою на один такт, номери інформаційних виходів, по яких видаються транзитні дані, визначаються вмістимим полів 57, 59 та 58, 60 налаштовуючих регістрів 45 та 46. При співпаданні адрес виходів робиться логічне додавання. В АЛЕ 10 та 11 можуть бути реалізовані слідуючи функції двох змінних: АБО, АБО-НІ, І, І-НІ, А1 > А2, А1 + А2, А1 = А2, разом з цими функціями через комірку можливий транзит. Транзит через комірку можливий і при виконанні операції послідовного додавання з запам'ятовуванням одиниці перенесення. У всіх решта операціях транзитний канал через комірку блокується. При реалізації в АЛЕ 10, 11 операції комутації входів: А1 та А2 на виходи А4 та А6 вхід транзиту використовується як управляючий вхід комутатора 72, а вихід транзиту без затримки використовується як другий вихід комутатора 72. При виконанні АЛЕ 10, 11 операції паралельного додавання вхід транзиту використовується як вхід одиниці перенесення суматора 73, а вихід транзиту без затримки, як вихід одиниці перенесення. Реалізовуючи в АЛЕ 10, 11 RST тригер 76 вхід транзиту є лічильним входом тригера 76. При виконанні операції виділення першої та останньої одиниці з безперервної посилки імпульсів, використовуються входи А1 та вхід транзиту, а в якості виходів - вихід АЛЕ та вихід транзиту без затримки. Крім цих функцій комірка може генерувати чотири види констант, циклічне вивантаження восьми біт з програмованим виходом, затримка на вісім біт з програмованим входом та виходом, затримка на дванадцять біт з фіксованим входом та виходом, затримка на двадцять чотири біти з фіксованим входом та виходом. Генерація констант реалізується в блоці регістрів, управління генерацією констант виконується дешифраторами 8 та 9. Для генерації вісьмирозрядних констант використовуються поля 51, 53, 55, 57 та 52, 54, 56, 58 налаштовуючих регістрів 45 та 46, які працюють в режимі зсуву, при цьому поля 47, 49, 59 та 48, 50, 60 залишаються фіксованими. Для реалізації дванадцятирозрядних констант в режимі зсуву працюють поля 49, 51, 53, 55, 57, 59 та 50, 52, 54, 56, 58. 60, поля 47 та 48 лишаються фіксованими. При налаштуванні полів 47 та 48 на генерацію дванадцятирозрядних констант одночасно, реалізується двадцятичотирьохрозрядна константа. Лічильники 61 та 62 служать для швидкої зміни вмістимого полів 47 та 48 налаштовуючих регістрів. Незалежно від роботи, яка виконується коміркою, при наявності сигналів на управляючих входах, лічильники рахують тактові імпульси, і при припиненні подачі сигналів на управляючі входи, здійснюється запис результатів рахунку в поля 47 та 48 налаштовуючих регістрів 45 та 46. З слідуючого такту комірка буде виконувати нову операцію, з зберіганням адрес завантаження та розвантаження даних. Для запису всіх нулів в поля 47 та 48 регістрів налаштування 45 та 46 на управляючі входи лічильників 61 та 62 достатньо подати на входи управління налаштуванням короткий імпульс. Таким чином, комірка дозволяє виконувати операції над двома парами змінних, незалежно від них передавати інформацію з двох входів на чотири виходи, до того ж на два виходи з додатковою затримкою на один такт. дозволяє робити логічне додавання комбінацій з перелічених операцій, дозволяє генерувати чотири види констант, має зв'язок програмного та операційного каналів. Є можливість робити контроль правильності виконання операцій, для цього обидва АЛЕ налаштовуються на однакові операції. Для збільшення стислості обчислень кожний АЛЕ налаштовується на свою операцію. Швидка зміна коду операцій АЛЕ дозволяє виконувати тестування матриці обчислювальних комірок та її обнуления. Наявність в кожній комірці блоку діагностики значно спрощує задачу тестування матриці.

ДивитисяДодаткова інформація

Назва патенту англійськоюCell of a uniform computing environment

Автори англійськоюHrytsyk Volodymyr Volodymyrovych, Kysil Bohdan Vasyliovych, Striamets Serhii Petrovych

Назва патенту російськоюЯчейка однородной вычислительной среды

Автори російськоюГрицык Владимир Владимирович, Кисиль Богдан Васильевич, Стрямец Сергей Петрович

МПК / Мітки

МПК: G06F 7/00, G06F 15/18

Мітки: обчислювального, середовища, комірка, однорідного

Код посилання

<a href="https://ua.patents.su/6-21850-komirka-odnoridnogo-obchislyuvalnogo-seredovishha.html" target="_blank" rel="follow" title="База патентів України">Комірка однорідного обчислювального середовища</a>

Попередній патент: Захисний клапанний пристрій для багатоконтурної пневматичної гальмівної системи автотранспортного засобу

Наступний патент: Спосіб виготовлення декоративної панелі

Випадковий патент: Устаткування для градуювання і перевірки витратомірів та лічильників газу