Пристрій і спосіб обробки даних

Номер патенту: 103603

Опубліковано: 11.11.2013

Автори: Йококава Такасі, Окада Сатосі, Ікегая Рйодзі, Сакаї Луї, Ямамото Макіко

Формула / Реферат

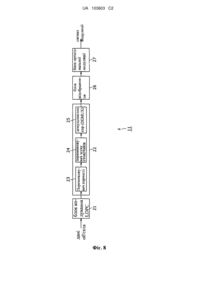

1. Пристрій обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду з довжиною N коду записують у напрямку стовпчиків зазначеної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC-коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків вказаної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків вказаної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, при цьому засіб заміни виконаний з можливістю заміни mb бітів коду так, що біти коду після заміни утворюють біти символів;

правилом співставлення є правило, яке визначає,

коли групи, в які повинні бути згруповані біти коду залежно від вірогідності помилки в бітах коду, використовують як групи бітів коду і групи, в які повинні бути згруповані біти символу залежно від вірогідності помилки в бітах символу, використовують як групи бітів символу,

набір груп, який є комбінацією будь-якої групи бітів коду і будь-якої групи бітів символу, з якими співставлена група бітів коду, і

кількість бітів в кожній з груп бітів коду і кожній з груп бітів символу набору груп.

2. Пристрій обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду (коду з малою щільністю перевірок на парність) з довжиною N коду записують у напрямку стовпчиків зазначеної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC-коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків зазначеної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків зазначеної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, при цьому засіб заміни виконано з можливістю заміни mb бітів коду так, що біти коду після заміни утворюють біти символів;

LDPC-код є LDPC-кодом, який визначений в стандарті DVB-S.2 або стандарті DVB-T.2 і який має довжину N коду, яка дорівнює 64 800 бітам;

правилом співставлення є правило, яке визначає,

коли групи, в які повинні бути згруповані біти коду залежно від вірогідності помилки в бітах коду, використовують як групи бітів коду і групи, в які повинні бути згруповані біти символу залежно від вірогідності помилки в бітах символу, використовують як групи бітів символу,

набір груп, який є комбінацією будь-якої групи бітів коду і будь-якої групи бітів символу, з якими співставлена група бітів коду, і

кількість бітів в кожній з груп бітів коду і кожній з груп бітів символу набору груп;

причому m бітів є 12 бітами і ціле число b дорівнює 1 і, крім того, 10 бітів коду перетворюють на один символ в 212 або 4 096 сигнальних точок,

12×1 бітів коду згруповані в три групи бітів коду, а

12×1 бітів символу згруповані в шість груп бітів символу;

правило співставлення визначає, що

один біт коду групи бітів коду, яка є кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є п'ятою кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є другою кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є третьою кращою з погляду вірогідності виникнення помилок, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є четвертою кращою з погляду вірогідності виникнення помилки, що

один біт коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є шостою кращою з погляду вірогідності виникнення помилки, що

один біт коду групи бітів коду, яка є третьою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є п'ятою кращою з погляду вірогідності виникнення помилки, і що

один біт коду групи бітів коду, яка є третьою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є шостою кращою з погляду вірогідності виникнення помилки.

3. Пристрій обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду (коду з малою щільністю перевірок на парність) з довжиною N коду записують у напрямку стовпчиків зазначеної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC-коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків вказаної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків вказаної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, при цьому засіб заміни виконано з можливістю заміни mb бітів коду так, що біти коду після заміни утворюють біти символів;

LDPC-код є LDPC-кодом, який визначений в стандарті DVB-S.2 або стандарті DVB-T.2 і який має довжину N коду, яка дорівнює 64 800 бітам, і швидкість кодування, яка дорівнює 5/6;

m бітів є 12 бітами і ціле число b дорівнює 1;

12 бітів коду перетворюють на один символ в одну з 4 096 сигнальних точок, визначених в 4096-ти позиційній КАМн;

вказана пам'ять містить 12 стовпчиків, призначених для зберігання 12×1 бітів у напрямку рядків і зберігання 64 800/(12 × 1) бітів у напрямку стовпчиків;

у вказаному засобі заміни здійснюють,

причому і+1-ий біт, починаючи з самого старшого біта серед 12× 1 бітів коду, які були зчитані у напрямку рядків із пам'яті, позначають через біт bі та і+1-ий біт, починаючи з самого старшого біта серед 12×1 бітів одного символу, позначають через біт уі, відповідно до правила співставлення

заміну з метою співставлення

біта b0 і біта у8,

біта b1 і біта у0,

біта b2 і біта у6,

біта b3 і біта у1,

біта b4 і біта у4,

біта b5 і біта y5,

біта b6 і біта у2,

біта b7 і біта у3,

біта b8 і біта у7,

біта b9 і біта у10,

біта b10 і біта у11 і

біта b11 і біта у9.

4. Пристрій обробки даних за будь-яким з пп. 1-3, який відрізняється тим, що в ньому

LDPC-код є LDPC-кодом, отриманим в результаті кодування за допомогою LDPC-коду відповідно до перевірочної матриці, в якій матриця контролю парності, яка є частиною LDPC-коду, що відповідає бітам контролю парності LDPC-коду, має ступінчасту структуру.

5. Пристрій обробки даних за п. 4, який відрізняється тим, що у ньому

кількість М бітів контролю парності LDPC-коду є числом, відмінним від простого, і в якому

два дільники кількості М бітів контролю парності, які відрізняються від 1 і М і добуток яких дорівнює кількості М бітів контролю парності, позначено через Р і q,

кількість інформаційних бітів LDPC-коду позначають через К,

ціле число, більше або рівне 0, але менше Р, позначають через х, і

інше ціле число, більше або рівне 9, але менше q, позначають через у,

вказаний засіб рознесення бітів контролю парності переміщає K+qx+y+1-ий біт коду з бітів контролю парності, які є бітами коду з К+1-ого до К+м-ого LDPC-коду, в позицію К+Ру+х+1-ого біта коду.

6. Пристрійобробки даних за будь-яким з пп. 1-3, який відрізняється тим, що додатково містить:

засіб перестановки, призначений для здійснення процесу перестановки бітів LDPC-коду, щоб декілька бітів коду, які відповідали значенню 1 і які містяться в будь-якому довільному рядку вказаної перевірочної матриці LDPC-коду, не містилися в одному і тому ж символі.

7. Пристрій обробки даних за будь-яким з пп. 1-3, який відрізняється тим, що в ньому

LDPC-код є LDPC-кодом, в якому інформаційна матриця має циклічну структуру, при цьому інформаційна матриця є частиною перевірочної матриці LDPC-коду і відповідає інформаційним бітам LDPC-коду,

пристрій обробки даних додатково містить засіб перестановки, призначений для здійснення прокручування стовпчиків, яке полягає в зміні позиції початку запису при записі бітів LDPC-коду у напрямку стовпчиків для кожного стовпчика вказаної пам'яті, вказаний процес є процесом, направленим на перестановку бітів LDPC-коду.

8. Пристрій обробки даних за п. 7, який відрізняється тим, що у ньому

матриця контролю парності перевірочної матриці LDPC-коду, яка відповідає перевірочній матриці LDPC-коду, має псевдоциклічну структуру, в якій частина матриці контролю частковості має циклічну структуру, а інша частина отримана заміною стовпчиків.

9. Пристрій обробки даних за п. 8, який відрізняється тим, що у ньому

матриця контролю парності має ступінчасту структуру, яка перетворюється на псевдоциклічну структуру заміною стовпчиків.

10. Пристрій обробки даних за п. 9, який відрізняється тим, що у вказаному засобі перестановки здійснюють прокручування стовпчиків для LDPC-коду після рознесення бітів контролю парності.

11. Пристрій обробки даних за п. 10, який відрізняється тим, що у ньому

кількість М бітів контролю парності LDPC-коду є числом, відмінним від простого, і в якому

два дільники кількості М бітів контролю парності, які відрізняються від 1 і М і добуток яких дорівнює кількості М бітів контролю парності, позначено через Р і q,

кількість інформаційних бітів LDPC-коду позначають через К,

ціле число, більше або рівне 0, але менше Р, позначають через х, і

інше ціле число, більше або рівне 9, але менше q, позначають через у,

вказаний засіб рознесення бітів контролю парності переміщає K+qx+y+1-ий біт коду з бітів контролю парності, які є бітами коду з К+1-ого по К+м-ий LDPC-коду, в позицію К+Ру+х+1-ого біта коду.

12. Пристрій обробки даних за п. 7, який відрізняється тим, що у ньому

LDPC-код є LDPC-кодом, який має довжину N коду, яка дорівнює 64 800 бітам, і який визначений в стандарті DVB-S.2 або стандарті DVB-T.2 і

m бітів є 12 бітами і ціле число b дорівнює 1 і, крім того,

дванадцять бітів LDPC-коду перетворюють на дванадцять з 4 096 сигнальних точок, визначених в заздалегідь заданому способі модуляції, а

вказана пам'ять містить дванадцять стовпчиків, призначених для зберігання 12×1 бітів у напрямку рядків і зберігання 64 800/(12×1) бітів у напрямку стовпчиків,

у вказаному засобі перестановки

встановлюють, коли адреса верхньої позиції вказаної пам'яті у напрямку стовпчиків є 0 і адреси кожної позиції вказаної пам'яті у напрямку стовпчиків є цілими числами, розташованими в порядку зростання,

позицію початку запису в перший стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 0,

встановлюють позицію початку запису в другий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 0,

встановлюють позицію початку запису в третій стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 2,

встановлюють позицію початку запису в четвертий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 2,

встановлюють позицію початку запису в п'ятий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 3,

встановлюють позицію початку запису в шостий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 4,

встановлюють позицію початку запису в сьомий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 4,

встановлюють позицію початку запису у восьмий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 5,

встановлюють позицію початку запису в дев'ятий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 5,

встановлюють позицію початку запису в десятий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 7,

встановлюють позицію початку запису в одинадцятий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 8, і

встановлюють позицію початку запису в дванадцятий стовпчик з дванадцяти стовпчиків вказаної пам'яті, в позицію з адресою, яка дорівнює 9.

13. Спосіб обробки даних в пристрої обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду (коду з малою щільністю перевірок на парність) з довжиною N коду записують у напрямку стовпчиків вказаної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC-коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків вказаної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків вказаної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, вказаний спосіб обробки даних передбачає етап заміни, який призначений для заміни mb бітів коду, так що біти коду після заміни утворюють біти символів;

правилом співставлення є правило, яке визначає,

коли групи, в які повинні бути згруповані біти коду залежно від вірогідності помилки в бітах коду, використовують як групи бітів коду і групи, в які повинні бути згруповані біти символу залежно від вірогідності помилки в бітах символу, використовують як групи бітів символу,

набір груп, який є комбінацією будь-якої групи бітів коду і будь-якої групи бітів символу, з якими співставлена група бітів коду, і

кількість бітів в кожній з груп бітів коду і кожній з груп бітів символу набору груп.

14. Спосіб обробки даних в пристрої обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду (коду з малою щільністю перевірок на парність) з довжиною N коду записують у напрямку стовпчиків вказаної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC- коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків вказаної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків вказаної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, вказаний спосіб обробки даних передбачає етап заміни, який призначений для заміни mb бітів коду, так що біти коду після заміни утворюють біти символів;

LDPC-код є LDPC-кодом, який визначений в стандарті DVB-S.2 або стандарті DVB-T.2 і який має довжину N коду, яка дорівнює 64 800 бітам;

правилом співставлення є правило, яке визначає,

коли групи, в які повинні бути згруповані біти коду залежно від вірогідності помилки в бітах коду, використовують

як групи бітів коду і групи, в які повинні бути згруповані біти символу залежно від вірогідності помилки в бітах символу, використовують як групи бітів символу

набір груп, який є комбінацією будь-якої групи бітів коду і будь-якої групи бітів символу, з якими співставлена група бітів коду, і

кількість бітів в кожній з груп бітів коду і кожній з груп бітів символу набору груп;

причому m бітів є 12 бітами і ціле число b дорівнює 1 і, крім того, 10 бітів коду перетворюють на один символ в 212 або 4 096 сигнальних точок,

12×1 бітів коду згруповані в три групи бітів коду, а

12×1 бітів символу згруповані в шість груп бітів символу;

правило співставлення визначає, що

один біт коду групи бітів коду, яка є кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є п'ятою кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є другою кращою з погляду вірогідності виникнення помилки, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є третьою кращою з погляду вірогідності виникнення помилок, що

два біти коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з двома бітами символу групи бітів символу, яка є четвертою кращою з погляду вірогідності виникнення помилки, що

один біт коду групи бітів коду, яка є другою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є шостою кращою з погляду вірогідності виникнення помилки, що

один біт коду групи бітів коду, яка є третьою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є п'ятою кращою з погляду вірогідності виникнення помилки, і що

один біт коду групи бітів коду, яка є третьою кращою з погляду вірогідності виникнення помилки, співставляють з одним бітом символу групи бітів символу, яка є шостою кращою з погляду вірогідності виникнення помилки.

15. Спосіб обробки даних в пристрої обробки даних, що містить

пристрій рознесення бітів контролю парності, призначений для рознесення бітів контролю парності LDPC-коду (код з малою щільністю перевірок на парність), на позиції інших бітів контролю парності,

пристрій прокручування стовпців, призначений для прокручування стовпців для LDPC-коду, отриманого з пристрою рознесення бітів контролю парності, та

демультиплексор, що містить пам'ять та засіб заміни, та призначений для заміни позицій двох або більшої кількості кодових розрядів коду LDPC, отриманого в пристрої прокручування стовпців, для отримання коду LDPC, в якому:

коли біти LDPC-коду (коду з малою щільністю перевірок на парність) з довжиною N коду записують у напрямку стовпчиків зазначеної пам'яті, яка призначена для зберігання бітів коду у напрямку рядків і напрямку стовпчиків, і m бітів LDPC-коду, зчитані у напрямку рядків, вважають одним символом і, крім того,

заздалегідь задане позитивне ціле число позначають через b,

у вказаній пам'яті зберігають mb бітів у напрямку рядків і зберігають N/(mb) бітів у напрямку стовпчиків;

біти LDPC-коду записують у напрямку стовпчиків вказаної пам'яті і зчитують у напрямку рядків;

при цьому mb бітів коду, зчитаних у напрямку рядків вказаної пам'яті, вважають b символами,

відповідно до правила співставлення, призначеного для співставлення бітів LDPC-коду і бітів символу, які представляють символи, вказаний спосіб обробки даних передбачає етап заміни, який призначений для заміни mb бітів коду, так що біти коду після заміни утворюють біти символів;

LDPC-код є LDPC-кодом, який визначений в стандарті DVB-S.2 або стандарті DVB-T.2 і який має довжину N коду, яка дорівнює 64 800 бітам і швидкість кодування, яка дорівнює 5/6;

m бітів є 12 бітами і ціле число b дорівнює 1;

12 бітів коду перетворюють на один символ в одну з 4 096 сигнальних точок, визначених в 4096-ти позиційній КАМн;

вказана пам'ять містить 12 стовпчиків, призначених для зберігання 12×1 бітів у напрямку рядків і зберігання 64 800/(12×1) бітів у напрямку стовпчиків;

на вказаному етапі заміни здійснюють,

причому і+1-ий біт, починаючи з самого старшого біта серед 12×1 бітів коду, які були зчитані у напрямку рядків із пам'яті, позначають через біт bі та і+1-ий біт, починаючи з самого старшого біта серед 12×1 бітів одного символу, позначають через біт уі, відповідно до правила співставлення,

заміну з метою співставлення

біта b0 і біта у8,

біта b1 і біта у0,

біта b2 і біта у6,

біта b3 і біта у1,

біта b4 і біта у4,

біта b5 і біта y5,

біта b6 і біта у2,

біта b7 і біта у3,

біта b8 і біта у7,

біта b9 і біта у10,

біта b10 і біта у11 і

біта b11 і біта у9.

Текст