Відбивач струму

Номер патенту: 102959

Опубліковано: 25.11.2015

Автори: Гарнага Володимир Анатолійович, Богомолов Сергій Віталійович, Філіпчук Віталій Сергійович, Азаров Олексій Дмитрович

Формула / Реферат

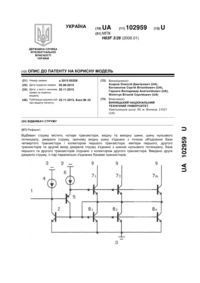

Відбивач струму, який містить чотири транзистори, вхідну та вихідну шини, шину нульового потенціалу, джерело струму, причому вхідну шину з'єднано з точкою об'єднання бази четвертого транзистора і колектором першого транзистора, емітери першого, другого транзисторів та другий вихід джерела струму з'єднано з шиною нульового потенціалу, база першого та другого транзисторів з'єднано з колектором другого транзистора, який відрізняється тим, що введено друге джерело струму, перший вхід якого з'єднано з емітером першого транзистора, другий вхід з'єднано з шиною нульового потенціалу, n пар паралельно з'єднаних базами транзисторів, де n=2…5, які з'єднано з точкою об'єднання бази другого та колектором першого транзисторів, а також з емітером першого транзистора, а колектори m, де m=2…5, транзисторів з'єднано з вихідною шиною.

Текст

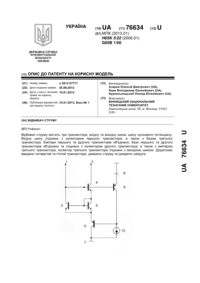

Реферат: Відбивач струму містить чотири транзистори, вхідну та вихідну шини, шину нульового потенціалу, джерело струму, причому вхідну шину з'єднано з точкою об'єднання бази четвертого транзистора і колектором першого транзистора, емітери першого, другого транзисторів та другий вихід джерела струму з'єднано з шиною нульового потенціалу, база першого та другого транзисторів з'єднано з колектором другого транзистора. Введено друге джерело струму, n пар паралельно з'єднаних базами транзисторів. UA 102959 U (54) ВІДБИВАЧ СТРУМУ UA 102959 U UA 102959 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до аналогової техніки і може бути використана в двотактних підсилювальних схемах. Відомо відбивач струму Уілсона (Титце У. Токовое зеркало Вильсона // Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том 1: Пер. с нем. - М.: ДМК Пресс, 2008. - с. 342344), який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а 15 також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною. Недоліком є обмежені функціональні можливості. За прототип вибраний відбивач струму (патент України № 88149, м.кл. Н03К 5/22, опубл. 11.03.2014), який містить чотири транзистори, вхідну та вихідну шини, шину нульового потенціалу, джерело струму, причому вхідну шину з'єднано з колектором першого транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, вхідну шину з'єднано з базою четвертого транзистора, емітер четвертого транзистора з'єднано з шиною нульового потенціалу, колектор четвертого транзистора з'єднано з базою третього транзистора, а також з другим виводом джерела струму, перший вивід джерела струму з'єднано з шиною нульового потенціалу, колектор третього транзистора з'єднано з базою та колектором другого транзистора, а також з базою першого транзистора, емітер третього транзистора з'єднано з вихідною шиною. Недоліком є низький вихідний опір пристрою, що обмежує функціональні можливості. В основу корисної моделі поставлено задачу створення такого відбивача струму, в якому за рахунок введення нових елементів та зв'язків між ними, підвищується вихідний опір, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у відбивач струму, який містить чотири транзистори, вхідну та вихідну шини, шину нульового потенціалу, джерело струму, причому вхідну шину з'єднано з точкою об'єднання бази першого транзистора і колектором другого транзистора, емітери другого, четвертого транзисторів та другий вихід джерела струму з'єднано з шиною нульового потенціалу, база четвертого та другого транзисторів з'єднано з колектором четвертого транзистора, введено друге джерело струму, перший вхід якого з'єднано з емітером першого транзистора, другий вхід з'єднано з шиною нульового потенціалу, n пар паралельно з'єднаних базами транзисторів, де n = 2...5, які з'єднано з точкою об'єднання бази другого та колектором першого транзисторів, а також з емітером першого транзистора, а колектори m, де m = 2...5, транзисторів з'єднано з вихідною шиною. На кресленні представлено схему відбивача струму. Пристрій містить вхідну шину 1, з'єднану з точкою об'єднання бази першого 5 і з колектором другого 2 транзисторів, емітери другого 2 транзистора, транзисторів 8 1-8n, де n = 2...5, та другий вихід першого 4 та другого 6 джерел струму з'єднано з шиною нульового потенціалу 3, база другого 2 транзистора об'єднана з колектором першого 5 транзистора, бази транзисторів 8 1-8n з'єднано з точкою об'єднання бази другого 2 та колектора першого 5 транзисторів, бази транзисторів 71-7m, де m = 2...5, з'єднано з емітером першого 5 транзистора, бази транзисторів 81-8n з'єднано з точками об'єднання колекторів та емітерів 81-8n та 71-7m транзисторів відповідно, колектори транзисторів 71-7m з'єднано з вихідною шиною 9. Пристрій працює таким чином. Вхідний сигнал у вигляді струму поступає на вхідну шину 1. Якщо вхідний струм збільшується, то перший 5 транзистор привідкривається, при цьому збільшується колекторний струм першого 5 транзистора, а напруга на колекторі першого 5 транзистора падає, а транзистори 71-7m привідкриваються, при цьому збільшується колекторний та емітерний струм транзисторів 71-7m. Збільшення колекторного струму транзисторів 71-7m передається через відбивач струму, побудований на другому 2 та 81-8n транзисторах на вхід схеми, тобто збільшується колекторний струм другого 2 транзистора, що компенсує збільшення вхідного струму. Якщо вхідний струм зменшується, то перший 5 транзистор призакривається, і зменшується його колекторний струм, а напруга на колекторі першого 5 транзистора зростає, при цьому транзистори 71-7m призакриваються, зменшується колекторний та еміторний струм транзисторів 71-7m. Зменшення колекторного струму транзисторів 71-7m передається через відбивач струму, 1 UA 102959 U 5 10 15 20 25 побудований на другому 2 та 81-8n транзисторах на вхід схеми, тобто зменшується колекторний струм другого 2 транзистора, що компенсує зменшення вхідного струму. l Коефіцієнт передачі по струму буде дорівнювати K 1 вих 1 , де K 1 - коефіцієнт передачі lвх по струму, lвих - вихідний сигнал у вигляді струму, lвх - вхідний сигнал у вигляді струму, і залежить від коефіцієнту передачі по струму, побудованого на другому 2 та 8 1-8n транзисторах. Перший 5 транзистор і вхідна шина 1 утворюють вхід схеми. Транзистори 7 1-7m забезпечують високий вихідний опір схеми. Емітерний струм з транзисторів 71-7m поступає на вихідну шину 9. Перше джерело струму 4 задає струм робочої точки колектора другого 2 і бази першого 5 транзисторів. Друге джерело струму 6 задає емітерний струм першого 5 і базові струми 71-7m транзисторів. Оптимальне число паралельно з'єднаних базами транзисторів 71-7m та 81-8n дорівнює п'яти, тому що при їх надмірній кількості буде зменшуватися емітерний струм першого 5 транзистора. Шина нульового потенціалу 3 встановлює необхідний рівень напруги для живлення схеми. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Відбивач струму, який містить чотири транзистори, вхідну та вихідну шини, шину нульового потенціалу, джерело струму, причому вхідну шину з'єднано з точкою об'єднання бази четвертого транзистора і колектором першого транзистора, емітери першого, другого транзисторів та другий вихід джерела струму з'єднано з шиною нульового потенціалу, база першого та другого транзисторів з'єднано з колектором другого транзистора, який відрізняється тим, що введено друге джерело струму, перший вхід якого з'єднано з емітером першого транзистора, другий вхід з'єднано з шиною нульового потенціалу, n пар паралельно з'єднаних базами транзисторів, де n=2…5, які з'єднано з точкою об'єднання бази другого та колектором першого транзисторів, а також з емітером першого транзистора, а колектори m, де m=2…5, транзисторів з'єднано з вихідною шиною. Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 2

ДивитисяДодаткова інформація

Назва патенту англійськоюCurrent reflector

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych, Harnaha Volodymyr Anatoliiovych, Filipchuk Vitalii Serhiiovych

Назва патенту російськоюОтражатель тока

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич, Гарнага Владимир Анатольевич, Филипчук Виталий Сергеевич

МПК / Мітки

МПК: H03F 3/26

Код посилання

<a href="https://ua.patents.su/4-102959-vidbivach-strumu.html" target="_blank" rel="follow" title="База патентів України">Відбивач струму</a>

Попередній патент: Спосіб санації та термореновації трубопроводів теплових мереж

Наступний патент: Спосіб прогнозування дефіциту міді у вагітної жінки з захворюванням, яке передається статевим шляхом

Випадковий патент: Спосіб отримання адсорбційного фільтрувального матеріалу