Відбивач струму

Номер патенту: 89902

Опубліковано: 12.05.2014

Автори: Азаров Олексій Дмитрович, Попенко Володимир Михайлович, Павлов Сергій Володимирович, Богомолов Сергій Віталійович

Формула / Реферат

Відбивач струму, який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, який відрізняється тим, що у нього введено п'ять транзисторів, джерело струму та шину нульового потенціалу, колектор четвертого транзистора з'єднано з вихідною шиною, емітер четвертого транзистора з'єднано з колектором третього транзистора, бази четвертого та шостого транзисторів об'єднано та з'єднано з колектором шостого транзистора, а також з другим виводом джерела струму, перший вивід джерела струму з'єднано з шиною нульового потенціалу, емітер шостого транзистора з'єднано з колектором сьомого транзистора, а також з базою сьомого транзистора, колектор п'ятого транзистора з'єднано з базою третього транзистора, бази п'ятого та восьмого транзисторів об'єднано і з'єднано з колектором восьмого транзистора, а також з емітером сьомого транзистора, емітери п'ятого та восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу.

Текст

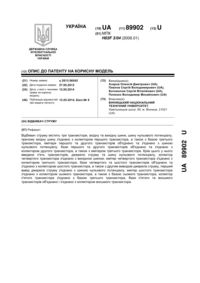

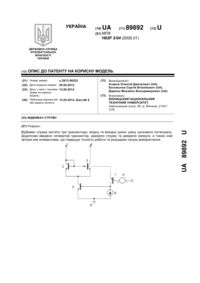

Реферат: Відбивач струму містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора. Крім цього у нього введено п'ять транзисторів, джерело струму та шину нульового потенціалу, колектор четвертого транзистора з'єднано з вихідною шиною, емітер четвертого транзистора з'єднано з колектором третього транзистора, бази четвертого та шостого транзисторів об'єднано та з'єднано з колектором шостого транзистора, а також з другим виводом джерела струму, перший вивід джерела струму з'єднано з шиною нульового потенціалу, емітер шостого транзистора з'єднано з колектором сьомого транзистора, а також з базою сьомого транзистора, колектор п'ятого транзистора з'єднано з базою третього транзистора, бази п'ятого та восьмого транзисторів об'єднано і з'єднано з колектором восьмого транзистора. UA 89902 U (54) ВІДБИВАЧ СТРУМУ UA 89902 U UA 89902 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до аналогової техніки і може бути використана в двотактних підсилювальних схемах. За аналог вибрано відбивач струму (U.S. Patent Saller at al.; Patent Number: 4,766,367; Appl. №.: 75,140; Date of Patent-Aug. 23, 1988), який містить шину нульового потенціалу, вхідну та вихідну шини, чотири транзистори та джерело струму, причому вхідну шину з’єднано з колектором першого транзистора, а також з базою третього транзистора, другий вивід джерела струму з'єднано з емітером третього транзистора, а також з базою четвертого транзистора, перший вивід джерела струму з'єднано з шиною нульового потенціалу, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, а також і колектором третього транзистора, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером четвертого транзистора, колектор четвертого транзистора з'єднано з вихідною шиною. Недоліком аналога є низька точність роботи. За прототип вибрано відбивач струму Уілсона (Wilson, G. R. (December 1968), "A Monolithic Junction FET-n-p-n Operational Amplifier", IEEE J. Solid State Circuits SC-3 (4): 341-348, doi: 10.1109/JSSC.1968 1049922), який містить три транзистори, вхідну та вихідну шини, шин) нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною. Недоліком прототипу є низька навантажувальна здатність. В основу корисної моделі поставлено задачу створення відбивача струму, в якому за рахунок введення нових елементів та зв'язків між ними, за умови, що генератор вхідного сигналу має обмежений опір, підвищується точність роботи, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у відбивач струму, який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, введено п'ять транзисторів, джерело струму га шину нульового потенціалу, причому колектор четвертого транзистора з'єднано з вихідною шиною, емітер четвертого транзистора з'єднано з колектором третього транзистора, бази четвертого та шостого транзисторів об'єднано та з'єднано з колектором шостого транзистора, а також з другим виводом джерела струму, перший вивід джерела струму з'єднано з шиною нульового потенціалу, емітер шостого транзистора з'єднано з колектором сьомого транзистора, а також з базою сьомого транзистора, колектор п'ятого транзистора з'єднано з базою третього транзистора, бази п'ятого та восьмого транзисторів об'єднано і з'єднано з колектором восьмого транзистора, а також з емітером сьомого транзистора, емітери п'ятого та восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу. На кресленні представлено схему відбивача струму. Пристрій містить вхідну шину 1, з'єднану з колектором першого 2 транзистора, а також з базою третього 5 транзистора, емітери першого 2 та другого 6 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 8, бази першого 2 та другого 6 транзисторів об'єднано та з'єднано з колектором другого 6 транзистора, а також з емітером третього 5 транзистора, колектор четвертого 4 транзистора з'єднано з вихідною шиною 3, емітер четвертого 4 транзистора з'єднано з колектором третього 5 транзистора, бази четвертого 4 та шостого 10 транзисторів об'єднано та з'єднано з колектором шостого 10 транзистора, а також з другим виводом джерела струму 9, перший вивід джерела струму 9 з'єднано з шиною нульового потенціалу 8, емітер шостого 10 транзистора з’єднано з колектором сьомого 11 транзистора, а також з базою сьомого 1 і транзистора, колектор п'ятого 7 транзистора з'єднано з базою третього 5 транзистора, бази п'ятого 7 та восьмого 12 транзисторів об'єднано і з'єднано з колектором восьмого 12 транзистора, а також з емітером сьомого 11 транзистора, емітери п'ятого 7 та восьмого 12 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 8. Пристрій працює таким чином. Вхідний сигнал у вигляді струму надходить на вхідну шину 1. Якщо вхідний струм втікає у схему, то базовий струм третього 5 транзистора збільшується, що призводить до його при відкривання та збільшення колекторного струму. При цьому збільшується як емітерний, так і базовий струми четвертого 4 транзистора. Збільшення базового струму четвертого 4 1 UA 89902 U 5 10 15 транзистора через шостий 10, сьомий 11 та восьмий 12 транзистори передається в базу п'ятого 7 транзистора, що призводять до його при відкривання. Внаслідок цього збільшується наскрізний струм через його колекторний та емітерний переходи, який, у свою чергу, врівноважує значення базового струму третього 5 транзистора. Якщо вхідний струм витікає із схеми, то базовий струм третього 5 транзистора зменшується, що призводить до його при закривання та зменшення колекторного струму. При цьому зменшується як емітерний, так і базовий струми четвертого 4 транзистора. Зменшення базового струму четвертого 4 транзистора через шостий 10, сьомий 11 та восьмий 12 транзистори передається в базу п'ятого 7 транзистора, що призводить до його при закривання. Внаслідок цього зменшується наскрізний струм через його колекторний та емітерний переходи, який, у свою чергу, врівноважує значення базового струму третього 5 транзистора. Вихідна шина 3 відслідковує зміну струму на колекторі четвертого 4 транзистора. Джерело струму 9 задає робочий струм для шостого 10, сьомого 11 та восьмого 12 транзисторів. Шина нульового потенціалу 8 задає необхідний рівень напруги для живлення схеми. Четвертий 4, п'ятий 7, шостий 10, сьомий 11 та восьмий 12 транзистори утворюють коло від'ємною зворотного зв'язку між базою та колектором третього 5 транзистора, Введення від'ємного зворотного зв'язку забезпечує збільшення вихідного опору схеми за рахунок компенсації зміни базового струму третього 5 транзистора. 20 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 25 30 35 Відбивач струму, який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, який відрізняється тим, що у нього введено п'ять транзисторів, джерело струму та шину нульового потенціалу, колектор четвертого транзистора з'єднано з вихідною шиною, емітер четвертого транзистора з'єднано з колектором третього транзистора, бази четвертого та шостого транзисторів об'єднано та з'єднано з колектором шостого транзистора, а також з другим виводом джерела струму, перший вивід джерела струму з'єднано з шиною нульового потенціалу, емітер шостого транзистора з'єднано з колектором сьомого транзистора, а також з базою сьомого транзистора, колектор п'ятого транзистора з'єднано з базою третього транзистора, бази п'ятого та восьмого транзисторів об'єднано і з'єднано з колектором восьмого транзистора, а також з емітером сьомого транзистора, емітери п'ятого та восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу. 2 UA 89902 U Комп’ютерна верстка С. Чулій Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Автори англійськоюAzarov Oleksii Dmytrovych, Pavlov Serhii Volodymyrovych, Bohomolov Serhii Vitaliiovych

Автори російськоюАзаров Алексей Дмитриевич, Павлов Сергей Владимирович, Богомолов Сергей Витальевич

МПК / Мітки

МПК: H03F 3/04

Код посилання

<a href="https://ua.patents.su/5-89902-vidbivach-strumu.html" target="_blank" rel="follow" title="База патентів України">Відбивач струму</a>

Попередній патент: Відбивач струму

Наступний патент: Відбивач струму

Випадковий патент: Кристалізатор