Пристрій для контролю цифрових об’єктів

Номер патенту: 12280

Опубліковано: 25.12.1996

Автори: Чашечніков Валерій Іванович, Михавчук Михайло Іванович, Дем'янчук Тарас Михайлович

Формула / Реферат

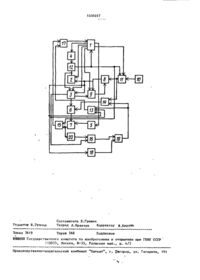

Устройство для контроля цифровых объектов, содержащее управляющий вычислительный блок, счетчик адреса памяти, блок памяти тестов, регистр адреса тестовой комбинации, регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, счетчик числа повторения тестовых комбинаций, первый элемент ЗИ, группу элементов ЗИ, генератор тактовой частоты и схему сравнения, первый, второй входы и выход которой соединены соответственно с выходом регистра адреса тестовой комбинации, выходом счетчика адреса памяти, соединенными с первым входом первого элемента ЗИ, первым входом прерывания управляющего вычислительного блока, первый, второй и третий информационные выходы которого соединены с информационными входами регистра адреса тестовой комбинации, счетчика адреса памяти, регистра выходной тестовой комбинации, первый, второй и третий управляющие выходы управляющего вычислительного блока соединены соответственно с первым входом выбора блока памяти тестов, первым входом группы элементов ЗИ, вторым входом первого элемента ЗИ, третий вход которого соединен с выходом генератора тактовой частоты, а выход - с входом суммирования счетчика числа повторения тестовой комбинации, выход переполнения которого соединен с входом суммирования счетчика адреса памяти, вторым входом группы элементов ЗИ, вторым входом выбора блока памяти тестов, первая информационная группа выходов которого соединена с третьими входами группы элементов ЗИ, вторая информационная группа выходов является выходом устройства, подключенного к информационным входам контролируемого объекта, адресный вход блока памяти тестов соединен с выходом счетчика адреса памяти, информационный вход счетчика числа повторения тестовой комбинации соединен с выходами группы элементов ЗИ, первая и вторая группы входов амплитудного дискриминатора соединены соответственно с входами устройства, к которым подключены выходы контролируемого объекта и выходы регистра выходной тестовой комбинации, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции, в него введены второй элемент ЗИ, первый, второй, третий элементы И, элемент НЕ, формирователь импульса, триггер и элемент ИЛИ, первый, второй входы и выход которого соединены соответственно с выходом второго элемента И, выходом второго элемента ЗИ, вторым входом прерывания управляющего вычислительного блока, первый и второй входы и выход первого элемента И соединены соответственно с выходом первого элемента ЗИ, первым входом второго элемента ЗИ и выходом триггера, синхровыходом устройства, который подключается к синхровходу контролируемого объекта, первый и второй входы второго элемента И подключены соответственно к выходу схемы сравнения, выходу амплитудного дискриминатора и входу элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и третьим информационным выходом блока памяти, вход формирователя импульса соединен с третьим входом второго элемента ЗИ и выходом переполнения счетчика числа повторения тестовой комбинации, вход сброса и вход установки триггера соединены соответственно с выходом

третьего элемента И и выходом формирователя импульса.

Текст

СОЮЗ СОВЕТСНИХ СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК (19) SU(1111608697 (51)5 G..06 F А1 15/46 ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ ПРИ ПЧНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ "(21) 4603823/24-24 I (22) 01.08.88 (46) 2 3 . 1 1 . 9 0 . Кюл. Ь 43 * (72) Т.М.Демьянчук, В.И.Чашечников и М.И.Михавчук (53) 621.396 (088.8) (56) Авторское свидетельство СССР № 711543, кл. G 05 В 23/02, 1978. Авторское свидетельство СССР №.377738, кл. G 05 В 23/02, 1970. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ОБЪЕКТОВ (57) Изобретение относится к автоматизированным системам контроля и может быть использовано при контроле больших и сверхбольших интегральных схем на МОП-структурах. Цель изобретения - расширение функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции. Устройство содержит генератор тактовых импульсов, управлянщий вычислительный блок, группу элементов, блок памяти тестовj счетчик адреса памяти, регистр адреса тестовой комбинации, схему сравнения, регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, счетчик числа повторения тестов комбинации, два элемента 3 И, три элемента И, элемент НЕ, элемент ИЛИ, формирователь импульса, триггер. Принцип действия устройства состоит в блокировке синхроимпульсов, поступающих на вход синхронизации объекта контроля в тот момент, когда его состояние достигает значения, записанного в регистре выходной тестовой комбинации. Объект считается годным, если он достигает заданного состояния за время, меньшее указанного в счетчике числа повторений тестовых комбинаций. 1 ил. if) С о Изобретение относится к автоматизированным системам контроля и может быть применено при контроле больших интегральных схем (ВИС) и сверхбольших интегральных схем (СБИС) на МОПструктурах. Цель изобретения - расширение функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции. Иа чертеже приведена функциональ" ная схема устройства, Устройство содержит управляющий вычислительный блок 1, счетчик 2 адреса памяти, блок 3 памяти тестов, регистр 4 адреса тестовой комбинации, регистр 5 выходной тестовой комбина'ции, контролируемый объект 6, многоканальный амплитудный дискриминатор 7, счетчик 8 числа повторения тестовых комбинаций, группу 9 элементов ЗИ, * * генератор 10 тактовой частоты, первый элемент ЗИ 11, схему 12 сравнения, второй элемент ЗИ 13, три элемента И 14-16, элемент ИЛИ 17, формирователь РПФ-К! CD I 1608697 , 18 импульса, триггер 19 и элемент і I НЕ 20. і Устройство работает следующим образом. В исходное состояние устройство устанавливается сигналом "Сброс" (не показан), при этом в исходное состояние устанавливаются счетчики 2 и 8, триггер 19 и управляющий вычислитель- (0 ный блок 1. Управляющий вычислительный блок 1 по команде "Пуск" передает в счетчик 2 адреса памяти начальный адрес ячейки блока 3, в которой хранится первая (5 тестовая комбинация для контролируемого типа объекта 6. В регистр 4 адреса тестовой комбинации записывается адрес тестовой комбинации, на которой требуется зафиксировать выходные 20 сигналы контролируемого объекта 6. В регистр 5 выходной тестовой комбинации из запоминающего устройства выходных тестовых комбинаций, входящего в состав управляющего вычисли25 тельного блока 1, поступает выходная тестовая комбинация, соответствующая выходным сигналам контролируемого объекта 6 на указанном в регистре 4 адреса контролируемой тестовой комбинации номере комбинации. Регистр 5 30 выходной тестовой комбинации соединен с многоканальным амплитудным дискриминатором 7 для задания порога каждого канала дискриминатора. л мент ЗИ 11. При запопненни сч.етчика 8 наращивается на " 1 " счетчик 2 и через формирователь 18 импульса по заднему фронту импульса устанавливается в исходное состояние триггер 19. При этом запрашивается блок 3 по следующему адресу и открывается элемент И для записи в счетчик 8 следующей тестовой комбинации. На требуемом номере цикла (при равенстве адресов в счетчике 2 и регистре 4) схема 12 сравнения запрещает прохождение тактовых импульсов на счетчик 8, закрывая элемент ЗИ 11, и подает стробирующий импульс на элемент И 15, разрешая поступление сигнала неисправности контролируемого объекта 6 на управляющий вычислительный блок 1 с выхода многоканального амплитудного дискриминатора 7. При необходимости исследований выходных сигналов следующей тестовой комбинации указанный цикл повторяется. Если контролируемый объект 6 является объектом с произвольным временем выполнения операции, то в дополнительный разряд необходимой ячейки блока 3 записывается сигнал разрешения автоматической синхронизации высокого логического уровня. При считывании данной ячейки блока 3 на входы контролируемого объекта 6 подаются * заданные входные воздействия, а максимальное число циклов (максимальное 35 необходимое количество тактовых имНа блок 3 из управляющего вычиспульсов генератора 10, поступающее лительного блока 1 поступает импульс на вход объекта 6 для установки запроса. В каждой ячейке блока 3 выобъекта в исходное состояние) переделены: один ряд разрядов, в котором писывается в обратном коде в счетчик записывается число Циклов генератора 40 8 числа повторения тестовых ком10, в течение которых на проверяемую бинаций через группу 9 элементов ЗИ. схему должна поступать данная тестоНа счетный вход счетчика 8 подаются вая комбинация входных воздействий; импульсы с генератора 10 через эледополнительный разряд, в котором замент ЗИ 11. Кроме того, эти импульсы писывается сигнал разрешения для вклю45 через элемент И 14 поступают на вточения режима автоматической синхророй вход контролируемого объекта 6. низации работы контролируемого объекта 6 с системой контроля. При совпадении выходной тестовой комбинации объекта 6 с записанной При считывании ячейки блока 3 на исходной тестовой комбинацией в ревходы контролируемого объекта 6 пода 50 гистре 5 с выхода многоканального ются заданные входные воздействия, амплитудного дискриминатора 7 через а число циклов, в течение которых элемент НЕ 20 и элемент И 16 на триг-' данные воздействия должны подаваться гер 19 поступает сигнал, изменяющий на контролируемый объект, переписыпо переднему фронту его состояние. ваются в обратном коде в счетчик 8 55 При этом сигналом низкого уровня с числа повторения тестовых комбинавыхода триггера 19 запрещается по- х ций через группу 9 элементов ЗИ. На ступление импульсов генератора 10 счетный вход счетчика 8 подаются на синхройход контролируемого объекимпульсы с генератора 10 через эле 1608697 6 та 6, так как последний выполнил памяти тестов, первая информационная заданную операцию. При заполнении группа выходов которого соединена счетчика 8 наращивается на "Г' счетс третьими входами группы элементов чик 2 и через формирователь 18 имЗИ, вторая информационная группа выпульса триггер 19 устанавливается в ходов является выходом устройства, исходное состояние. подключенного к информационным входам контролируемого объекта, адресЕсли при заполнении счетчика 8 ный вход блока памяти тестов соедитриггер 19 не изменил своего состоянен с выходом счетчика адреса памяти, ния (т.е., находится в исходном сос10 информационный вход счетчика числа тоянии) , то сигнал с выхода счетчика . повторения тестовой комбинации сое8 через элемент ЗИ 13 и элемент ШПЇ динен с выходами группы элементов ЗИ, 17 поступает на вход управляющего первая и вторая группы входов ампливычислительного блока 1, сигнализиJ5 тудного дискриминатора соединены соруя о неисправности в контролируемом ответственно с входами устройства, к объекте 6. которым подключены выходы контролируемого объекта и выходы регистра Ф о р м у л а и з о б р е т е н и я выходной тестовой комбинации, о тУстройство для контроля цифровых 2 0 л и ч а ю щ е е с я тем, что, с цеобъектов, содержащее управляющий вылью расширения функциональных возчислительный блок, счетчик адреса можностей путем обеспечения контроля памяти, блок памяти тестов, регистр объектов с произвольным временем выадреса тестовой комбинации, регистр_ полнения операции, в него введены втовыходной тестовой комбинации, много25 рой элемент ЗИ, первый, второй, третий канальный амплитудный дискриминатор, элементы И, элемент НЕ, формирователь счетчик числа повторения тестовых импульса, триггер и элемент ИЛИ, перкомбинаций, первый элемент ЗИ, групвый, второй входы и выход которого пу элементов ЗИ, генератор тактовой соединены соответственно с выходом частоты и схему сравнения, первый, Зо второго элемента И, выходом второго второй входы и выход которой соедиэлемента ЗИ, вторым входом прерывания нены соответственно с выходом реуправляюцего вычислительного блока, гистра адреса тестовой комбинации, первый и второй входы и выход первовыходом счетчика адреса памяти, соего элемента И соединены соответствендиненными с первым входом первого но с выходом первого элемента ЗИ, перэлемента ЗИ, первым входом прерывавым входом второго элемента ЗИ и выния управляющего вычислительного блоходом триггера, синхровыходом устройка, первый, второй и третий инфорства, который подключается к синхромационные выходы которого соединены входу контролируемого объекта, первый с информационными входами регистра и второй входы второго элемента И подадреса тестовой комбинации, счетчика ключены соответственно к выходу схемы адреса памяти, регистра выходной тес- 40 сравнения, выходу амплитудного дитовой комбинации, первый, второй и скриминатора и входу элемента НЕ, вытретий управляющие выходы управляюход которого соединен с первым входом щего вычислительного блока соединены третьего элемента И, второй вход косоответственно с первым входом выторого соединен с вторым входом втобгра блока памяти тестов, первым вхо- 45 рого элемента И и третьим информацидом группы элементов ЗИ, вторым вхоонным выходом блока памяти, вход фордом первого элемента ЗИ, третий вход мирователя импульса соединен с третькоторого соединен с выходом генератоим входом второго элемента ЗИ и выра тактовой частоты, а выход - с вхоходом переполнения счетчика числа дом суммирования счетчика числа по50 повторения тестовой комбинации, вход вторения тестовой комбинации, выход сброса и вход, установки триггера соепереполнения которого соединен с динены соответственно с выходом третьвходом суммирования счетчика адреса его элемента И и выходом формировав памяти, вторым входом группы элементеля импульса. тов ЗИ, вторым входом выбора блока 55 Г 1608697 Редактор Н.Тугсіда Составитель В.Гришин Техред А.Кравчук Корректор Н.Король Заказ 3619 Тираж 568 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР ' 113035, Москва, Ж-35, Раушская наб., д. 4/5 — — _ _ — — .. . _ _ — . _ — , . _ _ _ _ „ — . _ _ _ _ ——•._—_„.__ жг — . Производственно-издательский комбинат "Патент", г. 7 °Р°Ді ул. Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for control of digital objects

Автори англійськоюDemianchuk Taras Mykhailovych, Chashechnikov Valerii Ivanovych, Mykhavchuk Mykhailo Ivanovych

Назва патенту російськоюУстройство для контроля цифровых объектов

Автори російськоюДемьянчук Тарас Михайлович, Чашечников Валерий Иванович, Михавчук Михаил Иванович

МПК / Мітки

МПК: G06F 15/76

Мітки: контролю, об'єктів, цифрових, пристрій

Код посилання

<a href="https://ua.patents.su/4-12280-pristrijj-dlya-kontrolyu-cifrovikh-obehktiv.html" target="_blank" rel="follow" title="База патентів України">Пристрій для контролю цифрових об’єктів</a>

Попередній патент: Пластмасовий корпус для великих інтегральних схем

Наступний патент: Генератор тастатурного номеронабирача

Випадковий патент: Сфероїдний сонячний колектор