Вихідний блок тестера для контролю цифрових блоків

Номер патенту: 7993

Опубліковано: 26.12.1995

Автори: Вишняков Олександр Платонович, Вдовиченко Анатолій Олексійович, Павлів Дмитро Іванович

Формула / Реферат

(57) Выходной блок тестера для контроля цифровых блоков, содержащий первый триггер, элемент и шифратор логических состояний, вход которого является входом выходом блока для подключения к двунаправленному выводу объекта контроля, отличающийся тем, что в него введены выходной регистр, второй триггер, инвертор с открытым коллектором, элемент равнозначности и узел согласования нагрузки, содержащий входной регистр, два токозадающих элемента и два элемента развязки, причем первый и второй разрядные выходы входного регистра соединены с первыми выводами соответственно первого и второго токозадающих элементов и с анодами соответственно первого и второго элементов развязки, вторые выводы первого и второго токозадающих элементов подключены к шине логической единицы, выход первого триггера соединен с первым входом элемента равнозначности, через инвертор с открытым коллектором - с катодами первого и второго элементов развязки, со входом шифратора логических состояний и со вторым входом элемента равнозначности, выход которого соединен с первым входом элемента И, выход которого соединен со входом сброса первого триггера и с установочным входом второго триггера, выход которого является выходом сигнала "короткое замыкание" блока, первый и второй выходы шифратора логических состояний соединены с первым и вторым информационными входами выходного регистра, первый и второй разрядные выходы которого образуют информационные выходы блока, вход записи выходного регистра и второй вход элемента и образуют вход строба блока, информационный и тактовый входы первого триггера являются входом задания режима работы и тактовым входом блока соответственно, вход сброса второго триггера является входом сброса блока, первый и второй информационные входы входного регистра образуют входы задания нагрузки блока.

Текст

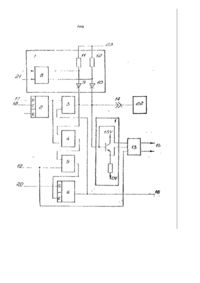

WMJ G 06 EJIZPQ, .G.QLEJ1/28 (ІЗ) C1 ПАТЕНТНЕ відомство НА ВИНАХІД (54) ВИХІДНИЙ БЛОК ТЕСТЕРА ДЛЯ КОНТРОЛЮ ЦИФРОВИХ ВЛОКІВ 1 (20)95280026. 15 09 93 (21)4842870/24, SU (22) 25 06 90 (46)26 12 95 Бюл № 4 (56) 1 Авторское свидетельство СССР N•822190,кп С 06 F 11/00 1979 2 Авторское свидетельство СССР № 1213444. кл С 01 R 31/28 1984 - прототип (71) Спеціальне проектно-конструкторське та технологічне бюро реле f автоматики [72) Вишняков Олександр Ппатонович, Вдо виченко Анатолій Олексійович, Павлів Дмитоо Іванович 73) Спец іальне конструкторське бюро 'РИТМ1 57) Выходной блок тестера для контроля дифровых блоков, содержащий первый тригер, элемент И шифратор логических состоіний, вход которого является входом выходом блока для подключения к даунапіавленному выводу объекта контроля, о т - л м а ю щ и й с я тем, что в него введены ыходной регистр, второй триггер, инвертор открытым коллектором, элемент равноначности и узел согласования нагрузки, со.ержащий входной регистр, два окозадзющих элемента и два элемента разязки, причем первый и второй разрядные ыходы входного регистра соединены с перыми выводами соответственно первого и торого токозэдающих элементов и с анода ми соответственно первого и второго элементов развязки, вторые выводы первого и второго токозадающих элементов подключены к шине логической единицы, выход первого триггера соединен с первым входом элемента равнозначности, через инвертор с открытым коллектором - с катодами первого и второго элементов развязки, со входом шифратора логических состояний и со вторым входом элемента равнозначности, выход которого соединен с первым входом элемента И, выход которого соединен со входом сброса первого триггера и с установочным входом второго триггера, выход которого является выходом сигнала "короткое замыкание" блока, первый и второй выходы шифратора логических состояний соединены с первым и вторым информационными входами выходного регистра, первый и второй разрядные выходы которого образуют информационные выходы блока, вход записи выходного регистра и второй вход элемента И образуют вход строба блока, информационный и тактовый входы первого триггера являются входом задания режима работы и тактовым входом блока соответственно, вход сброса второго триггера является входом сброса блока, первый и второй информационные входы входного регистра образуют входы задания нагрузки блока. Изобретение относится к вычислительэй технике и может использоваться в состаэ тестеров для контроля цифровых логических блоков ТТЛ, КМОП и других совместимых с ними по уровням сигналов. С > о 7993 Блок сод ержит ш ифратор 1 логических сос тояний, триггер 2, инвертор 3 с открытым коллектором, э лемент 4 равнозначнос ти, элемент И 5. триггер б. у зел 7 соглас ования нагрузки, вх одной регис тр 8, э лементы 9, 10 5 развязки, токозэд ающие э лементы 11, 12, выход ной регис тр 13, вход(вых од 14, информационные выход ы 15, выход 16 сигнала "короткое замыкание", вход 17 задания режима работы, тактовый вх од 18, вход 19 с тробз, 10 вход 20 с броса и вход ы 21 задания нагру зки. На чертеже показаны также объек т 22 и ш ина 23 логичес кой единицы. Выход ной блок работает с ледующим об разом. 15 Циклом проверки объекта контроля (ОК) 22 считаетс я фикс ированный поток цифровых пос лед овательнос тей, повторяющийся через опред еленные (обычно равные) промежу тки времени. При э том вых од ной блок 20 тес тера, подключенный к д вунаправленному выводу ОК 22, может работать как в режиме в ыдач и, так и в р еж им е п ри ем а информации. В режиме выд ачи на вх од 17 под аетс я 25 как " 1" , так и " 0", которые, прох од я через триггер 2 м инвертор 3 с открытым коллектором, опред еляют вход ные погические у ровни д ля ОК 22 с оответс твенно к ак " 0" и " 1". При э том "0" на вх од е 17 переводит инвер- 30 тор 3 в м пасс ивное с ос тояние, а у ровень " I формируетс я узлом 7. В режиме выд ачи опред еляетс я короткое замыкание дву направленного вывод а ОК, при котором сигналы на выход е триггера 35 2 и инвертора 3 совпад ают по уровню. В резу льтате на выходе э лемента 4 формиру ется уровень " 1", чго приводит при наличии с троба на входе 19 к установке триггера 6 в "1" и появлению сигнала на выход е 16 бпока. 40 Одновременно с игнал с выход а э лемен та И 5 ус танавливает в "0" триггер 2. По окончании с троба с игнал сброса с нимается, и в триггер 2 можно запис ывать информа цию со вход а 17. 45 В те моменты времени, когда по логике проверки дву направленный вх од ОК 22 д олжен перейти в реж им выд ачи, а вых одной блок - в режим приема информации, на вх од 17 полае~с я уровень "0" , инвертор 3 пере- 50 вод ится в пасс ивное с ос тояние и двоичная пос ледовательнос ть с выход а ОК 22 принимаетс я ш ифратором I. Значение третьего сос тояния на вх од е 4 шифратора 1 кодируется им как " 1, О , логий ческой ед иницы - как "1, -I и логического нуля - как "0, 0". Резу льтат фиксируется в регис тре 13 с помощью с троба на входе 19, мес тоположение которого вну три такта выдачи данных можно менять. На фиг. 2 показан фрагмент цифровой последовательнос ти (фиг.2,б) от ОК 22 и два примера пос тупления с троба. Ес ли фронты реального с игнала значительно отличаются от э талонного (фиг.26, пунк тир), то цифровой код, формируемый шифратором 1, будет также отличаться от э талонного и квалифицироватьс я как ошибочный ( фиг. 2, б). Изменяя при разных проверках мес тонах ожд ение строба, можно добиться э талонной цифровой пос лед овательнос ти (сд виг по времени в дальнейшей обработке с игнала корректируется), опред елив с определенной дискрет нос тью динамические искажения реального сигнала (фиг. 2,е) Для нормальной работы инвертора 3 с открытым коллектором к его выходу через диод ы 9 и 10 подключаютс я резис торы 11 и 12, вход ные вывод ы которых с оед инены с шиной +5 В. Подк лючение резис торов к вы ходу инвертора 3 осущес твляетс я с по мощью код а, запис анного в регис тр В по входам 21 Резис торы 11 и 12 имеют разное сопротивление; од ин из них величиной порядка с отен Ом. второй - ед иниц КОм. Ноль на каком-либо вых од е регис тра шу нтирует соответс твующий резис тор и отключает его от инвертора 3. Подключая гот или другой резис тор или оба с разу, можно изменять величину сопротивления в ш ироких пред елах. Уменьш ая величину общего сопротивления на выходе инвертора 3, можно увеличить кру тизну фронтов ци фрового сигнала, ис править искажения формы, возник ающие изза влияния емкос ти монтаж а. Увеличивая сопротивление, можно с низить потребление тока от обьекта 22 контроля и проверить микромощную логику, например К МОП При о тключен ном о бьекте кон тро ля можно проверить правильнос ть работы тес тера, в сос тав которого вх од ит данный выходной блок, кодируя с помощью шифратора 1 цифровые последовательности, формируемые тес тером. /ччз 7993 * • m а -; — ------ — -__ .— .0" _ V ------ — ------- 5 ------------------- ,--- с. 1 1 • 1 1 • 1 е Упорядник Замовлення 4525 Техред М.Моргентал Коректор Н. Милюкова Тираж Підписне Державне патентне відомство України, 254655. ГСП. Київ-53, Львівська пл., 8 Виробничо-видавничий комбінат "Патент", м. Ужгород. вул.Гагаріна, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюOutput tester unit for digital block check

Автори англійськоюVyshniakov Oleksandr Platonovych, Vdovychenko Anatolii Oleksiiovych, Pavliv Dmytro Ivanovych

Назва патенту російськоюВыходной блок тестера для контроля цифровых блоков

Автори російськоюВишняков Александр Платонович, Вдовиченко Анатолий Алексеевич, Павлив Дмитрий Иванович

МПК / Мітки

МПК: G06F 11/273, G06F 11/00

Мітки: блок, контролю, блоків, тестера, вихідній, цифрових

Код посилання

<a href="https://ua.patents.su/4-7993-vikhidnijj-blok-testera-dlya-kontrolyu-cifrovikh-blokiv.html" target="_blank" rel="follow" title="База патентів України">Вихідний блок тестера для контролю цифрових блоків</a>

Попередній патент: Спосіб одержання сорбційних матеріалів

Наступний патент: Ламельний роз’ємний контакт

Випадковий патент: Каталізатор для одержання вінілацетату, спосіб його одержання, спосіб одержання вінілацетату та спосіб одержання носія для каталізатора синтезу вінілацетату