Пристрій для формування часових затримок блв-дпи

Формула / Реферат

1. Пристрій для формування часових затримок, що має канал часової затримки, вузол логічної обробки вхідних сигналів та вузол індикації спрацювання каналу затримки, який відрізняється тим, що в нього введений вузол діагностики функціонування та передачі діагностичної інформації, реалізований на мікроконтролері, вузол вибору величини часової затримки, виконаний як інтелектуальні силові перемикачі, вузол вибору множника затримки, три канали перетворення вхідних сигналів та три перетворювачі вихідних сигналів, при цьому вузлом логічної обробки вхідних сигналів є програмована логічна матриця, перша група входів якої з’єднана з виходами каналу затримки сигналу, друга група входів з’єднана з виходами трьох каналів перетворення вхідних сигналів, а виходи з’єднані з входами вихідних перетворювачів сигналів, крім того, третя група входів програмованої логічної матриці з’єднана з виходами вузла вибору величини часової затримки та вузла вибору множника затримки, до того ж виходи програмованої логічної матриці з’єднані з входами вузла діагностики функціонування та передачі діагностичної інформації, який обернено зв’язаний з програмованою логічною матрицею, крім того, пристрій містить розміщені з двох боків металеві екрани.

Текст

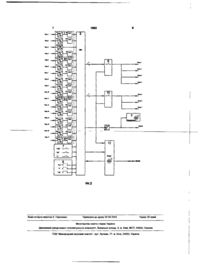

1 Пристрій для формування часових затримок, що має канал часової затримки, вузол логічної обробки вхідних сигналів та вузол індикації спрацювання каналу затримки, який відрізняється тим, що в нього введений вузол діагностики функціонування та передачі діагностичної інформації, реалізований на мікроконтролері, вузол вибору величини часової затримки, виконаний як інтелектуальні силові перемикачі, вузол вибору множника затримки, три канали перетворення вхідних сигналів та три перетворювачі вихідних сиг налів, при цьому вузлом логічної обробки вхідних сигналів є програмована логічна матриця, перша група входів якої з'єднана з виходами каналу затримки сигналу, друга група входів з'єднана з виходами трьох каналів перетворення вхідних сигналів, а виходи з'єднані з входами вихідних перетворювачів сигналів, крім того, третя група входів програмованої логічної матриці з'єднана з виходами вузла вибору величини часової затримки та вузла вибору множника затримки, до того ж виходи програмованої логічної матриці з'єднані з входами вузла діагностики функціонування та передачі діагностичної інформації, який обернено зв'язаний з програмованою логічною матрицею, крім того, пристрій містить розміщені з двох боків металеві екрани Корисна модель відноситься до автоматики, а саме до устаткування для автоматизованих систем управління технологічними процесами ядерних електростанцій та призначений для формування часових затримок Відомий пристрій БЛВ-МАД, ТУ 25-7192-93 Пристрій є найбільш близьким по технічній суті та виконуваним функціям формування часових затримок Цей пристрій містить канал часової затримки, що складається з аналогового реле часу, вузол логічної обробки сигналів, що складається з дискретних елементів та мікросхем малого ступеню інтеграції та вузол індикації спрацювання каналу затримки Сигнали, які необхідно затримати, проходять через ВХІДНІ перетворювачі та об'єднуються логічною функцією "або" Далі об'єднаний сигнал затримується за допомогою аналогового реле часу та подається на ВИХІДНІ перетворювачі Вузол логічної обробки сигналів, який складається з вхідних перетворювачів, логічних елементів "і", "або" та вихідних перетворювачів, виконує функцію логічної обробки сигналів Недоліком відомого пристрою є відсутність системи діагностики функціонування та передачі діагностичної інформації, недостатня захищеність від електромагнітних полів радіочастотного діапазону, недостатня захищеність від індустріальних перешкод, недостатня СТІЙКІСТЬ ДО електричних розрядів, недостатній захист від несанкціонованого доступу, а також відсутність захисту від наносекундних та мікросекундних імпульсних перешкод великої енергії по ланцюгам живлення, велику споживану потужність та порівняно низьку надійність Крім того, пристрій не має конструктивних елементів захисту від пошкодження під час експлуатації В основу корисної моделі поставлено задачу створення пристрою, в якому шляхом використання сучасних мікросхем великого ступеню інтеграції, а саме, програмованої логічної матриці, мікроконтролера, інтелектуальних силових перемикачів, елементів захисту від перешкод та пошкодження супресорів, стабілітронів, самовідновлювальних запобіжників, а також вдосконалення конструктивних елементів захисту та використання діагностики вузлів та елементів пристрою, досягається поліпшення параметрів електромагнітної сумісності, захист пристрою від електромагнітних полів радіочастотного діапазону, від індустріальних перешкод, від електростатичних розрядів, від наносекундних та мікросекундних імпульсних перешкод великої енергії, захисту від несанкціонованого доступу та від пошкодження елементів під час експлуатації Поставлена задача вирішується тим, що в пристрій, який містить канал часової затримки, CM со о 1932 вузол логічної обробки вхідних сигналів та вузол індикації спрацювання каналу затримки, введено вузол діагностики функціонування та передачі діагностичної інформації, реалізований на мікроконтролері, вузол вибору величини часової затримки, виконаний інтелектуальними силовими перемикачами, вузол вибору множника затримки з трьох каналів перетворення вхідних сигналів, та три перетворювача вихідних сигналів, при цьому, вузлом логічної обробки вхідних сигналів є програмована логічна матриця (ПЛМ), перша група входів якої з'єднана з виходами каналу затримки сигналів, друга група входів з'єднана з виходами трьох каналів перетворення вхідних сигналів, а виходи з'єднані з входами перетворювачів вихідних сигналів, крім того, третя група входів програмованої логічної матриці (ПЛМ) сполучена з виходами вузла вибору величини часової затримки та вузла вибору множника затримки, до того ж, виходи програмованої логічної матриці (ПЛМ) з'єднані з входами вузла діагностики функціонування та передачі діагностичної інформації, який зворотно зв'язаний з програмованою логічною матрицею, крім того пристрій постачено металевими екранами, розміщеними з двох його боків Порівняльний аналіз з відомими технічними рішеннями показав, що технічне рішення, яке пропонується, відрізняється наявністю нового складу елементів та має нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості корисної моделі Технічний результат, як наслідок цих властивостей - розширені функціональні можливості пристрою На фігурі 1 наведена блок-схема пристрою Пристрій складається з канапу 1 часової затримки сигналів, програмованої логічної матриці 2, вузла 3 індикації спрацювання каналу затримки, каналу 4 перетворення вхідних сигналів, каналу 5 перетворення вхідних сигналів, каналу 6 перетворення вхідного сигналу, вузла 7 вибору величини часової затримки, вузла 8 вибору множника затримки, перетворювача 9 вихідного сигналу, перетворювача 10 вихідного сигналу, гальванічно розв'язаного перетворювача 11 вихідного сигналу, вузла 12 діагностики функціонування та передачі діагностичної інформації На фігурі 2 представлена функціональна схема пристрою для формування часових затримок БЛВ-ДПИ Пристрій для формування часових затримок БЛВ-ДПИ містить канал 1 часової затримки сигналів, який складається з чотирьох входів Вхі, Вхг, Вхз, Вх4, чотирьох перетворювачів 13, 14, 15, 16 вхідних сигналів - двох перетворювачів 13, 16 вхідних сигналів з 24В на 5В та двох перетворювачів 14, 15 вхідних сигналів з 15В на 5В і трьох буферних елементів 29, ЗО, 31, програмовану логічну матрицю (ПЛМ) 2, вузол індикації 3 каналу затримки, канал 4 перетворення вхідних сигналів, який складається з шести входів Bxs, Вхє, Вх7, Bxe, Bxg, Вхю, шести перетворювачів 17, 18, 19, 20, 21, 22 вхідних сигналів і шести буферних елементів 32, 33, 34, 35, 36, 37, канал 5 перетворення вхідних сигналів, який також має шість входів Вхц, Вхіг, Вхіз, Вхн, Вхі5, Вхіб, шість перетворювачів 23, 24, 25, 26, 27, 28 вхідних сигналів та шість буферних елементів 38, 39, 40, 41, 42, 43, канал 6 перетворення вхідного сигналу, який має один вхід Вхи, один перетворювач 44 вхідного сигналу та буферний елемент 45, вузол 7 вибору часової затримки, вузол 8 вибору множника затримки, перетворювача 9 вихідного сигналу, перетворювача 10 вихідного сигналу, перетворювача 11 вихідного сигналу, вузла 12 діагностики функціонування та передачі діагностичної інформацн Канал 1 часової затримки сигналів та всі канали перетворення сигналів з'єднані з програмованою логічною матрицею 2, виходи якої зв'язані з перетворювачами 9, 10, 11 вихідних сигналів, вузлом 3 індикації спрацювання каналу затримки та вузлом 12 діагностики функціонування та передачі діагностичної інформації Пристрій для формування часових затримок БЛВ-ДПИ працює таким чином ВХІДНІ сигнали каналу 1 часової затримки через Вхі, Вх2, Вхз, Вх4 ВІДПОВІДНИХ рівнів через перетворювачі 13,16 вхідних сигналів з 24В до 5В і перетворювачі 14, 15 вхідних сигналів з 15В до 5В та буферні елементи 29, ЗО, 31 подаються на програмовану логічну матрицю 2, де об'єднуються по ЛОГІЧНІЙ функції "або", затримуються, розмножуються та виводяться на прямі та інверсні виходи ПЛМ 2 Далі сигнали через перетворювач 9 вихідного сигналу з 5В до 15В та перетворювач 11 вихідного сигналу з 5В до 24В подаються на виходи пристрою Вихі, Вих2, Вихв Індикація спрацювання каналу затримки здійснюється світлодюдом "Спрацювання" вузла 3 Величина затримки виставляється за допомогою перемикачів " 1 " , "10", "100" вузла 7 вибору величини затримки, а множник затримки виставляється за допомогою перемичок "0,1", " 1 " , "10" в вузлі 8 вибору множника затримки За допомогою декадних перемикачів "1", "10", "100" здійснюється вибір величини затримки з дискретністю 1с Тим часом ВХІДНІ сигнали Bxs, Вхб, Вхв через перетворювачі 17, 18, 20 вхідних сигналів з 15В до 5В та буферні елементи 32, 33, 35 подаються на ПЛМ 2, де об'єднуються по ЛОГІЧНІЙ функції "і" і далі через перетворювач 9 вихідних сигналів об'єднаний сигнал подається на Вих3 Аналогічно ВХІДНІ сигнали Вх7, Вхэ, Вхю через перетворювачі 19, 21, 22 вхідних сигналів з 15В до 5В та буферні елементи 34, 36, 37 також подаються на ПЛМ 2 де об'єднуються по ЛОГІЧНІЙ функції "і" і через перетворювач 9 вихідних сигналів об'єднаний сигнал подається на Вихд ВХІДНІ сигнали Вхіг, Вх15, Вхі 6 через перетворювачі 24, 27, 28 вхідних сигналів з 15В до 5В та буферні елементи 39, 42, 43 подаються на ПЛМ 2 де об'єднуються по ЛОГІЧНІЙ функції "або" і через перетворювач 10 вихідних сигналів з 5В до 15В об'єднаний сигнал подається на Вих5 ВХІДНІ сигнали Вхи, Вхіз, Вхи через перетворювачі 23, 25, 26 вхідних сигналів та буферні елементи 38, 40, 41 подаються на ПЛМ 2 де об'єднуються по ЛОГІЧНІЙ функції "або" і через вихідний перетворювач 10 з 5В до 15В об'єднаний сигнал подається на Вихб Вхідний сигнал Вхі 7 через перетворювач 44 вхідних сигналів з 15В до 5В та буферний елемент 45 подається на ПЛМ де інвертується Далі через 1932 перетворювач 10 вихідних сигналів з 5В до 15В сигнал подається на Вих7 Вузол 12 діагностики функціонування та передачі інформації, реалізований на мікроконтролері, приймає оброблені сигнали з ПЛМ 2 та здійснює постійний контроль роботи ПЛМ 2, перетворювачів 9, 10 вихідних сигналів та визначає встановлення пристрою за місцем призначення Місцева індикація правильності функціонування пристрою здійснюється СВІТЛОДІДОМ вузла 12 При включенні пристрою також здійснюється контроль вузла 3 індикації спрацювання шляхом подачі команд управління від мікроконтролера на ПЛМ 2 За допомогою локальної мережі RS-485 здійснюється зв'язок вузла 12 діагностики функціонування та передачі інформації з блоком зовнішнього контролю Вузол 12 діагностики функціонування та передачі інформації має наступну діагностичну функцію номер місця пристрою в МІСЦІ призначення, Фіг.1 тип пристрою, заводський номер, рік виробництва, стан прапорів діагностики, інформація про проходження тестування Конструктивно корисна модель БЛВ-ДПИ виконана на друкованій платі, яка закрита з двох боків металевими екранами, що дозволяє реалізувати необхідну захищеність від електромагнітних полів радіочастотного діапазону, від індустріальних перешкод, від електростатичних розрядів, від несанкціонованого доступу та від пошкодження елементів під час експлуатації Використання елементів захисту ланцюгів живлення, входів та виходів також здійснює захист від наносекундних та мікросекундних імпульсних перешкод великої енергії Використання сучасної елементної бази (мікроконтролер ПЛМ) значно зменшує споживану потужність, поліпшує теплові режими та підвищує надійність пристрою 1932 Виді Bxu2 Вад З BXW4 Вад 5 Вад 6 Вяд9 Вяд10 tsa/ 10 В«ц11 Вхд12 |25 б45 "100* 12 ^~ •РОБ' ФІГ.2 Комп ютерна верстка Е Гапоненко Підписано до друку 05 09 2003 Тираж 39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет', вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H01H 43/00

Мітки: блв-дпи, пристрій, часових, формування, затримок

Код посилання

<a href="https://ua.patents.su/4-1932-pristrijj-dlya-formuvannya-chasovikh-zatrimok-blv-dpi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для формування часових затримок блв-дпи</a>

Попередній патент: Спосіб оцінки здатності тканин макроорганізму до приживлення трансплантата

Наступний патент: Пристрій фіксації спрацювання бфс-дпи

Випадковий патент: Кран баштовий